#### **PIN DESCRIPTION**

| Pin No.      | Name            | I/O | Description                                                                                                                                                                                      |

|--------------|-----------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1            | ŌĒ              | 1   | RECEIVE enable input.                                                                                                                                                                            |

| 2–9          | R,              | I/O | 8-bit RECEIVE data output.                                                                                                                                                                       |

| 10           | ERR             | 0   | Output from fault registers. Registers detection of odd parity fault on using clock edge (CLK). A registered ERR output remains low until cleared. Open drain output, requires pull up resistor. |

| 11           | CLR             | 0   | Clears the fault register output.                                                                                                                                                                |

| 16-23 T, I/O |                 | I/O | 8-bit TRANSMIT data output.                                                                                                                                                                      |

| 15           | PARITY          | 1/0 | 1-bit PARITY output.                                                                                                                                                                             |

| 14           | ŌĒ <sub>T</sub> | I   | TRANSMIT enable input.                                                                                                                                                                           |

| 13           | ĒÑ              | i   | Latch enable for the Error Flag Latch.                                                                                                                                                           |

1823 Tbl 07

## **FUNCTION TABLE** — 'FCT853 (NONINVERTING)

| Inputs |                 |     |     |                              |                                          |    | C   | outputs |                    |                                         |

|--------|-----------------|-----|-----|------------------------------|------------------------------------------|----|-----|---------|--------------------|-----------------------------------------|

| ŌĒ,    | ŌĒ <sub>R</sub> | CLR | CLK | R <sub>i</sub><br>(∑ of H'S) | T <sub>i</sub> Incl PARITY<br>(∑ of H'S) | R, | T,  | PARITY  | ERR(1)             | Function                                |

|        | Н               | _   | _   | H (Odd)                      | NA                                       | NA | Н   | L       | NA                 | Transmit data from R Port               |

| L      | Н               | _   | _   | H (Even)                     | NA                                       | NA | Н   | Н       | NA                 | to T Port with parity;                  |

| L      | Н               | _   | _   | L (Odd)                      | NA                                       | NA | L   | L       | NA                 | receiving path is disabled.             |

| L      | Н               | -   | -   | L (Even)                     | NA                                       | NA | L   | Н       | NA .               |                                         |

| Н      | L               | L   | L   | NA                           | H (Odd)                                  | Н  | NA  | NA      | Н                  | Receive data from T Port                |

| Н      | L               | L   | L   | NA                           | H (Even)                                 | Н  | NA  | NA      | L                  | to R Port with parity test              |

| н      | L               | L   | L   | NA                           | L (Odd)                                  | L  | NA  | NA      | Н                  | resulting in flag; transmitting         |

| H      | L               | L   | L   | NA                           | L (Even)                                 | L  | NA  | NA      | L                  | path is disabled.                       |

| Н      | L               | Н   | L   | NA                           | H (Odd)                                  | Н  | NA  | NA      | Η                  | Receive data from T Port                |

| Н      | L               | Н   | L   | NA                           | H (Even)                                 | Н  | NA  | NA      | L                  | to R Port, pass the error test          |

| lΗ     | L               | н   | L   | NA                           | L (Odd)                                  | L  | NA  | NA      | H                  | resulting to error flag;                |

| Н      | L               | Н   | L   | NA                           | H (Even)                                 | L  | NA  | NA      | L                  | transmitting path is disabled.          |

| Н      | L               | Н   | Н   | NA                           | -                                        | -  | NA  | NA      | ERR <sub>n-1</sub> | Store the state of error flag register. |

| -      | -               | L   | Н   | -                            | _                                        | _  | NA  | NA      | Н                  | Clear the state of error flag register. |

| Н      | Н               | Н   | Н   | _                            | _                                        | Z  | Z   | Z       | NC                 | Both transmitting and                   |

| Н      | Н               | L   | Н   | _                            | -                                        | Z  | Z   | Z       | Н                  | receiving paths are disabled.           |

| Н      | Н               | _   | L   | L (Odd)                      | _                                        | Z  | Z   | Z       | Н                  | Parity logic defaults to                |

| Н      | Н               | _   | L   | H (Even)                     | _                                        | Z  | , Z | Z       | L                  | transmit mode.                          |

|        | L               | _   | _   | H (Odd)                      | NA                                       | NA | Н   | Н       | NA                 | Forced-error checking.                  |

| L      | Ĺ               | _   | -   | H (Even)                     | NA                                       | NA | Н   | L       | NA                 |                                         |

| L      | L               | -   | -   | L (Odd)                      | NA                                       | NA | L   | Н       | NA                 |                                         |

| L      | Ĺ               |     |     | L (Even)                     | NA                                       | NA | L   | L       | NA                 |                                         |

1823 TU 08

Odd = Odd number of logic one's Even = Even number of logic one's i = 0, 1, 2, 3, 4, 5, 6, 7

= Low to High transition of clock

#### Note:

3/30/92-3 9-118

<sup>1.</sup> Output state assumes HIGH output pre-state.

| Symbol           | Parameter                                       | Typ¹  | Max   | Units      | Conditions                                                                                                                                                                                                                                                                                          |

|------------------|-------------------------------------------------|-------|-------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I <sub>cc</sub>  | Quiescent Power Supply<br>Current (CMOS inputs) | 0.003 | 0.5   | mA         | $V_{CC} = MAX, f_1 = 0,$<br>Outputs Open,<br>$V_{IN} \le 0.2V \text{ or } V_{IN} \ge V_{CC} - 0.2V$                                                                                                                                                                                                 |

| Δl <sub>cc</sub> | Quiescent Power Supply<br>Current (TTL inputs)  | 0.5   | 2.0   | mA         | $V_{CC} = MAX$ , $V_{IN} = 3.4V^2$ , $f_1 = 0$ , Outputs Open                                                                                                                                                                                                                                       |

| I <sub>cco</sub> | Dynamic Power Supply Current <sup>3</sup>       | 0.15  | 0.25  | mA/<br>mHz | $V_{CC}$ = MAX, One Input Toggling,<br>50% Duty Cycle, Outputs Open,<br>$\overline{OE}_{T}$ = GND, $\overline{OE}_{R}$ = GND,<br>$V_{IN} \le 0.2V$ or $V_{IN} \ge V_{CC} - 0.2V$ ,                                                                                                                  |

|                  | Total Power Supply Current⁵                     | 1.4   | 3.4   | mA         | $V_{\rm cc}$ = MAX,<br>50% Duty Cycle, Outputs Open,<br>One Bit Toggling, $f_{\rm o}$ = 10MHz,<br>$\overline{\rm OE}_{\rm T}$ = GND, $\overline{\rm OE}_{\rm R}$ = $V_{\rm cc}$ , $f_{\rm t}$ = 2.5MHz,<br>$V_{\rm IN}$ $\leq$ 0.2V or $V_{\rm IN}$ $\geq$ $V_{\rm cc}$ -0.2V                       |

| l <sub>o</sub>   |                                                 | 1.9   | 5.4   | mA         | $V_{\rm CC} = {\sf MAX}$<br>50% Duty Cycle, Outputs Open,<br>One Bit Toggling, ${\sf f_0} = {\sf 10MHz}$ ,<br>$\overline{\sf OE}_{\sf T} = {\sf GND}, \overline{\sf OE}_{\sf R} = {\sf V}_{\sf CC}, {\sf f_1} = {\sf 2.5MHz},$<br>${\sf V}_{\sf IN} = {\sf 3.4V}$ or ${\sf V}_{\sf IN} = {\sf GND}$ |

|                  |                                                 | 4.0   | 7.84  | mA         | $V_{\rm cc}$ = MAX<br>50% Duty Cycle, Outputs Open,<br>Eight Bits Toggling, $f_{\rm o}$ = 10MHz,<br>$\overline{\rm OE}_{\rm T}$ = GND, $\overline{\rm OE}_{\rm R}$ = $V_{\rm cc}$ , $f_{\rm 1}$ = 2.5MHz,<br>$V_{\rm IN} \le 0.2V$ or $V_{\rm IN} \ge V_{\rm cc} - 0.2V$                            |

|                  |                                                 | 6.2   | 16.8⁴ | mA         | $V_{CC}$ = MAX<br>50% Duty Cycle, Outputs Open,<br>Eight Bits Toggling, $f_0$ = 10MHz,<br>$\overline{OE}_T$ = GND, $\overline{OE}_R$ = $V_{CC}$ , $f_1$ = 2.5MHz,<br>$V_{IN}$ = 3.4V or $V_{IN}$ GND                                                                                                |

#### Notes:

- 1. Typical values are at V<sub>cc</sub> = 5.0V, +25°C ambient and maximum loading.

- Per TTL driven input (V<sub>N</sub> = 3.4V); all other inputs at V<sub>cc</sub> or GND.

- 3. This parameter is not directly testable, but is derived for use in Total Power Supply calculations.

- 4. Values for these conditions are examples of the I<sub>cc</sub> formula. These limits are guaranteed but not tested.

- =  $1_{\text{DMESCENT}} + 1_{\text{INPUTS}} + 1_{\text{DYMMIC}}$ =  $1_{\text{CC}} + \Delta 1_{\text{CC}} D_{\text{H}} N_{\text{T}} + 1_{\text{CCD}} (f_{\text{V}} Z + f_{\text{t}} N_{\text{t}})$ = Quiescent Current with CMOS input levels

- $\Delta I_{cc}$  = Power Supply Current for a TTL High Input (V<sub>N</sub> = 3.4V)

- D<sub>H</sub> = Duty Cycle for TTL inputs High

N<sub>T</sub> = Number of TTL inputs at D<sub>H</sub>

- l<sub>ccD</sub> = Dynamic Current Caused by an Input Transition Pair (HLH or LHL)

- = Clock Frequency for Register Devices (Zero for Non-Register Devices)

- = Input Frequency

- = Number of Inputs at f.

- All currents are in milliamps and all frequencies are in megahertz.

9-117 3/30/92 - 3

#### **ABSOLUTE MAXIMUM RATINGS<sup>1,2</sup>**

| Symbol           | Parameter                           | Value        | Unit |

|------------------|-------------------------------------|--------------|------|

| T <sub>stG</sub> | Storage Temperature                 | -65 to +150  | °C   |

| T <sub>A</sub>   | Ambient Temperature<br>Under Bias   | -65 to +135  | °C   |

| V <sub>∞</sub>   | V <sub>cc</sub> Potential to Ground | -0.5 to +7.0 | ٧    |

| I <sub>IN</sub>  | Input Current                       | -30 to +5.0  | mA   |

|  | 1623 Tbl 01 |

|--|-------------|

Operation beyond the limits set forth in the above table may impair the useful life of the device. Unless otherwise noted, these limits are over the operating free-air temperature range.

| Symbol           | Parameter                 | Value                    | Unit |

|------------------|---------------------------|--------------------------|------|

| OUTPUT           | Current Applied to Output | 120                      | mA   |

| V <sub>IN</sub>  | Input Voltage             | $-0.5$ to $V_{cc} + 0.5$ | ٧    |

| V <sub>out</sub> | Voltage Applied to Output | $-0.5$ to $V_{cc} + 0.5$ | ٧    |

1823 TH 02

Unused inputs must always be connected to an appropriate logic voltage level, preferably either V<sub>cc</sub> or ground.

#### **RECOMMENDED OPERATING CONDITIONS**

| Free Air Ambient Temperature | Min   | Max    |

|------------------------------|-------|--------|

| Military                     | −55°C | +125°C |

| Commercial                   | 0°C   | +70°C  |

| 823 Tbi 03 | 03 | Tbi | B23 |  |

|------------|----|-----|-----|--|

|------------|----|-----|-----|--|

| Supply Voltage (V <sub>cc</sub> ) | Min    | Max    |

|-----------------------------------|--------|--------|

| Military                          | +4.5V  | +5.5V  |

| Commercial                        | +4.75V | +5.25V |

1823 Tbl 04

#### DC ELECTRICAL CHARACTERISTICS (Over recommended operating conditions)

| Symbol           |                                                 | Parameter                                                                                     | Min                         | Typ¹                                | Max                           | Units                    | V <sub>cc</sub> | Conditions               |                                                  |

|------------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------|-----------------------------|-------------------------------------|-------------------------------|--------------------------|-----------------|--------------------------|--------------------------------------------------|

| V <sub>IH</sub>  | Input HIC                                       | GH Voltage                                                                                    | 2.0                         |                                     |                               | V                        |                 |                          |                                                  |

| V <sub>IL</sub>  | Input LO                                        | W Voltage                                                                                     | 0.5                         |                                     | 0.8                           | V                        |                 |                          |                                                  |

| V <sub>H</sub>   | Hysteres                                        | is                                                                                            |                             |                                     | 0.35                          |                          | ٧               | _                        | All inputs                                       |

| V <sub>CD</sub>  | input Cia                                       | mp Diode Voltage                                                                              |                             |                                     | -0.7                          | -1.2                     | V               | MIN                      | I <sub>IN</sub> = -18mA                          |

| V <sub>OH</sub>  | Output                                          | $V_{cc} = 3V, V_{IN} = 0.2V, \text{ or } V_{cc} -$                                            | 0.2V                        | V <sub>cc</sub> - 0.2               | V <sub>cc</sub>               |                          | V               |                          | I <sub>он</sub> = -32µА                          |

|                  | High<br>Voltage<br>(Except<br>ERR)              | Military/Commercial (CMOS)<br>Military (TTL)<br>Commercial (TTL)                              |                             | V <sub>cc</sub> - 0.2<br>2.4<br>2.4 | V <sub>CC</sub><br>4.3<br>4.3 |                          | V<br>V          | MIN<br>MIN<br>MIN        | I <sub>OH</sub> = -15mA                          |

| V <sub>OL</sub>  | Output                                          | $V_{cc} = 3V, V_{iN} = 0.2V, \text{ or } V_{cc} -$                                            | 0.2V                        |                                     | GND                           | 0.2                      | ٧               |                          | $I_{OL} = 300 \mu A$                             |

|                  | Low<br>Voltage                                  | Military/Commercial (CMOS)<br>Military (TTL)<br>Commercial (TTL)<br>Military/Commercial (TTL) | All Other<br>Outputs<br>ERR |                                     | GND<br>0.3<br>0.3<br>0.3      | 0.2<br>0.5<br>0.5<br>0.5 | >>>>            | MIN<br>MIN<br>MIN<br>MIN | I <sub>oL</sub> = 32mA<br>I <sub>oL</sub> = 48mA |

| I <sub>IH</sub>  | Input HIC                                       | GH Current (Except I/O Pins)                                                                  |                             |                                     |                               | 5                        | μА              | MAX                      | $V_{in} = V_{CC}$                                |

| I <sub>IL</sub>  | Input LO                                        | W Current (Except I/O Pins)                                                                   |                             |                                     |                               | <b>-</b> 5               | μA              | MAX                      | V <sub>IN</sub> = GND                            |

| I <sub>IH</sub>  | Input HIC                                       | GH Current <sup>3</sup> (Except I/O Pins)                                                     |                             |                                     |                               | 5                        | μА              | MAX                      | $V_{IN} = 2.7V$                                  |

| I <sub>IL</sub>  | Input LO                                        | W Current <sup>3</sup> (Except I/O Pins)                                                      |                             |                                     |                               | -5                       | μА              |                          | $V_{IN} = 0.5V$                                  |

| I <sub>IH</sub>  | Input HIG                                       | GH Current (I/O Pins only)                                                                    |                             |                                     |                               | 15                       |                 |                          | $V_{iN} = V_{CC}$                                |

| I <sub>IL</sub>  | Input LOW Current (I/O Pins only)               |                                                                                               |                             |                                     |                               | -15                      | μΑ              | MAX                      | V <sub>IN</sub> = GND                            |

| l <sub>iH</sub>  | Input HIGH Current <sup>3</sup> (I/O Pins only) |                                                                                               |                             |                                     |                               | 15                       | μА              | MAX                      | $V_{IN} = 2.7V$                                  |

| I <sub>IL</sub>  | Input LOW Current <sup>3</sup> (I/O Pins only)  |                                                                                               |                             |                                     |                               | -15                      | μА              | MAX                      | $V_{IN} = 0.5V$                                  |

| los              | Output Short Circuit Current <sup>2</sup>       |                                                                                               |                             | 60                                  | -120                          |                          | mA              | MAX                      | $V_{OUT} = 0.0V$                                 |

| C;N              | Input Car                                       | oacitance <sup>3</sup>                                                                        |                             |                                     | 5                             | 10                       | pF              |                          | All inputs                                       |

| C <sub>OUT</sub> | Output C                                        | apacitance <sup>3</sup>                                                                       |                             |                                     | 9                             | 12                       | рF              |                          | All outputs                                      |

#### Notes

- 1. Typical limits are at  $V_{cc}$  = 5.0V,  $T_{A}$  = +25°C ambient.

- 2. Not more than one output should be shorted at a time. Duration of short should not exceed one second. The use of high speed test apparatus and/or sample and hold techniques are preferable in order to minimize internal chip heating and more accurately reflect

- operational values. Otherwise prolonged shorting of a high output may raise the chip temperature well above normal and thereby cause invalid readings in other parameter tests. In any sequence of parameter tests, I<sub>os</sub> tests should be performed last.

- 3. This parameter is guaranteed but not tested.

1823 Tel 05 noutout

# P54/74FCT853A/B (P54/74PCT853A/B) FAST CMOS PARITY BUS TRANSCEIVER

## Σ.<u>′</u> **FEATURES**

- Function, Pinout, and Drive Compatible with the FCT and F Logic

- FCT-B speed at 7.0ns max. (Com'l) FCT-A speed at 10.0ns max. (Com'l)

- CMOS V<sub>OH</sub> Levels for Low Power Consumption Typically 1/3 of FAST Bipolar Logic

- Edge-rate Control Circuitry for Significantly Improved Noise Characteristics

- ESD protection exceeds 2000V

- Inputs and Outputs Interface Directly with TTL. NMOS, and CMOS Devices

- Outputs Meet Levels Required for CMOS Static RAM Low Power Standby Mode

- 48 mA Sink Current (Com'l), 32 mA (Mil) 24 mA Source Current (Com'l), 15 mA (MII)

- Buffered Direction Tri-State Output

- High Speed Bidirectional Bus Transceiver for **Processor Organized Devices**

- Error Flag with Open-Drain Output

- Manufactured in 0.8 micron PACE Technology™

## DESCRIPTION

The 'FCT853 is a high-performance bus transceivers designed for two-way communications. It contains an 8bit data path from the R (port) to the T (port), an 8-bit data path from the T (port) to the R (port), and a 9-bit parity checker/generator. The latch configuration allows an error to be either passed, stored, sampled, or cleared at the error flag output by using the EN and CLR controls. The clear (CLR) input is used to clear the error flag register. The output enable OE, and OE, are used to force the port outputs to the high impedance state so that the device can drive bus lines directly. In addition,  $\overline{OE}_{\tau}$  and  $\overline{OE}_{g}$  can be used to force a parity error by enabling both lines simultaneously. This transmission of inverting parity gives

the designer more system diagnostic capability. The data presented at the output is non-inverted.

The 'FCT853 is manufacturered using PACE Technology which is Performance Advanced CMOS Engineered to use 0.8 micron effective channel lengths resulting in 500 picoseconds loaded\* internal gate delays. PACE Technology includes two-level metal and epitaxial substrates. In addition to very high performance and very high density, the technology features latch-up protection and single event upset protection, and is supported by a Class 1 environment volume production facility.

\* For a fan-in/fan-out of 4 at 85°C junction temperature and 5.0 V supply. For a fan-in/fan-out of 1, the internal gate delay is 200 picoseconds at room temperature.

### **FUNCTIONAL BLOCK DIAGRAM**

# 19 9-BIT PARITY TREE EN [ ČLR 🖂

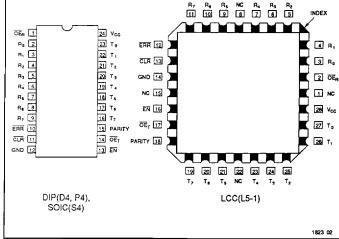

#### PIN CONFIGURATIONS

9-115

SEMICONDUCTOR CORPORATION

1823 01

Means Quality, Service and Speed

5/15/92

## 9

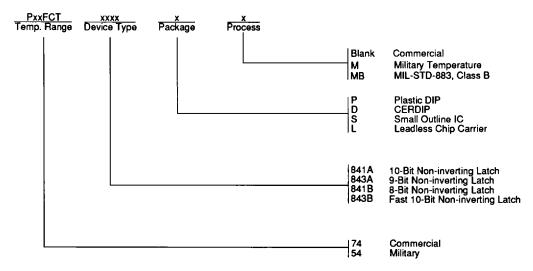

#### **ORDERING INFORMATION**

1564 05

9-113 42242-4