# 512KX8 Bit CMOS Pseudo Static RAM

### **FEATURES**

- Fast Access Time:

- CE Access Time: 80,100,120ns (Max.)

- Cycle Time: Random Read/Write Cycle Time 160, 180, 210ns (Max.)

- Low Power Dissipation: 200mW typ. (Active)

0.5mW typ. (Standby)

- Single 5V ± 10% Power Supply

- . TTL compatible inputs and outputs

- Non multiplexed Address

- Three State Output

- 2048 Refresh Cycles/32ms

- Self Refresh Current: 1mA/200μA (L-version) /100μA (LL-version)

- Data Retention Supply Voltage: 3.0V to 5.5V

- Battery Back-up Capability with KM658512L-L

- 32-Pin JEDEC Standard Plastic Package

- DIP (600mil)

- SOP (525mil)

- TSOP (400mil)

### **GENERAL DESCRIPTION**

The KM658512/L/L-L is a 4,194,304-bit high-speed Pseudo Static Random Access Memory organized as 524,288 words by 8 bits, fabricated using advanced CMOS technology.

The device, utilizing one transistor DRAM cell with onchip refresh timer, provides the advantages of DRAM (Low cost, High density) and Static RAM (Low standby power and ease of use).

The pin-out of KM658512/L/L-L follow the JEDEC standard for Static RAM with the addition of RFSH input. The RFSH input allows two types of refresh operation; Auto Refresh and Self Refresh.

The CE only Refresh is also supported.

The KM658512/L/L-L supports a write function similiar to static RAM in that the input data is written into the memory cell at the rising edge of WE, thus simplifying the interface to standard microprocessors.

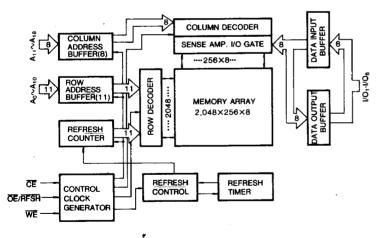

## **FUNCTIONAL BLOCK DIAGRAM**

## PIN CONFIGURATION

| A <sub>18</sub> . 1 | 0 | 32 V <sub>cc</sub>  |

|---------------------|---|---------------------|

| A <sub>16</sub> 2   |   | 31 A <sub>15</sub>  |

| A <sub>14</sub> 3   |   | 30 A <sub>17</sub>  |

| A <sub>12</sub> 4   |   | 29 WE               |

| A <sub>7</sub> 5    |   | 28 A <sub>13</sub>  |

| A <sub>6</sub> 6    |   | 27 A <sub>8</sub>   |

| A <sub>5</sub> 7    |   | 26 A <sub>9</sub>   |

| A4 8                |   | 25 A <sub>11</sub>  |

| A <sub>3</sub> 9    |   | 24 OE/RFSH          |

| A <sub>2</sub> 10   |   | 23 A <sub>10</sub>  |

| A <sub>1</sub> 11   |   | 22 ČE               |

| A <sub>0</sub> 12   |   | 21 I/O <sub>8</sub> |

| 1/0, 13             |   | 20 I/O <sub>7</sub> |

| I/O <sub>2</sub> 14 |   | 19 I/O <sub>6</sub> |

| I/O₃ 15             |   | 18 I/O <sub>5</sub> |

| V <sub>SS</sub> 16  |   | 17 I/O <sub>4</sub> |

|                     |   |                     |

| Pin Name                           | Pin Function          |

|------------------------------------|-----------------------|

| A0-A18                             | Address Inputs        |

| WE                                 | Write Enable          |

| OE/RFSH                            | Output Enable/Refresh |

| CE                                 | Chip Enable           |

| I/O <sub>1</sub> -I/O <sub>8</sub> | Data Inputs/Outputs   |

| Vcc                                | Power supply          |

| Vss                                | Ground                |