# IH5148 - IH5151

#### **GENERAL DESCRIPTION**

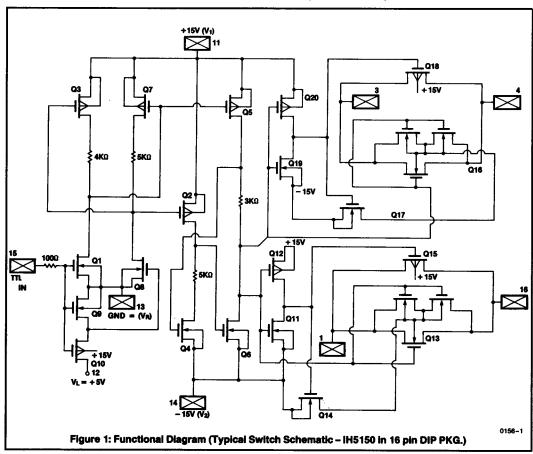

The IH5148 family of solid state analog switches are designed using an improved, high voltage CMOS technology. Destructive latchup has been eliminated. Early CMOS switches were destroyed when power supplies were removed with an input signal present; the IH5148 CMOS technology has eliminated this problem.

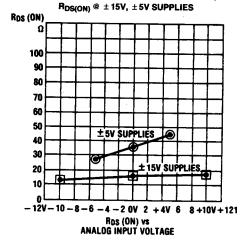

Key performance advantages of the 5148 series are TTL compatibility and ultra low-power operation.  $R_{DS(on)}$  switch resistance is typically in the  $14\Omega$  To  $18\Omega$  Area, for signals in the -10V to +10V range. Quiescent current is less than  $10\mu\text{A}$ . The 5148 also guarantees Break-Before-Make switching which is logically accomplished by extending the ton time (200nsec typ.) such that it exceeds topper time (120nsec typ.). This insures that an ON channel will be turned OFF before an OFF channel can turn ON. The need for external logic required to avoid channel to channel shorting during switching is thus eliminated.

Many of the devices in the 5148 series are pin-for-pin compatible with other analog switches, and offer improved electrical characteristics.

# High Reliability High-Level CMOS Analog Switches

#### **FEATURES**

- Low R<sub>DS</sub>(ON) 25Ω

- ullet Switches Greater Than 20Vpp Signals With  $\pm$  15V Supplies

- Quiescent Current Less Than 100µA

- Break-Before-Make Switching t<sub>OFF</sub> 120nsec Typ., t<sub>ON</sub> 200nsec Typical

- TTL, CMOS Compatible

- Non-Latching With Supply Turn-Off

- Complete Monolithic Construction

- ±5V to ±15V Supply Range

# CMOS ANALOG SWITCH PRODUCT CONDITIONING

- The Following Processes Are Performed 100% in Accordance With MiL-STD-883

- Precap Visual Method 2010, Cond. B

- Stabilization Bake Method 1008

- Temperature Cycle -- Method 1010

- Centrifuge Method 2001, Cond. E

- Hermeticity Method 1014, Cond. A, C

- (Leak Rate < 5×10-7 atm cc/s)

#### ORDERING INFORMATION

| Order Part<br>Number | Function  | Package          | Temperature Range | Harris<br>Equivalent |

|----------------------|-----------|------------------|-------------------|----------------------|

| IH5148MJE            | Dual SPST | 16 Pin CERDIP    | -55°C to 125°C    | HI-5048              |

| IH5148MFD            | Dual SPST | 14 Pin Flat Pack | -50°C to 125°C    | HI-5048              |

| IH5149MJE            | Dual DPST | 16 Pin CERDIP    | - 55°C to 125°C   | HI-5049              |

| IH5149MFD            | Dual DPST | 14 Pin Flat Pack | - 50°C to 125°C   | HI-5049              |

| IH5150MJE            | SPDT      | 16 Pin CERDIP    | -55°C to 125°C    | HI-5050              |

| IH5150MFD            | SPDT      | 14 Pin Flat Pack | -50°C to 125°C    | HI-5050              |

| IH5151MJE            | Dual SPDT | 16 Pin CERDIP    | -55°C to 125°C    | HI-5051              |

| IH5151MFD            | Dual SPDT | 14 Pin Flat Pack | -50°C to 125°C    | HI-5051              |

NOTES: 1. Ceramic (side braze) devices also available; consult factory.

<sup>2.</sup> MIL temp range parts also available with MIL-STD-883 processing.

#### **ABSOLUTE MAXIMUM RATINGS**

| V+, V                            | <36V  |

|----------------------------------|-------|

| V+, V <sub>D</sub>               |       |

| V <sub>D</sub> , V <sup>-</sup>  |       |

| V <sub>D</sub> , V <sub>S</sub>  |       |

| V <sub>1</sub> , V               |       |

| V <sub>I</sub> , V <sub>IN</sub> |       |

| V <sub>I</sub>                   |       |

| Vin                              |       |

| Current (Any Terminal)           | 50mA  |

| Storage Temperature65°C to +1    | 150°C |

| Operating Temperature55°C to         | + 125°C |

|--------------------------------------|---------|

| Lead Temperature (Soldering, 10sec)  | . 300°C |

| Power Dissipation                    | 450mW   |

| (All Leads Soldered to a P.C. Board) |         |

| Derate 6mW/°C Above 70°C             |         |

NOTE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **ELECTRICAL CHARACTERISTICS** $(T_A @ 25^{\circ}C, V^{+} = +15V, V^{-} = -15V, V_L = +5V)$

| Per Channel                    |                                                           |                                                                   | М        | in/Max Lin    | nits    |       |

|--------------------------------|-----------------------------------------------------------|-------------------------------------------------------------------|----------|---------------|---------|-------|

| Symbol                         | Characteristic                                            | Test Conditions                                                   | Military |               |         | Units |

|                                |                                                           |                                                                   | −55°C    | + 25°C        | + 125°C |       |

| I <sub>IN(ON)</sub>            | Input Logic Current                                       | V <sub>IN</sub> = 2.4V (Note 1)                                   | ±1       | ±1            | ±10     | μΑ    |

| IN(OFF)                        | Input Logic Current                                       | V <sub>IN</sub> = 0.8V (Note 1)                                   | ±1       | ±1            | ±10     | μΑ    |

| R <sub>DS(ON)</sub>            | Drain-Source On<br>Resistance                             | $V_D = \pm 10V$ , $I_S = -10mA$                                   | 25       | 25            | 50      | Ω     |

| ΔR <sub>DS(ON)</sub>           | Channel to Channel R <sub>DS(ON)</sub> Match              |                                                                   |          | 10<br>(Typ)   | ,,,,,,  | Ω     |

| V <sub>ANALOG</sub>            | Min. Analog Signal<br>Handling Capability                 |                                                                   | <u>-</u> | ± 14<br>(Typ) | _       | v     |

| l <sub>D(OFF)</sub><br>Is(OFF) | Switch OFF Leakage Current                                | V <sub>ANALOG</sub> = -10V to +10V                                |          | ± 1.0         | 100     | nA    |

| I <sub>D(ON)</sub> +<br>!s(on) | Switch On Leakage Current                                 | $V_D = V_S = -10V \text{ to } +10V$                               |          | ± 1.0         | 100     | nA    |

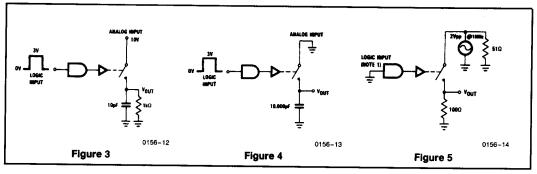

| Q <sub>(INJ)</sub>             | Charge Injection                                          | See Figure 4                                                      | ·        | (10)<br>(Typ) |         | mV    |

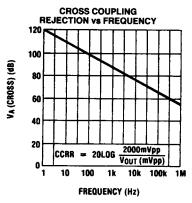

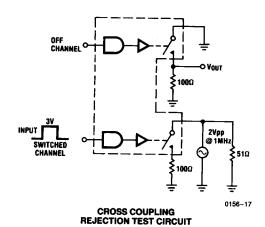

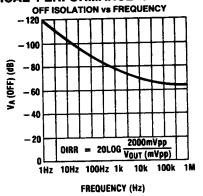

| OIRR                           | Min. Off Isolation Rejection Ratio                        | $I=1MHz$ , $R_L=100\Omega$ , $C_L \le 5pF$ , See Figure 5         |          | 54<br>(Typ)   |         | dB    |

| SUPPLY                         |                                                           | <u> </u>                                                          |          |               |         |       |

| I+                             | + Power Supply Quiescent Current                          |                                                                   | 10       | 10            | 100     | μΑ    |

| 1-                             | - Power Supply Quiescent Current                          | $V_1 = +15V, V_2 = -15V.$                                         | 10       | 10            | 100     | μА    |

| ΙL                             | +5V Supply Quiescent Current                              | V <sub>L</sub> =+5V, V <sub>R</sub> =0                            | 10       | 10            | 100     | μА    |

| IGND                           | Gnd Supply Quiescent Current                              |                                                                   | 10       | 10            | 100     | μA    |

| CCRR                           | Min. Channel to Channel<br>Cross Coupling Rejection Ratio | One Channel Off;<br>Any Other Channel<br>Switches as per Figure 8 |          | 54<br>(Typ)   |         | dB    |

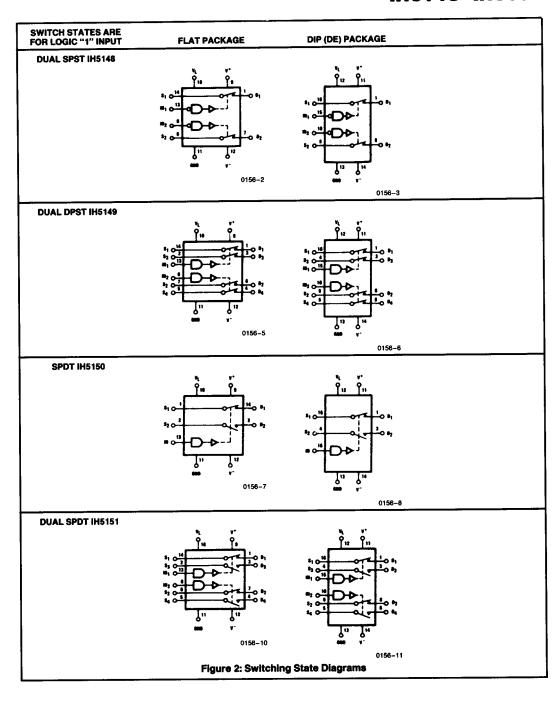

NOTE 1. Some channels are turned on by high "1" logic inputs and other channels are turned on by low "0" inputs; however 0.8V to 2.4V describes the min. range for switching properly. Refer to logic diagrams to find logical value of logic input required to produce "ON" or "OFF" state.

# SWITCHING TIME SPECIFICATION IH5148 SPST SWITCH

| Symbol           | Parameter         | Test Conditions                           | Min | Max | Units |

|------------------|-------------------|-------------------------------------------|-----|-----|-------|

| t <sub>on</sub>  | Switch "on" time  | $R_L = 1K\Omega$ ; $V_{ANALOG} = -10V$    |     | 250 | ns    |

| t <sub>off</sub> | Switch "off" time | T <sub>O</sub> + 10V; See Figures 3 and 6 |     | 200 | ns    |

#### **IH5149 DPST SWITCH**

| L | Symbol           | Parameter         | Test Conditions                           | Min | Max | Units |

|---|------------------|-------------------|-------------------------------------------|-----|-----|-------|

| L | t <sub>on</sub>  | Switch "on" time  | $R_L = 1K\Omega$ , $V_{ANALOG} = -10V$    |     | 350 | ns    |

| Į | t <sub>off</sub> | Switch "off" time | T <sub>O</sub> + 10V; See Figures 3 and 6 |     | 250 | ns    |

#### IH5150 & IH5151 SPDT SWITCH

| Symb             | ool | Parameter         | Test Conditions                           | Min | Max | Units |

|------------------|-----|-------------------|-------------------------------------------|-----|-----|-------|

| ton              |     | Switch "on" time  | $R_L = 1K\Omega$ , $V_{ANALOG} = -10V$    |     | 500 | ns    |

| t <sub>off</sub> |     | Switch "off" time | T <sub>O</sub> + 10V; See Figures 3 and 6 |     | 250 | ns    |

NOTE 2. For IH5150 & IH5151 devices, channels which are off for logic input≥ 2.4V (Pins 3 & 4 on 5150, & Pins 3 & 4, 5 & 6 on 5151) have slower t<sub>on</sub> time, than channels on Pins 1, 16, & 8, 9. This is done so switch will maintain break-before-make action when connected in DT configuration, i.e. Pin 1 connected in Pin 3.

#### **TEST CIRCUITS**

## TYPICAL PERFORMANCE CHARACTERISTICS (Per Channel)

0156-16

0156-15

2-422 \_

# TYPICAL PERFORMANCE CHARACTERISTICS (Per Channel) (Continued)

OFF STATE DEPENDS ON PART VOUT

OFF ISOLATION TEST CIRCUIT

POWER SUPPLY QUIESCENT CURRENT VS LOGIC FREQUENCY RATE

2000 - ROLLING TO THE TOTAL TO

LOGIC IN  $f = \frac{1}{T}$ LOGIC INPUT WAVEFORM

0156-20 Vout a ± 10V (15 H5148 SHOWN (H) Vout (13) OGIC INPUT ov +50 (1) +15V ov Vout Vout 8 ±10V 0156-22 Figure 6: Switching Time Test Circuit

#### **Nulling Out Charge Injection:**

Charge injection (Qinj. on spec. sheet) is caused by gate to drain, or gate to source capacitance of the output switch MOSFET. The gates of these MOSFETs typically swing from -15V to +15V as a rapidly changing pulse; thus this 30Vpp pulse is coupled through gate capacitance to output load capacitance, and the output "step" is a voltage divider from this combination. For example:

Qinject (Vpp)

$$\simeq \frac{C_{gate}}{C_{Load}} \times 30V$$

step.

i.e.

C<sub>gate</sub> = 1.5pF, C<sub>Load</sub> = 1000pF, then

Qinject(Vpp) =

$$\frac{1.5pF}{1000pF} \times 30V$$

step =  $45mVpp$

Thus if you are using switch in a Sample & Hold application with  $C_{\text{sample}}=1000\text{pF}$ , a 45mVpp "Sample to Hold error step" will occur.

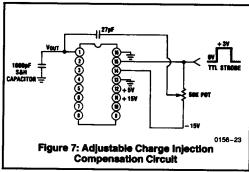

To null this error step out to zero the following circuit can be used:

The circuit shown above nulls out charge injection effects on switch pins 1 and 16; a similar circuit would be required on switch pins 8 and 9.

Simply adjust the pot until  $V_{\mbox{OUT}}\!=\!\mbox{OmVpp}$  pulse, with  $V_{\mbox{ANALOG}}\!=\!\mbox{OV}.$

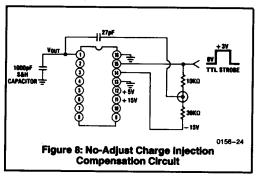

If you do not desire to do any adjusting, but wish the least amount of charge injection possible, then the following circuit should be used:

This configuration will produce a typical charge injection of V<sub>OUT</sub> ≤ 10mVpp into the 1000pF S & H capacitor shown.

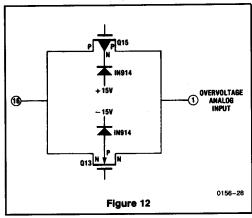

#### **Fault Condition Protection**

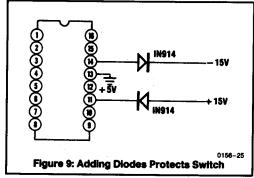

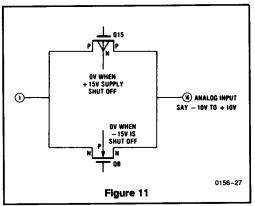

If your system has analog voltage levels which are independent of the  $\pm$ 15V (Power Supplies), and these analog levels can be present when supplies are shut off, you should add fault protection diodes as shown below:

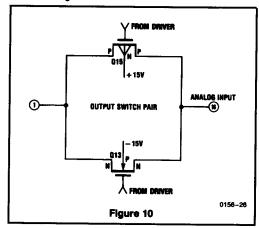

If the analog input levels are below ±15V, the pn junctions of Q13 & Q15 are reversed biased. However if the ±15V supplies are shut off and analog levels are still present, the configuration becomes;

The need for these diodes, in this circumstance, is shown below:

If ANALOG in is greater than 1V, then the pn junction of Q15 is forward biased and excessive current will be drawn. The addition of IN914 diodes prevents the fault currents from destroying the switch. A similar event would occur if ANALOG in was less than or equal to -1V, wherein Q13 would become forward biased. The IN914 diodes form a "back to back" diode arrangement with Q13 & Q15 bodies.

This structure provides a degree of overvoltage protection when supplies are on normally, and analog input level exceeds supplies.

This circuit will switch up to about ±18V ANALOG overvoltages. Beyond this drain(N) to body(P) breakdown VOLT-AGE of Q13 limits overvoltage protection.