6.2

## DAC63

# Ultra-High Speed DIGITAL-TO-ANALOG CONVERTER

#### **FEATURES**

- 12-BIT RESOLUTION AND ACCURACY

- 30nsec SETTLING TIME (MAJOR CARRY)

- ECL-COMPATIBLE INPUTS

- LOW GLITCH ENERGY

- ◆ ±30ppm/°C MAX GAIN DRIFT

- LINEARITY ERROR LESS THAN ±1/2LSB OVER SPECIFIED TEMP RANGE

### **DESCRIPTION**

The DAC63 is an ultra-fast-settling 12-bit current output D/A converter in a 24-pin dual-in-line package. The inputs are ECL-compatible and the output settles in 30nsec, typ (40nsec, max for C and T grades) to within ±0.012% of Full Scale Range for an MSB change. The DAC63 utilizes a monolithic 12-bit switch chip and a stable thin-film-on-sapphire resistor network to achieve fast settling time and excellent stability over temperature and time. Because of the close thermal tracking of the currentswitching transistors (all on one monolithic chip), the possibility of thermal-tail settling time problems are eliminated. An internal applications resistor for use with an external output op amp is included to convert the output current to insure excellent tracking and therefore lower drift. The linearity is guaranteed to be within ±1/2LSB over the specified temperature range of -25°C to +85°C for the CG, CM, BG, and BM grades and -55°C to +125°C for SM and TM grades. Gain drift is ±30ppm/°C max and bipolar offset drift is ±10ppm of FSR/°C max (high grades). Also included internally is a +6.2V reference. An output voltage compliance range of +2.0V to -0.5V allows the generation of an output voltage

- ADJUSTABLE LOGIC THRESHOLD FOR IDEAL SWITCHING

- INTERNALLY-BYPASSED SUPPLY LINES TO MINIMIZE SETTLING TIME

- INTERNAL FEEDBACK RESISTOR FOR EXCELLENT THERMAL TRACKING

- INDUSTRIAL AND MILITARY GRADES

- HIGH RELIABILITY SCREENING AVAILABLE

without using an external output amplifier. The device is available in both metal and ceramic bottom-brazed packages.

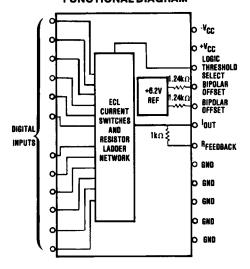

#### **FUNCTIONAL DIAGRAM**

International Airport Industrial Park - P.O. Box 11400 - Tucson, Arizona 85734 - Tel. (602) 746-1111 - Twx: 910-952-1111 - Cable: BBRCORP - Telex: 66-6491

## **SPECIFICATIONS**

**ELECTRICAL**At +25°C and rated supplies unless otherwise specified.

| MODEL                                  |       | DAC63CG/CM/TM  |          | DAC63BG/BM/SM |                                         |        | 4                                     |

|----------------------------------------|-------|----------------|----------|---------------|-----------------------------------------|--------|---------------------------------------|

| PARAMETER                              | MIN   | TYP            | MAX      | MIN           | TYP                                     | MAX    | UNITS                                 |

| INPUT                                  |       |                |          |               |                                         |        |                                       |

| DIGITAL INPUT                          | 1     | T              | T        |               | T                                       |        |                                       |

| Resolution                             | ĺ     |                | 12       |               |                                         | •      | Bits                                  |

| Logic Inputs <sup>(1)</sup>            |       | ECL-compatible | 1        |               | •                                       |        | 1                                     |

| Logic "1": Voltage                     | -0.78 | -0.90          | -0.96    | •             | •                                       | •      | V                                     |

| Current                                | 6.0   |                | 33.0     | •             |                                         | •      | μΑ                                    |

| Logic "0": Voltage                     | -1.62 | -1.75          | 1.85     | •             | •                                       |        | V                                     |

| Current                                |       | 10.0           | 1 1      |               | •                                       |        | nA                                    |

| Logic Threshold: Voltage               | -1.20 | 1.33           | -1.40    | •             | 1 .                                     | ٠ .    | ) v.                                  |

| Current                                |       |                | 0.25     |               | <u> </u>                                | ·      | mA                                    |

| TRANSFER CHARACTERISTICS               |       |                |          |               |                                         |        |                                       |

| ACCURACY                               |       |                |          |               |                                         | l .    | % of FSR <sup>(3</sup>                |

| Linearity Error                        | ì     |                | ±0.012   |               |                                         | 1 :    |                                       |

| Differential Linearity Error           | Į.    |                | ±0.012   |               | l .                                     | 1 .    | % of FSR                              |

| Gain Error <sup>(2)</sup>              |       | ±0.02          | ±0.1     |               | 1 .                                     | l :    | % of FSR                              |

| Offset Error <sup>izi</sup> : Unipolar |       | ±0.01          | ±0.04    |               | 1 :                                     | l .    | % of FSR                              |

| Bipolar                                |       | ±0.02          | ±0.1     |               |                                         |        | 76 OI F Sh                            |

| Monotonicity Temp. Range (min)         |       |                | l I      | _             |                                         | ١.     | •c                                    |

| CG, CM, BG, BM                         | -25   |                | +85      |               |                                         |        | , °C                                  |

| TM, SM                                 | -55   |                | +125     |               | ļ                                       |        | <del> </del>                          |

| SETTLING TIME (into 150Ω)              | 1     | 1              | 1        |               |                                         | 1      |                                       |

| 1LSB Change                            |       |                | 1 1      |               |                                         |        |                                       |

| Settling to ±0.012% of FSR             |       |                |          |               | 40                                      | 50     | nsec                                  |

| CM/TM, BM/SM                           | 1     | 30             | 40       |               | 40                                      | 45     | nsec                                  |

| CG, BG                                 |       | 30             | 40       |               | 35                                      | 49     | lisec                                 |

| Full Scale Change                      |       |                |          |               | 20                                      |        | nsec                                  |

| Settling to ±1% of FSR                 |       | 17             |          |               | 20                                      | İ      | nsec                                  |

| ±0.1% of FSR                           |       | 30             |          |               |                                         | 1      | lisec                                 |

| ±0.024% of FSR                         |       |                | 0.5      |               | 65                                      | 75     | nsec                                  |

| CM/TM, BM/SM                           |       | 55             | 65<br>50 |               | 40                                      | 55     | nsec                                  |

| CG, BG                                 |       | 35             | 30       |               | 1 **                                    | ] 33   | 1.300                                 |

| ±0.012% of FSR                         |       | 70             |          |               | 80                                      |        | nsec                                  |

| CM/TM, BM, SM                          |       | 40             |          |               | ,                                       |        | nsec                                  |

| CG, BG<br>Glitch Energy (4)            |       | 250            |          |               |                                         |        | LSB/nsec                              |

| DRIFT (over specified temp. range)     |       |                | †        |               | † · · · · · · · · · · · · · · · · · · · |        |                                       |

| Gain                                   | 1     | ±15            | ±30      |               | ±20                                     | ±40    | ppm/°C                                |

| Offset: Unipolar                       |       | ±0.3           | ±0.6     |               | ±0.5                                    | ±1     | ppm/°C                                |

| Bipolar                                |       | 10.0           | ±10      |               |                                         | ±15    | ppm/°C                                |

| Linearity Error                        |       |                |          |               |                                         | 1      |                                       |

| (over specified temp. range)           |       |                | ±0.012   |               |                                         | ±0.025 | % of FSR                              |

| Differential Linearity Error           | i     |                |          |               |                                         |        |                                       |

| (over specified temp. range)           | 1     |                | ±0.025   |               |                                         | ±0.05  | % of FSR                              |

| OUTPUT                                 |       |                |          |               | 1                                       |        |                                       |

| ANALOG OUTPUT                          |       | 1              |          |               |                                         |        | T                                     |

| Output Current                         | 1     | 0 to - 10, ±5  |          |               |                                         |        | mA                                    |

| Output Voltage Ranges                  | i i   |                |          |               |                                         |        | 1                                     |

| with External Op Amp                   |       | 0 to +10, ±5   | 1        |               |                                         |        | V                                     |

| without External Op Amp '5'            |       | 0 to +15, ±0.5 | 1        |               |                                         |        | V                                     |

| Output Impedance without               |       | 1              |          |               |                                         |        |                                       |

| External Op Amp                        |       | 1              | 1        |               |                                         |        | 1                                     |

| Unipolar: Positive                     |       | 150            |          |               |                                         |        | Ω                                     |

| Negative                               |       | 200            | !!!      |               | · ·                                     |        | Ω                                     |

| Bipolar                                |       | 170            | i l      |               | •                                       |        | Ω                                     |

| Compliance Voltage                     | -0.5  |                | +2.0     | •             |                                         | ·      |                                       |

| POWER SUPPLIES AND REFERENCE           |       |                |          |               |                                         |        | · · · · · · · · · · · · · · · · · · · |

| Internal Reference Voltage             |       | +6.2           |          |               | 1 :                                     | 1      | V                                     |

| Internal Reference Drift               | 1     | ±15            | j l      |               |                                         | l .    | ppm/°C                                |

| Power Supply Voltages                  | ± 13  | ± 15           | ±18      | •             | 1                                       | 1 :    |                                       |

| Power Supply Current: +15V             |       | 26             | 31       |               | 1 :                                     | 1 :    | mA                                    |

| 15V                                    |       | 38             | 46       |               | 1                                       | · ·    | mA<br>n m A                           |

| Power Supply Sensitivity: +15V         |       | ±0.0035        |          |               | 1                                       | 1      | %/%∆V                                 |

| -15V                                   | 1     | ±0.0004        | 1        |               | 1 :                                     | 1 .    | %/%∆∨                                 |

| Power Dissipation                      | 1     | 960            | 1160     |               | 1 '                                     | 1      | mW                                    |

| MODEL                                                          | DAC63CG/CM/TM                                        |     |                     | DAC63BG/BM/SM |     |     |                                       |

|----------------------------------------------------------------|------------------------------------------------------|-----|---------------------|---------------|-----|-----|---------------------------------------|

| PARAMETER                                                      | MIN                                                  | TYP | MAX                 | MIN           | TYP | MAX | UNITS                                 |

| PHYSICAL CHARACTERISTICS                                       |                                                      |     |                     |               |     |     | ļ                                     |

| TEMPERATURE RANGE Specification: CG, CM, BG, BM TM, SM Storage | -25<br>-55<br>-65                                    |     | +85<br>+125<br>+150 | :             |     | :   | ပံ့<br>လံ့ ပံ့                        |

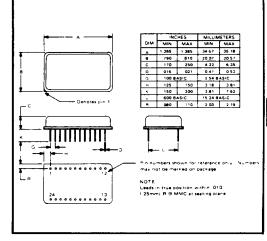

| PACKAGE<br>CG, BG<br>CM, TM, BM, SM                            | 24-pin DIP bottom-brazed ceramic<br>24-pin DIP metal |     |                     |               |     |     | · · · · · · · · · · · · · · · · · · · |

|                                                                |                                                      |     |                     |               |     |     |                                       |

|                                                                |                                                      |     |                     |               |     |     |                                       |

<sup>\*</sup>Specification same as for DAC63CG/CM/TM.

NOTES: (1) Logic Input voltages and currents are dependent on the logic threshold voltage. The logic input values given in each column are correct for the logic threshold voltage given in that column. (2) When used with an external output op amp or when the internal impedances/resistors are used as the load. (3) FSR is Full Scale Range, which is 10mA for both the DAC63BG and DAC63CG. (4) Refer to Output Glitch section. (5) Refer to Figures 8 and 9.

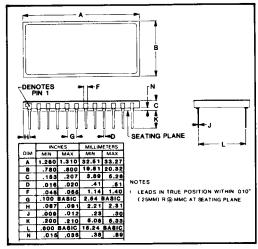

#### **MECHANICAL**

#### **PIN ASSIGNMENTS**

| Pin No. | Function                     |  |  |

|---------|------------------------------|--|--|

| 1       | Bit 1 (MSB)                  |  |  |

| 2       | Bit 2                        |  |  |

| 3       | Bit 3                        |  |  |

| 4       | Bit 4                        |  |  |

| 5       | Bit 5                        |  |  |

| 6       | Bit 6                        |  |  |

| 7       | Bit 7                        |  |  |

| 8       | Bit 8                        |  |  |

| 9       | Bit 9                        |  |  |

| 10      | Bit 10                       |  |  |

| 11      | Bit 11                       |  |  |

| 12      | Bit 12 (LSB)                 |  |  |

| 13      | GND                          |  |  |

| 14      | GND                          |  |  |

| 15      | GND                          |  |  |

| 16      | GND                          |  |  |

| 17      | GND                          |  |  |

| 18      | Feedback Resistor Connection |  |  |

| 19      | Current Output               |  |  |

| 20      | Bipolar Offset               |  |  |

| 21      | Bipolar Offset               |  |  |

| 22      | Logic Threshold              |  |  |

| 23      | +15VDC                       |  |  |

| 24      | -15VDC                       |  |  |

## DISCUSSION OF SPECIFICATIONS

#### **ACCURACY**

Linearity of a D/A converter is one of the true measures of its performance. The linearity error of the DAC63 is specified over its entire temperature range. The analog output will not vary by more than  $\pm 1/2$ LSB from an ideal straight line drawn between the end points (inputs all "1"s and all "0"s) over the specified temperature range.

Differential linearity error of a D/A converter is the deviation from an ideal 1LSB voltage change from one adjacent output state to the next. A differential linearity error specification of  $\pm 1/2$ LSB means that the output voltage step sizes can range from 1/2LSB to 3/2LSB when the input changes from one adjacent input state to the next.

Monotonicity over the specified temperature range is guaranteed to insure that the analog output will increase or remain the same for increasing input digital codes.

#### DRIFT

Gain Drift is a measure of the change in the full scale range output over temperature expressed in parts per million per °C (ppm/°C). Gain drift is established by: 1) testing the end point differences for the DAC63 at tmin, +25°C, and tmax; 2) calculating the gain error with respect to the +25°C value and; 3) dividing by the temperature change. This figure is expressed in ppm/°C and is given in the electrical specifications (includes internal reference).

Offset Drift is a measure of the actual change in output around zero over the specified temperature range. The offset is measured at t<sub>min</sub>, +25°C, and t<sub>max</sub>. The maximum change in Offset is referenced to the Offset at +25°C and is divided by the temperature range. This drift is expressed in parts per million of full scale range per °C (ppm of FSR/°C).

#### COMPLIANCE

Compliance voltage is the maximum voltage swing allowed on the current output node in order to maintain specified accuracy. The maximum compliance voltage of the DAC63 is  $\pm 2.0V$  and  $\pm 0.5V$ .

#### POWER SUPPLY SENSITIVITY

Power supply sensitivity is a measure of the effect of a power supply change on the D/A converter output. It is defined as a percent of FSR per percent of change in either the positive or negative supplies about the nominal power supply voltage. To insure precision operation, each supply lead should be bypassed to ground as close to the unit as possible with a  $1\mu$ F CS-type tantalum capacitor.

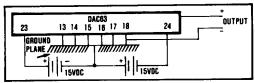

#### GROUNDING

Care must be exercised when grounding the DAC63 (pins 13, 14, 15, 16, and 17). In order to preserve the stated linearity and accuracy specifications it is necessary to use the ground pins as the analog ground reference point. Any voltage drop that develops between any of these five pins and the actual ground reference point will degrade the performance of the DAC63. To achieve fast settling performance it is recommended that pins 13 through 17 be returned directly to a ground plane (see Figure 1). The analog ground should be located as close to the DAC63 as possible. Otherwise, the accuracy will be degraded by the voltage drop in the ground lines.

FIGURE 1. DAC63 Grounding.

## DIGITAL INTERFACE, LOGIC THRESHOLD, AND NOISE IMMUNITY

The DAC63 is compatible with conventional ECL logic families such as ECL 10,000. The circuit diagram shows that the equivalent circuit of each DAC63 digital input is the base of one side of a differential amplifier. The logic 1 input voltage is -0.85V with a typical input current of  $8\mu$ A. The logic 0 input voltage is -1.75V with an input current of less than 8nA.

The Logic Threshold function of the DAC63 is very important in dealing with noise in the ECL input-driving circuitry. The ECL 10,000 logic family has a noise immunity of 125mV maximum. It has a temperature coefficient of  $-1.4 \text{mV}/^{\circ}\text{C}$  and a power supply sensitivity of  $16 \text{mV}/\% \Delta V$ . With a realistic condition of a 5% power supply variation and a 25°C temperature change, the noise immunity would be degraded to 10 mV. In addition, a precision D/A converter is more susceptible to noise than is the ECL logic. Noise at levels acceptable to the logic can couple through the D/A, resulting in an unacceptably noisy output.

Through the logic threshold input, the threshold voltage of the DAC63 is dynamically adjusted as the temperature and power supplies vary to give maximum noise immunity at the analog output over a wide range of conditions.

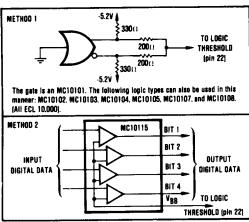

If an MC10115 line receiver (or similar logic function) is used to drive the DAC63 input, the logic threshold pin can be driven by the V<sub>BB</sub> output of the ECL gate. Refer to an ECL 10,000 data book for more detail. Figure 2 shows alternate methods for generating the drive signal for logic threshold, pin 22.

FIGURE 2. Driving the Logic Threshold Input.

#### SETTLING TIME

Settling time for the DAC63 is the total time required for the output to settle within an error band around its final value after a digital input change. This time includes the digital delay of the internal switches. The settling time of the DAC63 is determined by digitizing the output waveform produced by toggling the inputs between 011111111111 and 100000000000 continuously and verifying the output settles to within ±1/2LSB in the specified time. The testing technique used is described in detail in Application Note AN-115 which can be obtained from the factory.

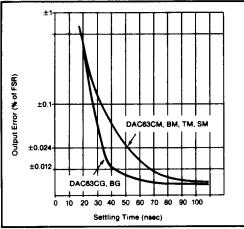

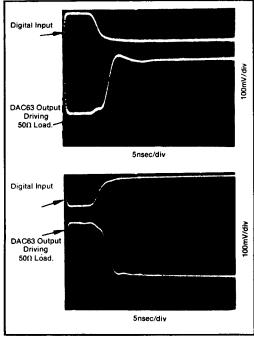

Figure 3 shows a typical settling time curve of the DAC63 versus output error. This curve is for full-scale digital code changes. Figure 4 is a photograph showing typical output response characteristics of the DAC63.

FIGURE 3. Output Error vs Settling Time (typical).

FIGURE 4. Full Scale Settling of DAC63 into 50Ω Load.

In order to achieve minimum settling time it is necessary to observe the following good high frequency construction techniques:

- The power supplies, including the logic threshold input (pin 22), should be bypassed by lμF CS-type tantalum capacitors.

- Use a ground plane to connect common ground points.

- Remove the ground plane from underneath signal lines where it would add capacitance.

- Separate analog and digital signal leads to avoid coupling of the digital signal into the analog paths.

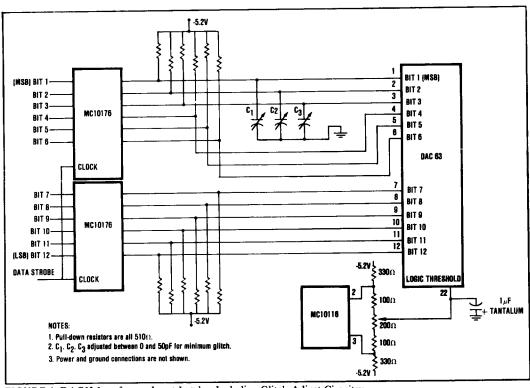

- 5. Bring the source of the digital driving signal as close to the inputs of the DAC63 as possible. If the digital inputs are not clean it will be necessary to reshape them using registers or line drivers. Figure 6 shows how to interface the DAC63 to an input register. It is recommended that the logic power line be bypassed near the digital logic circuitry as a further measure to achieve clean signals.

- If possible, the DAC63 should be soldered directly into the printed circuit board since connector lead length will cause ringing in the output.

#### **OUTPUT GLITCH**

"Glitch" is defined as the difference in the waveforms at the output of the DAC if there is data skew and if there is not. The measurement of glitch is accomplished by measuring the area between these two waveforms.

An output glitch of less than 250LSB-nsec is achievable with the DAC63 because it employs ECL circuitry with current switches that have virtually identical delay times for logic signals making either positive or negative transitions. A glitch results when the digital data changes from one code to the next and the bits do not all switch at the same time. The delay time between the earliest and latest switching bits is called skew time. Typically during the skew time of the digital data, which includes the DAC switching, the digital code is undefined and the DAC output can go to any voltage between the full scale extremes. The glitch creates a noisy output which can be troublesome in some applications such as precision displays and complex waveform generation. Figure 5 is a photograph of a scope trace of the DAC output with a glitch occurring at the major carry transition.

The DAC63 design has been optimized for low glitch energy. However, a further reduction in the output glitch can be achieved by adjusting the skew of the higher order bits of the driving circuitry and by adjusting the logic threshold. This can be done by connecting a variable capacitor from the data lines to ground on each of the first three significant bits (more than three lines may be adjusted if desired). Refer to Figure 6. It will be necessary to create a driving digital code pattern that causes a major carry transition around these bits. It is convenient to use a digital ramp from a counter for this purpose. Initially set the logic threshold exactly half-way between logic 1 and a logic 0. This will be about -1.3V. Then

FIGURE 5. Typical Glitch Repsonse of DAC63 at Major Carry Transition with a 1.6V Full Scale Range.

examine the major carry transition associated with bit 3 and adjust the capacitor for minimum glitch. Make the same adjustment to bit 2 and then to bit 1. If done in this order, interactions will be minimized. Finally, fine tune the response by adjusting the logic threshold voltage (pin 22) for minimum glitch. It may be necessary to repeat this procedure once or twice for complete optimization.

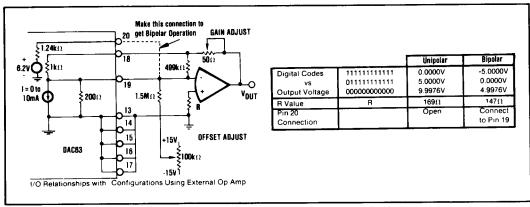

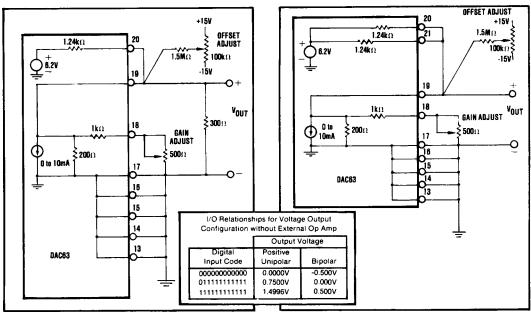

### OUTPUT CONFIGURATIONS AND APPLICATIONS INFORMATION

The DAC63 contains two 1.24k $\Omega$  resistors for generating the bipolar offset current and a  $lk\Omega$  resistor which is primarily used as the feedback resistor when used with an external op amp. This thin-film network is constructed on sapphire to provide excellent temperature tracking capability inherent in thin-film networks. These internal resistors along with other internal resistors cause the DAC63 output, in any mode, to be a ratiometric product of the reference. The feedback resistor has very low power sensitivity so that linearity is maintained independent of digital code changes. Because this resistor is constructed on a sapphire network, it is possible to have both superior tracking and low capacitance. Figure 7 shows the DAC63 connected to an external op amp in unipolar and bipolar modes. With the Burr-Brown model OPA600 it is possible to achieve settling times to  $\pm 0.01\%$ accuracy in 150nsec. Many of the output accuracy and linearity specifications are given when connected to an external op amp.

For highest speed operation, the DAC63 should be used without an external op amp. Figures 8 and 9 show how to connect the DAC63 for bipolar and positive unipolar

FIGURE 6. DAC63 Interface to Input Latches Including Glitch-Adjust Circuitry.

operation. Figure 10 illustrates how to connect the DAC63 to construct a fast A/D converter. The ADC attempts to create a null at the DAC output, so it is

possible to clamp the output voltage with a pair of diodes, thereby avoiding the negative compliance limit.

FIGURE 7. Bipolar and Unipolar Output Connections when Used with External Op Amp.

FIGURE 8. Bipolar Voltage Output Without External Op Amp.

FIGURE 9. Positive Unipolar Voltage Output Without External Op Amp.

FIGURE 10. DAC63 Used in a Fast A/D Converter.