# ZN527/ZN528

# **DUAL 8-BIT MICROPROCESSOR COMPATIBLE D-A CONVERTER**

The ZN527 and ZN528 are monolithic dual 8-bit DACs designed to be easily interfaced to microprocessors. Integrated on-chip are two 8-bit DAC's, separate VREF inputs and data latches for each DAC. A consequence of the two DAC's being fabricated on the same chip is excellent, inherent, DAC to DAC matching.

#### **FEATURES**

- 800ns Voltage Settling Time

- Monotonic over Full Temperature Range

- Single +5V Supply

- Excellent DAC to DAC Matching

- Separate VREF IN for each DAC

- Commercial and Military Temperature Ranges

#### ORDERING INFORMATION

| Device<br>type | Linearity<br>error (LSB) | Operating temperature | Package |

|----------------|--------------------------|-----------------------|---------|

| ZN527E         | ±1                       | -40°C to +85°C        | DP20    |

| ZN528E         | ±1/2                     | -40°C to +85°C        | DP20    |

| ZN527D         | ±1                       | -40°C to +85°C        | MP20    |

| ZN528D         | ±½                       | -40°C to +85°C        | MP20    |

| ZN527J         | ±1                       | -55°C to +125°C       | DC20    |

| ZN528J         | ±½                       | -55°C to +125°C       | DC20    |

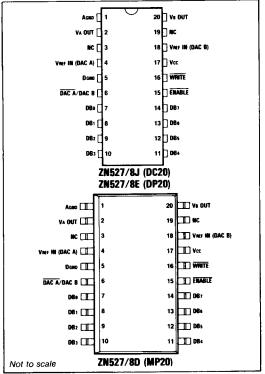

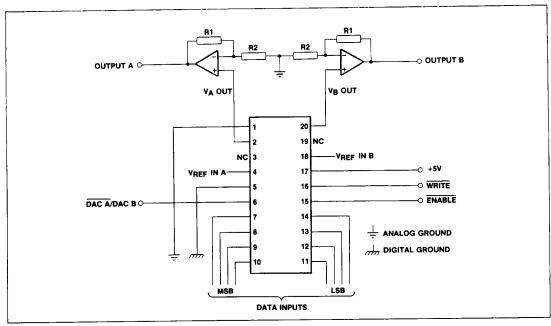

Pin connections - top view

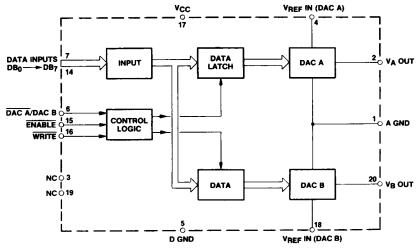

Fig.1 System diagram

# **ABSOLUTE MAXIMUM RATINGS**

Supply voltage Vcc Max. voltage, logic and VREF input

Operating temperture range

ZN527/8E and ZN527/8D

+Vcc-40°C to +85°C

+7V

ZN527/8J Storage temperature range Analog ground to digital ground -55°C to 125°C -55°C to 125°C  $\pm 200 mV$

# **ELECTRICAL CHARACTERISTICS**

Test conditions (unless otherwise stated):  $T_{amb} = 25 \, ^{\circ}\text{C}$

|                                                     | Value |         |       | Units        | Conditions                              |

|-----------------------------------------------------|-------|---------|-------|--------------|-----------------------------------------|

| Characteristic                                      | Min.  | Тур.    | Max.  | Units        | Conditions                              |

| ZN528                                               |       |         |       |              |                                         |

| Linearity error                                     |       |         | ±0.5  | LSB          |                                         |

| Differential linearity error                        |       | i       | ±0.75 | LSB          |                                         |

| ZN527                                               |       |         |       |              |                                         |

| Linearity error                                     |       | ļ       | ±1.0  | LSB          |                                         |

| Differential linearity error                        |       |         | ±0.75 | LSB          |                                         |

| All types                                           |       |         |       | 100          |                                         |

| Linearity error TC                                  |       | ±3      |       | ppm/°C       |                                         |

| Differential non-linearity TC                       |       | ±6      | _     | ppm/°C       | All bits OFF                            |

| Offset voltage                                      |       | 2<br>±3 | 5     | mV<br>ppm/°C | All bits OFF                            |

| Offset voltage TC                                   | 0.545 | 1       | 0.555 | 1 ' '        | Futornal reference                      |

| Full scale output                                   | 2.545 | 2.550   | 2.555 | V            | External reference<br>VREF IN = 2.560V, |

| Full scale output TC                                |       | 2       |       | ppm/°C       | all bits ON                             |

| •                                                   |       | 4       |       | kΩ           |                                         |

| Analog output resistance External reference voltage | 0     | 4       | 3.0   | V V          |                                         |

|                                                     |       | 800     | 0.0   | _            | 1 LSB major transition                  |

| Settling time to 0.5 LSB                            |       | 800     |       | ns           | (Note 1)                                |

|                                                     |       | 1.25    |       | μs           | All bits ON to OFF or                   |

|                                                     |       |         |       | ,            | OFF to ON (Note 1)                      |

| Operating temperature range:                        |       |         |       |              |                                         |

| ZN508E and ZN508D                                   | -40   |         | 85    | °C           |                                         |

| ZN508J                                              | -55   |         | 125   | °C           |                                         |

| Supply voltage (Vcc)                                | 4.5   | 5.0     | 5.5   | V            |                                         |

| Supply current                                      |       | 36      |       | mA           |                                         |

| Power consumption                                   |       | 180     |       | mW           |                                         |

| DC supply rejection                                 |       | -57     |       | dB           | $\Delta V cc = 250 \mu V p-p$           |

|                                                     |       | I       |       |              | f ≤ 50kHz                               |

| Digital to analog glitch impulse                    |       |         |       | nV-s         | 00000000 11111111                       |

| Channel to channel isolation                        |       |         |       |              |                                         |

| VREF A to Out B                                     |       | -82     |       | dB           | } f ≤ 50kHz                             |

| VREF B to Out A                                     |       | -82     |       | dB           | S I S DUNITZ                            |

| Internal voltage reference                          |       |         |       |              |                                         |

| Output voltage                                      |       | 2.5     |       | V            |                                         |

| Slope impedance                                     |       | 1       |       | Ω            |                                         |

| VREF OUT TC                                         |       | 50      |       | ppm/°C       |                                         |

| Reference current                                   | 1     | 1       | 15    | mA           |                                         |

| Logic                                               |       |         |       |              |                                         |

| (over specified operating temperature range)        |       |         |       | ,,           |                                         |

| High level input voltage V⊪                         | 2.0   |         | 0.0   | V            |                                         |

| Low level input voltage Vil.                        |       |         | 0.8   | V            |                                         |

| High level input current lin                        |       |         | 20    | μΑ           | $V_{IN} = 2.4, V_{CC} = 5.5V$           |

|                                                     |       |         | 320   | μΑ           | $V_{IN} = 5.5, V_{CC} = 5.5V$           |

| Low level input current IIL                         | 1     |         | -310  | μA           | $V_{IN} = 0.4V, V_{CC} = 5.5V$          |

| Oliver a April alla                  |      | Value |      |       | Conditions |

|--------------------------------------|------|-------|------|-------|------------|

| Characteristic                       | Min. | Тур.  | Max. | Units | Conditions |

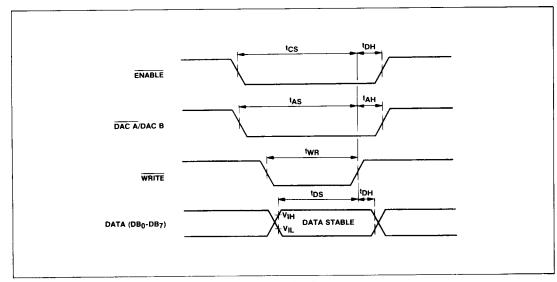

| Switching characteristics            |      |       |      |       |            |

| Chip select to write set up time tos | 150  |       |      | ns    |            |

| Chip select to write hold time, Tch  | 10   |       |      | ns    |            |

| DAC select to write set up time tas  | 150  |       |      | ns    |            |

| DAC select to write hold time tan    | 10   |       |      | ns    |            |

| Data valid to write set up time tos  | 100  |       |      | ns    |            |

| Data valid to write hold time ton    | 50   |       |      | ns    |            |

| Write pulse width twn                | 150  |       |      | ns    |            |

NOTE

1. RL = 10 Megohms CL = 10pF.

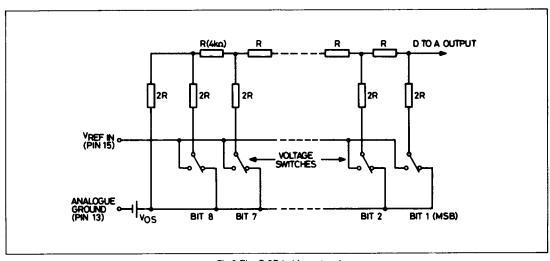

#### **D-A CONVERTER**

The converters are of the voltage switching type and use an R-2R ladder network as shown in Fig.2. Each 2R element is connected to 0V or VREF IN by transistor voltage switches specially designed for low offset voltage (<1mV). A binary weighted voltage is produced at the output of the R-2R ladder.

Analog output

$$=\frac{n}{256}$$

(VREF IN - Vos) + Vos

where n is the digital input to the D-A from the data latch. Vos is a small offset voltage produced by the D-A switch currents flowing through the package lead resistance. The value of Vos is typically 1mV. This offset will normally be removed by the setting up procedure (see Operating Notes) and because the offset temperature coefficient is low  $(\pm 6\mu V/^{\circ}C)$  the effect on accuracy is negligible.

Fig.2 The R-2R ladder network

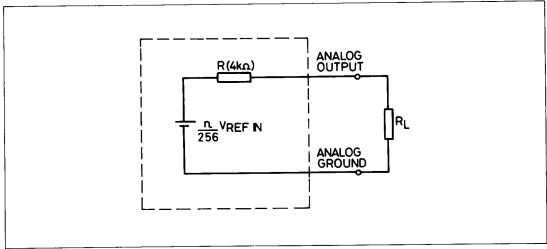

Fig.3 Analog output equivalent circuit

Fig.3 shows an equivalent circuit of the outputs (ignoring Vos). The output resistance R has a temperature coefficient of  $\pm 0.2\%$  per °C.

The gain drift due to this is  $\underbrace{0.2R}_{R + R_1}$  % per °C

$R_L$  should be chosen to be as large as possible to make the gain drift small. As an example if  $R_L=400k\Omega$  then the gain drift due to the TC of R for a  $100\,^{\circ}\mathrm{C}$  change in ambient temperature will be less than 0.2%. Alternatively the ZN527/8 outputs can be buffered by amplifiers (see Operating Notes).

#### REFERENCE

#### **External Reference**

Should an external reference voltage be connected to VREF IN, the slope resistance of such a reference source should be less than  $\frac{2.5\Omega}{1.00}$ , where n is the number of converters supplied.

$V_{\text{REF}}$  IN can be varied from 0 to  $\pm 3\text{V}$  for ratiometric operation. The ZN527/8 is guaranteed monotonic for VREF IN above 2V.

Fig.4 Logic timing diagram

#### LOGIC

Input coding is binary for unipolar operation and offset binary for bipolar operation. Both DAC A and DAC B share an internal data bus and an 8-bit input port. The DAC to be loaded with new data is chosen by DAC A/DAC B select pin; DAC A when the input is low and DAC B when the input is high. When ENABLE and WRITE are both low the DAC selected is in the write mode. The input data latches of the selected DAC are transparent and its analog output responds to the data presented to the input port. The data is then latched when either ENABLE or WRITE are taken high.

| DAC A/DAC B | CS | WR | DAC A | DAC B |

|-------------|----|----|-------|-------|

| L           | L  | L  | WRITE | HOLD  |

| н           | L  | L  | HOLD  | WRITE |

| Х           | Н  | x  | HOLD  | HOLD  |

| X           | x  | н  | HOLD  | HOLD  |

Table 1 Logic truth table

#### **OPERATING NOTES**

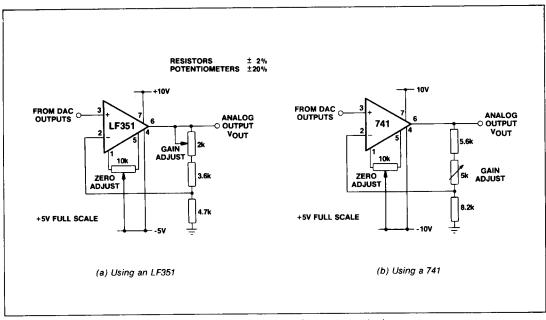

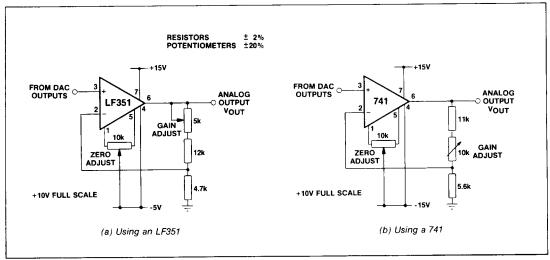

In some applications the standard 0 to VREF IN output voltage range and drive capability are not suitable, and other output ranges, both unipolar and bipolar are required.

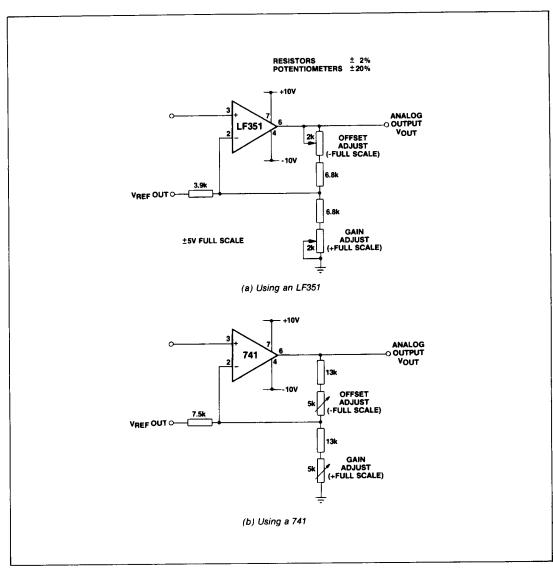

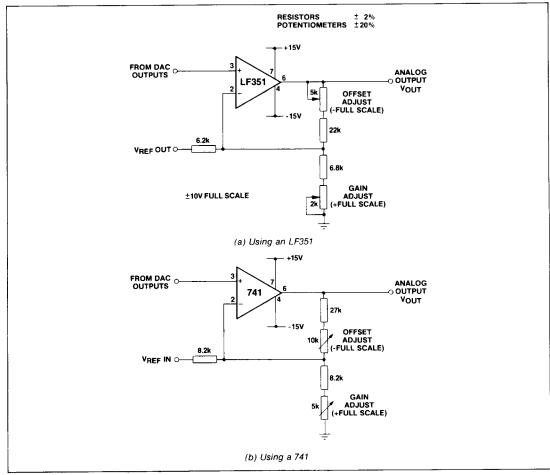

To maintain flexibility two types of operational amplifier are illustrated; the industry standard 741 and a low cost pincompatible alternative with a JFET input, the LF351. The LF351 features a high slew rate of  $13V/\mu s$ , which gives a faster potential settling time than the 741. To keep drift to a minimum when using the 741, the external range setting resistors are calculated to match them to the  $4k\Omega$  ladder output impedance. This is not a consideration with the LF351, as the input offset current change with temperature is negligible for the impedances concerned. The resistor values for the LF351 were chosen to keep the output ringing to a minimum; a problem sometimes encountered with high slew rate op-amps. It is only the relative and not the absolute values of these resistors which set the range, and therefore can be changed as long as their ratios remain the same.

#### **Unipolar Operation**

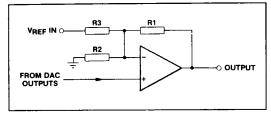

The general scheme for unipolar operation is shown in Fig.4 and is suitable for amplifiers with input bias currents less than 1.5µA.

The resulting full scale range is given by

Vout FS =

$$1 + \frac{R1}{R2}$$

(VREF IN - 1 LSB)

= G (VREF IN) - 1 LSB)

The impedance at the inverting input is R1/R2 and for low drift with temperature (741 only), this parallel combination should be equal to the ladder resistance (4k $\Omega$ ).

The required nominal values of R1 and R2 are therefore given by R1 =  $4Gk\Omega$  and R2 =  $4G/(G-1)k\Omega$ .

Using these relationships a table of nominal resistance values for R1 and R2 can be constructed for VREF IN = 2.5V (Table 2). For gain setting R1 is adjusted about its nominal value. Practical circuit realisations for +5V and +10V output ranges are given in Figs. 6 and 7.

| Output range | G | R1   | R2     |

|--------------|---|------|--------|

| +5V          | 2 | 8kΩ  | 8kΩ    |

| +10V         |   | 16kΩ | 5.33kΩ |

Table 2 Nominal values for R1 and R2

Fig.5 Unipolar operation - basic circuit

Fig.6 +5V full scale unipolar operation - component values

Fig.7 +10V full scale unipolar operation - component values

#### **Unipolar Adjustment Procedure**

- 1. Set all bits to OFF (low) with  $\overline{\text{ENABLE}}$  low and adjust zero until Vout = 0.0000V.

- 2. Set all bit ON (high) and adjust gain until  $V_{OUT} = FS 1 LSB$ .

| Output range, +FS | LSB    | FS - 1 LSB |                          |

|-------------------|--------|------------|--------------------------|

| + 5V              | 19.5mV | 4.9805V    | $1 LSB = \frac{FS}{256}$ |

| + 10V             | 39.1mV | 9.9609V    |                          |

Table 3 Unipolar setting up points

| Input code<br>(Binary) | Analog output (nominal value) |

|------------------------|-------------------------------|

| 11111111               | FS - 1 LSB                    |

| 11111110               | FS - 2 LSB                    |

| 11000000               | ¾ FS                          |

| 10000001               | ½ FS + 1 LSB                  |

| 10000000               | ½ FS                          |

| 01111111               | ½ FS - 1 LSB                  |

| 01000000               | 1/4 FS                        |

| 00000001               | 1 LSB                         |

| 00000000               | 0                             |

Table 4 Unipolar logic coding

Fig.8 Bipolar operation

#### **Bipolar Operation**

For bipolar operation the output from the ZN527/8 is offset by half full scale by connecting a resistor R3 between VREF IN and the inverting input of the buffer amplifier (Fig.8).

When the digital input to the ZN527/8 is zero the analog output is zero and the amplifier output should be – full scale. An input of all ones to the D-A will give a ZN527/8 output of VREF IN – 1 LSB and an amplifier output of + full scale. When using the 741, the parallel combination of R1, R2 and R3 should match the  $4k\Omega$  ladder resistance.

The nominal values of R1, R2 and R3 which meet these conditions are given by

R1 = 8Gk

$$\Omega$$

, R2 = 8G/(G-1)k $\Omega$  and R3 = 8k $\Omega$ ,

where the resultant output range is  $\pm G$  VREF IN.

A binary output range of  $\pm V_{REF}$  IN (which corresponds to the basic unipolar range 0 to  $V_{REF}$  IN) is obtained if R1 = R3 =  $8k\Omega$  and R2 =  $\infty$ .

Assuming that VREF IN = 2.5V the nominal values of resistors for  $\pm$ 5V and  $\pm$ 10V output ranges are given in Table 5.

| Output range | G | R1   | R2      | R3  |

|--------------|---|------|---------|-----|

| + 5V         | 2 | 16kΩ | 16kΩ    | 8kΩ |

| ± 10V        | 4 | 32kΩ | 10.66kΩ | 8kΩ |

Table 5

Minus full scale (offset) is set by adjusting R1 about its nominal value relative to R3. Plus full scale (gain) is set by adjusting R2 relative to R1.

Practical circuit realisations are given in Figs. 9 and 10. Note that in the  $\pm$ 5V case (741 only), R3 has been chosen as 7.5k $\Omega$  (instead of 8.2k $\Omega$ ) to give a more symmetrical range of adjustment using standard potentiometers.

Fig.9  $\pm 5V$  full scale bipolar operation - component values

Fig.10  $\pm$ 10V full scale bipolar operation - component values

# **Bipolar Adjustment Procedure**

- 1. Set all bits to OFF (low) with ENABLE low and adjust offset until the amplifier output reads full scale.

- 2. Set all bits ON (high) and adjust gain until the amplifier output reads  $\,+\,$  (full scale 1 LSB).

| Input range, $\pm$ FS | LSB              | -FS                   | +(FS - 1 LSB)        |                           |

|-----------------------|------------------|-----------------------|----------------------|---------------------------|

| ±5V<br>±10V           | 39.1mV<br>78.1mV | -5.0000V<br>-10.0000V | +4.9609V<br>+9.9219V | $1 LSB = \frac{2FS}{256}$ |

Table 6 Bipolar setting up points

| Input code (offset binary) | Analog output<br>(nominal value) |

|----------------------------|----------------------------------|

| 11111111                   | +(FS - 1 LSB)                    |

| 11111110                   | +(FS - 2 LSB)                    |

| 11000000                   | +1/2 FS                          |

| 10000001                   | +1 LSB                           |

| 10000000                   | 0                                |

| 01111111                   | -1 LSB                           |

| 01000000                   | -1⁄2 FS                          |

| 00000001                   | -(FS - 1 LSB)                    |

| 00000000                   | -FS                              |

Table 7 Bipolar logic coding