#### SPEED/PACKAGE AVAILABILITY

54 F,W 74 A,F 54H F,W 74H A,F 54LS F,W 74LS A,F

## **DESCRIPTION**

This monolithic edge-triggered dual J-K flip-flop features individual J, K, clock, and clear inputs to each flip-flop. A low logic level at the clear input resets the Q output to a low level regardless of the levels at the other inputs. With clear inactive (high), a high level at the clock input enables the J and K inputs and data will be accepted. The logic levels at the J and K inputs may be allowed to change when the clock pulse is high and the bistable will perform according to the function table, as long as minimum setup and hold times are observed. Input data is transferred to the outputs on the negative-going edge of the clock pulse.

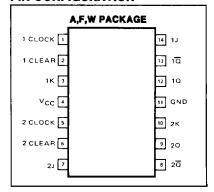

#### **PIN CONFIGURATION**

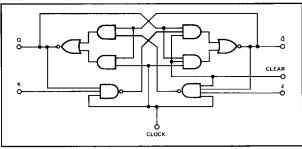

## **LOGIC DIAGRAM**

## FUNCTION TABLE (Each Flip-Flop)

| 54/74, 54/74H |        |         |   |                |                  |  |  |  |

|---------------|--------|---------|---|----------------|------------------|--|--|--|

|               | INPUTS | OUTPUTS |   |                |                  |  |  |  |

| CLEAR         | CLOCK  | J       | K | q              | ō                |  |  |  |

| L             | х      | х       | х | L              | Н                |  |  |  |

| Н             | ~~     | L       | L | Q <sub>0</sub> | $\overline{Q}_0$ |  |  |  |

| н             |        | Н       | L | ΗĬ             | Ľ                |  |  |  |

| H             |        | L       | Н | L              | Н                |  |  |  |

| Н             | ~~     | Н       | Н | TOG            | GLE              |  |  |  |

| 54/74L\$73 |        |         |    |                |                  |  |  |  |

|------------|--------|---------|----|----------------|------------------|--|--|--|

|            | INPUTS | OUTPUTS |    |                |                  |  |  |  |

| CLEAR      | CLOCK  | J       | ,K | a              | Q                |  |  |  |

| L          | Х      | Х       | Х  | L              | н                |  |  |  |

| Н          | ţ      | L       | L  | Q <sub>O</sub> | ō₀<br>L          |  |  |  |

| н          | ļ      | Н       | L  | Ηĭ             | Ľ                |  |  |  |

| н          | ļ      | L       | н  | L              | Н                |  |  |  |

| Н          | ļ      | Н       | Н  | TOG            | GLE              |  |  |  |

| Н          | Н      | X       | Х  | Qo             | $\overline{Q}_0$ |  |  |  |

- H ~ high level (steady state)

- L = low level (steady state)

- X = irrelevant

- transition from high to low level

- Q<sub>0</sub> = the level of Q before the indicated input conditions were established.

TOGGLE: Each output changes to the complement of its previous level on each ↓ clock tran-

TOGGLE: Each output changes to the complement of its previous level on each ‡ clock transition.

# SWITCHING CHARACTERISTICS V<sub>CC</sub> = 5V, T<sub>A</sub> = 25°C

|                       |                                                          |               |                                              | 54/74    |                                              |     | 54/74H                                      |     | 54/74LS |     |     |     |      |

|-----------------------|----------------------------------------------------------|---------------|----------------------------------------------|----------|----------------------------------------------|-----|---------------------------------------------|-----|---------|-----|-----|-----|------|

| TEST CONDITIONS       |                                                          |               | C <sub>L</sub> =15pF<br>R <sub>L</sub> =400Ω |          | C <sub>L</sub> =25pF<br>R <sub>L</sub> =280Ω |     | C <sub>L</sub> =15pF<br>R <sub>L</sub> =2kΩ |     |         |     |     |     |      |

| PARAMETE              | ir.                                                      | FROM<br>INPUT | TO<br>OUTPUT                                 | MIN      | ТҮР                                          | MAX | MIN                                         | TYP | MAX     | MIN | ТҮР | MAX | UNIT |

| fClock .              | Clock frequency                                          |               |                                              | 15       | 20                                           |     | 25                                          | 30  |         | 30  | 45  |     | MHz  |

| <sup>t</sup> w(Clock) | Width of clock<br>input pulse<br>Clock high<br>Clock low |               |                                              | 20<br>47 |                                              |     | 12<br>28                                    |     |         | 20  |     |     | ns   |

| <sup>t</sup> w(Clear) | Width of clear input pulse                               |               |                                              | 25       |                                              |     | 16                                          |     |         | 25  |     |     | ns   |

| <sup>t</sup> Setup    | Input setup time                                         |               |                                              | 01       |                                              |     | of                                          |     |         | 20  | İ   |     | ns   |

| tHold                 | Input hold time                                          |               |                                              | l ot     |                                              |     | l ot                                        |     |         | 0   |     |     | ns   |

| Propagation tPLH      | n delay time<br>Low-to-high                              | Clear         |                                              |          | 16                                           | 25  |                                             | 6   | 13      |     | 11  | 20  | ns   |

| <sup>t</sup> PHL      | High-to-low                                              |               |                                              |          | 25                                           | 40  |                                             | 12  | 24      |     | 15  | 30  | ns   |

| t <sub>PLH</sub>      | Low-to-high                                              | Cłock         |                                              | 10       | 16                                           | 25  |                                             | 16  | 21      |     | 11  | 20  | ns   |

| <b>tPHL</b>           | High-to-low                                              |               |                                              | 10       | 25                                           | 40  |                                             | 22  | 27      |     | 15  | 30  | ns   |

Load circuit and typical waveforms are shown at the front of section.