#### 4 Megabit Static RAM Module 512K x 8-Bit

#### **Features**

- ☐ High-speed access times Com'l: 20, 25, and 35 ns Ind'l: 25, and 35 ns

- ☐ High density 4-megabit SRAM module

- ☐ JEDEC approved pinout

- □ Single +5V (±10%) power supply

- ☐ TTL compatible inputs and outputs

- ☐ Packages CerDIP (600 mil) - D

### **Description**

The PDM4M096 is a high-performance CMOS static RAM module organized as 524,288 x 8 bits. This product is produced in Paradigm's proprietary CMOS technology which offers the designer the highest speed parts. Writing to this device is accomplished when the write enable (WE) and the chip enable (CE) inputs are both LOW. Reading is accomplished when WE remains HIGH and CE and OE are both LOW.

The PDM4M096 operates from a single +5V power supply and all the inputs and outputs are fully TTL compatible. The PDM4M096 comes in two versions, the standard power version PDM4M096S and a low power version the PDM4M096L. The two versions are functionally the same and only differ in their power consumption.

The PDM4M096 is available in a 32-pin 600 mil DIP.

### **Functional Block Diagram**

#### I/O<sub>0-7</sub> 128K x 8 128K x 8 SRAM SRAM WE CE CE ŌĒ 128K x B 128K x 8 SRAM SRAM CE 1 CE DECODER CE

#### Note: Decoder is not required for higher speed versions.

## Pin Configuration

### Truth Table<sup>(1)</sup>

| ŌE | WE | CE | VO               | MODE           |

|----|----|----|------------------|----------------|

| Х  | Х  | Н  | Hi-Z             | Standby        |

| L  | Н  | L  | D <sub>OUT</sub> | Read           |

| Х  | L  | L  | D <sub>IN</sub>  | Write          |

| Н  | Н  | L  | Hi-Z             | Output Disable |

NOTE: 1. H = V<sub>IH</sub>, L = V<sub>IL</sub>, X = DON'T CARE

## Absolute Maximum Ratings<sup>(1)</sup>

| Symbol            | Rating                               | Com'l.       | Ind.         | Unit |

|-------------------|--------------------------------------|--------------|--------------|------|

| V <sub>TERM</sub> | Terminal Voltage with Respect to GND | -0.5 to +7.0 | -0.5 to +7.0 | V    |

| TBIAS             | Temperature Under Bias               | -55 to +125  | -65 to +135  | °C   |

| T <sub>STG</sub>  | Storage Temperature                  | -55 to +125  | -65 to +150  | °C   |

| P <sub>T</sub>    | Power Dissipation                    | 1.0          | 1.0          | W    |

| lout              | DC Output Current                    | 50           | 50           | mA   |

NOTE: 1. Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

### **Recommended DC Operating Conditions**

| Symbol          | Parameter           | Min. | Тур. | Max. | Unit |

|-----------------|---------------------|------|------|------|------|

| V <sub>CC</sub> | Supply Voltage      | 4.75 | 5.0  | 5.25 | ٧    |

| GND             | Supply Voltage      | 0    | 0    | 0    | V    |

| Industrial      | Ambient Temperature | -40  | 25   | 85   | °C   |

| Commercial      | Ambient Temperature | 0    | 25   | 70   | °C   |

### DC Electrical Characteristics ( $V_{CC} = 5.0V \pm 5\%$ )

|                 |                        |                                                                                                  |                 | PDM4                | IM096      | PDM4                | Unit       |    |

|-----------------|------------------------|--------------------------------------------------------------------------------------------------|-----------------|---------------------|------------|---------------------|------------|----|

| Symbol          | Parameter              | Test Conditions                                                                                  | Test Conditions |                     |            | Min.                | Max.       |    |

| I <sub>LI</sub> | Input Leakage Current  | V <sub>CC</sub> = MAX., V <sub>IN</sub> = GND to V <sub>CC</sub>                                 | Com'i           | -5                  | 5          | -2                  | 2          | μА |

| l <sub>LO</sub> | Output Leakage Current | $V_{CC}$ = MAX., $V_{OUT}$ = GND to $V_{CC}$<br>$\overline{CE}$ = $V_{IH}$ , or $CE2$ = $V_{IL}$ | Com'i           | <b>-</b> 5          | 5          | -2                  | 2          | μА |

| V <sub>OL</sub> | Output Low Voltage     | $I_{OL}$ = 8 mA, $V_{CC}$ = Min.<br>$I_{OL}$ = 10 mA, $V_{CC}$ = Min.                            |                 | <u>-</u>            | 0.4<br>0.5 | _                   | 0.4<br>0.5 | V  |

| V <sub>OH</sub> | Output High Voltage    | $I_{OH} = -4 \text{ mA}, V_{CC} = \text{Min}.$                                                   |                 | 2.4                 | _          | 2.4                 |            | V  |

| V <sub>IH</sub> | Input High Voltage     |                                                                                                  |                 | 2.2                 | 6.0        | 2.2                 | 6.0        | V  |

| V <sub>IL</sub> | Input Low Voltage      |                                                                                                  |                 | -0.5 <sup>(1)</sup> | 0.8        | -0.5 <sup>(1)</sup> | 0.8        | ν  |

NOTE: 1.  $V_{IL}(min) = -3.0V$  for pulse width less than 20 ns.

### Power Supply Characteristics ( $V_{CC} = 5.0V \pm 10\%$ )

|                  |                                                                                                                                                             |       |               | -20        |            | -25        |            | -35        |            | П    |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------------|------------|------------|------------|------------|------------|------------|------|--|

| Symbol           | Parameter                                                                                                                                                   | Power | Function      | Com'i.     | Ind.       | Com'l.     | Ind.       | Com'l.     | Ind.       | Unit |  |

| lcc              | Operating Current CE = V <sub>IL</sub> , V <sub>CC</sub> = Max.,                                                                                            | s     | Read<br>Write | 380<br>380 | 420<br>420 | 340<br>340 | 380<br>380 | 300<br>300 | 340<br>340 | mA   |  |

|                  | $f = f_{MAX}^{(2)}$                                                                                                                                         | L     | Read<br>Write | 380<br>380 | 420<br>420 | 340<br>340 | 380<br>380 | 300<br>300 | 340<br>340 | mA   |  |

| I <sub>SB</sub>  | Standby<br>Current (TTL Level)                                                                                                                              | s     |               | 160        | 160        | 150        | 150        | 140        | 140        | mA   |  |

|                  | $\overline{CE} \ge V_{IH}$ , $V_{CC} = Max.$ ,<br>$f = f_{MAX} = 1/trc$ ,                                                                                   | L     |               | 150        | 150        | 140        | 140        | 130        | 130        | mA   |  |

| I <sub>SB1</sub> | Full Standby<br>Current (CMOS Level)                                                                                                                        | s     |               | 40         | 40         | 40         | 40         | 40         | 40         | mA   |  |

|                  | $\label{eq:continuous} \begin{split} \overline{CE} &\geq V_{HC}, \\ V_{CC} &= Max., f = 0, \\ V_{IN} &\geq V_{CC} - 0.2V \text{ or } \leq 0.2V \end{split}$ | L     |               | 20         | 20         | 20         | 20         | 20         | 20         | mA   |  |

NOTE:All Values are maximum guaranteed values.  $V_{LC} \leq 0.2 V, \, V_{HC} \geq 0.2 V$

# Capacitance<sup>(1)</sup> $(T_A = +25^{\circ}C, f = 1.0 \text{ MHz})$

| Symbol           | Parameter          | Max. | Unit |

|------------------|--------------------|------|------|

| C <sub>IN</sub>  | Input Capacitance  | 50   | рF   |

| C <sub>OUT</sub> | Output Capacitance | 50   | pF   |

NOTE: 1. This parameter is determined by device characterization but is not production tested.

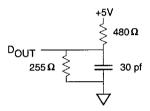

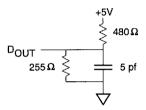

#### **AC Test Conditions**

| Input Pulse Levels            | GND to 3.0V         |

|-------------------------------|---------------------|

| Input Rise and Fall Times     | 5 ns                |

| Input Timing Reference Levels | 1.5V                |

| Output Reference Levels       | 1.5V                |

| Output Load                   | See Figures 1 and 2 |

Figure 1. Output Load Equivalent

Figure 2. Output Load Equivalent (for t<sub>LZCE</sub>, t<sub>HZCE</sub>, t<sub>LZWE</sub>, t<sub>HZWE</sub>, t<sub>LZOE</sub>, t<sub>HZOE</sub>)

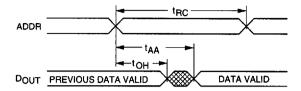

# Read Cycle No. 1<sup>(5, 6)</sup>

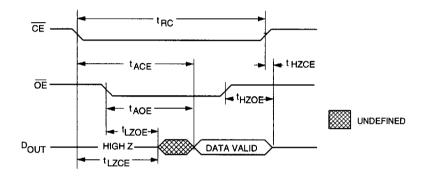

# Read Cycle No. 2<sup>(3, 5, 7)</sup>

### AC Electrical Characteristics ( $V_{CC} = 5V \pm 10\%$ , All Temperature Ranges)

|                   | Description                                           | -20  |      | -25  |      | -35  |      |       |  |

|-------------------|-------------------------------------------------------|------|------|------|------|------|------|-------|--|

| Symbol            | READ Cycle                                            | Min. | Max. | Min. | Max. | Min. | Max. | Units |  |

| t <sub>RC</sub>   | READ Cycle time                                       | 20   |      | 25   |      | 35   |      | пѕ    |  |

| t <sub>AA</sub>   | Address Access Time                                   |      | 20   |      | 25   |      | 35   | ns    |  |

| t <sub>ACE</sub>  | Chip enable Access Time                               |      | 20   |      | 25   |      | 35   | ns    |  |

| t <sub>OH</sub>   | Output Hold from Address Change                       | 3    |      | 3    |      | 3    |      | ns    |  |

| tLZCE             | Chip Enable to Output in Low-Z <sup>(4)</sup>         | 0    |      | 0    |      | 0    |      | ns    |  |

| t <sub>HZCE</sub> | Chip Disable to Output in High-Z <sup>(2, 3, 4)</sup> |      | 10   |      | 15   |      | 20   | ns    |  |

| t <sub>PU</sub>   | Chip Enable to Power Up Time <sup>(4)</sup>           | 0    |      | 0    |      | 0    |      | ns    |  |

| t <sub>PD</sub>   | Chip Disable to Power Down Time <sup>(4)</sup>        |      | 20   |      | 25   |      | 30   | ns    |  |

| t <sub>AOE</sub>  | Output Enable Access Time                             |      | 10   |      | 12   |      | 15   | ns    |  |

| t <sub>LZOE</sub> | Output Enable to Output in Low-Z(4)                   | 0    |      | 0    |      | 0    |      | ns    |  |

| t <sub>HZOE</sub> | Output Disable to Output in High- $Z^{(2, 3, 4)}$     |      | 8    |      | 10   |      | 20   | ns    |  |

Note: Reference page 6 for all notes on this page.

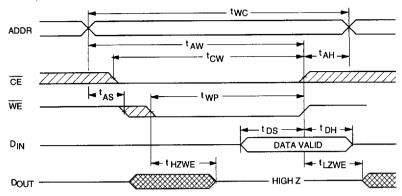

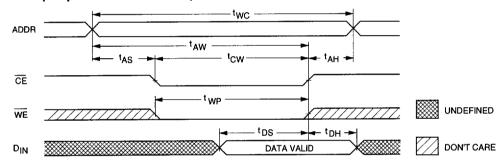

# Write Cycle No. 1 (Write Enable Controlled)

### Write Cycle No. 2 (Chip Enable Controlled)

AC Electrical Characteristics ( $V_{CC} = 5V \pm 10\%$ , All Temperature Ranges)

| Description                                           |                 | -20  |          | -25  |      | -35  |      |       |  |

|-------------------------------------------------------|-----------------|------|----------|------|------|------|------|-------|--|

| WRITE Cycle                                           | Symbol          | Min. | Max.     | Min. | Max. | Min. | Max. | Units |  |

| WRITE Cycle time                                      | twc             | 20   |          | 25   |      | 35   |      | ns    |  |

| Chip enable to end of write                           | t <sub>CW</sub> | 17   |          | 20   |      | 30   |      | ns    |  |

| Address Valid to end of write                         | t <sub>AW</sub> | 17   |          | 20   | ļ    | 30   |      | ns    |  |

| Address setup time                                    | t <sub>AS</sub> | 0    |          | 0    |      | 10   |      | ns    |  |

| Address hold from end of write (8)                    | t <sub>AH</sub> | 0    |          | 0    |      | 0    |      | ns    |  |

| Write pulse width                                     | twp             | 17   |          | 17   |      | 20   |      | ns    |  |

| Data setup time                                       | t <sub>DS</sub> | 12   | <u> </u> | 12   |      | 15   |      | ns    |  |

| Data hold time <sup>(8)</sup>                         | t <sub>DH</sub> | 0    |          | 0    |      | 0    |      | ns    |  |

| Write disable to output in Low-Z <sup>(4)</sup>       | tLZWE           | 0    |          | 0    |      | 0    |      | ns    |  |

| Write enable to output in High-Z <sup>(2, 3, 4)</sup> | tHZWE           |      | 8        |      | 10   |      | 15   | ns    |  |

Note: Reference page 6 for all notes on this page.

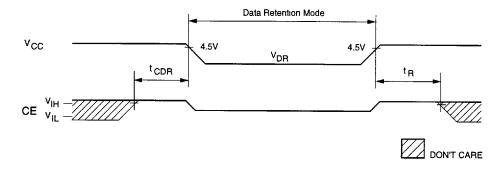

### Low V<sub>CC</sub> Data Retention Waveform

### **Data Retention Electrical Characteristics (L Version Only)**

| Symbol                        | Parameter                            | Test Conditions                                                 |                      |                     | Тур. | Max. | Unit |

|-------------------------------|--------------------------------------|-----------------------------------------------------------------|----------------------|---------------------|------|------|------|

| $V_{DR}$                      | V <sub>CC</sub> for Retention Data   |                                                                 | 2                    | _                   |      | V    |      |

| ICCDR                         | Data Retention Current               | $ \overline{CE} \ge V_{CC} - 0.2V \\ V_{IN} \ge V_{CC} - 0.2V $ | V <sub>CC</sub> = 2V | -                   | .380 | 2    | mA   |

|                               |                                      | $V_{\text{IN}} \ge V_{\text{CC}} - 0.2V$ or $\le 0.2V$          | V <sub>CC</sub> = 3V | _                   | 1.4  | 3    | mA   |

| t <sub>CDR</sub>              | Chip Deselect to Data Retention Time |                                                                 |                      | 0                   | _    | _    | ns   |

| t <sub>R</sub> <sup>(4)</sup> | Operation Recovery Time              |                                                                 |                      | t <sub>RC</sub> (5) |      | _    | ns   |

NOTES: (For 3 previous Electrical Characteristics tables)

- 1. -55°C to +125°C temperature range only.

- t<sub>HZCE</sub> and t<sub>HZWE</sub> aretested with CL = 5 pF as shown in Fig. #2. Transition is measured ±200 mV from steady state voltage.

- 3. At any given temperature and voltage condition,  $t_{\mbox{HZCE}}$  is less than  $t_{\mbox{LZCE}}$ .

- 4. This parameter is sampled.

- 5. WE is high for a READ cycle.

- 6. The device is continuously selected. All the Chip Enables are held in their active state.

- 7. The address is valid prior to or coincident with the latest occuring Chip Enable.

- 8. During chip enable controlled write cycle t<sub>DH</sub> and t<sub>AH</sub> equal 5 ns (min).

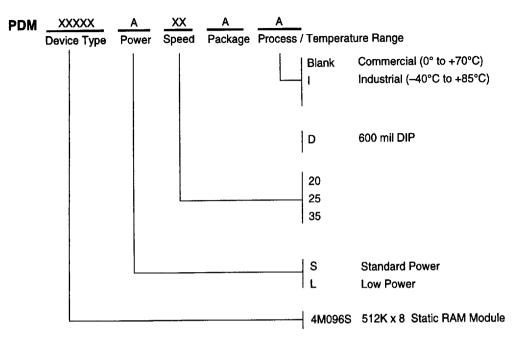

#### **Ordering Information**

Chip PDM4M096 Package Type

32-pin CerDIP 600 Mil

#### **Advanced Packaging**

Advances in packaging techniques permit a wide variety of solutions to board space problems.

Modules are comprised of individual semiconductor devises with other support devises, such as decoders and capacitors as required, mounted on a multilayer substrate. The substrate is custom designed to provide appropriate circuitry for the components in a package configuration that meets thermal and mechanical design objectives in a minimal amount of board real estate. The final module may have a through-hole pin configuration or may be surface mountable device.

Commercial modules are generally developed using components encapsulated in plastic, surface mounted on FR4 epoxy laminate substrates. The surface mountable component packages may be SOJ, SOIC, VSOP, TSOP, or QFP styles.

Ceramic packaging may be used for devices that need to be hermetic or require extended temperature range performance, such as military applications. Ceramic modules may use LCC or CSOJ component packaging on ceramic substrates with sidebrazed lead attach, or may use multiple die bonded in an MCM-C package.

#### Module Package Styles

Many module package styles are available from Paradigm. Features and relative board space are described here.

#### SIP

Vertically mounted, the SIP (Single In-line Package) contains a single row of pins along on edge for through-hole assembly. Pins are on a 100-mil pitch. Components may be mounted on both sides of the substrate. The device is most commonly constructed using plastic encapsulated components on an FR4 substrate, but it may be constructed of ceramic, as well. The vertical orientation and the ability to mount components on both sides of the substrate adds up to exceptional density.

#### ZIP

ZIP (Zig-zag In-line Package) is similar in space savings to the SIP, since both feature vertical substrate configurations. They also feature the additional advantages of larger pin counts with the structural stability of two rows of pins. Pins are placed on a 100-mil pitch, with 100-mil spacing between the rows.

#### **SIMM**

The SIMM (Single In-line Memory Module) package is similar to the SIP. The major difference is, rather than a single row of pins, the bottom edge has a row of connector contacts that are designed to plug into a socket mounted on the motherboard. Spacing between contacts is either 50- or 100-mil pitch. Since socket mounted SIMMs may be changed easily, they offer greater system flexibility by allowing multiple densities and speed grades.

#### CELP/DIMM

Like the SIMM, the DIMM (Dual readout In-line Memory Module) is socket mounted, but its dual readout contains larger pinouts for extremely high density in a compact component.

#### DIP

DIP (Dual In-line Package) modules offer a low profile with excellent mechanical ruggedness. Historically, DIP modules have provided the same form, fit, and function as future generation memory devices. Ceramic DIP modules have also been the preferred package for military applications.

#### PCA

The PGA (Pin Grid Array) has an array of pins arranged in a matrix on a 100-mil grid. This ceramic package style provides a large pin count in a smaller area than possible in package styles with pins only on the package edge or perimeter. With its large number of through-hole contract points, it offers exceptional structural integrity. This package style is also commonly used for multichip arrays bonded within a single cavity.