SCDS018I - MAY 1995 - REVISED MAY 1998

- **Functionally Equivalent to QS3253**

- 5- $\Omega$  Switch Connection Between Two Ports

- **TTL-Compatible Input Levels**

- **Package Options Include Plastic** Small-Outline (D), Shrink Small-Outline (DB, DBQ), Thin Very Small-Outline (DGV), and Thin Shrink Small-Outline (PW) **Packages**

## description

The SN74CBT3253 is a dual 1-of-4 high-speed TTL-compatible FET multiplexer/demultiplexer. The low on-state resistance of the switch allows connections to be made with minimal propagation delay.

1<del>OE</del>, 2<del>OE</del>, S0, and S1 select the appropriate B output for the A-input data.

The SN74CBT3253 is characterized for operation from -40°C to 85°C.

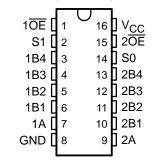

### D, DB, DBQ, DGV, OR PW PACKAGE (TOP VIEW)

### **FUNCTION TABLE** (each multiplexer/demultiplexer)

| INPUTS |    |    | FUNCTION         |  |  |

|--------|----|----|------------------|--|--|

| OE     | S1 | S0 | FUNCTION         |  |  |

| L      | L  | L  | A port = B1 port |  |  |

| L      | L  | Н  | A port = B2 port |  |  |

| L      | Н  | L  | A port = B3 port |  |  |

| L      | Н  | Н  | A port = B4 port |  |  |

| Н      | Χ  | Χ  | Disconnect       |  |  |

SCDS018I - MAY 1995 - REVISED MAY 1998

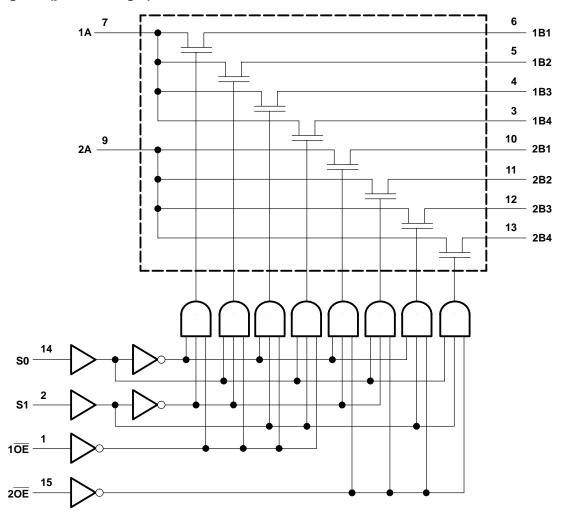

## logic diagram (positive logic)

## absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

| Supply voltage range, V <sub>CC</sub>                   |              | –0.5 V to 7 V  |

|---------------------------------------------------------|--------------|----------------|

| Input voltage range, V <sub>I</sub> (see Note 1)        |              | –0.5 V to 7 V  |

| Continuous channel current                              |              | 128 mA         |

| Input clamp current, $I_K (V_{I/O} < 0)$                |              | –50 mA         |

| Package thermal impedance, θ <sub>JA</sub> (see Note 2) | ): D package | 113°C/W        |

| •                                                       | DB package   | 131°C/W        |

|                                                         | DBQ package  | 139°C/W        |

|                                                         | DGV package  | 180°C/W        |

|                                                         | PW package   | 149°C/W        |

| Storage temperature range, T <sub>sta</sub>             |              | -65°C to 150°C |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. The input and output negative-voltage ratings may be exceeded if the input and output clamp-current ratings are observed.

<sup>2.</sup> The package thermal impedance is calculated in accordance with JESD 51.

SCDS018I - MAY 1995 - REVISED MAY 1998

## recommended operating conditions (see Note 3)

|                 |                                  | MIN | MAX | UNIT |

|-----------------|----------------------------------|-----|-----|------|

| VCC             | Supply voltage                   | 4   | 5.5 | V    |

| VIH             | High-level control input voltage | 2   |     | V    |

| V <sub>IL</sub> | Low-level control input voltage  |     | 0.8 | V    |

| TA              | Operating free-air temperature   | -40 | 85  | °C   |

NOTE 3: All unused control inputs of the device must be held at V<sub>CC</sub> or GND to ensure proper device operation. Refer to the TI application report, Implications of Slow or Floating CMOS Inputs, literature number SCBA004.

# electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

| PARAMETER TEST CONDITIONS |                | ONS                                                      | MIN                          | TYP <sup>†</sup>                       | MAX | UNIT |      |    |

|---------------------------|----------------|----------------------------------------------------------|------------------------------|----------------------------------------|-----|------|------|----|

| VIK                       |                | $V_{CC} = 4.5 \text{ V},$                                | I <sub>I</sub> = -18 mA      |                                        |     |      | -1.2 | V  |

| I                         |                | $V_{CC} = 5 V$ ,                                         | $V_I = 5.5 \text{ V or GND}$ |                                        |     |      | ±1   | μΑ |

| Icc                       |                | $V_{CC} = 5.5 \text{ V},$                                | $I_{O} = 0$ ,                | $V_I = V_{CC}$ or GND                  |     |      | 3    | μΑ |

| ∆lcc <sup>‡</sup>         | Control inputs | $V_{CC} = 5.5 \text{ V},$                                | One input at 3.4 V,          | Other inputs at V <sub>CC</sub> or GND |     |      | 2.5  | mA |

| Ci                        | Control inputs | V <sub>I</sub> = 3 V or 0                                |                              |                                        |     | 3.5  |      | pF |

| C <sub>io(OFF)</sub>      | A port         | $V_0 = 3 \text{ V or } 0,$                               | <del>0</del>                 |                                        |     | 10   |      | pF |

|                           | B port         | ν <sub>O</sub> = 3 ν οι ο,                               | OE = V <sub>CC</sub>         |                                        |     | 4    |      | ρг |

| r <sub>on</sub> §         |                | $V_{CC} = 4 \text{ V},$<br>TYP at $V_{CC} = 4 \text{ V}$ | V <sub>I</sub> = 2.4 V,      | I <sub>I</sub> = 15 mA                 |     |      |      |    |

|                           |                | V <sub>CC</sub> = 4.5 V                                  | V <sub>I</sub> = 0           | I <sub>I</sub> = 64 mA                 |     | 5    | 7    | Ω  |

|                           |                |                                                          |                              | I <sub>I</sub> = 30 mA                 |     | 5    | 7    |    |

|                           |                |                                                          | V <sub>I</sub> = 2.4 V,      | I <sub>I</sub> = 15 mA                 |     | 10   | 15   |    |

<sup>&</sup>lt;sup>†</sup> All typical values are at  $V_{CC} = 5 \text{ V}$  (unless otherwise noted),  $T_A = 25^{\circ}\text{C}$ .

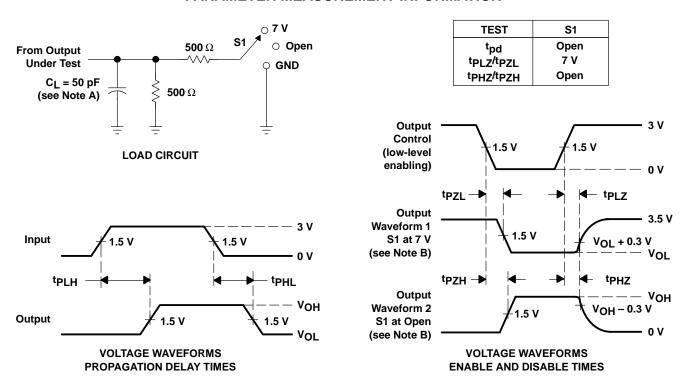

# switching characteristics over recommended operating free-air temperature range, $C_L = 50 \text{ pF}$ (unless otherwise noted) (see Figure 1)

| PARAMETER        | FROM<br>(INPUT) | TO<br>(OUTPUT) | V <sub>CC</sub> = 4 V |      | V <sub>CC</sub> = 5 V<br>± 0.5 V |      | UNIT |

|------------------|-----------------|----------------|-----------------------|------|----------------------------------|------|------|

|                  | (1141 01)       |                | MIN                   | MAX  | MIN                              | MAX  |      |

| $t_{pd}\P$       | A or B          | B or A         |                       | 0.35 |                                  | 0.25 | ns   |

| <sup>t</sup> pd  | S               | A or B         |                       | 6.6  | 1.6                              | 6.2  | ns   |

|                  | S               | A or B         |                       | 7.1  | 1.3                              | 6.3  | 20   |

| <sup>t</sup> en  | ŌĒ              | AUID           |                       | 7.3  | 1.4                              | 6.4  | ns   |

| 4                | S               | A or D         |                       | 7.9  | 1.1                              | 7.4  | - ns |

| <sup>t</sup> dis | ŌĒ              | A or B         |                       | 7.3  | 2.3                              | 7    |      |

The propagation delay is the calculated RC time constant of the typical on-state resistance of the switch and the specified load capacitance, when driven by an ideal voltage source (zero output impedance).

<sup>&</sup>lt;sup>‡</sup> This is the increase in supply current for each input that is at the specified TTL voltage level rather than V<sub>CC</sub> or GND.

<sup>§</sup> Measured by the voltage drop between the A and the B terminals at the indicated current through the switch. On-state resistance is determined by the lower voltage of the two (A or B) terminals.

#### PARAMETER MEASUREMENT INFORMATION

- NOTES: A. C<sub>L</sub> includes probe and jig capacitance.

- B. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

- C. All input pulses are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz,  $Z_Q = 50 \Omega$ ,  $t_f \leq$  2.5 ns,  $t_f \leq$  2.5 ns.

- D. The outputs are measured one at a time with one transition per measurement.

- E. tpLZ and tpHZ are the same as tdis.

- F.  $t_{PZL}$  and  $t_{PZH}$  are the same as  $t_{en}$ .

- G. tplH and tpHL are the same as tpd.

Figure 1. Load Circuit and Voltage Waveforms