# **CD74LPT543**

December 1996

### Fast CMOS 3.3V 8-Bit Latched Transceiver

### Features

- Advanced 0.6 micron CMOS Technology

- Compatible with LCX™ Families of Products

- Supports 5V Tolerant Mixed Signal Mode Operation

- Input Can Be 3V or 5V

- Output Can Be 3V or Connected to 5V Bus

- · Advanced Low Power CMOS Operation

- Active Bus-Hold Circuitry

- . Excellent Output Drive Capability:

- Balanced Drives (24mA Sink and Source)

- Low Ground Bounce Outputs

- · Hysteresis on All Inputs

### Ordering Information

| PART NUMBER   | TEMP.<br>RANGE<br>(°C) | PACKAGE    | PKG.<br>NO. |

|---------------|------------------------|------------|-------------|

| CD74LPT543AM  | -40 to 85              | 24 Ld SOIC | M24.3-P     |

| CD74LPT543AQM | -40 to 85              | 24 Ld QSOP | M24.15-P    |

| CD74LPT543CM  | -40 to 85              | 24 Ld SOIC | M24.3-P     |

| CD74LPT543CQM | -40 to 85              | 24 Ld QSOP | M24.15-P    |

| CD74LPT543M   | -40 to 85              | 24 Ld SOIC | M24.3-P     |

| CD74LPT543QM  | -40 to 85              | 24 Ld QSOP | M24.15-P    |

NOTE: QSOP is commonly known as SSOP.

When ordering, use the entire part number. Add the suffix 96 to obtain the variant in the tape and reel.

## Description

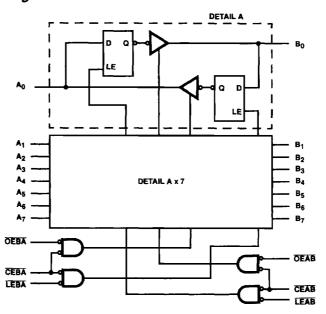

The CD74LPT543 is an 8-bit wide non-inverting transceiver designed with two sets of eight D-type latches with separate input and output controls for each set. For data flow from A to B, for example, the A-to-B Enable (CEAB) input must be LOW in order to enter data from A<sub>0</sub>-A<sub>7</sub> or to take data from B<sub>0</sub>-B<sub>7</sub>, as indicated in the Truth Table. With CEAB LOW, a LOW signal makes the A-to-B latches transparent; a subsequent LOW-to-HIGH transition of the LEAB signal puts the A latches in the storage mode and their outputs no longer change the A inputs. With CEAB and OEAB both LOW, the three-state B output buffers are active and reflect the data present at the output of the A latches. Control of data from B to A is similar, but uses the CEBA, LEBA, and OEBA inputs. Active bus-hold circuitry is provided to hold unused or floating data inputs at a valid logic level.

The CD74LPT543 can be driven from either 3.3V or 5.0V devices allowing this device to be used as a translator in a mixed 3.3/5.0V system.

### **Pinout**

**CD74LPT543** (QSOP, SOIC) TOP VIEW LEBA 1 Vcc OEBA 2 23 CEBA 22 B<sub>0</sub> 20) B<sub>2</sub> 19 B<sub>3</sub> A4 7 18 B. 17 Bs 9 16 B<sub>6</sub> A7 10 15 B7 14 LEAB CEAB 11 13 OEAB

# Functional Block Diagram

TRUTH TABLE (NOTES 1, 3)

| INPUTS |      |      | LATCH<br>STATUS | OUTPUT<br>BUFFERS                |

|--------|------|------|-----------------|----------------------------------|

| CEAB   | LEAB | OEAB | A-TO-B          | B <sub>0</sub> - B <sub>7</sub>  |

| Н      | Х    | Х    | Storing         | High Z                           |

| X      | Н    | Х    | Storing         | х                                |

| Х      | Х    | н    | х               | High Z                           |

| L      | L    | L    | Transparent     | Current A Inputs                 |

| L      | н    | L    | Storing         | Previous A<br>Inputs<br>(Note 2) |

### NOTES:

- A-to-B data flow is shown. B-to-A flow control is the same except using CEBA, LEBA, and OEBA.

- 2. Before LEAB LOW-to-HIGH Transition

- 3. H = High Voltage Level

- L = Low Voltage Level

- X = Don't Care or Irrelevant

- Z = High Impedance

# Pin Descriptions

| PIN NAME                        | DESCRIPTION                                      |

|---------------------------------|--------------------------------------------------|

| OEAB                            | A-to-B Output Enable Input (Active LOW)          |

| OEBA                            | B-to-A Output Enable Input (Active LOW)          |

| CEAB                            | A-to-B Enable Input (Active LOW)                 |

| CEBA                            | B-to-A Enable Input (Active LOW)                 |

| LEAB                            | A-to-B Latch Enable Input (Active LOW)           |

| LEBA                            | B-to-A Latch Enable Input (Active LOW)           |

| A <sub>0</sub> - A <sub>7</sub> | A-to-B Data Inputs or B-to-A Three-State Outputs |

| B <sub>0</sub> - B <sub>7</sub> | B-to-A Data Inputs or B-to-A Three-State Outputs |

| GND                             | Ground                                           |

| Vcc                             | Power                                            |

### CD74LPT543

| Absolute Maximum Ratings                                                                                                                                                                   | Thermal Information                                 |                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-----------------------------------------|

| DC Input Voltage         -0.5V to 7.0V           DC Output Current         120mA                                                                                                           | Thermal Resistance (Typical, Note 4) θ SOIC Package | <sub>JA</sub> ( <sup>o</sup> C/W)<br>75 |

| Operating Conditions                                                                                                                                                                       | QSOP Package                                        | 100                                     |

| Operating Temperature Range40°C to 85°C Supply Voltage to Ground Potential Inputs and V <sub>CC</sub> Only0.5V to 7.0V Supply Voltage to Ground Potential Outputs and D/O Only0.5V to 7.0V | Maximum Junction Temperature                        | to 150°C                                |

CAUTION: Stresses above those listed in "Absolute Maximum Flatings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

4.  $\theta_{\mbox{\scriptsize JA}}$  is measured with the component mounted on an evaluation PC board in free air.

# **Electrical Specifications**

| PARAMETER                                      | SYMBOL          | (NOTE 5) TEST CONDITIONS                                                         |                                   | MIN                       | (NOTE 6)<br>TYP | MAX  | UNITS |

|------------------------------------------------|-----------------|----------------------------------------------------------------------------------|-----------------------------------|---------------------------|-----------------|------|-------|

| DC ELECTRICAL SPE                              | CIFICATION      | NS Over the Operating Range, TA                                                  | = -40°C to 85°C, V <sub>0</sub>   | <sub>CC</sub> = 2.7V to 3 | 3.6V            |      |       |

| Input HIGH Voltage<br>(Input Pins)             | V <sub>IH</sub> | Guaranteed Logic HIGH Level                                                      | Guaranteed Logic HIGH Level       |                           | -               | 5.5  | ٧     |

| Input HIGH Voltage<br>(I/O Pins)               | V <sub>IH</sub> | Guaranteed Logic HIGH Level                                                      |                                   | 2.0                       | -               | 5.5  | ٧     |

| Input LOW Voltage<br>(Input and I/O Pins)      | V <sub>IL</sub> | Guaranteed Logic LOW Level                                                       |                                   | -0.5                      |                 | 0.8  | ٧     |

| Input HIGH Current<br>(Input Pins)             | lін             | V <sub>CC</sub> = Max                                                            | V <sub>IN</sub> = 5.5V            | -                         | -               | ±1   | μА    |

| Input HIGH Current<br>(I/O Pins)               | łін             | V <sub>CC</sub> = Max                                                            | V <sub>IN</sub> = V <sub>CC</sub> | -                         | -               | ±1   | μА    |

| Input LOW Current<br>(Input Pins)              | 1 <sub>IL</sub> | V <sub>CC</sub> = Max                                                            | V <sub>IN</sub> = GND             | -                         | -               | ±1   | μА    |

| Input LOW Current<br>(I/O Pins)                | l <sub>IL</sub> | V <sub>CC</sub> = Max                                                            | V <sub>IN</sub> = GND             | -                         | -               | ±1   | μА    |

| High Impedance                                 | lоzн            | V <sub>CC</sub> = Max                                                            | V <sub>OUT</sub> = 5.5V           | -                         | -               | ±1   | μА    |

| Output Current<br>(Three-State Output<br>Pins) | lozl            | V <sub>CC</sub> = Max                                                            | V <sub>OUT</sub> = GND            | -                         | -               | ±1   | μА    |

| Clamp Diode Voltage                            | VIK             | V <sub>CC</sub> = Min, I <sub>IN</sub> = -18mA                                   |                                   | -                         | -0.7            | -1.2 | ٧     |

| Output HIGH Current                            | IODH            | V <sub>CC</sub> = 3.3V, V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> , V | O = 1.5V (Note 7)                 | -36                       | -60             | -110 | mA    |

| Output LOW Current                             | IODL            | V <sub>CC</sub> = 3.3V, V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> , V | O = 1.5V (Note 7)                 | 50                        | 90              | 200  | mA    |

| Output HIGH Voltage                            | V <sub>OH</sub> | V <sub>CC</sub> = Min, V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub>      | I <sub>OH</sub> = -0.1mA          | V <sub>CC</sub> - 0.2     | -               |      | ٧     |

|                                                |                 |                                                                                  | I <sub>OH</sub> = -3mA            | 2.4                       | 3.0             | -    | V     |

|                                                |                 | V <sub>CC</sub> = 3.0V, V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub>     | I <sub>OH</sub> = -8mA            | 2.4<br>(Note 9)           | 3.0             | -    | ٧     |

|                                                |                 |                                                                                  | i <sub>OH</sub> = -24mA           | 2.0                       |                 | -    | ٧     |

| Output LOW Voltage                             | V <sub>OL</sub> | V <sub>CC</sub> = Min, V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub>      | I <sub>OL</sub> = 0.1mA           |                           | -               | 0.2  | ٧     |

|                                                |                 |                                                                                  | I <sub>OL</sub> = 16mA            |                           | 0.2             | 0.4  | ٧     |

|                                                |                 |                                                                                  | I <sub>OL</sub> = 24mA            | -                         | 0.3             | 0.5  | V     |

# CD74LPT543

### **Electrical Specifications (Continued)**

| PARAMETER                                            | SYMBOL           | (NOTE 5) TEST CONDITIONS                                                                                                                                                    |                                                                   | MIN | (NOTE 6)<br>TYP | MAX              | UNITS      |

|------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-----|-----------------|------------------|------------|

| Short Circuit Current<br>(Note 8)                    | los              | V <sub>CC</sub> = Max (Note 7), V <sub>OUT</sub> = GND                                                                                                                      |                                                                   | -60 | -85             | -240             | mA         |

| Power Down Disable                                   | OFF              | V <sub>CC</sub> = 0V, V <sub>IN</sub> or V <sub>OUT</sub> ≤4.5V                                                                                                             |                                                                   | -   |                 | ±100             | μА         |

| Input Hysteresis                                     | V <sub>H</sub>   |                                                                                                                                                                             |                                                                   | -   | 150             | -                | mV         |

| CAPACITANCE TA =                                     | 25°C, f = 1M     | Hz                                                                                                                                                                          |                                                                   |     |                 |                  |            |

| Input Capacitance<br>(Note 10)                       | C <sub>IN</sub>  | V <sub>IN</sub> = 0V                                                                                                                                                        |                                                                   | •   | 4.5             | 6                | pF         |

| Output Capacitance<br>(Note 10)                      | C <sub>OUT</sub> | V <sub>OUT</sub> = 0V                                                                                                                                                       |                                                                   | -   | 5.5             | 8                | pF         |

| POWER SUPPLY SPI                                     | ECIFICATIO       | NS .                                                                                                                                                                        |                                                                   | _   |                 |                  |            |

| Quiescent Power<br>Supply Current                    | lcc              | V <sub>CC</sub> = Max                                                                                                                                                       | V <sub>IN</sub> = GND<br>or V <sub>CC</sub>                       | -   | 0.1             | 10               | μА         |

| Quiescent Power<br>Supply Current TTL<br>Inputs HIGH | ΔICC             | V <sub>CC</sub> = Max                                                                                                                                                       | V <sub>IN</sub> = V <sub>CC</sub> - 0.6V<br>(Note 11)             | -   | 2.0             | 30               | μА         |

| Dynamic Power<br>Supply<br>(Note 12)                 | ICCD             | V <sub>CC</sub> = Max, Outputs Open<br>CEAB and OEAB = GND<br>CEBA = V <sub>CC</sub><br>One Bit Toggling<br>50% Duty Cycle                                                  | V <sub>IN</sub> = V <sub>CC</sub><br>V <sub>IN</sub> = GND        | -   | 50              | 75               | μA/<br>MHz |

| Total Power Supply<br>Current (Note 14)              | lc               | $V_{CC}$ = Max, Outputs Open $f_1$ = 10MHz, 50% Duty Cycle $\overline{\text{CEAB}}$ and $\overline{\text{OEAB}}$ = GND $\overline{\text{CEBA}}$ = $V_{CC}$ One Bit Toggling | $V_{IN} = V_{CC} \cdot 0.6V$<br>$V_{IN} = GND$                    | -   | 0.6             | 2.3              | mA         |

|                                                      |                  | V <sub>CC</sub> = Max, Outputs Open<br>1 <sub>j</sub> = 2.5MHz, 50% Duty Cycle<br>CEAB and OEAB = GND<br>CEBA = V <sub>CC</sub><br>8 Bits Toggling                          | V <sub>IN</sub> = V <sub>CC</sub> - 0.6V<br>V <sub>IN</sub> = GND |     | 2.1             | 4.7<br>(Note 13) | mA         |

### Switching Specifications Over Operating Range (NOTE 15)

|                                                                                                                             |                                       | (NOTE 16)                                      | CD74LPT543       |      | CD74LPT543A      |     | CD74LPT543C      |     | T     |

|-----------------------------------------------------------------------------------------------------------------------------|---------------------------------------|------------------------------------------------|------------------|------|------------------|-----|------------------|-----|-------|

| PARAMETER                                                                                                                   | SYMBOL                                | TEST                                           | (NOTE 17)<br>MIN | MAX  | (NOTE 17)<br>MIN | MAX | (NOTE 17)<br>MIN | MAX | UNITS |

| Propagation Delay<br>Transparent Mode<br>A <sub>N</sub> to B <sub>N</sub> or B <sub>N</sub> to A <sub>N</sub>               | t <sub>PLH,</sub><br>t <sub>PHL</sub> | C <sub>L</sub> = 50pF<br>R <sub>L</sub> = 500Ω | 2.5              | 8.5  | 2.5              | 6.5 | 2.5              | 5.3 | ns    |

| Propagation Delay<br>LEBA to A <sub>N</sub><br>LEAB to B <sub>N</sub>                                                       | t <sub>PLH,</sub><br>t <sub>PHL</sub> |                                                | 2.5              | 12.5 | 2.5              | 8.0 | 2.5              | 7.0 | ns    |

| Output Enable Time<br>OEBA or OEAB to A <sub>N</sub> or B <sub>N</sub><br>CEBA or CEAB to A <sub>N</sub> or B <sub>N</sub>  |                                       |                                                | 2.0              | 12.0 | 2.0              | 9.0 | 2.0              | 8.0 | ns    |

| Output Disable Time<br>OEBA or OEAB to A <sub>N</sub> or B <sub>N</sub><br>CEBA or CEAB to A <sub>N</sub> or B <sub>N</sub> |                                       |                                                | 2.0              | 9.0  | 2.0              | 7.5 | 2.0              | 6.5 | ns    |

| Setup Time HIGH or LOW,<br>AN or B <sub>N</sub> to LEAB or LEBA                                                             | t <sub>SU</sub>                       | 1                                              | 3.0              | -    | 2.0              | •   | 2.0              | -   | пŝ    |

| Hold Time HIGH or LOW,<br>A <sub>N</sub> or B <sub>N</sub> to LEAB or LEBA                                                  | <sup>t</sup> H                        |                                                | 2.0              | -    | 2.0              | -   | 2.0              | -   | ns    |

| LEAB or LEBA Pulse Width<br>LOW                                                                                             | t₩                                    |                                                | 5.0              | -    | 5.0              | -   | 5.0              | -   | ns    |

### NOTES:

- 5. For conditions shown as Max or Min, use appropriate value specified under Electrical Specifications for the applicable device type.

- 6. Typical values are at V<sub>CC</sub> = 3.3V, 25°C ambient and maximum loading.

- 7. Not more than one output should be shorted at one time. Duration of the test should not exceed one second.

- 8. This parameter is guaranteed but not tested.

- 9. VOH = VCC 0.6V at rated current.

- 10. This parameter is determined by device characterization but is not production tested.

- 11. Per TTL driven input; all other inputs at VCC or GND.

- 12. This parameter is not directly testable, but is derived for use in Total Power Supply Calculations.

- 13. Values for these conditions are examples of the ICC formula. These limits are guaranteed but not tested

- 14. IC = IQUIESCENT + INPUTS + IDYNAMIC

- IC = ICC + AICC DHNT + ICCD (ICP/2 + INI)

- I<sub>CC</sub> = Quiescent Current

- ΔI<sub>CC</sub> = Power Supply Current for a TTL High Input (V<sub>IN</sub> = 3.4V)

- DH = Duty Cycle for TTL Inputs High

- NT = Number of TTL Inputs at DH

- I<sub>CCD</sub> = Dynamic Current Caused by an Input Transition Pair (HLH or LHL)

- f<sub>CP</sub> = Clock Frequency for Register Devices (Zero for Non-Register Devices)

- f<sub>i</sub> = Input Frequency

- N<sub>I</sub> = Number of inputs at f<sub>I</sub>

- All currents are in milliamps and all frequencies are in megahertz.

- Propagation Delays and Enable/Disable times are with V<sub>CC</sub> = 3.3V 0.3V, normal range. For V<sub>CC</sub> = 2.7V, extended range, all Propagation Delays and Enable/Disable times should be degraded by 20%.

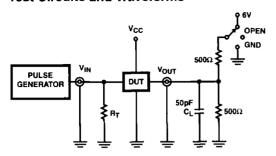

- 16. See test circuit and wave forms

- 17. Minimum limits are guaranteed but not tested on Propagation Delays.

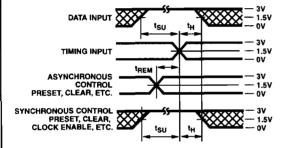

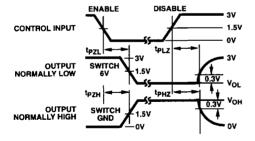

### Test Circuits and Waveforms

### NOTE:

18. Pulse Generator for All Pulses: Rate  $\leq$  1.0MHz;  $Z_{OUT} \leq$  50 $\Omega$ ;  $t_{f_1}$ ,  $t_r \leq$  2.5ns.

FIGURE 1. TEST CIRCUIT

| TEST                                             | SWITCH |

|--------------------------------------------------|--------|

| t <sub>PLZ</sub> , t <sub>PZL</sub> , Open Drain | 6V     |

| <sup>†</sup> РНZ, <sup>†</sup> РZН               | GND    |

| t <sub>PLH</sub> , t <sub>PHL</sub>              | Open   |

**SWITCH POSITION**

### **DEFINITIONS:**

$C_L$  = Load capacitance, includes jig and probe capacitance.  $R_T$  = Termination resistance, should be equal to  $Z_{OUT}$  of the Pulse Generator.

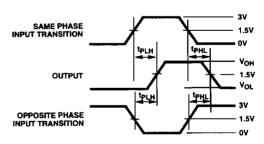

FIGURE 2. SETUP, HOLD, AND RELEASE TIMING

FIGURE 3. PULSE WIDTH

FIGURE 4. ENABLE AND DISABLE TIMING

FIGURE 5. PROPAGATION DELAY