# LF155/156/157 JFET-Input Operational Amplifiers

#### **Features**

#### **All Devices**

- Low input offset voltage 0.3 mV

- High common mode rejection ratio 100 dB

- Low input bias current 30 pA

- Low input noise current 0.01 pA/√Hz

- Low input offset voltage drift 3.0 μV/°C

### LF155 Only

■ Low supply current — 2.5 mA

### LF156 Only

- High slew rate 13 V/µS

- Wide gain bandwidth 8 MHz

- Fast settling time to 0.01% --- 4 µS

#### LF 157 Only

- High slew rate 60 V/µS

- Wide bandwidth decompensated (A<sub>VCL</sub> = 5 min) -- 28 MHz

- Fast settling time 4 μS

### **Description**

The LF156 series of JFET-input operational amplifiers feature low input bias currents and high slew rate. They are direct replacements for the industry standard LF155/156/157 types (except that pin 8 is used for internal post-package V<sub>OS</sub> trimming, so pin 8 cannot be used for PC board trace routing). Only military temperature range devices are available.

The LF155 is a general-purpose device having lower internal power dissipation than the other two versions, and a slew rate of 5  $V/\mu S$ .

The LF156 has higher internal stage currents than the LF155, giving it a slew rate of 12 V/ $\mu$ S. The LF156, like the LF155, is compensated for ac stability in unity-gain applications.

The LF157 decompensated version is the fastest member of the series, with a 45 V/ $\mu$ S slew rate. The LF157 requires a minimum closed-loop gain configuration of +5 for ac stability.

Two accuracy grades are offered for each version; the "A" versions have tighter  $V_{\rm OS}$ ,  $I_{\rm B}$ , and  $I_{\rm OS}$  specifications. All types are offered in hermetic DIP, TO-99 can, and LCC packages, and can be ordered with Mil-Std-883, Level B processing.

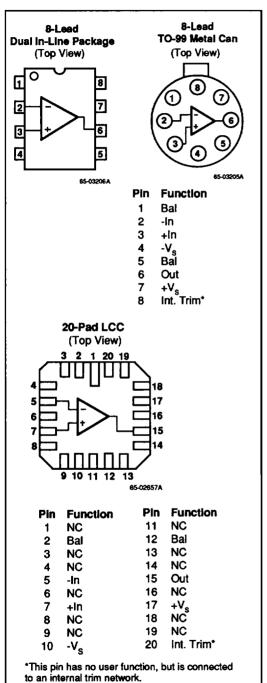

### **Connection Information**

### **Ordering Information**

| Part Number | Package | Operating<br>Temperature<br>Range |

|-------------|---------|-----------------------------------|

| LF155AD     | D       | -55°C to +125°C                   |

| LF156AD     | D       | -55°C to +125°C                   |

| LF157AD     | D       | -55°C to +125°C                   |

| LF155D      | D       | -55°C to +125°C                   |

| LF156D      | D       | -55°C to +125°C                   |

| LF157D      | D       | -55°C to +125°C                   |

| LF155AT     | Т       | -55°C to +125°C                   |

| LF156AT     | Т       | -55°C to +125°C                   |

| LF157AT     | T       | -55°C to +125°C                   |

| LF155AL     | L       | -55°C to +125°C                   |

| LF156AL     | L       | -55°C to +125°C                   |

| LF157AL     | L       | -55°C to +125°C                   |

#### Notes

Add /883B suffix to basic part number to specify Mil-Std-883, Level B processing.

L = 20-pad leadless chip carrier

D = 8 lead ceramic DIP

T = 8-lead metal can (TO-99)

Contact a Raytheon sales office or representative for ordering information on special package/temperature range combinations.

### **Absolute Maximum Ratings**

| Supply Voltage                   | ±22V           |

|----------------------------------|----------------|

| Differential Input Voltage Range |                |

| Input Voltage Range*             | ±20V           |

| Output Short Circuit             | Continuous     |

| Operating Temperature            |                |

| Range                            | 55°C to +125°C |

| Storage Temperature              |                |

| Range                            | 55°C to +150°C |

| Lead Soldering Temperature       |                |

| (60 sec)                         | +300°C         |

<sup>\*</sup>For supply voltages less than ±20V, the absolute maximum input voltage is equal to the supply voltage.

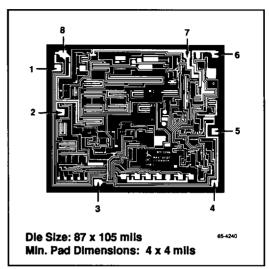

### **Mask Pattern**

### **Thermal Characteristics**

|                                          | 8-Lead<br>TO-99<br>Metal Can | 8-Lead<br>Ceramic<br>DIP | 20-Lead<br>LCC<br>Package |

|------------------------------------------|------------------------------|--------------------------|---------------------------|

| Max. Junction Temp.                      | 175°C                        | 175°C                    | 175°C                     |

| Max. P <sub>D</sub> T <sub>A</sub> <50°C | 658 mW                       | 833 mW                   | 925 mW                    |

| Therm. Res θ <sub>Jc</sub>               | 50°C/W                       | 45°C/W                   | 37°C/W                    |

| Therm. Res. θ <sub>JA</sub>              | 190°C/W                      | 150°C/W                  | 105°C/W                   |

| For T <sub>A</sub> >50°C Derate at       | 5.26 mW/°C                   | 8.33 mW/°C               | 7.0 mW/°C                 |

# **Electrical Characteristics** ( $\pm 15$ V $\leq$ V $_{\rm S}$ $\leq$ $\pm 20$ V, T $_{\rm A}$ = +25°C, unless otherwise noted)

|                                  |                                                                                                                                  | LF155A/<br>156A/157A      | LF155/<br>156/157          |                          |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------|---------------------------|----------------------------|--------------------------|

| Parameters                       | Test Conditions                                                                                                                  | Min Typ Max               | Min Typ Max                | Units                    |

| Input Offset Voltage             | $R_s = 50\Omega$ , $V_{CM} = 0V$                                                                                                 | 0.3 2.0                   | 0.4 5.0                    | mV                       |

| V <sub>os</sub> Adjustment Range |                                                                                                                                  | 8.0                       | 8.0                        | mV                       |

| Input Offset Current             | $V_{CM} = 0V, T_{j} = +25^{\circ}C$                                                                                              | 3 10                      | 6 20                       | pА                       |

| Input Bias Current               | $V_{CM} = 0V, T_J = +25^{\circ}C$                                                                                                | 30 50                     | 30 100                     | pΑ                       |

| Input Resistance                 |                                                                                                                                  | 1012                      | 10 <sup>12</sup>           | Ω                        |

| Large-Signal Voltage Gain        | $V_s = \pm 15V, R_L \ge 2 k\Omega,$<br>$V_o = \pm 10V$                                                                           | 50 200                    | 50 200                     | V/mV                     |

| Output Voltage Swing             | $R_L = 10 \text{ k}\Omega, V_S = \pm 15V$<br>$R_L = 2 \text{ k}\Omega, V_S = \pm 15V$                                            | ±12 ±13.5<br>±10 ±13.2    | ±12 ±13.5<br>±10 ±13.2     | >>                       |

| Supply Current                   | V <sub>s</sub> = ±15V<br>LF155<br>LF156/157                                                                                      | 3.0 4.0<br>4.0 7.0        | 3.0 4.0<br>4.0 7.0         | mA<br>mA                 |

| Slew Rate                        | $A_{VCL} = +1$ , $V_S = \pm 15V$ , LF155<br>$A_{VCL} = +1$ , $V_S = \pm 15V$ , LF156<br>$A_{VCL} = +5$ , $V_S = \pm 15V$ , LF157 | 3.0 6.0<br>10 13<br>40 60 | 2.0 6.0<br>7.5 13<br>30 60 | V/μS<br>V/μS<br>V/μS     |

| Gain Bandwidth Product           | $A_{VCL} = +1, V_S = \pm 15V, LF155$<br>$A_{VCL} = +1, V_S = \pm 15V, LF156$<br>$A_{VCL} = +5, V_S = \pm 15V, LF157$             | 6.0<br>8.0<br>30          | 5.7<br>7.6<br>28           | MHz<br>MHz<br>MHz        |

| Settling Time                    | To 0.01%, LF155<br>To 0.01%, LF156<br>To 0.01%, LF157                                                                            | 4.5<br>3.8<br>3.8         | 4.5<br>3.8<br>3.8          | 9<br>9<br>9<br>9         |

| Input Voltage Range              | $V_s = \pm 15V$                                                                                                                  | ±10.5+15.1<br>-12.0       | ±10.5+15.1<br>-12.0        | ٧                        |

| Common Mode Rejection Ratio      | $V_{CM} = \pm 10.5$                                                                                                              | 85 100                    | 85 100                     | dB                       |

| Power Supply Rejection Ratio     | $V_S = \pm 10V \text{ to } \pm 20V$                                                                                              | 85 100                    | 85 100                     | dB                       |

| Input Noise Voltage Density      | $R_S = 100\Omega$ , $V_S = \pm 15V$<br>$F_O = 100$ Hz, LF155<br>$F_O = 1000$ Hz                                                  | 25<br>20                  | 25<br>20                   | nV/√ <u>Hz</u><br>nV/√Hz |

|                                  | V <sub>S</sub> = ±15V<br>F <sub>O</sub> = 100 Hz, LF156/157<br>F <sub>O</sub> = 1000 Hz                                          | 15<br>12                  | 15<br>12                   | nV/√Hz<br>nV/√Hz         |

| Input Noise Current Density      | $V_S = \pm 15V$<br>$F_O = 100 \text{ Hz}$<br>$F_O = 1000 \text{ Hz}$                                                             | 0.01<br>0.01              | 0.01<br>0.01               | pA√Hz<br>pA√Hz           |

| Input Capacitance                |                                                                                                                                  | 3                         | 3                          | pF                       |

## **Electrical Characteristics** ( $\pm 15\text{V} \le \text{V}_\text{S} \le \pm 20\text{V}$ , $-55^{\circ}\text{C} \le \text{T}_\text{A} \le +125^{\circ}\text{C}$ , unless otherwise noted)

|                                       |                                                                                                 | LF155A/<br>156A/157A |                | LF155/<br>156/157 |       |                |     |                |

|---------------------------------------|-------------------------------------------------------------------------------------------------|----------------------|----------------|-------------------|-------|----------------|-----|----------------|

| Parameters                            | Test Conditions                                                                                 | Min                  | Тур            | Max               | Min   | Тур            | Max | Units          |

| Input Offset Voltage                  | $R_s = 50\Omega$ , $V_{CM} = 0V$                                                                |                      | 0.5            | 2.5               |       | 1.0            | 7.0 | mV             |

| Average Input Offset<br>Voltage Drift | Without external trim, $R_S = 50\Omega$ With external trim, $R_S = 50\Omega$                    |                      | 3.0<br>2.0     | 5.0               |       | 5.0<br>3.0     |     | μV/*C<br>μV/*C |

| Input Offset Current                  | $T_J = +125^{\circ}C, V_{CM} = 0V$                                                              |                      | 0.6            | 10                |       | 8.0            | 20  | nA             |

| Input Bias Current                    | $T_J = +125^{\circ}C, V_{CM} = 0V$                                                              |                      | 10             | 25                |       | 10             | 50  | nA             |

| Input Voltage Range                   | V <sub>S</sub> = ±15V                                                                           | ±10.4                | +15.1<br>-12.0 |                   | ±10.4 | +15.1<br>-12.0 |     | ٧              |

| Common Mode Rejection Ratio           | $V_S = \pm 15V, V_{CM} = \pm 10.4V$                                                             | 85                   | 100            |                   | 85    | 100            |     | dB             |

| Power Supply Rejection Ratio          | V <sub>s</sub> = ±10V to ±20V                                                                   | 85                   | 100            |                   | 85    | 100            |     | dB             |

| Large Signal Voltage Gain             | $V_S = \pm 15V, R_L \ge 2k\Omega,$<br>$V_O = \pm 10V$                                           | 25                   | 200            |                   | 25    | 150            |     | V/mV           |

| Output Voltage Swing                  | $R_L \ge 10 \text{ k}\Omega, V_S \approx \pm 15V$<br>$R_L \ge 2 \text{ k}\Omega, V_S = \pm 15V$ |                      | ±13.5<br>±13.0 |                   | _     | ±13.5<br>±13.0 |     | >>             |

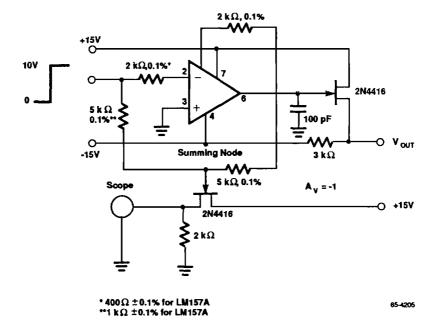

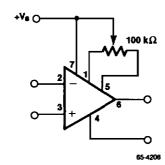

Settling -Time Test Circuit

65-4207

Note: For potentiometers with a temperature coefficient < 100 ppm/ $^{\circ}$ C, the added TCV<sub>CS</sub> with nulling Is  $\approx 0.5 \,\mu$ V/ $^{\circ}$ C /mV of adjustment

Input Offset Voltage Nulling

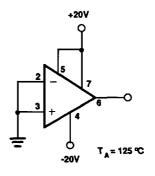

Burn-In Circuit

### **Applications Information**

### **Input Voltage Considerations**

The LF155/156/157 JFET input stages can accommodate large input differential voltages without external clamping as long as neither input exceeds the negative power supply. An input voltage which is more negative than -V<sub>s</sub> can result in a destroyed unit.

If both inputs exceed the negative common mode voltage limit, the amplifier will be forced to a high positive output. If only one input exceeds the negative common mode voltage limit, a phase reversal takes place forcing the output to the corresponding high or low state. In either of the above conditions, normal operation will return when both inputs are returned to within the specified common mode voltage range.

Exceeding the positive common mode limit on a single input will not change the phase of the output. However, if both inputs exceed the limit, the output of the amplifier will be forced to a high state.

### **Dynamic Operation Considerations**

As with most amplifiers, care should be taken with lead dress, component placement, and supply decoupling in order to ensure stability. For example, resistors from the output to an input should be placed with the body close to the input. This minimizes "pick-up" and increases the frequency of the feedback pole by minimizing the capacitance from input to ground.

A feedback pole is created when the feedback around any amplifier is resistive. The parallel resistance and capacitance from the input of the device to ac ground sets the frequency of the pole. In many instances, the frequency of this pole is much greater than the expected 3 dB frequency of the closed-loop gain. Consequently, the pole has negligible effect on stability margin. However, if the feedback pole is less than approximately six times the expected 3 dB frequency, a lead capacitor should be placed from the output to the inverting input of the op amp. The capacitor value should be such that the RC time constant of the capacitor and feedback resistor is greater than, or equal to, the original feedback-pole time constant.

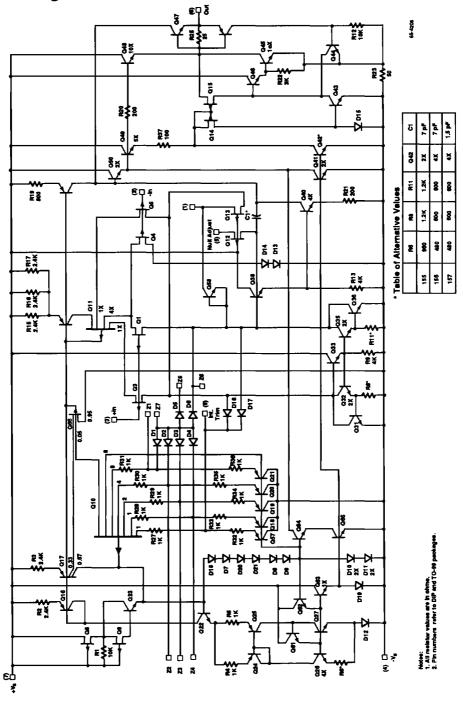

### **Schematic Diagram**