### SPEED/PACKAGE AVAILABILITY

54 F,W 74 B 54LS F,W 74LS B 74S B

### **DESCRIPTION**

Information at the D inputs meeting the setup time requirements is transferred to the Q outputs on the positive-going edge of the clock pulse. Clock triggering occurs at a particular voltage level and is not directly related to the transition time of the positive-going pulse. When the clock input is at either the high or low level, the D input signal has no effect at the output.

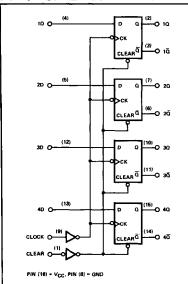

### **FUNCTIONAL BLOCK DIAGRAM**

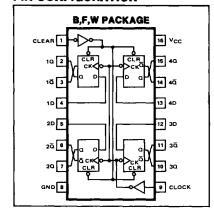

### PIN CONFIGURATION

## TRUTH TABLE (EACH FLIP-FLOP)

| J       | NPUTS | OUTPUTS |                |                  |  |  |

|---------|-------|---------|----------------|------------------|--|--|

| CLEAR ( | CLOCK | D       | Q              | ā                |  |  |

| L       | x     |         | L              | H                |  |  |

| Н       | †     | н       | Н              | Ĺ                |  |  |

| н       | †     | L       | Ìι             | н                |  |  |

| н       | L     | Χ       | Q <sub>0</sub> | <u>_</u> 00<br>H |  |  |

- H = high level (steady state)

- L = low level (steady state)

- X = irrelevant

- † = transition from low to high level

- Q<sub>0</sub>= the level of Q before the indicated steady-state input conditions were established

# SWITCHING CHARACTERISTICS V<sub>CC</sub> = 5V, T<sub>A</sub> = 25°C

|                                      |                                             |                | 54/74                                        |          | 54/74L8           |          | 54/748                                       |          |          |         |          |          |      |

|--------------------------------------|---------------------------------------------|----------------|----------------------------------------------|----------|-------------------|----------|----------------------------------------------|----------|----------|---------|----------|----------|------|

| TEST CONDITIONS                      |                                             |                | C <sub>L</sub> =15pF<br>R <sub>L</sub> =400Ω |          | CL≈15pF<br>RL≠2kΩ |          | C <sub>L</sub> =15pF<br>R <sub>L</sub> =280Ω |          |          |         |          |          |      |

| PARAMET                              | rer .                                       | FROM           | TO<br>OUTPUT                                 | MIN      | TYP               | MAX      | MIN                                          | ТҮР      | MAX      | MIN     | ТҮР      | MAX      | UNIT |

| fClock                               | Clock frequency                             |                |                                              | 25       | 35                |          | 30                                           | 40       |          | 75      | 110      |          | MHz  |

| t <sub>W</sub>                       | Width of pulse<br>Clock<br>Clear            |                |                                              | 20       |                   |          | 20                                           |          |          | 12      |          | i        | ns   |

| <sup>t</sup> Setup                   | input setup time<br>Data<br>Clear inactive  |                |                                              | 20<br>25 |                   |          | 20<br>25                                     |          | 1        | 8<br>15 |          |          | ns   |

| <sup>t</sup> Hold                    | Input hold time                             |                | l                                            | 0        |                   |          | 5                                            |          |          | 2       | 1        |          | ns   |

| Propagation tPLH tPHL                | on delay time<br>Low-to-high<br>High-to-low | Clear          |                                              |          | 16<br>23          | 25<br>35 |                                              | 16<br>23 | 25<br>35 | ;       |          |          | ns   |

| tPLH<br>tPHL                         | Low-to-high<br>High-to-low                  | Clock          |                                              |          | 20<br>21          | 30<br>30 |                                              | 20<br>21 | 30<br>35 |         | 9        | 12<br>17 |      |

| <sup>†</sup> PLH<br><sup>†</sup> PHL | Low-to-high<br>High-to-low                  | Clear<br>Clear | Q<br>Q                                       |          |                   |          |                                              |          |          |         | 13<br>13 | 15<br>22 |      |

Load circuit and typical waveforms are shown at the front of section.