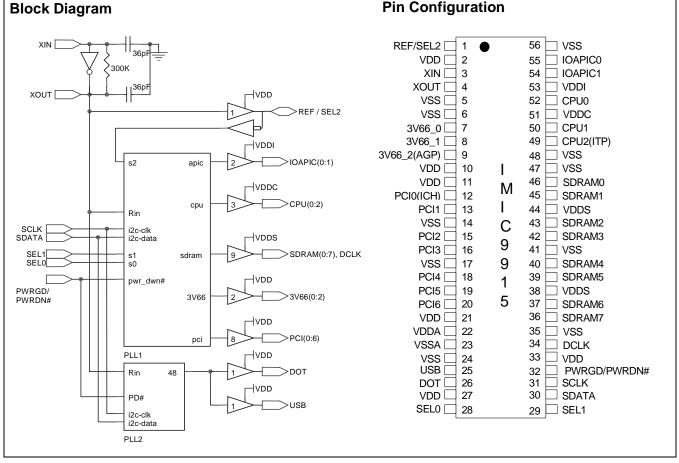

Low EMI Clock Generator for Intel<sup>®</sup> 133-MHz/2-DIMM Chipset Systems

#### Features

- Meets Intel<sup>®</sup> 133-MHz/SDRAM chipset specification

- Three copies of CPU clock (CPU[0:1] and CPU2\_ITP)

- Nine copies of SDRAM clock (SDRAM[0:7] and DCLK)

- Seven copies of PCI clock

- Three copies of 3V66 clock

- Two copies of IOAPIC clock

- One REF clock

- One USB clock (non-SSC)

- One DOT clock (non-SSC)

- Cypress Spread Spectrum for best electromagnetic interference (EMI) reduction

- SMBus support with read back

- 56-pin SSOP/TSSOP package

| Table 1. | Frequency | Table | (MHz) <sup>[1]</sup> |

|----------|-----------|-------|----------------------|

|----------|-----------|-------|----------------------|

| SEL2 | SEL1 | SEL0 | CPU         | SDRAM                  | PCI  |

|------|------|------|-------------|------------------------|------|

| Х    | 0    | 0    | Three-State | Х                      | 0    |

| Х    | 0    | 1    | Test Mode   | Х                      | 0    |

| 0    | 1    | 0    | 66.6 MHz    | 100 MHz <sup>[2]</sup> | 33.3 |

| 0    | 1    | 1    | 100 MHz     | 100 MHz <sup>[2]</sup> | 33.3 |

| 1    | 1    | 0    | 133.3 MHz   | 133.3 MHz              | 33.3 |

| 1    | 1    | 1    | 133.3 MHz   | 100 MHz <sup>[2]</sup> | 33.3 |

#### Notes:

The following clocks remain fixed frequencies except in Test Mode: 3V66 = 66.6 MHz, USB/DOT = 48 MHz, REF = 14.318 MHz, and IOAPIC = 33.3 MHz. SMBus programmable to 133 MHz, Byte 3, Bit 0. 1. 2.

# Pin Description<sup>[3]</sup>

| Pin                                       | Name                    | PWR  | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------------------------------|-------------------------|------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                         | SEL2/REF                | VDD  | I/O | <b>This is a bidirectional pin</b> . At power-up, it is an input pin Sel2 for selecting the CPU/SDRAM frequencies (see <i>Table 1</i> ). When the power reaches the rail, the state of Sel2 is latched, and this pin becomes REF, a buffer output of the signal applied at Xin, typically 14.318 MHz. This pin has an Internal pull-down. Typical 50 K $\Omega$ (range 20 K $\Omega$ to 70 K $\Omega$ ). |

| 3                                         | XIN                     | VDD  | I   | <b>On-chip Reference Oscillator Input Pin</b> . Requires either an external parallel resonant crystal (nominally 14.318 MHz) or externally generated reference signal                                                                                                                                                                                                                                    |

| 4                                         | XOUT                    | VDD  | 0   | <b>On-chip Reference Oscillator Pin</b> . Drives an external parallel resonant crystal. When an externally generated reference signal is used at Xin, this pin remains unconnected.                                                                                                                                                                                                                      |

| 12,13,15,<br>16,18,19, 20                 | PCI0_ICH<br>PCI(16)     | VDD  | 0   | <b>3.3V PCI Clock Outputs</b> . They are synchronous to CPU clocks. See <i>Figure 11</i> ).                                                                                                                                                                                                                                                                                                              |

| 7, 8, 9                                   | 3V66(0:2)               | VDD  | 0   | 3.3V Fixed 66.6 MHz Clock Outputs. See Figure 11.                                                                                                                                                                                                                                                                                                                                                        |

| 25                                        | USB                     | VDD  | 0   | 3.3V Fixed 48 MHz clock outputs.                                                                                                                                                                                                                                                                                                                                                                         |

| 26                                        | DOT                     | VDD  | 0   | 3.3V Fixed 48 MHz clock outputs.                                                                                                                                                                                                                                                                                                                                                                         |

| 28, 29                                    | SEL(0,1)                | VDD  | I   | <b>3.3V LVTTL Inputs for Logic Selection</b> . This pin has an internal pull-up. Typical 250 K $\Omega$ (range 200 K $\Omega$ to 500 K $\Omega$ )                                                                                                                                                                                                                                                        |

| 30                                        | SDATA                   | VDD  | I/O | Serial Data Input Pin. Conforms to the SMBus specification of a Slave<br>Receive/Transmit device. This pin is an input when receiving data. It is an<br>open drain output when acknowledging or transmitting data. See SMBus<br>function description.                                                                                                                                                    |

| 31                                        | SCLK                    | VDD  | I   | Serial Clock Input Pin. Conforms to the SMBus specification.                                                                                                                                                                                                                                                                                                                                             |

| 32                                        | PWRGD/PWR<br>DN#        | VDD  | I   | This is a Dual Function Pin. During power-up, it serves as a power-down control. After PWRGD has gone HIGH once, whenever pin 32 goes LOW, the device will go into power-down mode.                                                                                                                                                                                                                      |

| 34                                        | DCLK                    | VDD  | 0   | <b>3.3V SDRAM Feedback Clock</b> . See <i>Table 1</i> for frequency selection. See <i>Figure 11</i> for timing relationship.                                                                                                                                                                                                                                                                             |

| 36,37,39,40,<br>42,43,45, 46              | SDRAM(70)               | VDDS | 0   | <b>3.3V SDRAM DIMM Clocks</b> . See <i>Table 1</i> for frequency selection. See <i>Figure 11</i> for timing relationship.                                                                                                                                                                                                                                                                                |

| 49, 50, 52                                | CPU(2)_ITP,C<br>PU(1,0) | VDDC | 0   | <b>2.5V Host Clock Outputs</b> . See <i>Table 1</i> for frequency selection.                                                                                                                                                                                                                                                                                                                             |

| 54, 55                                    | IOAPIC(1,0)             | VDDI | 0   | 2.5V IOAPIC Clock Outputs. See Figure 11 for timing relationship.                                                                                                                                                                                                                                                                                                                                        |

| 2,10, 11, 21,<br>27, 33                   | VDD                     |      |     | 3.3V Common Power Supply                                                                                                                                                                                                                                                                                                                                                                                 |

| 22                                        | VDDA                    |      |     | Analog Circuitry 3.3V Power Supply                                                                                                                                                                                                                                                                                                                                                                       |

| 23                                        | VSSA                    |      |     | Analog Circuitry Power Supply Ground Pins                                                                                                                                                                                                                                                                                                                                                                |

| 51, 53                                    | VDDC, VDDI              |      |     | 2.5V Power Supply                                                                                                                                                                                                                                                                                                                                                                                        |

| 5, 6,14, 17, 24,<br>35, 41, 47, 48,<br>56 | VSS                     |      |     | Common Ground Pins                                                                                                                                                                                                                                                                                                                                                                                       |

| 38, 44                                    | VDDS                    |      |     | 3.3V Power Support for SDRAM Clock Output Drivers                                                                                                                                                                                                                                                                                                                                                        |

Note:

A bypass capacitor (0.1µF) should be placed as close as possible to each positive power pin. If these bypass capacitors are not close to the pins their high frequency filtering characteristic will be cancelled by the lead inductance of the traces.

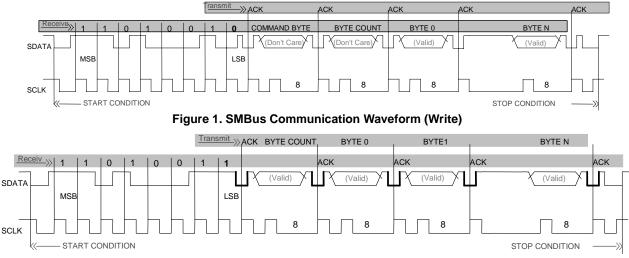

# **Two-Wire SMBus Control Interface**

The two-wire control interface implements a Read/Write slave-only interface, according to SMBus specification. (See *Figure 1* and *Figure 2*, below). The device can be read back by using standard SMBus command bytes. Subaddressing is not supported, thus all <u>preceding bytes must be sent</u> in order to change one of the control bytes. The two-wire control interface allows each clock output to be individually enabled or disabled. 100 Kbits/second (standard mode) data transfer is supported.

During normal data transfer, the SDATA signal only changes when the SCLK signal is low, and is stable when SCLK is high. There are two exceptions to this. A HIGH-to-LOW transition on SDATA while SCLK is HIGH is used to indicate the start of a data transfer cycle. A LOW-to-HIGH transition on SDATA while SCLK is HIGH indicates the end of a data transfer cycle. Data is always sent as complete eight-bit bytes, after which an acknowledge is generated. The first byte of a transfer cycle is an eight-bit address. The LSB address Byte = 0 in write mode.

The device will respond to transfers of 10 bytes (max) of data. The device will generate an acknowledge (LOW) signal on the SDATA wire following reception of each byte. Data is transferred MSB first at a max. rate of 100kbits/S. This device will also respond to a <u>D3</u> address which sets it in a read mode. It will not respond to any other control interface conditions, and previously set control registers are retained.

Figure 2. SMBus Communication Waveform (Read)

# **Serial Control Registers**

#### Byte 4: CPU Clock Register

| Bit | @Pup        | Pin# | Name | Description                                                                                    |

|-----|-------------|------|------|------------------------------------------------------------------------------------------------|

| 7   | H/W Setting | 14   | FS3  | For selecting frequencies in Table 1                                                           |

| 6   | H/W Setting | 4    | FS2  | For selecting frequencies in Table 1                                                           |

| 5   | H/W Setting | 3    | FS1  | For selecting frequencies in Table 1                                                           |

| 4   | H/W Setting | 2    | FS0  | For selecting frequencies in Table 1                                                           |

| 3   | 0           |      |      | 0 = HW, 1 = SW Frequency Selection                                                             |

| 2   | H/W Setting | 15   | FS4  | For selecting frequencies in Table 1                                                           |

| 1   | 1           |      | SSCG | Spread Spectrum Enable. 0 = Spread Off, 1 = Spread On<br>This is a Read and Write control bit. |

| 0   | 0           |      |      | 0 = running; 1= three-state all outputs                                                        |

Byte 5: CPU Clock Register (All bits are Read-only)

| Bit | @Pup | Pin# | Name  | Description                                  |

|-----|------|------|-------|----------------------------------------------|

| 7   | 0    |      |       | Reserved                                     |

| 6   | 0    |      |       | Reserved                                     |

| 5   | Х    | 26   | MULTO | MULT0 (pin 26) value. This bit is Read-only. |

| 4   | Х    | 15   | FS4   | FS4 read back. This bit is Read-only.        |

| Byte 5: CPU Clock Register | (All bits are Read-only) | (continued) |

|----------------------------|--------------------------|-------------|

|----------------------------|--------------------------|-------------|

| Bit | @Pup | Pin# | Name | Description                           |

|-----|------|------|------|---------------------------------------|

| 3   | Х    | 14   | FS3  | FS3 read back. This bit is Read-only. |

| 2   | Х    | 4    | FS2  | FS2 read back. This bit is Read-only. |

| 1   | Х    | 3    | FS1  | FS1 read back. This bit is Read-only. |

| 0   | Х    | 2    | FS0  | FS0 read back. This bit is Read-only. |

# Byte 6: CPU Clock Register

| Bit | @Pup | Pin#  | Name    | Description                                                                                                                                                                 |

|-----|------|-------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | 0    |       |         | Function Test Bit, always program to 0.                                                                                                                                     |

| 6   | 0    |       |         | Reserved.                                                                                                                                                                   |

| 5   | 0    | 14    | PCI_F0  | PCI_STP# control of PCI_F0. 0 = Free Running, 1 = Stopped when PCI_STP# is LOW.                                                                                             |

| 4   | 0    | 15    | PCI_F1  | PCI_STP# control of PCI_F1. 0 = Free Running, 1 = Stopped when PCI_STP# is LOW.                                                                                             |

| 3   | 1    | 40,39 | CPU0T/C | Controls CPU0T and CPU0C functionality when CPU_STP# is asserted LOW<br>0 = Free Running, 1 + Stopped with CPU_STP# asserted LOW. This is a Read- and<br>Write-Control bit. |

| 2   | 0    | 44,43 | CPU1T/C | Controls CPU1T and CPU1C functionality when CPU_STP# is asserted LOW 0 = Free Running, 1 Stopped with CPU_STP# asserted LOW. This and Read- and Write-control Bit.          |

| 1   | 1    | 40,39 | CPU0T/C | CPU0T, CPU0C Output Control, 1= enabled, 0 = disabled. This is a Read- and Write-control bit.                                                                               |

| 0   | 1    | 44,43 | CPU1T/C | CPU1T, CPU1C Output Control, 1= enabled, 0 = disabled. This is a Read- and Write-control bit.                                                                               |

### **<u>Byte 7</u>: PCI Clock Register** (All bits are Read and Write functional)

| Bit | @Pup | Pin# | Name   | Description                                       |

|-----|------|------|--------|---------------------------------------------------|

| 7   | 1    | 15   | PCI_F0 | PCI_F0 Output Control 1 = enabled, 0 = forced LOW |

| 6   | 1    | 14   | PCI_F1 | PCI_F1 Output Control 1 = enabled, 0 = forced LOW |

| 5   | 1    | 23   | PCI5   | PCI5 Output Control 1 = enabled, 0 = forced LOW   |

| 4   | 1    | 22   | PCI4   | PCI4 Output Control 1 = enabled, 0 = forced LOW   |

| 3   | 1    | 21   | PCI3   | PCI3 Output Control 1 = enabled, 0 = forced LOW   |

| 2   | 1    | 20   | PCI2   | PCI2 Output Control 1 = enabled, 0 = forced LOW   |

| 1   | 1    | 17   | PCI1   | PCI1 Output Control 1 = enabled, 0 = forced LOW   |

| 0   | 1    | 16   | PCI0   | PCI0 Output Control 1 = enabled, 0 = forced LOW   |

### Byte 8: Silicon Signature Register

| Bit | @Pup | Description    |

|-----|------|----------------|

| 7   | 1    | Vendor ID      |

| 6   | 0    | 1000 = Cypress |

| 5   | 0    |                |

| 4   | 0    |                |

| 3   | 0    | Revision ID    |

| 2   | 0    |                |

| 1   | 0    |                |

| 0   | 0    |                |

# Byte 9: Peripheral Control Register (All bits are Read-only)

| Bit | @Pup | Pin# | Name    | Description                                                                                                                                               |

|-----|------|------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | 1    | 33   | PD#     | PD# Enable. 0 = enable, 1 = disable                                                                                                                       |

| 6   | 0    |      |         | 0 = when PD# asserted LOW, CPU(0:1)T stop in a high state, CPU(0:1)C stop in a low state. 1 = when PD# asserted LOW, CPU(0:1)T and CPU(0:1)C stop in H-Z. |

| 5   | 1    | 27   | 48M     | 48M Output Control 1 = enabled, 0 = forced LOW                                                                                                            |

| 4   | 1    | 26   | 48M_24M | 48M_24M Output Control 1 = enabled, 0 = forced LOW                                                                                                        |

| 3   | 1    | 26   | 48M_24M | 48M_24M, 0 = pin28 output is 24 MHz, 1= pin28 output is 48 MHz.                                                                                           |

| 2   | 0    |      |         | SS2 Spread Spectrum control bit (0 = down spread, 1= Center spread)                                                                                       |

| 1   | 0    |      |         | SS1 Spread Spectrum control bit. See Table 6.                                                                                                             |

| 0   | 0    |      |         | SS0 Spread Spectrum control bit. See Table 6.                                                                                                             |

Byte 10: Peripheral Control Register (All bits are Read-only)

| Bit | @Pup | Pin# | Name  | Description                                     |

|-----|------|------|-------|-------------------------------------------------|

| 7   | 1    | 47   | SDCLK | SDCLK Output Enable 1 = enabled, 0 = disabled   |

| 6   | 1    | 4    | REF2  | REF2 Output Control 1 = enabled, 0 = forced LOW |

| 5   | 1    | 3    | REF1  | REF1 Output Control 1 = enabled, 0 = forced LOW |

| 4   | 1    | 2    | REF0  | REF0 Output Control 1 = enabled, 0 = forced LOW |

| 3   | 1    | 10   | ZCLK1 | ZCLK1 Output Enable 1 = enabled, 0 = disabled   |

| 2   | 1    | 9    | ZCLK0 | ZCLK0 Output Enabled 1 = enabled, 0 = disabled  |

| 1   | 1    | 30   | AGP1  | AGP1 Output Enabled 1 = enabled, 0 = disabled   |

| 0   | 1    | 31   | AGP0  | AGP0 Output Enabled 1 = enabled, 0 = disabled   |

### Byte 11: Dial-a-Skew<sup>™</sup> and Dial-a-Ratio<sup>™</sup> Control Register

| Bit | @Pup | Name   | Description                                                                                                                                         |  |

|-----|------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7   | 0    | DARSD2 | Programming these bits allow modifying the frequency ratio of the SDCLK clock                                                                       |  |

| 6   | 0    | DARSD1 | relative to the VCO. See <i>Table 2</i> .                                                                                                           |  |

| 5   | 0    | DARSD0 |                                                                                                                                                     |  |

| 4   | 0    | DARAG2 | Programming these bits allow modifying the frequency ratio of the AGP(1:0), PCI(5:0) and PCIF(0:1) clocks relative to the VCO. See <i>Table 3</i> . |  |

| 3   | 0    | DARAG1 |                                                                                                                                                     |  |

| 2   | 0    | DARAG0 |                                                                                                                                                     |  |

| 1   | 0    | DASSD1 | Programming these bits allow shifting skew between CPU and SDCLK signals. Se <i>Table 4</i> .                                                       |  |

| 0   | 0    | DASSD0 |                                                                                                                                                     |  |

#### Table 2. Dial-a-Ratio SDCLK

| DARSD (2:0) | VC0/SDCLK Ratio             |

|-------------|-----------------------------|

| 000         | Frequency Selection Default |

| 001         | 2                           |

| 010         | 3                           |

| 011         | 4                           |

| 100         | 5                           |

| 101         | 6                           |

| 110         | 8                           |

| 111         | 9                           |

# Table 3. Dial-a-Ratio AGP(0:1)<sup>[4]</sup>

| DARAG (2:0) | VC0/AGP ratio               |

|-------------|-----------------------------|

| 000         | Frequency Selection Default |

| 001         | 6                           |

| 010         | 7                           |

| 011         | 8                           |

| 100         | 9                           |

| 101         | 10                          |

| 110         | 10                          |

| 111         | 10                          |

#### Table 4. Dial-a-Skew SDCLK CPU

| DASSD (1:0) | SDCLK-CPU Skew                |

|-------------|-------------------------------|

| 00          | 0 ps (Default) <sup>[5]</sup> |

| 01          | +150 ps (CPU lag)*            |

| 10          | +300 ps (CPU lag)*            |

| 11          | +450 ps (CPU lag)*            |

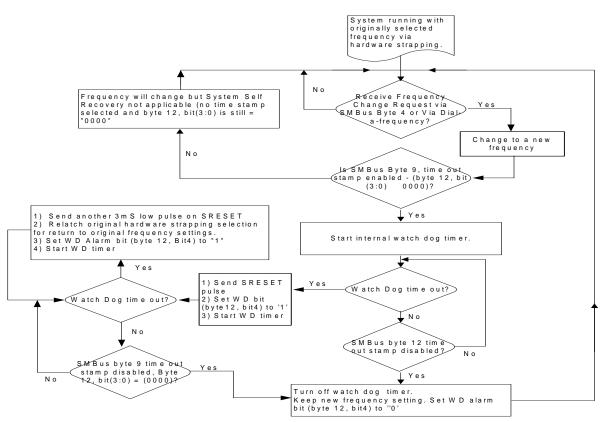

#### Byte 12: Watchdog Time Stamp Register

| Bit | @Pup | Name | Description                                                                                                                                                                                                                                                                                                 |

|-----|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | 1    |      | <b>SRESET#/PCI_STP#</b> . 1 = Pin 12 is the input pin as PCI_STP# signal. 0 = Pin 12 is the output pin as SRESET# signal.                                                                                                                                                                                   |

| 6   | 0    |      | <b>Frequency Revert</b> . This bit allows setting the Revert Frequency once the system is rebooted due to Watchdog time out only.0 = selects frequency of existing H/W setting1 = selects frequency of the second to last S/W setting. (the software setting prior to the one that caused a system reboot). |

| 5   | 0    |      | WDTEST. For WD-Test, ALWAYS program to "0."                                                                                                                                                                                                                                                                 |

| 4   | 0    |      | <b>WD Alarm</b> . This bit is set to "1" when the Watchdog times out. It is reset to "0" when the system clears the WD time stamps (WD3:0).                                                                                                                                                                 |

| 3   | 0    | WD3  | This bits selects the Watchdog Time Stamp Value. See Table 5.                                                                                                                                                                                                                                               |

| 2   | 0    | WD2  |                                                                                                                                                                                                                                                                                                             |

| 1   | 0    | WD1  |                                                                                                                                                                                                                                                                                                             |

| 0   | 0    | WD0  |                                                                                                                                                                                                                                                                                                             |

#### Table 5. Watchdog Time Stamp Table

| WD(3:0) | FUNCTION  |

|---------|-----------|

| 0000    | Off       |

| 0001    | 1 second  |

| 0010    | 2 seconds |

| 0011    | 3 seconds |

| 0100    | 4 seconds |

| 0101    | 5 seconds |

| 0110    | 6 seconds |

| 0111    | 7 seconds |

#### Notes:

The ratio of AGP to PCI is retained at 2:1.

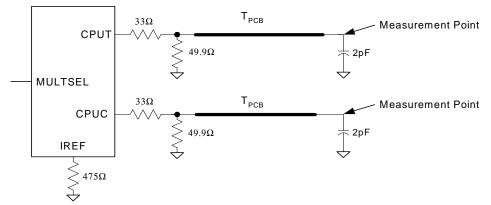

See Figure 10 for CPU measurement point. See Figure 11 for SDCLK measurement point.

### Table 5. Watchdog Time Stamp Table (continued)

| WD(3:0) | FUNCTION   |

|---------|------------|

| 1000    | 8 seconds  |

| 1001    | 9 seconds  |

| 1010    | 10 seconds |

| 1011    | 11 seconds |

| 1100    | 12 seconds |

| 1101    | 13 seconds |

| 1110    | 14 seconds |

| 1111    | 15 seconds |

\_\_\_\_\_

Byte 13: Dial-a-Frequency™ Control Register N (All bits are Read and Write functional)<sup>[6]</sup>

| Bit | @Pup | Description |

|-----|------|-------------|

| 7   | 0    | Reserved    |

| 6   | 0    | N6, MSB     |

| 5   | 0    | N5          |

| 4   | 0    | N4          |

| 3   | 0    | N3          |

| 2   | 0    | N2          |

| 1   | 0    | N3          |

| 0   | 0    | N0, LSB     |

Byte 14: Dial-a-Frequency Control Register R (All bits are Read and Write functional)<sup>[6]</sup>

| Bit | @Pup | Description                                                                                                                           |

|-----|------|---------------------------------------------------------------------------------------------------------------------------------------|

| 7   | 0    | Reserved                                                                                                                              |

| 6   | 0    | R5 MSB                                                                                                                                |

| 5   | 0    | R4                                                                                                                                    |

| 4   | 0    | R3                                                                                                                                    |

| 3   | 0    | R2                                                                                                                                    |

| 2   | 0    | R1                                                                                                                                    |

| 1   | 0    | R0, LSB                                                                                                                               |

| 0   | 0    | R and N register load gate $0 =$ gate closed (data is latched), $1 =$ gate open (data is loading from SMBus registers into R and N.)# |

Note:

6. Byte 13 and Byte 14 should be Write together in every case.

### **Dial-a-Frequency Feature**

SMBus Dial-a-Frequency feature is available in this device via Byte13 and Byte14. P is a large value PLL constant that depends on the frequency selection achieved through the hardware selectors (FS4, FS0). P value may be determined from the following table.

| FS(4:0)                                                                               | Р        |

|---------------------------------------------------------------------------------------|----------|

| 00110, 01000, 01010, 01100, 11001, 11011,<br>01101                                    | 32005333 |

| 00100, 00101, 10000, 10001, 10101, 10111,<br>11000, 11010, 11100, 11101, 11110, 11111 | 38406400 |

| 00000, 00001, 00010, 00111, 01001, 01011,<br>01110, 01111, 10010, 10100, 10110        | 48008000 |

| 00011, 10011                                                                          | 64010667 |

### Spread Spectrum Clock Generation (SSCG)

Spread Spectrum is a modulation technique used to minimizing EMI radiation generated by repetitive digital signals. A clock presents the greatest EMI energy at the center frequency it is generating. Spread Spectrum distributes this energy over a specific and controlled frequency bandwidth therefore causing the average energy at any one point in this band to decrease in value. This technique is achieved by modulating the clock away from its resting frequency by a certain percentage (which also determines the amount of EMI reduction). In this device, Spread Spectrum is enabled by setting specific register bits in the SMBus control Bytes. See the SMBus register section of this data sheet for the exact bit and byte functionally. *Table 6* is a listing of the modes and percentages of Spread Spectrum modulation that this device incorporates.

# Table 6. Spread Spectrum

### System Self Recovery Clock Management

This feature is designed to allow the system designer to change frequency while the system is running and reboot the operation of the system in case of a hang up due to the frequency change.

When the system sends an SMBus command requesting a frequency change through Byte 4 or through bytes 13 and 14, it must have previously sent a command to byte 12, for selecting which time out stamp the Watchdog must perform, otherwise the System Self Recovery feature will not be applicable. Consequently, this device will change frequency and then the Watchdog timer starts timing. Meanwhile, the system BIOS is running its operation with the new frequency. If this device receives a new SMBus command to clear the bits originally programmed in Byte 12, bits (3:0) (reprogram to 0000), before the Watchdog times out, then this device will keep operating in its normal condition with the new selected frequency. If the Watchdog times out the first time before the new SMBus reprograms Byte 12, bits (3:0) to (0000), then this device will send a low system reset pulse, on SRESET# (see byte12, bit7), and changes WD alarm (Byte12, Bit4) status to "1" then restarts the Watchdog timer again. If the Watchdog times out a second time, then this device will send another low pulse on SRESET#, will relatch original hardware strapping frequency (or second to last software selected frequency, see byte12, bit6) selection, set WD alarm bit (Byte12, bit4) to "1," then start WD timer again. The above-described sequence will keep repeating until the BIOS clears the SMBus byte12 bits (3:0). Once the BIOS sets Byte 12 bits (3:0) = 0000, then the Watchdog timer is turned off and the WD alarm bit (Byte 12, bit4) is reset to "0."

| SS2 | SS1 | SS0 | Spread Mode | Spread %     |

|-----|-----|-----|-------------|--------------|

| 0   | 0   | 0   | Down        | 0, -0.50     |

| 0   | 0   | 1   | Down        | +0.12, -0.62 |

| 0   | 1   | 0   | Down        | +0.25, -0.75 |

| 0   | 1   | 1   | Down        | +0.50, -1.00 |

| 1   | 0   | 0   | Center      | +0.25, -0.25 |

| 1   | 0   | 1   | Center      | +0.37, -0.37 |

| 1   | 1   | 0   | Center      | +0.50, -0.50 |

| 1   | 1   | 1   | Center      | +0.75, -0.75 |

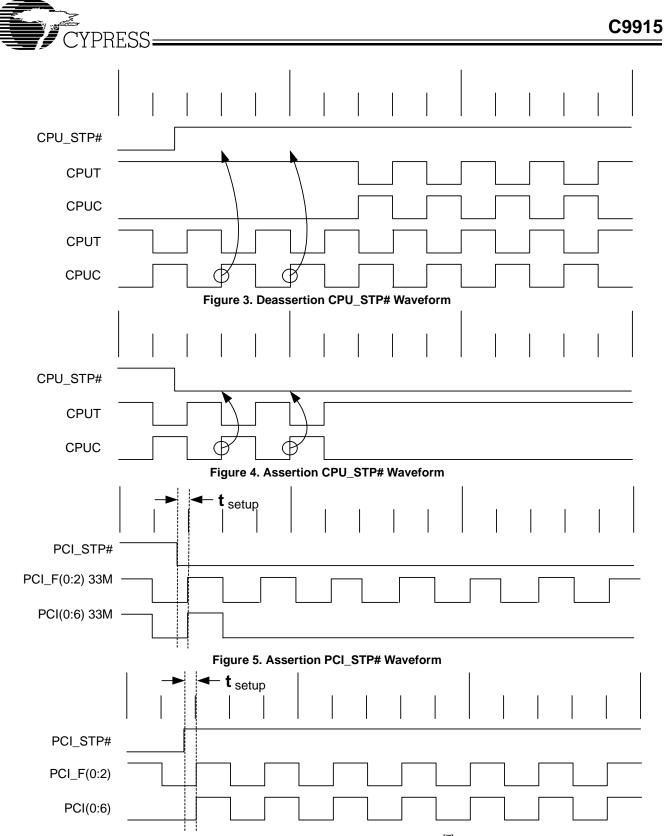

#### **CPU\_STP#** Clarification

The CPU\_STP# signal is an active LOW input used for synchronous stopping and starting the CPU output clocks while the rest of the clock generator continues to function.

#### **CPU\_STP#** Assertion

When CPU\_STP# pin is asserted, all CPU outputs that are set with the SMBus configuration to be stoppable via assertion of CPU\_STP# will be stopped after being sampled by two falling CPU clock edges. The final state of the stopped CPU signals is CPU = HIGH and CPU0# = LOW. There is no change to the output drive current values during the stopped state. The CPU is driven HIGH with a current value equal to (Mult 0 "select") x (Iref), and the CPU# signal will not be driven. Due to external pull-down circuitry CPU# will be LOW during this stopped state.

#### **CPU\_STP#** Deassertion

The de-assertion of the CPU\_STP# signal will cause all CPU outputs that were stopped to resume normal operation in a

synchronous manner. Synchronous manner meaning that no short or stretched clock pulses will be produce when the clock resumes. The maximum latency from the de-Assertion to active outputs is no more than 2 CPU clock cycles.

#### **PCI\_STP#** Assertion

The PCI\_STP# signal is an active LOW input used for synchronous stopping and starting the PCI outputs while the rest of the clock generator continues to function. The set-up time for capturing PCI\_STP# going LOW is 10 ns ( $t_{setup}$ ). (See *Figure 5.*) The PCI\_F (0:2) clocks will not be affected by this pin if their control bits in the SMBus register are set to allow them to be free running.

#### **PCI\_STP#** Deassertion

The deassertion of the PCI\_STP# signal will cause all PCI(0:6) and stoppable PCI\_F(0:2) clocks to resume running in a synchronous manner within 2 PCI clock periods after PCI\_STP# transitions to a HIGH level.

Figure 6. Deassertion PCI\_STP# Waveform<sup>[7]</sup>

Note:

7. The PCI STOP function is controlled by two inputs. One is the device PCI\_STP# pin number 34 and the other is SMBus Byte 0,Bit 3. These two inputs are logically ANDed. If either the external pin or the internal SMBus register bit is set LOW, the stoppable PCI clocks will be stopped in a logic LOW state. Reading SMBus Byte 0,Bit 3 will return a 0 value if either of these control bits are set LOW, thereby indicating that the device's stoppable PCI clocks are not running.

#### PD# (Power-down) Clarification

The PD# pin is used to shut off ALL clocks prior to shutting off power to the device. PD# is an asynchronous active LOW input. This signal is synchronized internally to the device powering down the clock synthesizer. PD# is an asynchronous function for powering up the system. When PD# is LOW, all clocks are driven to a LOW value and held there; the VCO and PLLs are also powered down. All clocks are shut down in a synchronous manner so has not to cause glitches while transitioning to the LOW "stopped" state.

PD# – Assertion (Transition from Logic "1" to Logic "0") When PD# is sampled LOW by two consecutive rising edges be held LOW on their next HIGH-to-LOW transition. CPUT clocks must be hold with CPUT clock pin driven high with a value of 2× Iref and CPUC undriven.

Due to the state of internal logic, stopping and holding the REF clock outputs in the LOW state may require more than one clock cycle to complete.

#### PD# – Deassertion (Transition from Logic "0" to Logic "1")

The power-up latency between PD# rising to a valid logic "1" level and the starting of all clocks is less than 3.0 ms.

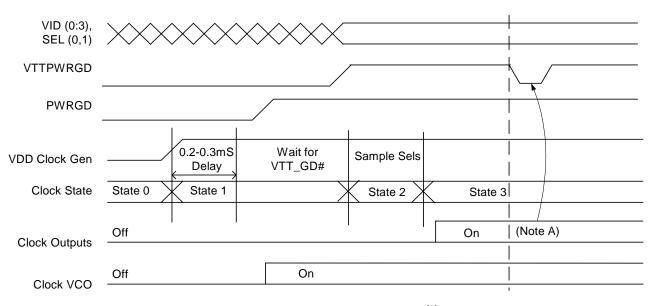

#### Figure 8. VTTPWRGD Timing Diagram<sup>[8]</sup>

Note:

8. Device is not affected, VTTPWRGD is ignored.

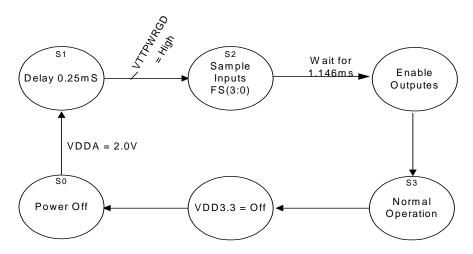

Figure 9. Clock Generator Power Up/Run State Diagram

# Maximum Ratings<sup>[9.]</sup>

| Input Voltage Relative to V <sub>SS</sub> :                      | V <sub>SS</sub> – 0.3V |

|------------------------------------------------------------------|------------------------|

| Input Voltage Relative to V <sub>DDQ</sub> or AV <sub>DD</sub> : | V <sub>DD</sub> + 0.3V |

| Storage Temperature:65                                           | °C to + 150°C          |

| Operating Temperature: | 0°C to +70°C |

|------------------------|--------------|

| Maximum Power Supply:  | 3.5V         |

# **DC Characteristics**

# Current Accuracy<sup>[10]</sup>

| Parameter | Description                       | Conditions                                        | Min.      | Max. | Load                                      |

|-----------|-----------------------------------|---------------------------------------------------|-----------|------|-------------------------------------------|

| lout      | V <sub>DD</sub> = nominal (3.30V) | M0 = 0 or 1 and Rr shown in table                 | –7% Inom  |      | Nominal test load for given configuration |

| lout      | V <sub>DD</sub> = 3.30 ±5%        | All combinations of M0 or 1 and Rr shown in table | –12% Inom |      | Nominal test load for given configuration |

## DC Component Parameters (V<sub>DD</sub> = $3.3V\pm5\%$ , TA = $0^{\circ}C$ to $70^{\circ}C$ )

| Symbol  | Description               | Conditions                                            | Min. | Тур. | Max.        | Unit |

|---------|---------------------------|-------------------------------------------------------|------|------|-------------|------|

| Idd3.3V | Dynamic Supply Current    | All frequencies at maximum values <sup>[11]</sup>     |      |      | 280         | mA   |

| lpd3.3V | Power-down Supply Current | PD# Asserted                                          |      |      | See Note 11 | mA   |

| Cin     | Input Pin Capacitance     |                                                       |      |      | 5           | pF   |

| Cout    | Output Pin Capacitance    |                                                       |      |      | 6           | pF   |

| Lpin    | Pin Inductance            |                                                       |      |      | 7           | nH   |

| Cxtal   | Crystal Pin Capacitance   | Measured from the $X_{IN}$ or $X_{OUT}$ pin to Ground | 30   | 36   | 42          | pF   |

#### Table 7. Maximum Lumped Capacitive Output Loads

| Clock                   | Max. Load | Unit |

|-------------------------|-----------|------|

| PCI(0:5), PCI_F(0:1)    | 30        | pF   |

| AGP (0:1), SDCLK        | 30        | pF   |

| ZCLK (0:1)              | 30        | pF   |

| 48M_24, 48M Clock       | 20        | pF   |

| REF (0:2)               | 30        | pF   |

| CPU(0:1)T<br>CPU(0:1) C | 2         | pF   |

Notes:

Multiple Supplies The voltage on any input or I/O pin cannot exceed the power pin during power-up. Power supply sequencing is NOT required.

Inom refers to the expected current based on the configuration of the device.

Absolute value = (Programmed CPU Iref 97) +10 mA.

# AC Parameters<sup>[12]</sup>

|                     |                                            | 100                | MHz                | 133 MHz            |                 |      |             |  |

|---------------------|--------------------------------------------|--------------------|--------------------|--------------------|-----------------|------|-------------|--|

| Parameters          | Description                                | Min.               | Max.               | Min.               | Max.            | Unit | Notes       |  |

| Crystal             |                                            |                    | 1                  | 1                  |                 |      |             |  |

| TDC                 | X <sub>IN</sub> Duty Cycle                 | 47.5               | 52.5               | 47.5               | 52.5            | %    | 13,21       |  |

| TPeriod             | X <sub>IN</sub> Period                     | 69.841             | 71.0               | 69.841             | 71.0            | ns   | 13,14,16,21 |  |

| VHIGH               | X <sub>IN</sub> HIGH Voltage               | 0.7V <sub>DD</sub> | V <sub>DD</sub>    | 0.7V <sub>DD</sub> | V <sub>DD</sub> | V    |             |  |

| VLOW                | X <sub>IN</sub> LOW Voltage                | 0                  | 0.3V <sub>DD</sub> | 0                  | $0.3V_{DD}$     | V    |             |  |

| Tr/Tf               | X <sub>IN</sub> Rise and Fall Times        |                    | 10.0               |                    | 10.0            | ns   |             |  |

| ТССЈ                | X <sub>IN</sub> Cycle-to-Cycle Jitter      |                    | 500                |                    | 500             | ps   | 14,17,21    |  |

| CPU at 0.7V Tin     | ning                                       |                    |                    |                    |                 |      |             |  |

| TSKEW               | Any CPU to CPU Clock Skew                  |                    | 150                |                    | 150             | ps   | 17, 24, 28  |  |

| TCCJ                | CPU Cycle-to-Cycle Jitter                  |                    | 150                |                    | 150             | ps   | 17, 24, 28  |  |

| TDC                 | CPU and CPUC Duty Cycle                    | 45                 | 55                 | 45                 | 55              | %    | 17, 24, 28  |  |

| TPeriod             | CPU and CPUC Period                        | 9                  | 10.2               | 7.35               | 7.65            | ns   | 17, 24, 28  |  |

| Tr / Tf             | CPU and CPUC Rise and Fall Times           | 175                | 700                | 175                | 700             | ps   | 17, 18      |  |

|                     | Rise/Fall Matching                         |                    | 20%                |                    | 20%             |      | 18, 27, 28  |  |

| DeltaTr             | Rise Time Variation                        |                    | 125                |                    | 125             | ps   | 18, 28      |  |

| DeltaTf             | Fall Time Variation                        |                    | 125                |                    | 125             | ps   | 18, 28      |  |

| Vcross              | Crossing Point Voltage at 0.7V Swing       | 280                | 430                | 280                | 430             | mV   | 18, 24, 28  |  |

| AGP                 |                                            |                    |                    |                    |                 |      |             |  |

| TDC                 | AGP Duty Cycle                             |                    | 55                 | 45                 | 55              | %    | 14, 16      |  |

| TPeriod             | AGP Period                                 | 15.0               | 15.3               | 15.0               | 15.3            | ns   | 14, 16      |  |

| THIGH               | AGP HIGH Time                              | 5.25               | -                  | 5.25               |                 | ns   | 25          |  |

| TLOW                | AGP LOW Time                               | 5.05               | -                  | 5.05               |                 | ns   | 26          |  |

| Tr / Tf             | AGP Rise and Fall Times                    | 0.5                | 1.6                | 0.5                | 1.6             | ns   | 14, 15      |  |

| Tskew<br>Unbuffered | Any AGP to Any AGP Clock Skew              |                    | 175                |                    | 175             | ps   | 14, 16      |  |

| тссј                | AGP Cycle-to-Cycle Jitter                  |                    | 250                |                    | 250             | ps   | 14, 16      |  |

| ZCLK                |                                            |                    | 1                  | 1                  |                 |      |             |  |

| TDC                 | ZCLK(0:1) Duty Cycle                       | 45                 | 55                 | 45                 | 55              | %    | 14, 16      |  |

| Tr / Tf             | ZCLK(0:1) Rise and Fall Times              | 0.5                | 1.6                | 0.5                | 1.6             | ns   | 14, 15      |  |

| TSKEW               | Any ZCLK(0:1) to Any ZCLK(0:1) Skew        |                    | 175                |                    | 175             | ps   | 14, 16      |  |

| ТССЈ                | ZCLK(0:1)Cycle-to-Cycle Jitter             |                    | 250                |                    | 250             | ps   | 14,16       |  |

| PCI                 | 1                                          |                    |                    |                    |                 |      | T           |  |

| TDC                 | PCI_F(0:1) PCI (0:5) Duty Cycle            | 45                 | 55                 | 45                 | 55              | %    | 14, 16      |  |

| TPeriod             | PCI_F(0:1) PCI (0:5) Period                | 30.0               |                    | 30.0               |                 | nS   | 13,14,16    |  |

| THIGH               | PCI_F(0:1) PCI (0:5) HIGH Time             | 12.0               |                    | 12.0               |                 | nS   | 25          |  |

| TLOW                | PCI_F(0:1) PCI (0:5) LOW Time              | 12.0               |                    | 12.0               |                 | nS   | 26          |  |

| Tr / Tf             | PCI_F(0:1) PCI (0:5) Rise and Fall Times   | 0.5                | 2.0                | 0.5                | 2.0             | nS   | 14, 15      |  |

| TSKEW               | Any PCI Clock to Any PCI Clock Skew        |                    | 500                |                    | 500             | pS   | 14, 16      |  |

| TCCJ                | PCI_F(0:1) PCI (0:5) Cycle-to-Cycle Jitter |                    | 250                |                    | 250             | ps   | 14, 16      |  |

| SDCLK               |                                            |                    |                    |                    |                 |      |             |  |

| TDC                 | SDCLK Duty Cycle                           | 45                 | 55                 | 45                 | 55              | %    | 14, 16      |  |

| TPeriod             | SDCLK Period                               | 7.4                | 15                 | 7.4                | 15              | ns   | 14, 16      |  |

| THIGH               | SDCLK HIGH Time                            | 3.0                |                    | 1.87               |                 | ns   | 25          |  |

# AC Parameters<sup>[12]</sup> (continued)

|                    |                                       | 100     | MHz    | 133     | MHz    |      |        |

|--------------------|---------------------------------------|---------|--------|---------|--------|------|--------|

| Parameters         | Description                           | Min.    | Max.   | Min.    | Max.   | Unit | Notes  |

| TLOW               | SDCLK LOW Time                        | 2.8     |        | 1.67    |        | ns   | 26     |

| Tr / Tf            | SDCLK Rise and Fall Times             | 0.4     | 1.6    | 0.4     | 1.6    | ns   | 14, 15 |

| TCCJ               | SDCLK Cycle-to-Cycle Jitter           | -       | 250    | -       | 250    | ps   | 14, 15 |

| 48M                | -                                     |         |        | •       |        |      |        |

| TDC 48M Duty Cycle |                                       | 45      | 55     | 45      | 55     | %    | 14, 16 |

| TPeriod            | 48M Period                            | 20.829  | 20.834 | 20.829  | 20.834 | ns   | 14, 16 |

| Tr / Tf            | 48M Rise and Fall Times               | 1.0     | 2.0    | 1.0     | 2.0    | ns   | 14, 15 |

| TCCJ               | 48M Cycle-to-Cycle Jitter             |         | 350    |         | 350    | ps   | 14, 16 |

| 24M                |                                       |         |        |         |        |      |        |

| TDC                | 24MHz Duty Cycle                      | 45      | 55     | 45      | 55     | %    | 14, 16 |

| TPeriod            | 24MHz Period                          | 41.66   | 41.67  | 41.66   | 41.67  | ns   | 14, 16 |

| Tr / Tf            | 24MHz Rise and Fall Times             | 1.0     | 4.0    | 1.0     | 4.0    | ns   | 14, 15 |

| TCCJ               | 24MHz Cycle-to-Cycle Jitter           |         | 500    |         | 500    | ps   | 14, 16 |

| REF                | -                                     |         |        | •       |        |      |        |

| TDC                | REF Duty Cycle                        | 45      | 55     | 45      | 55     | %    | 14, 16 |

| TPeriod            | REF Period                            | 69.8413 | 71.0   | 69.8413 | 71.0   | ns   | 14, 16 |

| Tr / Tf            | REF Rise and Fall Times               | 1.0     | 4.0    | 1.0     | 4.0    | ns   | 14, 15 |

| TCCJ               | REF Cycle-to-Cycle Jitter             |         | 1000   |         | 1000   | ps   | 14, 16 |

| ENABLE/DISAE       | BLE and SETUP                         |         |        | •       |        |      |        |

| tpZL, tpZH         | Output Enable Delay (all outputs)     | 1.0     | 10.0   | 1.0     | 10.0   | ns   |        |

| tpLZ, tpZH         | Output Disable Delay (all outputs)    | 1.0     | 10.0   | 1.0     | 10.0   | ns   |        |

| tstable            | All Clock Stabilization from Power-up |         | 1.5    |         | 1.5    | ms   | 19     |

| tss                | Stopclock Set-up Time                 | 10.0    |        | 10.0    |        | ns   |        |

| tsh                | Stopclock Hold Time                   | 0       |        | 0       |        | ns   | 20     |

Notes:

- 12

- All outputs loaded as per maximum capacitive load table. See *Table 7*. This parameter is measured as an average over 1 $\mu$ s duration with a crystal center frequency of 14.318 MHz. 13.

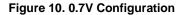

All outputs loaded per Table 7, below. Probes are placed on the pins, and measurements are acquired between 0.4V and 2.4V for 3.3V signals (see test and measurement set-up section of this data sheet). 14. 15.

Probes are placed on the pins, and measurements are acquired at 1.5V for 3.3V signals (see test and measurement set-up section of this data sheet). This measurement is applicable with Spread On or Spread OFF. Measured from  $V_{OL} = 0.175$  to  $V_{OH} = 0.525V$ . The time specified is measured from when all  $V_{DD}$ s reach their supply rail (3.3V) until the frequency output is stable and operating within the specifications. 16.

17. 18.

19.

CPU\_STP# and PCI\_STP# set-up time with respect to any PCI\_F clock to guarantee that the effected clock will stop or start at the next PCI\_F clock's rising edge. When X<sub>IN</sub> is driven from an external clock source. 20. 21.

22.

When X<sub>IN</sub> is driven from an external clock source. When crystal meets minimum 40-ohm device series resistance specification. This is required for the duty cycle on the REF clock out to be as specified. The device will operate reliably with input duty cycles up to 30/70 but the REF clock duty cycle will not be within data sheet specifications. Measured at crossing point (Vx) or where subtraction of CLK–CLK# crosses 0V. THIGH is measured at 2.4V for all non-host outputs. TLOW is measured at 0.4V for all non-host outputs. Determined as a fraction of 2\*(Trise-Tfall)/ (Trise+Tfall). For CPU load. See *Figure 10*. 23.

24.

25.

26. 27.

28.

# **Test and Measurement Set-up**

#### For Differential CPU Output Signals

The following diagram shows lumped test load configurations for the differential host clock outputs.

| Table 8. | CPU Clock | <b>Current Select</b> | Function |

|----------|-----------|-----------------------|----------|

|----------|-----------|-----------------------|----------|

| Mult0 | Board Target Trace/Term Z Reference R, Iref – Vdd (3*Rr) |                             | Output Current | V <sub>ОН</sub> @ Z |

|-------|----------------------------------------------------------|-----------------------------|----------------|---------------------|

| 0     | 50 ohms (not used)                                       | Rr = 221 1%, Iref = 5.00 mA | loh = 4*Iref   | 1.0V @ 50           |

| 1     | 50 ohms                                                  | Rr = 475 1%, Iref = 2.32 mA | loh = 6*Iref   | 0.7V @ 50           |

#### Table 9. Group Timing Relationship and Tolerances

|              | Offset       | Tolerance (or<br>Range) | Conditions | Notes   |

|--------------|--------------|-------------------------|------------|---------|

| CPU to SDCLK | TypicaL 0 ns | ±2 ns                   | CPU leads  | Note 29 |

| CPU to AGP   | TypicaL 2 ns | 1–4 ns                  | CPU leads  | Note 29 |

| CPU to ZCLK  | TypicaL 2 ns | 1–4 ns                  | CPU leads  | Note 29 |

| CPU to PCI   | Typical 2 ns | 1–4 ns                  | CPU leads  | Note 29 |

Note:

29. See Figure 10 for CPU clocks measurement point. See Figure 11 for SDCLK, AGP, ZCLK and PCI Outputs measurement point.

# Ordering Information

| Part Number | Package Type                                               | Product Flow           |

|-------------|------------------------------------------------------------|------------------------|

| IMIC9915AY  | 48-Pin Shrunk Small Outline package (SSOP)                 | Commercial, 0° to 70°C |

| IMIC9915AYT | 48-Pin Shrunk Small Outline package (SSOP) – Tape and Reel | Commercial, 0° to 70°C |

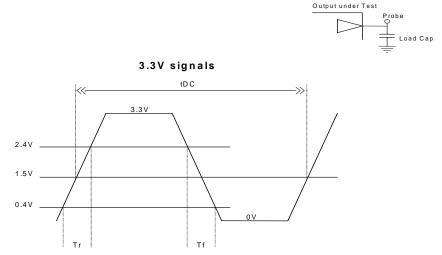

# **Package Drawing and Dimensions**

Intel is a registered trademark of Intel Corporation. Dial-a-Skew, Dial-a-Frequency, and Dial-a-Ratio are trademarks of Cypress Semiconductor. All product and company names mentioned in this document may be the trademarks of their respective holders.

© Cypress Semiconductor Corporation, 2002. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress Semiconductor product. Nor does it convey or imply any license under patent or other rights. Cypress Semiconductor does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress Semiconductor against all charges.

|                                                                                     | Document Title: C9915 Low EMI Clock Generator for Intel <sup>®</sup> 133-MHz/2-DIMM Chipset Systems<br>Document Number: 38-07123 |          |                                                                |                                                               |  |  |  |

|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|----------|----------------------------------------------------------------|---------------------------------------------------------------|--|--|--|

| REV.     ECN NO.     Issue<br>Date     Orig. of<br>Change     Description of Change |                                                                                                                                  |          |                                                                |                                                               |  |  |  |

| **                                                                                  | 112009                                                                                                                           | 03/01/02 | DMG                                                            | New Data Sheet                                                |  |  |  |

| *A                                                                                  | 117409                                                                                                                           | 08/20/02 | RGL Corrected the Ordering Information to match the Dev Master |                                                               |  |  |  |

| *В                                                                                  | 122792                                                                                                                           | 12/14/02 | RBI                                                            | Add Power up Requirements to Operating Conditions Information |  |  |  |