# 54ACQ/74ACQ646 • 54ACTQ/74ACTQ646 Quiet Series Octal Transceiver/Register with TRI-STATE® Outputs

## **General Description**

The 'ACQ/'ACTQ646 consist of registered bus transceiver circuits, with outputs, D-type flip-flops, and control circuitry providing multiplexed transmission of data directly from the input bus or from the internal storage registers. Data on the A or B bus will be loaded into the respective registers on the LOW-to-HIGH transition of the appropriate clock pin (CPAB or CPBA).

The 'ACQ/'ACTQ utilizes NSC Quiet Series technology to guarantee quiet output switching and improved dynamic threshold performance. FACT Quiet Series™ features GTO™ output control and undershoot corrector in addition to a split ground bus for superior performance.

#### **Features**

- Guaranteed simultaneous switching noise level and dynamic threshold performance

- Guaranteed pin-to-pin skew AC performance

- Independent registers for A and B busses

- Multiplexed real-time and stored data transfers

- 300 mil slim dual-in-line package

- Outputs source/sink 24 mA

- Faster prop delays than the standard 'AC/'ACT646

- 4 kV minimum ESD immunity

The information on the ACQ646 is Advanced Information only.

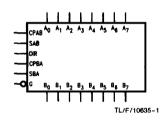

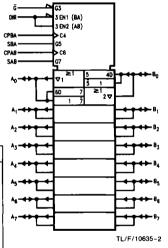

## **Logic Symbols**

| Pin Names                      | Description             |

|--------------------------------|-------------------------|

| A <sub>0</sub> -A <sub>7</sub> | Data Register A Inputs  |

|                                | Data Register A Outputs |

| B <sub>0</sub> -B <sub>7</sub> | Data Register B Inputs  |

| • •                            | Data Register B Outputs |

| CPAB, CPBA                     | Clock Pulse Inputs      |

| SAB, SBA                       | Transmit/Receive Inputs |

| G                              | Output Enable Input     |

| DIR                            | Direction Control Input |

IEEE/IEC

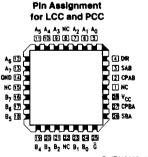

## Connection Diagrams

TL/F/10635-4