## 1 K × 8 CMOS Dual Port RAM

## Introduction

The M 67130/67140 are very low power CMOS dual port static RAMs organized as 1024 × 8. They are designed to be used as a stand-alone 8 bit dual port RAM or as a combination MASTER/SLAVE dual port for 16 bits or more width systems. The TEMIC MASTER/SLAVE dual port approach in memory system applications results in full speed, error free operation without the need for additional discrete logic.

Master and slave devices provide two independent ports with separate control, address and I/O pins that permit independent, asynchronous access for reads and writes to any location in the memory. An automatic power down feature controlled by  $\overline{\text{CS}}$  permits the onchip circuitry of each port in order to enter a very low stand by power mode.

Using an array of eight transistors (8T) memory cell and fabricated with the state of the art 1.0  $\mu$ m lithography named SCMOS, the M67130/140 combine an extremely low standby supply current (typ = 1.0  $\mu$ A) with a fast access time at 35 ns over the full temperature range. All versions offer battery backup data retention capability with a typical power consumption at less than 5  $\mu$ W.

For military/space applications that demand superior levels of performance and reliability the M 67130/140 is processed according to the methods of the latest revision of the MIL STD 883 (class B or S) and/or ESA SCC 9000.

#### **Features**

- Fast access time

35 ns to 55 ns

30 ns preliminary for commercial only

- 67130L/67140L low power

67130V/67140V very low power

- Expandable data bus to 16 bits or more using master/slave devices when using more than one device.

- On chip arbitration logic

- BUSY output flag on master

- BUSY input flag on slave

- INT flag for port to port communication

- · Fully asynchronous operation from either port

- Battery backup operation :

2 V data retention

- TTL compatible

- Single 5V ± 10 % Power Supply (1)

3.3 V versions are also available. Please consult sales.

## Interface

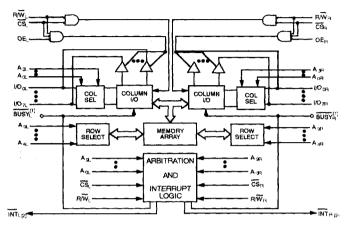

## **Block Diagram**

Notes: 1. M 67130 (MASTER): BUSY is open drain output and requires pullup resistor

M 67140 (SLAVE): BUSY in input

2. Open drain output requires pull-up resistor

## M67130/M67140

#### Pin Names

| LEFT PORT              | RIGHT PORT           | NAMES             |

|------------------------|----------------------|-------------------|

| ₹SL                    | $\overline{CS}_R$    | Chip select       |

| R/₩ <sub>L</sub>       | R/₩ <sub>R</sub>     | Write Enable      |

| <del>OE</del> L        | ŌĒ <sub>R</sub>      | Output Enable     |

| A <sub>0L</sub> - 9L   | A <sub>0R</sub> 9R   | Address           |

| I/O <sub>0L - 7L</sub> | I/O <sub>OR 7R</sub> | Data Input/Output |

| BUSYL                  | BUSYR                | Busy Flag         |

| INTL                   | INT <sub>R</sub>     | Interrupt Flag    |

| VC                     | CC                   | Power             |

| GN                     | ND                   | Ground            |

## **Functional Description**

The M 67130/M67140 has two ports with separate control, address and I/0 pins that permit independent read/write access to any memory location. These devices have an automatic power-down feature controlled by  $\overline{CS}$ .  $\overline{CS}$  controls on-chip power-down circuitry which causes the port concerned to go into stand-by mode when not selected ( $\overline{CS}$  high). When a port is selected access to the full memory array is permitted. Each port has its own Output Enable control ( $\overline{OE}$ ). In read mode, the port's  $\overline{OE}$  turns the Output drivers on when set LOW. Non-conflicting READ/WRITE conditions are illustrated in table 1.

## **Interrupt Logic**

The interrupt flag ( $\overline{\text{INT}}$ ) allows communication between ports or systems. If the user chooses to use the interrupt function, a memory location (mail box or message center) is assigned to each port. The left port interrupt flag ( $\overline{\text{INT}}_L$ ) is set when the right port writes to memory location 3FE (HEX). The left port clears the interrupt by reading address location 3FE. Similarly, the right port interrupt flag ( $\overline{\text{INT}}_R$ ) is set when the left port writes to memory location 3FF (hex), and the right port must read memory location 3FF in order to clear the interrupt flag ( $\overline{\text{INT}}_R$ ). The 8 bit message at 3FE or 3FF is user-defined. If the interrupt function is not used, address locations 3FE and 3FF are not reserved for mail boxes but become part of the RAM. See table 3 for the interrupt function.

#### **Arbitration Logic**

The arbitration logic will resolve an address match or a chip select match down to a minimum of 5 ns and determine which port has access. In all cases, an active BUSY flag will be set for the inhibited port.

The  $\overline{BUSY}$  flags are required when both ports attempt to access the same location simultaneously. Should this conflict arise, on-chip arbitration logic will determine which port has access and set the  $\overline{BUSY}$  flag for the inhibited port.  $\overline{BUSY}$  is set at speeds that allow the processor to hold the operation with its associated address and data. It should be noted that the operation is invalid for the port for which  $\overline{BUSY}$  is set LOW. The inhibited port will be given access when  $\overline{BUSY}$  goes inactive.

A conflict will occur when both left and right ports are active and the two addresses coincide. The on-chip arbitration determines access in these circumstances. Two modes of arbitration are provided: (1) if the addresses match and are valid before  $\overline{CS}$  on-chip control logic arbitrates between  $\overline{CS}_L$  and  $\overline{CS}_R$  for access; or (2) if the  $\overline{CS}$ s are low before an address match, on-chip control logic arbitrates between the left and right addresses for access (refer to table 2). The inhibited port's  $\overline{BUSY}$  flag is set and will reset when the port granted access completes its operation in both arbitration modes.

#### **Data Bus Width Expansion**

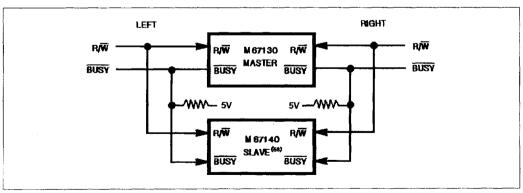

#### Master/Slave Description

Expanding the data bus width to 16 or more bits in a dual-port RAM system means that several chips may be active simultaneously. If every chip has a hardware arbitrator, and the addresses for each chip arrive at the same time one chip may activate its L BUSY signal while another activates its R BUSY signal. Both sides are now busy and the CPUs will wait indefinitely for their port to become free.

To overcome this "Busy Lock-Out" problem, MHS has developed a MASTER/SLAVE system which uses a single hardware arbitrator located on the MASTER. The SLAVE has BUSY inputs which allow direct interface to the MASTER with no external components, giving a speed advantage over other systems.

When dual-port RAMs are expanded in width, the SLAVE RAMs must be prevented from writing until the BUSY input has been settled. Otherwise, the SLAVE chip may begin a write cycle during a conflict situation. On the opposite, the write pulse must extend a hold time beyond BUSY to ensure that a write cycle occurs once the conflict is resolved. This timing is inherent in all dual-port memory systems where more than one chip is active at the same time.

The write pulse to the SLAVE must be inhibited by the MASTER's maximum arbitration time. If a conflict then occurs, the write to the SLAVE will be inhibited because of the MASTER's  $\overline{BUSY}$  signal.

#### **Truth Table**

Table 1: Non Contention Read/Write Control<sup>(4)</sup>

| Secretary and Apolla or the Introduction |   | THE PERSON NAMED OF THE PERSON | 20-7                | BUNCTION :                                            |

|------------------------------------------|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------------------------------------------------------|

| Х                                        | н | x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Z                   | Port Disabled and in Power Down Mode. ICCSB or ICCSB1 |

| L                                        | L | X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | DATAIN              | Data on Port Written into memory <sup>(2)</sup>       |

| Н                                        | L | L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | DATA <sub>OUT</sub> | Data in Memory Output on Port <sup>(3)</sup>          |

| н                                        | L | н                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Z                   | High Impedance Outputs                                |

- Notes: 1.  $A_{OL} \sim A_{9L} \neq A_{OR} \sim A_{9R}$ . 2. If  $\overline{BUSY} = L$ , data is not written.

- 3. If  $\overline{BUSY} = L$ , data may not be valid, see  $t_{WDD}$  and  $t_{DDD}$  timing.

- 4. H = HIGH, L = LOW, X = DON'T CARE, Z = HIGH IMPEDANCE.

Table 2: Arbitration(6)

| LEFT        | FORE                                | Might         | PORT                                | FLAC       | S (5)   |                      |

|-------------|-------------------------------------|---------------|-------------------------------------|------------|---------|----------------------|

| St.         | Au - Au                             | CSa           | Act - Ace                           | <b>建国政</b> | - AUGUS | FUNCTION             |

| Н.          | х                                   | н             | X                                   | Н          | Н       | No Contention        |

| L           | Any                                 | Н             | X                                   | н          | н       | No Contention        |

| Н           | X                                   | L             | Any                                 | Any H H    |         | No Contention        |

| L           | ≠ A <sub>0R</sub> A <sub>9R</sub>   | L             | ≠ A <sub>0L</sub> – A <sub>9L</sub> | н          | н       | No Contention        |

| ADDRESS ARI | BITRATION WIT                       | H CE LOW BEF  | ORE ADDRESS N                       | MATCH      |         |                      |

| L           | LV5R                                | L             | LV5R                                | н          | L       | L-Port Wins          |

| L           | RV5L                                | L.            | RV5L                                | L          | H       | R-Port Wins          |

| L           | Same                                | L,            | Same                                | Н          | L       | Arbitration Resolved |

| L           | Same                                | L,            | Same                                | L          | H       | Arbitration Resolved |

| CS ARBITRAT | ION WITH ADD                        | RESS MATCH BI | EFORE CS                            |            |         |                      |

| LL5R        | $= A_{0R} - A_{9R}$                 | LL5R          | $\approx A_{0L} - A_{9L}$           | H          | L       | L-Port Wins          |

| RL5L        | $= A_{0R} - A_{9R}$                 | RL5L          | $= A_{0L} - A_{9L}$                 | L          | Н       | R-Port Wins          |

| LW5R        | $= A_{0R} \sim A_{9R}$              | LW5R          | $\approx A_{0L} - A_{9L}$           | Н          | L.      | Arbitration Resolved |

| LW5R        | = A <sub>0R</sub> ~ A <sub>9R</sub> | LW5R          | $= A_{OL} - A_{OL}$                 | Ĺ          | н       | Arbitration Resolved |

- Notes: 5. INT Flags Don't Care.

- 6. X = DON'T CARE, L = LOW, H = HIGH. LV5R = Left Address Valid ≥ 5 ns before right address.

- RV5L = Right Address Valid ≥ 5 ns before left address.

- Same = Left and Right Addresses match within 5 ns of each other.

- LLSR = Left  $\overline{CS}$  = LOW  $\geq 5$  ns before Right  $\overline{CS}$ .

- RL5L = Right  $\overline{CS}$  = LOW  $\geq 5$  ns before left  $\overline{CS}$ . LW5R = Left and Right  $\overline{CS}$  = LOWwithin 5 ns of each other.

Table 3: Interrupt Flag (7, 10)

|                  | gift is         | LEFT | PORT      |                  |                  |                 | RIGHT | PORT    |                  | TUNCTION                          |

|------------------|-----------------|------|-----------|------------------|------------------|-----------------|-------|---------|------------------|-----------------------------------|

| R/W <sub>L</sub> | CS <sub>1</sub> | OEL  | Aor. Asr. | INT <sub>L</sub> | R/W <sub>B</sub> | CS <sub>k</sub> | OFR   | AOR-ASS | M,               | PONCIAGO.                         |

| L                | L               | Х    | 3FF       | X                | х                | х               | X     | X       | L(8)             | Set Right INT <sub>R</sub> Flag   |

| X                | X               | х    | х         | х                | X                | L               | L     | 3FF     | H <sup>(9)</sup> | Reset Right INT <sub>R</sub> Flag |

| X                | X               | Х    | х         | L(9)             | L                | L               | Х     | 3FE     | X                | Set Left INT <sub>L</sub> Flag    |

| х                | L               | L    | 3FE       | H(8)             | X                | Х               | X     | X       | х                | Reset Left INT <sub>L</sub> Flag  |

Notes: 7. Assumes  $\overline{BUSY}_L = \overline{BUSY}_R = H$ .

- 8. If  $\overline{BUSY}_{L} = L$ , then NC.

- 9. If  $\overline{B}\overline{U}\overline{S}\overline{Y}_R = L$ , then NC.

- 10.  $H \approx HIGH$ , L = LOW, X = DON'T CARE, NC = NO CHANGE.

## **Electrical Characteristics**

#### **Absolute Maximum Ratings**

#### \* Notice

Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extented periods may affect reliability.

| GRENATING RANGE | OPERATING SUPPLY VOCIDAGE        | OPERATORS DEMPERATURE |

|-----------------|----------------------------------|-----------------------|

| Military        | $V_{CC} = 5 \text{ V} \pm 10 \%$ | 55 °C to + 125 °C     |

| Automotive      | $V_{CC} = 5 \text{ V} \pm 10 \%$ | -40 °C to + 125 °C    |

| Industrial      | $V_{CC} = 5 \text{ V} \pm 10 \%$ | -40 °C to + 85 °C     |

| Commercial      | $V_{CC} = 5 V \pm 10 \%$         | 0 °C to + 70 °C       |

#### **DC Parameters**

| a di Supre<br>Para di Supre<br>La di Subsessione |                                                                  |        |             |             |             |             |             |             |             | t en     | <b>14</b>  |

|--------------------------------------------------|------------------------------------------------------------------|--------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|----------|------------|

|                                                  | <b>《大学》 《 新疆 100 《 新疆 100 》</b>                                  |        |             |             | Mark I      |             | 4.4         | 1           | a fra       |          |            |

| I <sub>CCSB (11)</sub>                           | Standby supply current (Both ports TTL level inputs)             | V<br>L | 5<br>40     | 5<br>40     | 5<br>50     | 5<br>40     | 5<br>50     | 5<br>40     | 5<br>50     | mA<br>mA | Max<br>Max |

| I <sub>CCSB1 (12)</sub>                          | Standby supply current (Both ports CMOS level inputs)            | V<br>L | 100<br>1000 | 100<br>1000 | 200<br>2000 | 100<br>1000 | 200<br>2000 | 100<br>1000 | 200<br>2000 | μA<br>μA | Max<br>Max |

| I <sub>CCOP (13)</sub>                           | Operating supply current (Both ports active)                     | V<br>L | 160<br>175  | 145<br>155  | 180<br>200  | 135<br>150  | 150<br>170  | 130<br>140  | 140<br>170  | mA<br>mA | Max<br>Max |

| I <sub>CCOP1 (14)</sub>                          | Operating supply current<br>(One port active – One port standby) | V<br>L | 100<br>105  | 85<br>95    | 100<br>110  | 75<br>85    | 85<br>90    | 70<br>80    | 75<br>80    | mA<br>mA | Max<br>Max |

Notes: 11,  $\overline{CS}_L = \overline{CS}_R \ge 2.2 \text{ V}.$

12.  $\overline{CS}_L = \overline{CS}_R \ge VCC - 0.2 \text{ V}.$

13. Both ports active – Maximum frequency – Outputs open –  $\overline{OE}$  = VIH.

14. One port active (f = fMAX) – Output open – One port stand-by TTL or CMOS Level inputs –  $\overline{CS}_L = \overline{CS}_R \ge 2.2 \text{ V}$ .

| PARAMETE              | R DESCRIPTION                                                        | 67130-38/35/45/55<br>67140-36/35/45/55 | UNIT | VALUE |

|-----------------------|----------------------------------------------------------------------|----------------------------------------|------|-------|

| II/O <sub>(15)</sub>  | Input/Output leakage current                                         | +/- 10                                 | μΑ   | Max   |

| VIL(16)               | Input low voltage                                                    | 0.8                                    | v    | Max   |

| VIH(16)               | Input high voltage                                                   | 2.2                                    | V    | Min   |

| VOL(17)               | Output low voltage (I/O <sub>t)</sub> -I/O <sub>7</sub> )            | 0.4                                    | v    | Max   |

| VOL                   | Open dra n output low voltage<br>(BUSY, INT) I <sub>OL</sub> = 16 mA | 0.5                                    | ٧    | Max   |

| VOH(17)               | Output high voltage                                                  | 2.4                                    | v    | Min   |

| C IN(21)              | Input capacitance                                                    | 5                                      | pF   | Max   |

| C OUT <sub>(21)</sub> | Output capacitance                                                   | 7                                      | pF   | Max   |

**Notes:** 15.  $V_{CC} = 5.5 \text{ V}$ ,  $V_{IR} = G_{IR} \text{ of to } V_{CC}$ ,  $\overline{CS} = V_{IH}$ ,  $V_{OU} = 0$  to  $V_{CC}$ .

16. VIH max =  $V_{CC} + 0.3 \text{ V}$ , VIL min - 0.3 V or -1 V pulse width 50 ns.

17.  $V_{CC}$  min, IOL = 4 mA, IOH = -4 mA.

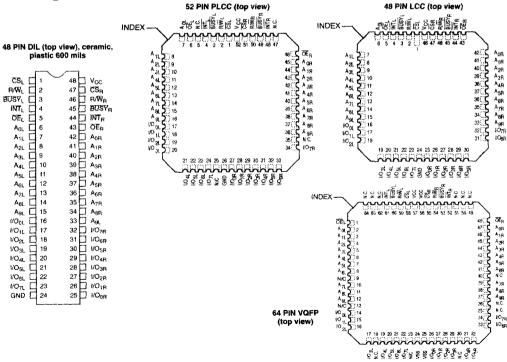

## **Data-Retention Mode**

MHS CMOS RAMs are designed with battery backup in mind. Data retention voltage and supply current are guaranteed over temperature. The following rules insure data retention:

1 – Chip select  $(\overline{CS})$  must be held high during data retention ; within Vcc to VCC\_{DR}.

$2 - \overline{CS}$  must be kept between  $V_{CC} - 0.2 \text{ V}$  and 70 % of Vcc during the power up and power down transitions.

3 - The RAM can begin operation > tRC after Vcc reaches the minimum operating voltage (4.5 volts).

#### Timing

| PARAMETER          | ASSECCIONDENGUIS (16)     | OUM. | X<br>Anti-Ped<br>Acto | usur |

|--------------------|---------------------------|------|-----------------------|------|

| ICC <sub>DR1</sub> | @ VCC <sub>DR</sub> = 2 V | 5    | 20                    | μΑ   |

| ICC <sub>DR2</sub> | @ VCC <sub>DR</sub> ≈ 3 V | 10   | 30                    | μΑ   |

**Notes:** 18.  $\overline{CS}$  = Vcc, Vin = Gnd to Vcc. 19.  $t_{RC}$  = Read cycle time.

#### **AC Test Conditions**

Input Pulse Levels : GND to 3.0 V Input Rise/Fall Times : 5 ns

Input Timing Reference Levels: 1.5 V

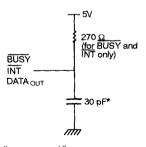

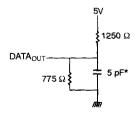

Output Reference Levels: 1.5 V Output Load: see figures 1, 2

Figure 1. Output Load.

\* Including scope and jig

Figure 2. Output load.

(For tHZ, tLZ, tWZ, and tOW)

#### **AC Parameters**

| READ C |                 |                                      |    | 1000 |    |    |    |    |    | 8  | enter. |

|--------|-----------------|--------------------------------------|----|------|----|----|----|----|----|----|--------|

| TAVAVR | t <sub>RC</sub> | Read cycle time                      | 30 | -    | 35 |    | 45 |    | 55 | -  | лs     |

| TAVQV  | t <sub>AA</sub> | Address access time                  | -  | 30   |    | 35 | -  | 45 | -  | 55 | ns     |

| TELQV  | tACS            | Chip Select access time (22)         | -  | 30   |    | 35 | -  | 45 | _  | 55 | ns     |

| TGLQV  | IAOE            | Output enable access time            |    | 15   | _  | 25 | -  | 30 | -  | 35 | ns     |

| TAVQX  | фн              | Output hold from address change      | 0  |      | 0  | _  | 0  | -  | 0  |    | ns     |

| TELQZ  | tLZ             | Output low Z time (20, 21)           | 0  |      | 5  |    | 5  |    | 5  | -  | ns     |

| TEHQZ  | tHZ             | Output high Z time (20, 21)          | _  | 12   | -  | 15 | -  | 20 | -  | 30 | ns     |

| TPU    | ŧ₽U             | Chip Select to power up time (21)    | 0  | -    | 0  |    | 0  | _  | 0  | -  | ns     |

| TPD    | tpD             | Chip disable to power down time (21) | -  | 50   | -  | 50 |    | 50 | -  | 50 | ns     |

Notes:

- 20. Transition is measured ± 500 mV from low or high impedance voltage with load (figures 1 and 2).

- 21. This parameter is guaranteed but not tested.

22. To access RAM CS = VIL.

- 23. STD symbol.

- 24. ALT symbol.

- (\*). Commercial only, not available in DIP.

- (\*\*). DIP package available for commercial only.

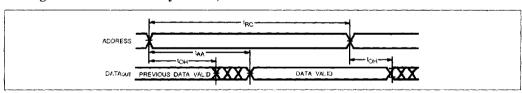

## Timing Waveform of Read Cycle no 1, Either Side (25, 26, 28)

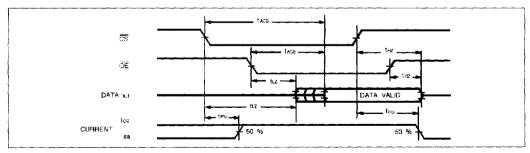

## Timing Waveform of Read Cycle no 2, Either Side (25, 27, 29)

- 25. R/W is high for read cycles.

- 26. Device is continuously enabled,  $\overline{CS} = VIL$ .

- 27. Addresses valid prior to or coincident with CS transition low.

- 28. OE = VIL.

- 29. To access RAM,  $\overline{CS} = VIL$ .

## M67130/M67140

#### **AC Parameters**

|        |                 |                                              |    |    |    |    |    |    |    | 100 | <b>CHT</b> |

|--------|-----------------|----------------------------------------------|----|----|----|----|----|----|----|-----|------------|

| TAVAVW | twc             | Write cycle time                             | 30 | _  | 35 | -  | 45 | -  | 55 |     | ns         |

| TELWH  | tsw             | Chip select to end of write (32)             | 25 | -  | 30 |    | 35 | _  | 40 |     | ns         |

| TAVWH  | t <sub>AW</sub> | Address valid to end of write                | 25 | _  | 30 | _  | 35 | _  | 40 |     | ns         |

| TAVWL  | t <sub>AS</sub> | Address Set-up Time                          | 0  | _  | 0  |    | 0  | _  | 0  | _   | ns         |

| TWLWH  | t <sub>WP</sub> | Write Pulse Width                            | 25 | _  | 30 |    | 35 | _  | 40 | _   | ns         |

| TWHAX  | twr             | Write Recovery Time                          | 0  |    | 0  | _  | 0  | _  | 0  | -   | ns         |

| TDVWH  | tow             | Data Valid to end of write                   | 15 | -  | 20 |    | 20 | -  | 20 | ~   | ns         |

| TGHQZ  | tHZ             | Output high Z time (30, 31)                  | -  | 12 | -  | 15 | -  | 20 | -  | 30  | ns         |

| TWHDX  | t <sub>DH</sub> | Data hold time (33)                          | 0  | -  | 0  | -  | 0  | _  | 0  |     | ns         |

| TWLQZ  | twz.            | Write enable to output in high Z (30, 31)    | -  | 12 | -  | 15 | -  | 20 | -  | 30  | ns         |

| TWHQX  | tow             | Output active from end of write (30, 31, 33) | 0  | _  | 0  | -  | 0  | -  | 0  | -   | ns         |

Notes: 30. Transition is measured  $\pm$  500 mV from low or high impedance voltage with load (figures 1 and 2).

31. This parameter is guaranteed but not tested.

32. To access RAM CS = VIL.

This condition must be valid for entire tsw time.

33. The specification for t<sub>DH</sub> must be met by the device supplying write data to the RAM under all operating conditions. Although t<sub>DH</sub> and t<sub>OW</sub> values vary over voltage and temperature, the actual t<sub>DH</sub> will always be smaller than the actual t<sub>OW</sub>.

34. STD symbol.

35. ALT symbol.

(\*). Commercial only. Not available in DIP.

(\*\*). DIP package available for commercial only.

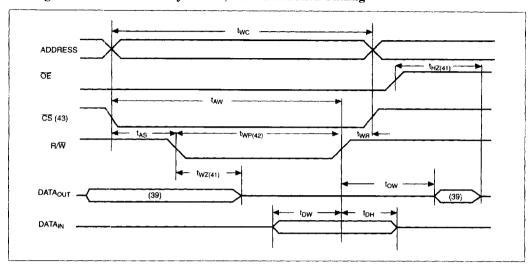

## Timing Waveform of Write Cycle no 1, R/W Controlled Timing (36, 37, 38, 42)

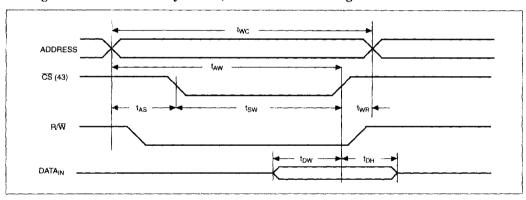

## Timing Waveform of Write Cycle no 2, CS Controlled Timing (36, 37, 38, 40)

- Notes:

- 36. R/W must be high during all address transitions.

- 37. A write occurs during the overlap ( $t_{SW}$  or  $t_{WP}$ ) of a low  $\overline{CS}$  and a low  $R/\overline{W}$ .

- 38. two is measured from the earlier of CS or R/W going high to the end of write cycle.

- 39. During this period, the I/O pins are in the output state, and input signals must not be applied.

- If the CS low transition occurs simultaneously with or after the R/W low transition, the outputs remain in the high impedance state.

- 41. Transition is measured ± 500 mV from steady state with a 5 pF load (including scope and jig). This parameter is sampled and not 100 % tested.

- 42. If  $\overrightarrow{OE}$  is low during a R/W controlled write cycle, the write pulse width must be the larger of  $t_{WP}$  or  $(t_{WZ} + t_{DW})$  to allow the I/O drivers to turn off and data to be placed on the bus for the required  $t_{DW}$ . If  $\overrightarrow{OE}$  is high during an R/W controlled write cycle, this requirement does not apply and the write pulse can be as short as the specified  $t_{WP}$

- 43. To access RAM.  $\overline{CS} = VIL$ .

## M67130/M67140

#### **AC Parameters**

| Symbol           | , PARAMETER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       | 0-30(*)<br>0-30(*) |      | 130-35<br>140-35 | Section 1985 | 130-45<br>1 <b>48-45</b> | Service of the Police | 13 <b>4</b> -55<br>7140-55 |      |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------------------|------|------------------|--------------|--------------------------|-----------------------|----------------------------|------|

|                  | IUSY TIMING (Far )467120 maly)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | MIN.  | MAX.               | MIN. | MAX.             | MIN.         | MAX                      | MIN.                  | MAX.                       | UNIT |

|                  | along the state of | PREIA | MINARY             |      |                  |              |                          |                       |                            |      |

| t <sub>BAA</sub> | BUSY Access time to address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       | 30                 | -    | 35               | _            | 35                       | -                     | 45                         | ns   |

| <sup>‡</sup> BDA | BUSY Disable time to address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -     | 25                 | -    | 30               | _            | 35                       |                       | 40                         | ns   |

| t <sub>BAC</sub> | BUSY Access time to Chip Select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       | 25                 | _    | 30               | _            | 30                       |                       | 35                         | ns   |

| <sup>t</sup> BDC | BUSY Disable time to Chip Select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       | 25                 |      | 25               | ,            | 25                       | -                     | 30                         | ns   |

| twDD             | Write Pulse to data delay (44)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -     | 55                 | -    | 60               |              | 70                       | -                     | 80                         | ns   |

| t <sub>DDD</sub> | Write data valid to read data delay (44)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -     | 33                 | -    | 35               | -            | 45                       | -                     | 55                         | ns   |

| t <sub>APS</sub> | Arbitration priority set-up time (45)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5     |                    | 5    |                  | 5            | -                        | 5                     | _                          | ns   |

| <sup>†</sup> BOD | BUSY disable to valid data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       | Note 46            |      | Note 46          | _            | Note 46                  | -                     | Note 46                    | ns   |

| P                | BUSY TIMING (For M 67140 only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       |                    |      |                  |              |                          |                       |                            | ns   |

| twB              | Write to BUSY input (47)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0     | -                  | 0    |                  | 0            |                          | 0                     | -                          | ns   |

| (wH              | Write hold after BUSY (48)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 20    |                    | 20   | -                | 20           | -                        | 20                    | -                          | ns   |

| twdd             | Write pulse to data delay (49)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -     | 55                 | -    | 60               | -            | 70                       | -                     | 80                         | ns   |

| todo             | Write data valid to read data delay (49)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -     | 30                 | _    | 35               | -            | 45                       | -                     | 55                         | ns   |

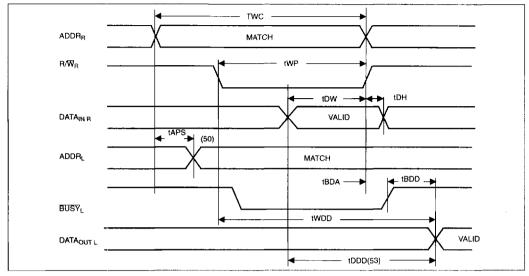

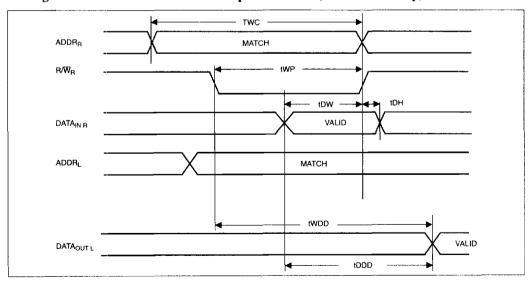

- Notes: 44. Port-to-port delay through RAM cells from writing port to reading port, refer to "Timing Waveform of Read with BUSY (For M67130 only)".

- 45. To ensure that the earlier of the two ports wins.

- 46.  $t_{BDD}$  is a calculated parameter and is the greater of 0,  $t_{WDD}$   $t_{WP}$  (actual) or  $t_{DDD}$   $t_{DW}$  (actual).

- 47. To ensure that the write cycle is inhibited during contention.

- 48. To ensure that a write cycle is completed after contention.

- 49. Port-to-port delay through RAM cells from writing port to reading port, refer to "Timing Waveforms of Read with Port to port delay (For M67140 only)".

- (\*). Commercial only. Not available in DIP.

- (\*\*). DIP package available for commercial only.

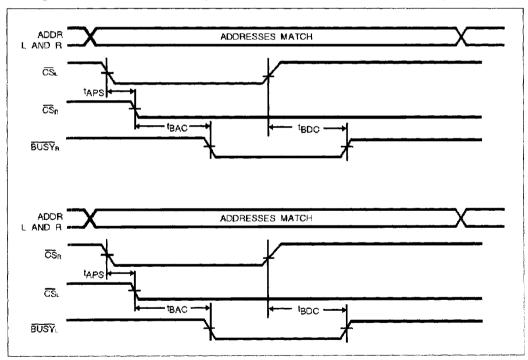

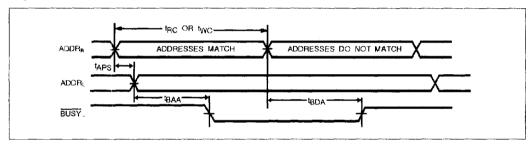

## Timing Waveform of Read with BUSY (50, 51, 52) (For M67130)

Notes:

- 50. To ensure that the earlier of the two port wins.

- 51. Write cycle parameters should be adhered to, to ensure proper writing.

- 52. Device is continuously enabled for both ports.

- 53. OE at L for the reading port.

## Timing Waveform of Write with Port-to-port (54, 55, 56) (For M67140 only)

Notes

- 54. Assume  $\overline{BUSY} = H$  for the writing port, and  $\overline{OE} = L$  for the reading port.

- 55. Write cycle parameters should be adhered to, to ensure proper writing.

- 56. Device is continuously enabled for both ports.

## Timing Waveform of Write with BUSY (For M67140)

## Timing Waveform of Contention Cycle no 1, $\overline{CS}$ Arbitration (For M67130 only)

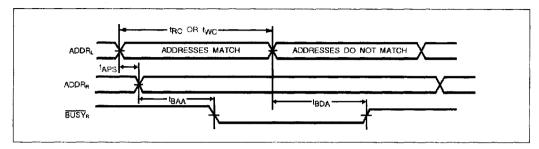

# Timing Waveform of Contention Cycle $n^o$ 2, Address Valid Abritration (For M67130 only) $^{(57)}$

## Left Address Valid First:

## Right Address Valid First:

Note: 57.  $CS_L = \overline{CS}_R = V_{IL}$

## 16 Bit Master/Slave Dual-port Memory Systems

Note: 58. No arbitration in M67140 (SLAVE). BUSY-IN inhibits write in M67140 (SLAVE).

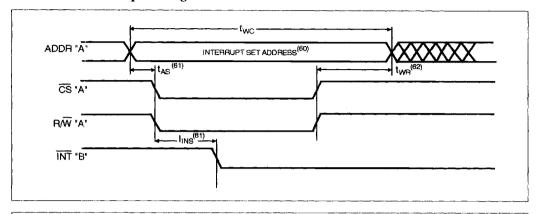

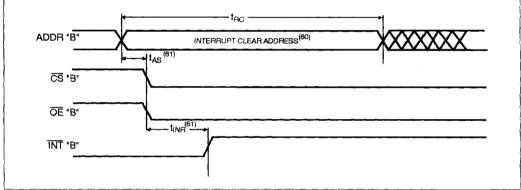

## Waveform of Interrupt Timing (59)

Notes: 59. /

- 59. All timing is the same for left and right ports. Port "A" may be either the left or right port. Port "B" is the port opposite from "A".

- 60. See interrupt thruth table.

- 61. Timing depends on which enable signal is asserted last.

- 62. Timing depends on which enable signal is de-asserted first.

# AC Electrical Characteristics over the Full Operating Temperature and Supply Voltage Range

| INTERRUPT<br>TIMING | PARAMETER            | 67130/ | 140-30<br>!) |     | 140-35<br>*) | 67130/ | 140-45 | 67130/ | 140-55 | UNIT |

|---------------------|----------------------|--------|--------------|-----|--------------|--------|--------|--------|--------|------|

| SYMMOL              |                      | MIN.   | MAX          | MIN | MAX.         | MIN.   | MAX.   | MIN.   | MAX.   |      |

| tAS                 | Address set-up time  | 0      | -            | 0   | 1            | 0      | -      | 0      |        | ns   |

| twR                 | Write recovery time  | 0      | -            | 0   | _            | 0      | -      | 0      | -      | ns   |

| tins                | Interrupt set time   | -      | 30           |     | 35           |        | 40     | -      | 45     | ns   |

| ting                | Interrupt reset time |        | 30           |     | 35           | -      | 40     | -      | 45     | ns   |

<sup>(\*).</sup> Commercial only. Not available in DIP.

<sup>(\*\*).</sup> DIP package available for commercial only.

= Dry pack

: D

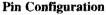

## **Ordering Information**

TEMPERATURE RANGE PACKAGE DEVICE SPEED FLOW C 67130V -1K = 48 pin DIL ceramic 600 mils 30 ns CK = 48 pin DIL side-brazed 600 mils 35 ns 4K = 48 pin LCC45 ns S3 = 52 pin PLCC55 ns 3K = 48 pin DIL plastic 600 mils RD = 64 pin VQFPKK = Flat pack 48 pins 400 mils 67130 = 8K (1K × 8) MasterQ3 = CQPJ 52 $67140 = 8K (1K \times 8)$  Slave 0 = Dice form= Low power = Very low power blank = MHS standards /883 MIL STD 883 Class B or S C = Commercial $0^{\circ}$  to  $+70^{\circ}$ C P883 = MIL STD 883 + PIND test -40° to +85°C I = Industrial SB/SC = SCC 9000 level B/C -40° to +125°C A = AutomotiveSHXXX = Special customer request -55° to +125°C M = MilitaryFHXXX = Flight models (space) -55° to +125°C S = SpaceEHXXX = Engineering models (space) MHXXX = Mechanical parts (space) LHXXX = Life test parts (space) = Tape and reel : R : RD = Tape and reel dry pack

## Military and Space Versions

The following tables give package/consumption/access time/process flow available combinations

| Temp. | Packages                        | <sub>je</sub> "Cousa       | coption :                             | Aq                         | ang Time                   | ((o),            | Section 1                                 |             |             |

|-------|---------------------------------|----------------------------|---------------------------------------|----------------------------|----------------------------|------------------|-------------------------------------------|-------------|-------------|

|       |                                 | V                          | L                                     | 35                         | 45                         | 55               | Mil flows<br>(including<br>SMD5962–86875) | Mil flows   | Space flows |

| М     | 1K<br>4K<br>CK<br>KK<br>Q3<br>0 | •<br>•<br>•<br>X<br>•<br>X | * * * * * * * * * * * * * * * * * * * | •<br>•<br>•<br>X<br>•<br>X | •<br>•<br>•<br>X<br>•<br>X | •<br>•<br>•<br>X | * * * * * * * * *                         |             |             |

| S     | 4K<br>CK<br>KK<br>0             | •<br>•<br>X<br>X           | •                                     |                            | •<br>•<br>X<br>X           | •<br>•<br>X      |                                           | •<br>•<br>X | •<br>X      |

| Terry. | -  | C   |   | Acq | in The | (trist): | Polynoma.<br>System                       | RT po<br>Gra | ora<br>OE   |

|--------|----|-----|---|-----|--------|----------|-------------------------------------------|--------------|-------------|

|        |    | v   | L | 35  | 45     | 55       | Mil flows<br>(including<br>SMD5962–86875) | Mil flows    | Space flows |

| М      | łK | •   | • | •   | •      | •        | •                                         |              |             |

|        | 4K | •   | • | •   | •      | •        | •                                         |              |             |

|        | CK | ) • | • | •   | •      | •        | •                                         | ]            |             |

|        | KK | x   | Х | X   | X      | X        | X                                         |              |             |

|        | Q3 | •   | • | •   | •      | •        | •                                         |              |             |

|        | 0  | X   | • | X   | х      | •        | •                                         |              |             |

| S      | 4K | •   |   |     | •      | •        |                                           | •            | •           |