# 3.3V CMOS OCTAL EDGE-TRIGGERED D-TYPE FLIP-FLOP WITH 3-STATE OUTPUTS, 5 VOLT TOLERANT I/O AND BUS-HOLD

### IDT74LVCH374A

# **FEATURES:**

- 0.5 MICRON CMOS Technology

- ESD > 2000V per MIL-STD-883, Method 3015;

- > 200V using machine model (C = 200pF, R = 0)

- 1.27mm pitch SOIC, 0.65mm pitch SSOP,

0.635mm pitch QSOP, 0.65mm pitch TSSOP packages

- Extended commercial range of 40°C to +85°C

- VCC =  $3.3V \pm 0.3V$ , Normal Range

- VCC = 2.3V to 3.6V, Extended Range

- CMOS power levels (0.4µW typ. static)

- Rail-to-Rail output swing for increased noise margin

- All inputs, outputs and I/O are 5 Volt tolerant

- Supports hot insertion

### Drive Features for LVCH374A:

- High Output Drivers: ±24mA

- Reduced system switching noise

### APPLICATIONS:

- 5V and 3.3V mixed voltage systems

- Data communication and telecommunication systems

### **DESCRIPTION:**

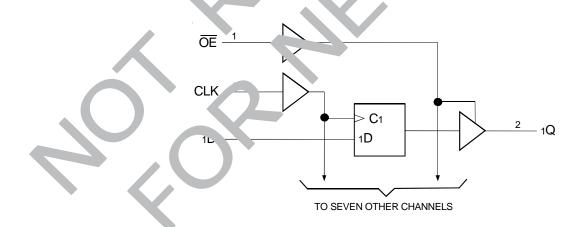

The LVCH374A octal edge triggered D-Type flip-flop is built using advanced dual metal CMOS technology. The device features 3-state outputs designed specifically for driving highly capacitive or relatively low-impedance loads. The LVCH374A is particularly suitable for implementing buffer registers, input-output (I/O) ports, bidirectional bus drivers, and working registers.

On the positive transition of the clock (CLK) input, the Q outputs are set to the logic levels set up at the data (D) inputs.

A buffered output-enable  $(\overline{OE})$  input can be used to place the eight outputs in either a normal logic state (high or low logic levels) or a high-impedance state. In the high-impedance state, the outputs neither load nor drive the bus lines significantly.  $\overline{OE}$  does not affect internal operations of the latch. Old data can be retained or new data can be entered while the outputs are in the high-impedance state.

The LVCH374A has been designed with a  $\pm 24$ mA output driver. This driver is capable of driving a moderate to heavy load while maintaining speed performance.

Inputs can be driven from either 3.3V or 5V devices. This feature allows the use of this device as a translator in a mixed 3.3V/5V system environment.

The LVCH374A has "bus-hold" which retains the inputs' last state whenever the input goes to a high-impedance. This prevents floating inputs and eliminates the need for pull-up/down resistors.

# FUNCTIONAL BLOCK DIAGRAM

EXTENDED COMMERCIAL TEMPERATURE RANGE

OCTOBER 1999

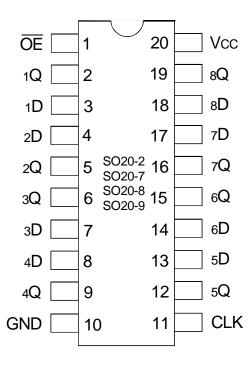

# **PIN CONFIGURATION**

SOIC/ SSOP/ QSOP/ TSSOP TOP VIEW

# PIN DESCRIPTION

| Pin Names | Description                      |

|-----------|----------------------------------|

| ŌĒ        | Output-enable Input (Active LOW) |

| CLK       | Clock Input                      |

| хD        | Data Inputs <sup>(1)</sup>       |

| ΩX        | Data Outputs                     |

#### NOTE:

These pins have "Bus-hold". All other pins are standard inputs, outputs, or I/Os.

# ABSOLUTE MAXIMUM RATINGS (1)

| Symbol | Description                          | Max.          | Unit |

|--------|--------------------------------------|---------------|------|

| VTERM  | Terminal Voltage with Respect to GND | - 0.5 to +6.5 | V    |

| Tstg   | Storage Temperature                  | - 65 to +150  | °C   |

| lout   | DC Output Current                    | - 50 to +50   | mA   |

| lik    | Continuous Clamp Current,            | - 50          | mA   |

| Іок    | VI < 0 or Vo < 0                     |               |      |

| Icc    | Continuous Current through           | ±100          | mA   |

| Iss    | each Vcc or GND                      |               |      |

#### NOTE:

Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

# CAPACITANCE (TA = +25°C, f = 1.0MHz)

| Symbol | Parameter <sup>(1)</sup> | Conditions | Тур. | Max. | Unit      |

|--------|--------------------------|------------|------|------|-----------|

| CIN    | Input Capacitance        | VIN = 0V   | 4.5  | 6    | pF        |

| Соит   | Output<br>Capacitance    | Vout = 0V  | 5.5  | 8    | pF        |

| CI/O   | I/O Port<br>Capacitance  | VIN = 0V   | 6.5  | 8    | pF        |

|        |                          |            |      |      | 8LVC Link |

#### NOTE:

1. As applicable to the device type.

# FUNCTION TABLE (each flip-flop) (1)

|    | Inputs   |    | Outputs |

|----|----------|----|---------|

| ŌĒ | CLK      | хD | Ох      |

| L  | <b>↑</b> | Н  | Н       |

| L  | 1        | L  | L       |

| L  | H or L   | Х  | $Q_0$   |

| Н  | Х        | Х  | Z       |

### NOTE:

- 1. H = HIGH Voltage Level

- L = LOW Voltage Level

- X = Don't Care

- Z = High-Impedance

- ↑ = LOW-to-HIGH Transition

- Q<sub>0</sub> = Level of Q before the indicated steady-state input conditions were established.

# DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE

Following Conditions Apply Unless Otherwise Specified:

Operating Condition: TA = - 40°C To +85°C

| Symbol       | Parameter                                   | -                                                   | Test Conditions              | Min. | Typ. <sup>(1)</sup> | Max.  | Unit |

|--------------|---------------------------------------------|-----------------------------------------------------|------------------------------|------|---------------------|-------|------|

| VIH          | Input HIGH Voltage Level                    | Vcc = 2.3V to 2.7V                                  |                              | 1.7  | _                   | -     | ٧    |

|              |                                             | Vcc = 2.7V to 3.6V                                  |                              | 2    | _                   | _     | 1    |

| VIL          | Input LOW Voltage Level                     | Vcc = 2.3V to 2.7V                                  |                              | _    | _                   | 0.7   | V    |

|              |                                             | Vcc = 2.7V to 3.6V                                  |                              | _    | _                   | 0.8   | 1    |

| lih<br>lil   | Input Leakage Current                       | Vcc = 3.6V                                          | VI = 0 to 5.5V               | _    | _                   | ±5    | μA   |

| lozн         | High Impedance Output Current               | Vcc = 3.6V                                          | Vo = 0 to 5.5V               | _    | _                   | ±10   | μA   |

| lozL         | (3-State Output pins)                       |                                                     |                              |      |                     |       |      |

| loff         | Input/Output Power Off Leakage              | Vcc = 0V, Vin or Vo                                 | ≤ 5.5V                       | _    | _                   | ±50   | μA   |

| Vik          | Clamp Diode Voltage                         | Vcc = 2.3V, IIN = -1                                | 8mA                          | _    | - 0.7               | - 1.2 | V    |

| VH           | Input Hysteresis                            | Vcc = 3.3V                                          |                              | _    | 100                 | _     | mV   |

| ICCL<br>ICCH | Quiescent Power Supply Current              | Vcc = 3.6V                                          | VIN = GND or Vcc             | _    | _                   | 10    | μA   |

| Iccz         |                                             |                                                     | $3.6 \le VIN \le 5.5V^{(2)}$ | _    | _                   | 10    | 1    |

| Δlcc         | Quiescent Power Supply<br>Current Variation | One input at Vcc - 0.6V, other inputs at Vcc or GND |                              | _    | _                   | 500   | µA   |

#### NOTES:

1. Typical values are at Vcc = 3.3V, +25°C ambient.

2. This applies in the disabled state only.

# **BUS-HOLD CHARACTERISTICS**

| Symbol | Parameter <sup>(1)</sup>         | Test Conditions |                | Min. | Typ. <sup>(2)</sup> | Max.  | Unit      |

|--------|----------------------------------|-----------------|----------------|------|---------------------|-------|-----------|

| Івнн   | Bus-Hold Input Sustain Current   | Vcc = 3.0V      | VI = 2.0V      | - 75 | _                   | -     | μA        |

| IBHL   |                                  |                 | VI = 0.8V      | 75   | _                   | _     |           |

| Івнн   | Bus-Hold Input Sustain Current   | Vcc = 2.3V      | VI = 1.7V      | _    | _                   | _     | μA        |

| IBHL   |                                  |                 | VI = 0.7V      | _    | _                   | -     |           |

| Івнно  | Bus-Hold Input Overdrive Current | Vcc = 3.6V      | VI = 0 to 3.6V | _    | _                   | ± 500 | μΑ        |

| Івньо  |                                  |                 |                |      |                     |       |           |

|        |                                  |                 |                |      |                     |       | 8LVC Link |

#### **NOTES**

1. Pins with Bus-hold are identified in the pin description.

2. Typical values are at Vcc = 3.3V, +25°C ambient.

# **OUTPUT DRIVE CHARACTERISTICS**

| Symbol | Parameter           | Test Co            | onditions <sup>(1)</sup> | Min.      | Max. | Unit      |

|--------|---------------------|--------------------|--------------------------|-----------|------|-----------|

| Vон    | Output HIGH Voltage | Vcc = 2.3V to 3.6V | IOH = - 0.1mA            | Vcc - 0.2 | _    | V         |

|        |                     | Vcc = 2.3V         | IOH = -6mA               | 2         | _    |           |

|        |                     | Vcc = 2.3V         | IOH = - 12mA             | 1.7       | _    |           |

|        |                     | Vcc = 2.7V         |                          | 2.2       | _    |           |

|        |                     | Vcc = 3.0V         |                          | 2.4       | _    |           |

|        |                     | Vcc = 3.0V         | IOH = - 24mA             | 2.2       | _    |           |

| Vol    | Output LOW Voltage  | Vcc = 2.3V to 3.6V | IOL = 0.1mA              | _         | 0.2  | V         |

|        |                     | Vcc = 2.3V         | IOL = 6mA                | _         | 0.4  |           |

|        |                     |                    | IOL = 12mA               | _         | 0.7  |           |

|        |                     | Vcc = 2.7V         | IOL = 12mA               | _         | 0.4  |           |

|        |                     | Vcc = 3.0V         | IoL = 24mA               | _         | 0.55 |           |

|        |                     | •                  | •                        | •         |      | 8LVC Link |

#### NOTE:

# OPERATING CHARACTERISTICS, $V_{CC} = 3.3V \pm 0.3V$ , $T_A = 25$ °C

| Symbol | Parameter                                                    | Test Conditions     | Typical | Unit |

|--------|--------------------------------------------------------------|---------------------|---------|------|

| CPD    | Power Dissipation Capacitance per flip-flop Outputs enabled  | CL = 0pF, f = 10Mhz | 54.5    | pF   |

| CPD    | Power Dissipation Capacitance per flip-flop Outputs disabled |                     | 13.5    | pF   |

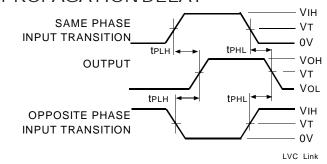

# SWITCHING CHARACTERISTICS (1)

|              |                                 | Vcc = 2 | .5V±0.2V | Vcc = | = 2.7V | Vcc = 3. | 3V±0.3V |      |

|--------------|---------------------------------|---------|----------|-------|--------|----------|---------|------|

| Symbol       | Parameter                       | Min.    | Max.     | Min.  | Max.   | Min.     | Max.    | Unit |

| fmax         |                                 | _       | _        | 80    | _      | 100      | _       | MHz  |

| tplh<br>tphl | Propagation Delay<br>CLK to xQ  | _       | _        | _     | 8.1    | 1.5      | 7       | ns   |

| tpzh<br>tpzl | Output Enable Time  OE or xQ    | _       | _        | _     | 8.5    | 1.5      | 7.5     | ns   |

| tphz<br>tplz | Output Disable Time  OE or xQ   | _       | _        | _     | 7.1    | 1.5      | 6.5     | ns   |

| tw           | Pulse Duration, CLK HIGH or LOW | _       | _        | 3.3   | _      | 3.3      | _       | ns   |

| tsu          | Setup Time, Data before CLK↑    | _       | _        | 2     | _      | 2        | _       | ns   |

| tн           | Hold Time, Data after CLK↑      | _       | _        | 1.5   | _      | 1.5      | _       | ns   |

| tsk(0)       | Output Skew <sup>(2)</sup>      | _       | _        | _     | _      | _        | 500     | ps   |

### NOTES:

- 1. See test circuits and waveforms.  $TA = -40^{\circ}C$  to  $+85^{\circ}C$ .

- 2. Skew between any two outputs of the same package and switching in the same direction.

<sup>1.</sup> VIH and VIL must be within the min. or max. range shown in the DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE table for the appropriate Vcc range. TA = - 40°C to +85°C.

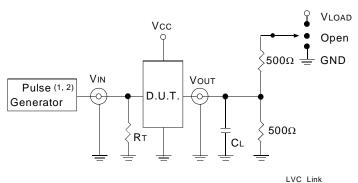

# TEST CIRCUITS AND WAVEFORMS

# **TEST CONDITIONS**

| Symbol | $Vcc^{(1)} = 3.3V \pm 0.3V$ | $Vcc^{(1)} = 2.7V$ | $Vcc^{(2)} = 2.5V \pm 0.2V$ | Unit |

|--------|-----------------------------|--------------------|-----------------------------|------|

| VLOAD  | 6                           | 6                  | 2 x Vcc                     | ٧    |

| VIH    | 2.7                         | 2.7                | Vcc                         | ٧    |

| VT     | 1.5                         | 1.5                | Vcc/2                       | ٧    |

| VLZ    | 300                         | 300                | 150                         | mV   |

| VHZ    | 300                         | 300                | 150                         | mV   |

| CL     | 50                          | 50                 | 30                          | pF   |

### TEST CIRCUITS FOR ALL OUTPUTS

#### **DEFINITIONS:**

CL= Load capacitance: includes jig and probe capacitance.

$\mathsf{RT} = \mathsf{Termination}$  resistance: should be equal to  $\mathsf{ZouT}$  of the Pulse Generator.

#### NOTES:

NOTES:

- 1. Pulse Generator for All Pulses: Rate ≤ 10MHz: tF ≤ 2.5ns: tR ≤ 2.5ns.

- 2. Pulse Generator for All Pulses: Rate  $\leq$  10MHz; tF  $\leq$  2ns; tR  $\leq$  2ns.

### **SWITCH POSITION**

| Test            | Switch    |

|-----------------|-----------|

| Open Drain      | Vload     |

| Disable Low     |           |

| Enable Low      |           |

| Disable High    | GND       |

| Enable High     |           |

| All Other tests | Open      |

|                 | 8LVC Link |

OUTPUT SKEW - tsk (x) Vін Vт INPUT -0V tPLH1 tPHL1 Vон Vт OUTPUT 1 Vol tsk (x) tsk (x) Vон Vт OUTPUT 2 Voi tPLH2 tPHL2

tsk(x) = |tplh2 - tplh1| or |tphl2 - tphl1|

#### 1. For tsk(o) OUTPUT1 and OUTPUT2 are any two outputs.

2. For tsk(b) OUTPUT1 and OUTPUT2 are in the same bank.

# PROPAGATION DELAY

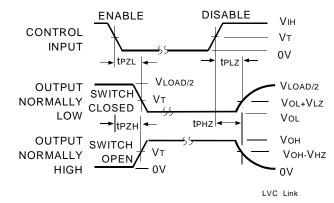

# **ENABLE AND DISABLE TIMES**

#### NOTE:

Diagram shown for input Control Enable-LOW and input Control Disable-HIGH.

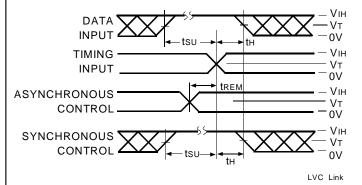

# SET-UP, HOLD, AND RELEASE TIMES

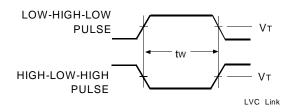

### **PULSE WIDTH**

LVC Link

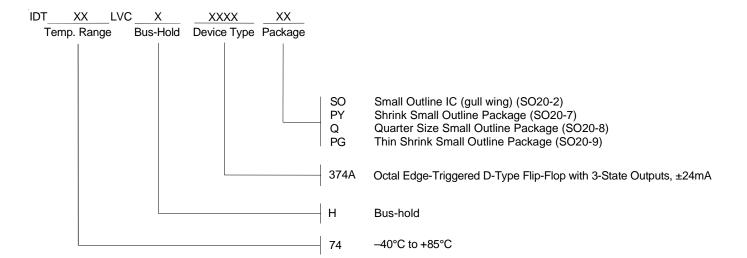

### ORDERING INFORMATION

CORPORATE HEADQUARTERS 2975 Stender Way Santa Clara, CA 95054 for SALES: 800-345-7015 or 408-727-6116 fax: 408-492-8674 www.idt.com\*