# Comlinear CLC415 Quad, Wideband Monolithic Op Amp

### **General Description**

The CLC415 is a wideband, quad, monolithic operational amplifier designed for intermediate-gain applications where power and cost per channel are of primary concern. Benefitting from Comlinear's current feedback architecture, the CLC415 offers a gain range of ±1 to ±10 while providing stable, oscillation-free operation without external compensation, even at unity gain.

Operating from ±5V supplies, the CLC415 consumes only 50mW of power per channel, yet maintains a 160MHz small-signal bandwidth and a 1500V/µs slew rate. High density applications requiring an integrated solution will enjoy the CLC415's 70dB channel isolation (input referred @ 5MHz).

With its exceptional differential gain and phase, typically 0.03% and 0.03° @ 3.58MHz, the CLC415 is designed to meet the performance and cost per channel requirements of high volume composite video applications. The CLC415's large-signal bandwidth, high slew rate and high drive capability are features well suited for RGB-video applications.

The CLC415 is a quad version of the high speed CLC406 while the CLC414 is a lower power quad version of the same. Both of these quads afford the designer lower power consumption and lower cost per channel with the additional benefit of requiring less board space per amplifier.

Constructed using an advanced, complementary bipolar process and Comlinear's proven current feedback architectures, the CLC415 is available in several versions to meet a variety of requirements.

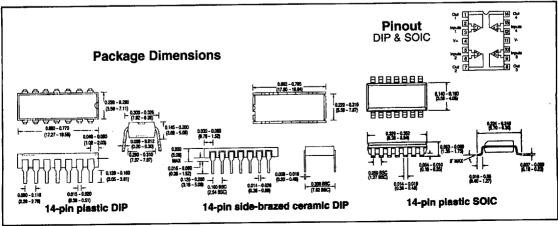

-40°C to +85°C CLC415AJP -40°C to +85°C CLC415AJE CLC415ALC

14-pin plastic DIP 14-pin plastic SOIC

-40°C to +85°C -55°C to +125°C CLC415AMC

dice qualified to Method 5008,

CLC415A8B -55°C to +125°C MIL-STD-883, Level B 14-pin hermetic CERDIP, MIL-STD-883, Level B

CI C415A8D -55°C to +125°C 14-pin sidebrazed CERDIP, MIL-STD-883, Level B

DESC SMD number: 5962-90994

#### **Features**

- 160MHz small signal bandwidth

- 0.05% settling in 12ns

- Low power, 160mW (40mW disabled)

- Low distortion, -60dBc at 20MHz

- Fast disable (200ns)

- Differential gain/phase: 0.01%/0.01°

- ±1 to ±8 closed-loop gain range

# Applications

- Video switching and distribution

- Analog bus driving (with disable)

- Low power "standby" using disable

- Fast, precision A/D conversion

- D/A current-to-voltage conversion

- F processors

- High-speed communications

| CLC415 Electrical Characteristics (A <sub>v</sub> = $\pm 6$ , V <sub>cc</sub> = $\pm 5$ V, R <sub>L</sub> = $100\Omega$ , R <sub>f</sub> = $500\Omega$ : unless specified) |                                    |             |             |              |              |                    |              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-------------|-------------|--------------|--------------|--------------------|--------------|

| PARAMETERS                                                                                                                                                                 | CONDITIONS                         | TYP         |             | MIN RAT      |              | UNITS              | SYMBOL       |

| Ambient Temperature                                                                                                                                                        | CLC415AJ/AI                        | +25°C       | -40°C       | +25°C        | +85°C        | I ONIS             | JUNDOL       |

| Ambient Temperature                                                                                                                                                        | CLC415A8/AL/AM                     | +25°C       | -55°C       | +25°C        | +125°C       | 1                  | <del> </del> |

| FREQUENCY DOMAIN RE                                                                                                                                                        |                                    |             |             | 1.200        | <del></del>  |                    |              |

| † -3dB bandwidth                                                                                                                                                           | V <sub>out</sub> <2V <sub>pp</sub> | 160         | >120        | >120         | >90          | MHz                | SSBW         |

|                                                                                                                                                                            | $V_{out} < 5V_{po}$                | 120         | >85         | >90          | >80          | MHz                | LSBW         |

| gain flatness                                                                                                                                                              | Vout <2Vp<br>DC to 25MHz           |             | i           |              |              |                    | 20011        |

| † peaking                                                                                                                                                                  |                                    | 0           | <0.2        | <0.2         | <0.2         | dB                 | GFPL         |

| † peaking                                                                                                                                                                  | >25MHz                             | 0           | <0.5        | <0.5         | <0.5         | dB                 | GFPH         |

| † rolloff                                                                                                                                                                  | DC to 50MHz                        | 0.2         | <0.7        | <0.7         | <1.1         | dB                 | GFR          |

| linear phase deviation                                                                                                                                                     | DC to 75MHZ                        | 0.5         | <1.0        | <1.0         | <1.3         | 1.                 | LPD          |

| differential gain (A <sub>v=+2</sub> )                                                                                                                                     |                                    | 0.03        | <0.08       | <0.08        | <0.08        | %                  | DG1          |

| differential phase (A <sub>v=+2)</sub>                                                                                                                                     | 4.43MHz                            | 0.03        | <0.10       | <0.10        | <0.10        | %                  | DG2          |

| differential priase (Av=+2)                                                                                                                                                |                                    | 0.03        | <0.08       | <0.08        | <0.08        | <b>I</b> :         | DP1          |

| crosstalk input referred                                                                                                                                                   | 4.43MHz<br>5MHz (all hostile)      | 0.03        | <0.10       | <0.10        | <0.10        | '                  | DP2          |

| input referred                                                                                                                                                             | 5MHz (chan. to chan.)              | 65<br>70    | <60         | <60          | <59          | dB                 | XT           |

| TIME DOMAIN RESPONSE                                                                                                                                                       |                                    | 70          | <63         | <63          | <62          | dB                 | CXT          |

| rise and fall time                                                                                                                                                         |                                    |             |             |              | ١            | ľ                  | ł            |

| rise and rail diffe                                                                                                                                                        | 2V step<br>5V step                 | 2.0         | <3.0        | <3.0         | <4.0         | ns                 | TRS          |

| settling time to 0.1%                                                                                                                                                      |                                    | 3.0         | <4.0        | <3.6         | <4.5         | ns                 | TRL          |

| overshoot                                                                                                                                                                  | 2V step                            | 12          | <18         | <18          | <22          | ns                 | TS           |

| slew rate                                                                                                                                                                  | 2V step                            | 8           | <12         | <12          | <12          | %                  | OS           |

|                                                                                                                                                                            | DEGROUP.                           | 1500        | >1200       | >1200        | >1000        | V/μs               | SR           |

| DISTORTION AND NOISE<br>†2nd harmonic distortion                                                                                                                           |                                    |             |             |              | 1            |                    |              |

|                                                                                                                                                                            | 2V <sub>pp</sub> , 20MHz           | -44         | <-38        | <-38         | <-34         | dBc                | HD2          |

| †3rd harmonic distortion                                                                                                                                                   | 2V <sub>pp</sub> , 20MHz           | -54         | <-46        | <-46         | <-42         | dBc                | HD3          |

| equivalent noise input<br>non-inverting voltage                                                                                                                            | >1MHz                              |             |             |              |              |                    |              |

| inverting current                                                                                                                                                          | >1MHz                              | 3.0         | <3.6        | <3.6         | <4.0         | nV/√Hz             | VN           |

| non-inverting current                                                                                                                                                      | >1MHz                              | 11.5        | <14         | <14          | <16          | pA√Hz              | ICN          |

| total noise floor                                                                                                                                                          | >IMHz                              | 2.0         | <2.6        | <2.6         | <3.0         | pA√Hz              | NCN          |

| total integrated noise                                                                                                                                                     | >1MHz to 100MHz                    | -157        | <-155       | <-155        | <-154        | dBm <sub>1Hz</sub> | SNF          |

|                                                                                                                                                                            |                                    | 37          | <44         | <44          | <48          | μV                 | INV          |

| STATIC, DC PERFORMANCE                                                                                                                                                     |                                    |             | _           |              |              | 1                  |              |

| *input offset voltage<br>average temperature co                                                                                                                            | rofficiont.                        | 2           | 9           | <5           | <10          | mV                 | VIO .        |

| *input bias current                                                                                                                                                        | non-invertina                      | 20<br>5     | <50         |              | <50          | μV/C               | DVIO         |

| average temperature co                                                                                                                                                     |                                    | 30          | <25<br><150 | <13          | <13          | μA                 | IBN          |

| *inout bias current                                                                                                                                                        | inverting                          | 30          | <18         | <10          | <50          | nA/C               | DIBN         |

| average temperature co                                                                                                                                                     |                                    | 20          | <100        | <10          | <15<br>-50   | μA                 | IBI          |

| tpower supply rejection ratio                                                                                                                                              | - III                              | 55          | >47         | >47          | <50<br>>45   | nA*C               | DIBI         |

| common mode rejection ratio                                                                                                                                                |                                    | 50          | ×45         | >45          | ×43          | dB<br>dB           | PSRR<br>CMRR |

| *supply current, all channels                                                                                                                                              | no load                            | 20          | <b>2</b> 7  | ₹26          | 24 I         | l mA               | ICC          |

| MISCELLANEOUS PERFORMANCE                                                                                                                                                  |                                    |             |             |              |              | 1101               | <del> </del> |

| non-inverting input resistance                                                                                                                                             |                                    |             | >300        | >600         | >600         | l 160              | DIN          |

| non-inverting input capacitan                                                                                                                                              |                                    | 1300<br>1.0 | ₹2.0        | <b>≥</b> 000 | >000<br><2.0 | kΩ<br>pF           | RIN          |

| ouput impedance                                                                                                                                                            | DC                                 | 0.2         | ₹0.6        | <0.3         | <2.0<br><0.2 | ρr<br>Ω            | CIN<br>RO    |

| output voltage range                                                                                                                                                       | R <sub>i</sub> =100Ω               | ±2.6        | ±2.3        | ±2.5         | ±2.5         | V                  | l vo         |

| common mode input range                                                                                                                                                    |                                    | ±2.2        | ±1.4        | ±2.0         | ±2.0         | ľ v                | CMIR         |

Min/max ratings are based on product characterization and simulation. Individual parameters are tested as noted. Outgoing quality levels are determined from tested parameters.

50

50

50

70

#### **Absolute Maximum Ratings** Miscellaneous Ratings ٧؞ ±7V recommended gain range: ±1 to ±10 $\mathbf{I}_{\mathrm{out}}$ output is short circuit protected to ground, however, maximum reliability is obtained if Notes: Int does not exceed... 70mA 100% tested at +25°C, sample at +85°C. Sample tested at +25°C. common mode input voltage ±V<sub>∞</sub> 100% tested at +25 C differential input voltage 100% tested +25°C, -55°C, +125°C. 100% tested +25°C, sample at -55°C, +125°C. 100% wafer probed at +25°C to +25°C min/max specifications. maximum junction temperature +175°C operating temperature range AJ/AI: -40°C to +85°C A8/AL/AM: -55°C to +125°C storage temperature range -65°C to +150°C note 1: Gain flatness tests performed from 0.1 MHz lead temperature (soldering 10 sec)

output current

+300°C

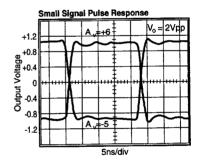

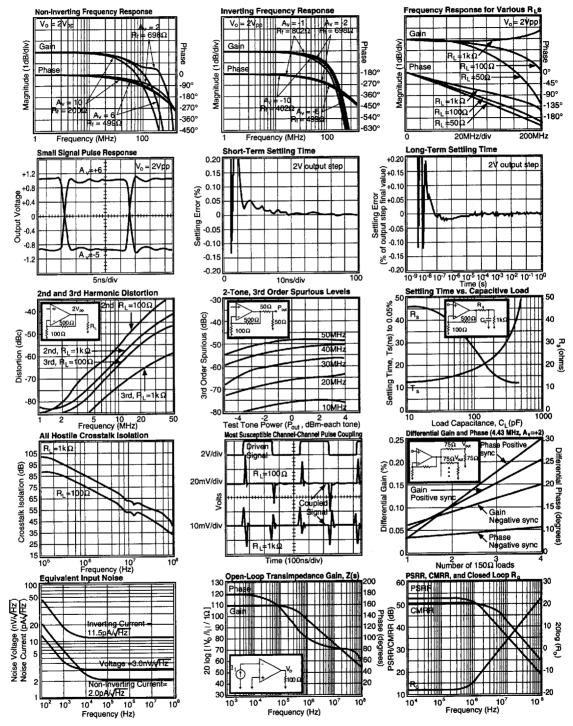

# CLC415 Typical Performance Characteristics (T<sub>A</sub> = 25°, A<sub>V</sub> = +6, V<sub>CC</sub> = ±5V, R<sub>L</sub> = 100Ω, R<sub>f</sub> =100Ω: unless specified)

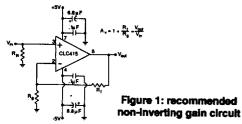

#### Feedback Resistor

The CLC415 achieves its exceptional AC performance while requiring very low quiescent power by using the current feedback topology and an internal slew rate enhancement circuit. The loop gain and frequency response for a current feedback op amp is predominantly set by the feedback resistor value. The CLC415 is optimized for a gain of +6 to use a  $500\Omega$  feedback resistor (use a  $900\Omega$  R, for maximally flat response at a gain of +2). Using lower values can lead to excessive ringing in the pulse response while a higher value will limit the bandwidth.

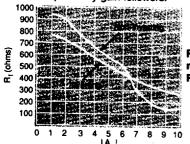

Application Note OA-13 provides a more detailed discussion of choosing a feedback resistor. The equations found in this application note are to be considered a starting point for the determination of  $R_{\rm I}$  at any gain. The value of input impedance for the CLC415 is approximately  $60\Omega$ . These equations do not account for parasitic capacitance at the inverting input nor across  $R_{\rm I}$ . The plot found below entitled "Recommended  $R_{\rm I}$  vs. Gain" offers values of  $R_{\rm I}$  which will optimize the frequency response of the CLC415 over its  $\pm 1$  to  $\pm 10$  gain range. Unlike voltage feedback, current feedback op amps require a non-zero  $R_{\rm I}$  for unity gain followers.

## Figure 3: recommended R, vs. gain

### Unused Amplifiers

It is recommended that any unused amplifiers in the quad package be connected as unity gain followers (R<sub>f</sub> =  $500\Omega$ ) with the non-inverting input tied to ground through a  $50\Omega$  resistor.

Slew Rate and Harmonic Distortion

Please see the application information for the CLC406.

# Differential Gain and Phase

Differential gain and phase performance specifications are common to composite video distribution applications. These specifications refer to the change in small signal gain and phase of the color subcarrier frequency (4.43MHz for PAL composite video) as the amplifier output is swept over a range of DC voltages. Application Note OA-08 provides an additional discussion of differential gain and phase measurements.

Non-inverting Source Impedance

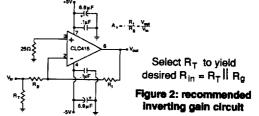

For best operation, the DC source impedance looking out of the non-inverting input should be less than  $3k\Omega$  but greater than  $20\Omega$ . Parasitic self oscillations may occur in the input transistors if the DC source impedance is out of

this range. This impedance also acts as the gain for the non-inverting input bias and noise currents and therefore can become troublesome for high values of DC source impedance. The inverting configuration of Figure 2 shows a  $25\Omega$  resistor to ground on the non-inverting input which insures stability but does not provide bias current cancellation. The input bias currents are unrelated for a current feedback amplifier which eliminates the need for source impedance matching to achieve bias current cancellation.

# DC Accuracy and Noise

Please refer to the application information section of the CLC406 for a discussion of output offset voltage and spot noise calculation.

#### Crosstalk

In any multi-channel integrated circuit there is an undesirable tendency for the signal in one channel to couple with and reproduce itself in the output of another channel. This effect is referred to as crosstalk. Crosstalk is expressed as channel separation or channel isolation which indicates the magnitude of this undesirable effect. This effect is measured by driving one or more channels and observing the output of the other undriven channel(s). The CLC415 plot page offers two different graphs detailing the effect of crosstalk over frequency. One plot entitled "All-Hostile Crosstalk Isolation" graphs all-hostile, inputreferred crosstalk. All-hostile crosstalk refers to the condition where three channels are driven simultaneously while observing the output of the undriven fourth channel. Input-referred implies that crosstalk is directly affected by gain and therefore a higher gain increases the crosstalk effect by a factor equal to that gain setting. The plot entitled "Most Susceptible Channel-to-Channel Pulse Coupling" describes the effect of crosstalk when one channel is driven with a 2Vpp pulse while the output of the most effected channel is observed.

#### **Printed Circuit Layout**

As with any high speed component, a careful attention to the board layout is necessary for optimum performance. Of particular importance is the careful control of parasitic capacitances on the output pin. As the output impedance plot shows, the closed loop output for the CLC415 eventually becomes inductive as the loop gain rolls off with increasing frequency. Direct capacitive loading on the output pin can quickly lead to peaking in the frequency response, overshoot in the pulse response, ringing or even sustained oscillations. The "Settling Time vs. Capacitive Load" plot should be used as a starting point for the selection of a series output resistor when a capacitive load must be driven. A quad amplifier will require careful attention to signal routing in order to minimize the effects of crosstalk. Signal coupling through the power supplies can be reduced with bypass capacitors placed close to the device supply pins.

#### **Evaluation Board**

Evaluation PC boards (part number 730024 for throughhole and 730031 for SOIC) for the CLC415 are available.