# SN74AS3374 METASTABLE-RESISTANT OCTAL D-TYPE EDGE-TRIGGERED FLIP-FLOPS WITH 3-STATE OUTPUTS

DW OR N PACKAGE (TOP VIEW)

> U20∏ 1D 19∏ 2D

18∏ 30

17 40

10 🔯

20 72

30 🗍 3

40 🛮 4

D3060, FEBRUARY 1989

| • | Meta-Flops Series — Metastable-Resistant<br>Filip-Flops        |  |

|---|----------------------------------------------------------------|--|

| • | Specifically Designed for Data<br>Synchronization Applications |  |

- Improved Metaetable Characteristics Provide Greater System Reliability

- 3-State Outputs Drive Bus Lines Directly

- Package Options Include Plastic "Small Outline" Packages and Standard Plastic DIPs

#### description

The 'AS3374, a member of the Meta-Flops' Series, is an 8-bit metastable-resistant bus interface circuit designed specifically for data synchronization applications where the normal setup and hold time specifications will frequently be violated.

Synchronization of two digital signals operating at different frequencies is a common system dilemma. This problem is typically solved by synchronizing one of the signals to the local clock through a flip-flop. This solution, however, presents a problem. The setup and hold time specifications associated with the flip-flop's output are certain to be violated. Whenever the setup or hold times of a flip-flop are violated, its output response is uncertain. A flip-flop is metastable if its output hangs up in the region between VIL and VIH. The metastable state lasts until the flip-flop recovers into one of its two stable states. For conventional flip-flope, this recovery time can be longer than the specified propagation delay time.

Evaluating the metastable characteristics for a particular flip-flop is not an easy task. The number of times the output hangs up in the metastable region is extremely small compared to the total number of clock transitions.

Conventional test equipment is not designed to measure these parameters. Measuring these

GND 5 16 VCC

50 6 15 5D

60 7 14 6D

70 8 13 7D

6 80 9 12 8D

70 10 11 CLK

<sup>†</sup> This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

#### PUNCTION TABLE (EACH DUAL-RANK PLIP-PLOP)

| INPUTS |     |   | OUTPUT      |

|--------|-----|---|-------------|

| ᅋ      | CLK | D | L a         |

| н      | ×   | × | Z           |

| L      | t   | L | L           |

| L      | t   | н | н           |

| L      | L   | x | <u> 0</u> 0 |

parameters on a production basis is impractical. Resistance to metastable failure is ensured by design only. For additional information on metastability, please refer to the application note located on page 4-51 of the ALS/AS Logic Data Book, 1986.

The SN74AS3374 is characterized for operation from 0°C to 70°C.

Meta-Flops is a trademark of Texas Instruments Incorporated.

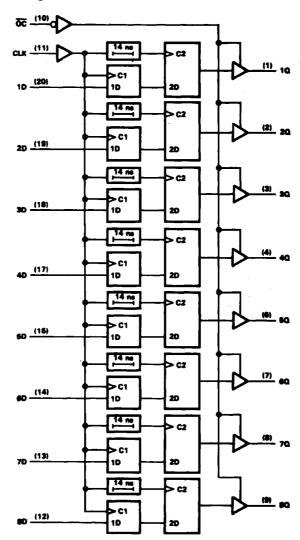

# logic diagram (positive logic)

# SN74AS3374 METASTABLE-RESISTANT OCTAL D-TYPE EDGE-TRIGGERED FLIP-FLOPS WITH 3-STATE OUTPUTS

## sheekits maximum ratings over operating free-sir temperature range (unless otherwise noted)

| Voltage applied to a disabled 3-state | output | 5.5 V       |

|---------------------------------------|--------|-------------|

| Operating free-air temperature range  |        | 0°C to 70°C |

#### recommended operating conditions

|                 |                                         |          | MIN  | NOM | MAX  | UNIT |

|-----------------|-----------------------------------------|----------|------|-----|------|------|

| Vcc             | Supply voltage                          |          | 4.75 | 5   | 5.25 | ٧    |

| VIH             | High-level input voltage                |          | 2    |     |      | >    |

| VIL             | Low-level input voltage                 |          |      |     | 0.8  | >    |

| Юн              | High-level output current               |          |      | ,   | -15  | mA   |

| lOL.            | Low-level output current                |          |      |     | 48   | mA   |

| fclock          | Clock frequency                         |          | 0    |     | 45   | MHz  |

|                 | Pulse duration                          | CLK high | 5    |     |      | _ ns |

| t <sub>w</sub>  |                                         | CLK low  | 5    |     |      |      |

| t <sub>eu</sub> | Setup time, data before CLK             | t        | 4    |     |      | ns.  |

| th th           | Hold time, data after CLKf <sup>†</sup> |          | 2    |     |      | N8   |

| TA              | Operating free-air temperatur           | <u> </u> | 0    |     | 70   | •c   |

<sup>†</sup> The data setup and hold times are specified for synchronous operation. These parameters also help guarantee overall speed characteristics of the device. Since production testing for metastability is impractical, conformance to conventional switching characteristics verifies metastable-failure resistance.

### electrical characteristics over recommended operating free-sir temperature range (unless otherwise noted)

| PARAMETER       | TEST CONDITIONS                                   | ARIN | TYP  | MAX  | UNIT |

|-----------------|---------------------------------------------------|------|------|------|------|

| VIK             | V <sub>CC</sub> = 4.75 V, I <sub>I</sub> = -18 mA |      |      | -1.2 | >    |

|                 | VCC = 4.75 V, IOH = -3 mA                         | 2.4  | 3.2  |      | >    |

| VOH             | VCC = 4.75 V, IOH = -15 mA                        | 2    |      |      |      |

|                 | VCC = 4.75 V, IOL = 32 mA                         |      | 0.25 | 0.4  | >    |

| VOL             | V <sub>CC</sub> = 4.75 V, I <sub>OL</sub> = 48 mA |      | 0.35 | 0.5  |      |

| 4               | V <sub>CC</sub> = 5.25 V, V <sub>I</sub> = 7 V    |      |      | 0.1  | m#   |

| 104             | V <sub>CC</sub> = 5.25 V, V <sub>1</sub> = 2.7 V  |      |      | 20   | *    |

| lik.            | V <sub>CC</sub> = 5.25 V, V <sub>1</sub> = 0.4 V  |      |      | -0.2 | mA   |

| IOZH            | V <sub>CC</sub> = 5.25 V, V <sub>I</sub> = 2.4 V  |      |      | 20   | *    |

| IOZL.           | V <sub>CC</sub> = 5.25 V, V <sub>O</sub> = 0.4 V  |      |      | - 20 | ¥.   |

| lo <sup>1</sup> | V <sub>CC</sub> = 5.25 V, V <sub>O</sub> = 2.25 V | - 30 |      | -112 | mA   |

| Icc             | V <sub>CC</sub> = 5.25 V, OC high                 |      | 100  | 140  | mA   |

<sup>&</sup>lt;sup>4</sup> All typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25 °C. <sup>5</sup> The output conditions have been chosen to produce a current that closely approximates one-half of the true short-circuit output current, los-

# SN74AS3374 METASTABLE-RESISTANT OCTAL D-TYPE EDGE-TRIGGERED FLIP-FLOPS WITH 3-STATE OUTPUTS

# switching characteristics over recommended operating free-sir temperature range (unless otherwise noted) (see Note 1)

| PARAMETER   | PROM  | то       | Gi<br>R1 | 77P | ₽.<br>Q.<br>Q. | CL - 90<br>R1 - 80<br>R2 - 90 | Ω, | UNIT      |

|-------------|-------|----------|----------|-----|----------------|-------------------------------|----|-----------|

| fmex        |       |          |          | 60  |                | 48                            |    | MHz       |

| <b>tPLH</b> | CLK   | <u> </u> | L        | 18  | 20             | 14                            | 23 | -         |

| TPHL.       | CDA . | L        |          | 16_ | 20             | 14                            | 23 | ] "       |

| <b>TPZH</b> | 575   | ۵        |          | 7   |                | 2                             |    |           |

| TPZL.       |       |          |          | 7   |                | 2                             | 11 | <b>CO</b> |

| tenz        | ठट    | ٥        |          | 5   | 7              | 1                             |    |           |

| <b>TPLZ</b> |       |          | Ĺ        | . 5 | 7              | 1                             |    | 746       |

NOTE 1: Load circuit and voltage waveforms are shown in Section 1.