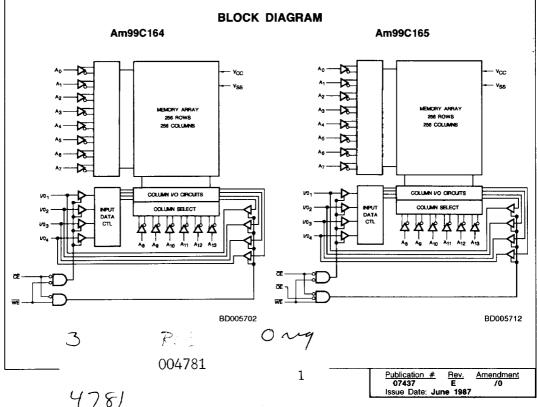

# Am99C164/Am99CL164 Am99C165/Am99CL165

16,384 x 4 Static R/W Random-Access Memory **PRELIMINARY**

#### DISTINCTIVE CHARACTERISTICS

- Fast access time 35/45/55/70 ns maximum

- 16K x 4 organization

- Output Enable (OE) control to alleviate bus-contention conditions (Am99C165)

- Single 5-V ±10% power-supply operation

- Fully static storage and interface circuitry

- Automatic power-down when deselected

- Low power dissipation

- 550 mW operating power

- 200 μW data retention

- 2-V data-retention capability

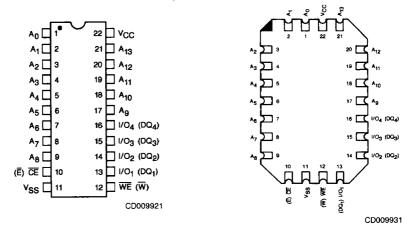

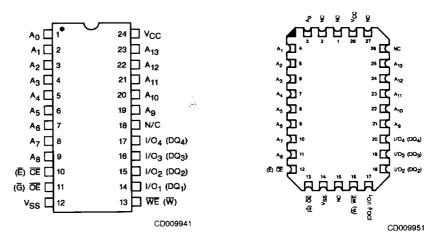

- 22-pin 0.300-inch DIP (Am99C164)

- 22-pin LCC (Am99C164)

- 24-pin 0.300-inch DIP (Am99C165)

- 28-Pin LCC (Am99C165)

#### **GENERAL DESCRIPTION**

The Am99C164 and Am99C165 are high-performance 16,384 x 4-bit static random-access memories (RAMs) manufactured with state-of-the-art CMOS processing tech-

The Am99C164 device features common input/output pins and two control signals, CE and WE. While CE controls read, write, and selection/deselection of the device, WE controls the write operation and output buffers only.

The Am99C165 device features three control signals (CE, WE, and OE) to facilitate not only memory expansion, but also alleviate any bus-contention conditions which might limit high-performance read/write operation. While WE activates only the input buffers during a write cycle, OE activates only the output buffers during a read cycle. CE in the HIGH state deselects the entire device and reduces power consumption. All input/output interface levels are fully TTL-compatible for both the Am99C164 and Am99C165.

The Am99C164 and Am99C165 require a single 5-volt power supply while operating but can hold the data when power-supply level is maintained at a voltage as low as 2

The Am99C164 is available in 22-pin 0.300-inch wide ceramic and plastic DIPs, and 22-pin rectangular ceramic leadless chip carriers. The Am99C165 is available in 24-pin 0.300-inch wide ceramic and plastic DIPs, and 28-pin rectangular ceramic leadless chip carriers.

4781

# PRODUCT SELECTOR GUIDE

|                             | Family Part No.  Ordering Part No. |        |     | Am99C164/Am99CL164<br>Am99C165/Am99CL165 |      |     |  |  |  |

|-----------------------------|------------------------------------|--------|-----|------------------------------------------|------|-----|--|--|--|

| Ordering Part               |                                    |        |     | -45                                      | -55  | -70 |  |  |  |

| Access Time (               | ns)                                |        | 35  | 45                                       | 55   | 70  |  |  |  |

|                             | Symbol                             | Power* |     |                                          |      |     |  |  |  |

|                             | Icc (mA)                           | s      | 110 | 110                                      | (110 | 110 |  |  |  |

|                             |                                    | L      | 105 | 95                                       | 90   | 90  |  |  |  |

|                             | I <sub>SB1</sub> (mA)              | S      | 45  | 45                                       | 45   | 45  |  |  |  |

| Commercial (C) Devices:     | .3B1 (A)                           | L      | 25  | 25                                       | 25   | 25  |  |  |  |

| 0 to +70°C                  | I <sub>SB2</sub> (mA)              | S      | 25  | 25                                       | 25   | 25  |  |  |  |

|                             | 13B2 (IIIA)                        | L      | 20  | 20                                       | 20   | 20  |  |  |  |

|                             | I <sub>SB3</sub> (mA)              | S      | 15  | 15                                       | 15   | 15  |  |  |  |

|                             | -363 (IIIA)                        | L      | 0.3 | 0.3                                      | 0.3  | 0.3 |  |  |  |

|                             | ICCDR (mA)                         | S      | _   | _                                        | _    | -   |  |  |  |

| <del></del>                 | @ 2 V                              | L      | 0.1 | 0.1                                      | 0.1  | 0.1 |  |  |  |

|                             | I <sub>CC</sub> (mA)               | S      | _   | 120                                      | 120  | 120 |  |  |  |

|                             | -00 ()                             | L      |     | 110                                      | 105  | 105 |  |  |  |

| Extended<br>Commercial      | I <sub>SB1</sub> (mA)              | S      | _   | 50                                       | 50   | 50  |  |  |  |

| (E)                         | 361 ()                             | L      | -   | 30                                       | 30   | 30  |  |  |  |

| and Military<br>(M) Devices | I <sub>SB2</sub> (mA)              | s      |     | 35                                       | 35   | 35  |  |  |  |

| -55 to +125°C               |                                    | L      |     | 25                                       | 25   | 25  |  |  |  |

|                             | I <sub>SB3</sub> (mA)              | s      |     | 20                                       | 20   | 20  |  |  |  |

| ĺ                           | 350 ()                             | LL     |     | 1.0                                      | 1.0  | 1.0 |  |  |  |

|                             | ICCDR (mA)                         | S      | _   | -                                        | _    | -   |  |  |  |

|                             | @ 2 V                              | L      | -   | 0.3                                      | 0.3  | 0.3 |  |  |  |

<sup>\*</sup>S = Standard Power (Am99C164, Am99C165); L = Low Power (Am99CL164, Am99CL165)

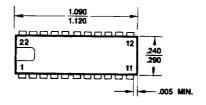

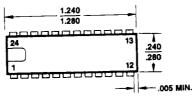

# CONNECTION DIAGRAMS

#### Am99C164/Am99CL164

Note: Pin 1 is marked for orientation.

#### Am99C165/Am99CL165

Note: Pin 1 is marked for orientation.

IEEE Nomenclature in Brackets.

# LOGIC SYMBOLS Am99C164/Am99CL164 Am99C165/Am99CL165 1/01-1/04 1/01-1/04 WE

ŌĒ

LS002670

# Address Designators

LS002660

| External        | Internal*       | Pin Number<br>DIP Package |

|-----------------|-----------------|---------------------------|

| A <sub>0</sub>  | AX <sub>5</sub> | 1                         |

| A <sub>1</sub>  | AX <sub>6</sub> | 2                         |

| A <sub>2</sub>  | AX <sub>3</sub> | 3                         |

| A <sub>3</sub>  | AX <sub>4</sub> | 4                         |

| A <sub>4</sub>  | AX <sub>7</sub> | 5                         |

| A <sub>5</sub>  | AY <sub>0</sub> | 6                         |

| A <sub>6</sub>  | AY <sub>1</sub> | 7                         |

| A <sub>7</sub>  | AY <sub>2</sub> | 8                         |

| A <sub>8</sub>  | AY <sub>3</sub> | 9                         |

| A9              | AY <sub>4</sub> | 17, 19*                   |

| A <sub>10</sub> | AY <sub>5</sub> | 18, 20*                   |

| A <sub>11</sub> | AX <sub>0</sub> | 19, 21*                   |

| A <sub>12</sub> | AX <sub>2</sub> | 20, 22*                   |

| A <sub>13</sub> | AX <sub>3</sub> | 21, 23*                   |

<sup>\*</sup>For Am99C165, Am99CL165

Œ

WE

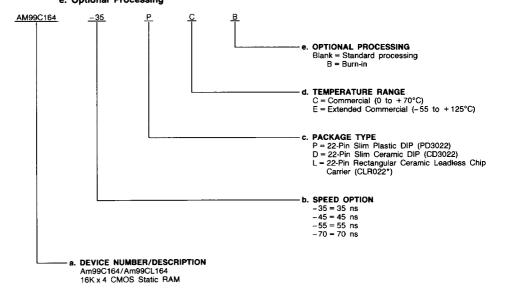

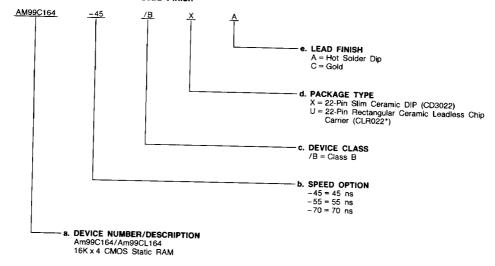

#### **ORDERING INFORMATION — Am99C164**

#### Standard Products

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of: a. Device Number

- b. Speed Option (if applicable)

- c. Package Type

- d. Temperature Range e. Optional Processing

\*Preliminary. Subject to change.

| Valid Combinations |                          |  |  |  |  |  |  |

|--------------------|--------------------------|--|--|--|--|--|--|

| AM99C164-35        | PC, PCB, DC,             |  |  |  |  |  |  |

| AM99CL164-35       | DCB, LC, LCB             |  |  |  |  |  |  |

| AM99C164-45        |                          |  |  |  |  |  |  |

| AM99CL164-45       | PC, PCB, DC,             |  |  |  |  |  |  |

| AM99C164-55        | DCB, DE,                 |  |  |  |  |  |  |

| AM99CL164-55       | DEB, LC,<br>LCB, LE, LEB |  |  |  |  |  |  |

| AM99C164-70        | 7 LOB, LE, LEB           |  |  |  |  |  |  |

| AM99CL164-70       | 1                        |  |  |  |  |  |  |

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released combinations, and to obtain additional data on AMD's standard military grade products.

# ORDERING INFORMATION — Am99C164 (Cont'd.)

#### **APL Products**

AMD products for Aerospace and Defense applications are available in several packages and operating ranges. APL (Approved Products List) products are fully compliant with MIL-STD-883C requirements. The order number (Valid Combination) for APL

- b. Speed Option (if applicable)

- c. Device Class

- d. Package Type

- e. Lead Finish

\*Preliminary. Subject to change.

| Valid Combinations |                  |  |  |  |  |  |

|--------------------|------------------|--|--|--|--|--|

| AM99C164-45        |                  |  |  |  |  |  |

| AM99CL164-45       |                  |  |  |  |  |  |

| AM99C164-55        | /BXA, /BXC, /BUA |  |  |  |  |  |

| AM99CL164-55       |                  |  |  |  |  |  |

| AM99C164-70        | 7                |  |  |  |  |  |

| AM99CL164-70       | 7                |  |  |  |  |  |

## **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations or to check for newly released valid combinations.

#### **Group A Tests**

Group A tests consist of Subgroups 1, 2, 3, 7, 8, 9, 10, 11

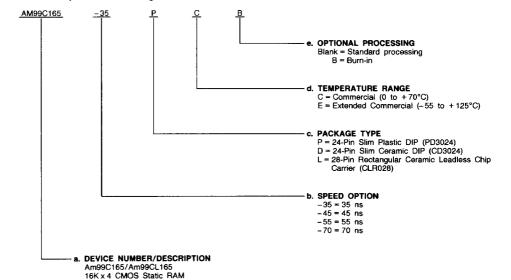

#### **ORDERING INFORMATION — Am99C165**

#### Standard Products

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of: a. Device Number

- b. Speed Option (if applicable)

- c. Package Type

- d. Temperature Range

- e. Optional Processing

| Valid Combinations |                   |  |  |  |  |  |  |

|--------------------|-------------------|--|--|--|--|--|--|

| AM99C165-35        | PC, PCB, DC, DCB, |  |  |  |  |  |  |

| AM99CL165-35       | LC, LCB           |  |  |  |  |  |  |

| AM99C165-45        |                   |  |  |  |  |  |  |

| AM99CL165-45       | PC, PCB, DC, DCB, |  |  |  |  |  |  |

| AM99C165-55        | DE, DEB, LC, LCB, |  |  |  |  |  |  |

| AM99CL165-55       | LE, LEB           |  |  |  |  |  |  |

| AM99C165-70        |                   |  |  |  |  |  |  |

| AM99CL165-70       | 1                 |  |  |  |  |  |  |

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released combinations, and to obtain additional data on AMD's standard military grade products.

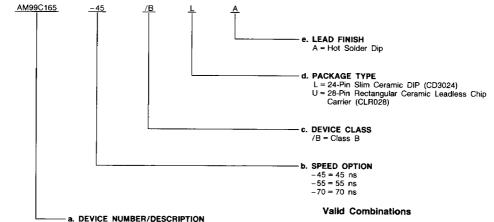

### ORDERING INFORMATION — Am99C165 (Cont'd.)

#### **APL Products**

AMD products for Aerospace and Defense applications are available in several packages and operating ranges. APL (Approved Products List) products are fully compliant with MIL-STD-883C requirements. The order number (Valid Combination) for APL products is formed by a combination of: a. Device Number

- b. Speed Option (if applicable)

- c. Device Class

- d. Package Type

- e. Lead Finish

| Valid Combinations |            |  |  |  |  |  |

|--------------------|------------|--|--|--|--|--|

| AM99C165-45        |            |  |  |  |  |  |

| AM99CL165-45       |            |  |  |  |  |  |

| AM99C165-55        | /BLA, /BUA |  |  |  |  |  |

| AM99CL165-55       |            |  |  |  |  |  |

| AM99C165-70        |            |  |  |  |  |  |

| AM99CL165-70       | 7          |  |  |  |  |  |

Am99C165/Am99CL165 16K x 4 CMOS Static RAM Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations or to check for newly released valid combinations.

#### **Group A Tests**

Group A tests consist of Subgroups 1, 2, 3, 7, 8, 9, 10, 11

## PIN DESCRIPTION

#### A<sub>0</sub> - A<sub>13</sub> Address Lines (Input)

The address input lines select the RAM location to be read from or written into.

#### CE Chip Enable (Input, Active LOW)

$\overline{\text{CE}}$  selects the memory device.  $\overline{\text{WE}}$  is ignored when  $\overline{\text{CE}}$  is HIGH.

### WE Write Enable (Input, Active LOW)

When  $\overline{WE}$  is LOW and  $\overline{CE}$  is also LOW, data will be written into the location specified on the address pins. When  $\overline{WE}$  is

HIGH and  $\overline{\text{CE}}$  is LOW (and  $\overline{\text{OE}}$  is LOW for Am99C165) data will be read out and placed on the I/O pin.

## OE Output Enable (Input, Active LOW)

When  $\overline{\text{OE}}$  is LOW, it activates the output buffers during a read cycle, for Am99C165 only.

#### I/O<sub>1</sub>-I/O<sub>4</sub> Data in/Out Bus (Input/Output)

These I/O lines provide the path for data to be read from or written into the selected memory location.

V<sub>CC</sub> +5-Voit Power Supply

VSS 0-Volt Ground

## ABSOLUTE MAXIMUM RATINGS (Note 1) Storage Temperature Ceramic DIPs & LCCs .....-65 to +150°C Plastic DIPs ...... -55 to +125°C

Ambient Temperature with Power Applied Ceramic DIPs & LCCs .....-65 to +135°C

Plastic DIPs .....-10 to +85°C DC Supply Voltage

to Ground Potential Continuous......-0.5 to +7.0 V All Signal Voltages.....-0.5 to +7.0 V

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality

at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device

reliability.

**OPERATING RANGES** (Note 2)

Commercial (C) Devices Temperature (T<sub>A</sub>)......0 to +70°C

Extended Commercial (E) and Military (M) Devices Temperature (T<sub>A</sub>).......55 to +125°C

Supply Voltage (VCC) .....+4.5 to +5.5 V Operating ranges define those limits between which the functionality of the device is guaranteed.

DC CHARACTERISTICS over operating range unless otherwise specified (for APL Products, Group A, Subgroups 1, 2, 3 are tested unless otherwise noted)

| Parameter<br>Symbol | Parameter<br>Description | Test Conditions                                                                                                                                              | Min. | Max.                  | Units |

|---------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------------|-------|

| ГОН                 | Output HIGH Current      | V <sub>OH</sub> = 2.4 V,<br>V <sub>CC</sub> = 4.5 V                                                                                                          | -4   |                       | mA    |

| lor                 | Output LOW Current       | V <sub>OL</sub> = 0.4 V                                                                                                                                      | 8    |                       | mA    |

| V <sub>IH</sub>     | Input HIGH Voltage       |                                                                                                                                                              | 2.2  | V <sub>CC</sub> + 1.0 | V     |

| VIL                 | Input LOW Voltage        | Note 8                                                                                                                                                       | -0.5 | 0.8                   | ٧     |

| l <sub>lx</sub> 1   | Input Load Current       | GND ≤ V <sub>IN</sub> ≤ V <sub>CC</sub>                                                                                                                      |      | 2.0                   | μΑ    |

| liozi               | Output Leakage Current   | $\begin{array}{l} \text{GND} \leqslant \text{V}_{\text{OUT}} \leqslant \text{V}_{\text{CC}}, \\ \hline \text{CE} \geqslant \text{V}_{\text{IH}} \end{array}$ |      | 2.0                   | μΑ    |

# DC CHARACTERISTICS over Commercial (0 to +70°C) Operating Range\*

|                     |                             |                                                                                 |         | Am<br>Am | CER        |      |            |       |

|---------------------|-----------------------------|---------------------------------------------------------------------------------|---------|----------|------------|------|------------|-------|

| Parameter<br>Symbol | Parameter<br>Description    | Test Conditions                                                                 | Power** | -35      | <b>⊢45</b> | -55  | <b>-70</b> | Unit  |

|                     | Dynamic Operating           | Cycle = Min.,<br>Duty = 100%,                                                   | s       | (110)    | (110)      | (10) | (10)       | mA    |

| lcc                 | Supply Current              | Œ ≤ V <sub>IL</sub> ,<br>I/O = 0 mA                                             | L       | 105      | 95         | 90   | 90)        | mA    |

|                     | Static Operating            | CE ≤ V <sub>IL</sub> ,                                                          | s       | 80       | 80         | 80   | 80         | mA.   |

| CC1                 | Supply Current              | I/O = 0 mA                                                                      | L       | 60       | 60         | 60   | 60         |       |

|                     | Standby Current,            | CE ≥ V <sub>IH</sub> ;                                                          | S       | 45       | 45         | 45   | 45         | mA    |

| I <sub>SB1</sub>    | Cycling TTL Levels          | V <sub>CC</sub> = Max.,<br>Cycle = Min.                                         | L       | 25       | 25         | 25   | 25         | 1107  |

|                     | Standby Current,            | CE ≥ V <sub>IH</sub> ,                                                          | ∔ S     | 25       | 26         | 25   | 26         | mA    |

| <sup>1</sup> SB2    | Stable TTL Levels           | V <sub>IN</sub> ≥ V <sub>IH</sub> or<br>≤ V <sub>IL</sub>                       | k L     | 20       | 20         | 20   | 20         |       |

|                     | Standby Current,            | CE ≥ V <sub>CC</sub> - 0.2 V,                                                   | S       | 15       | 15         | 15   | 15_        | mA    |

| l <sub>SB3</sub>    | Stable CMOS Input<br>Levels | $V_{\text{IN}} \geqslant V_{\text{CC}} - 0.2 \text{ V}$ or $\leq 0.2 \text{ V}$ | L       | 0.3      | 0.3        | 0.3  | 0.3        | ,,,,, |

Notes: See notes following Capacitance table on the following page.

\*All values are guaranteed maximum limits.

\*\*S = Standard Power (Am99C164/Am99C165) L = Low Power (Am99CL164/Am99CL165)

8 8 3 B

# DC CHARACTERISTICS over Extended Commercial and Military (-55 to +125°C) Operating Ranges\*

| Parameter<br>Symbol | Parameter                              |                                                                                                |         | Am99C164/Am99CL164<br>Am99C165/Am99CL165 |      |       |      |

|---------------------|----------------------------------------|------------------------------------------------------------------------------------------------|---------|------------------------------------------|------|-------|------|

| Зупівої             | Description                            | Test Conditions                                                                                | Power** | -45                                      | ~55  | -70   | Unit |

| Icc                 | Dynamic Operating<br>Supply Current    | Cycle = Min.,<br>Duty = 100%,                                                                  | S       | 129                                      | 120) | (120) | Des  |

|                     |                                        | CE ≤ V <sub>IL</sub> ,<br>I/O = 0 mA                                                           | L       | 110                                      | 105  | (105) | mA   |

| ICC1                | Static Operating Supply Current        | CE ≤ V <sub>IL</sub> ,                                                                         | S       | 100                                      | 100  | 100   |      |

|                     |                                        | I/O = 0 mA                                                                                     | L       | 80                                       | 80   | 80    | mA   |

| I <sub>SB1</sub>    | Standby Current,<br>Cycling TTL Levels | $\overline{CE} \geqslant V_{IH},$ $V_{CC} = Max.,$                                             | S       | 50                                       | 50   | 50    |      |

|                     | -y-mg //L Lovels                       | Cycle = Min.                                                                                   | L       | 30                                       | 30   | 30    | mA   |

| I <sub>SB2</sub>    | Standby Current, Stable TTL Levels     | CE ≥ V <sub>IH</sub> ,<br>V <sub>IN</sub> = V <sub>IH</sub> or                                 | S       | 35                                       | 35   | 35    |      |

|                     | ļ <u>-</u>                             | < V <sub>IL</sub>                                                                              | L       | 25                                       | 25   | 25    | mA   |

| I <sub>SB3</sub>    | Standby Current,<br>Stable CMOS        | $\overline{CE} \geqslant V_{CC} - 0.2 \text{ V},$<br>$V_{IN} \geqslant V_{CC} - 0.2 \text{ V}$ | S       | 20                                       | 20   | 20 )  |      |

|                     | Input Levies guaranteed maximum lim    | or ≤ 0.2 V                                                                                     | L       | 1.0                                      | 1.0  | 1.0   | mA   |

<sup>\*\*</sup>S = Standard Power (Am99C164/Am99C165)

### **CAPACITANCE**+

| Parameter<br>Symbol                           | Parameter<br>Description      | Test Conditions                      | Min. | Max. | Units   |  |

|-----------------------------------------------|-------------------------------|--------------------------------------|------|------|---------|--|

| C <sub>I</sub> ++ Input Capacitance Except CE |                               | f = 1 MHz,                           |      |      | -       |  |

| C <sub>O</sub> ++                             | Output Capacitance            | V <sub>IN</sub> = 0 V                |      |      | pF      |  |

| CE ++                                         | Chip Enable Input Capacitance | V <sub>OUT</sub> = 0 V<br>f = 1 MHz, |      | 7    | <b></b> |  |

| † Those on                                    | Dacitances are not 100% total | $V_{IN} \approx 0 \text{ V}$         |      | 7.5  | pF      |  |

<sup>†</sup> These capacitances are not 100% tested, but are evaluated at initial characterization and at any time the product is modified where capacitance may be affected. Measurement performed at  $T_A = +25^{\circ}C$ .

Notes: 1. Absolute Maximum Ratings are intended for user guidelines and are not tested.

- 2. For test and correlation purposes, operating temperature is defined as the "instant-on" case temperature.

- 3. Parameter not tested—guaranteed by characterization.

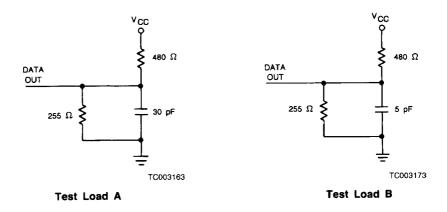

- 4. Test conditions assume signal transition times of 5 ns or less, timing reference levels of 1.5 V, input-pulse levels of 0 to 3.0 V, and output loading of specified  $I_{OL}/I_{OH}$  and 30-pF load capacitance. Output timing reference is 1.5 V (see Test Load A in Switching Test Circuits section).

- 5. The internal write time of the memory is defined by the overlap of  $\overline{\text{CE}}$  active and  $\overline{\text{WE}}$  LOW. Both signals must be active to initiate a write and either signal can terminate a write by going inactive. The data input setup and hold timing should be referenced to the transition edge that terminates the write.

- 6. The minimum limit is not tested and is included for design information only.

- 7. Parameter not tested, guaranteed by characterization using the load shown in Test Load B-Switching Test Circuits. Transition is measured ±500 mV from steady state voltage.

- 8. Undershoot to -3.0 V for a duration of 10 ns between the 50% amplitude points is permissible.

- 9. Address input rise and fall times must not exceed 1 µs when CE is active. This limit is not tested and is intended for

L = Low Power (Am99CL164/Am99CL165)

<sup>++ =</sup> Not included in Group A tests.

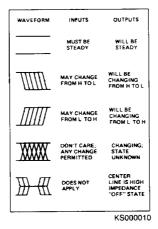

## KEY TO SWITCHING WAVEFORMS

## **SWITCHING TEST CIRCUITS**

# SWITCHING TEST WAVEFORM

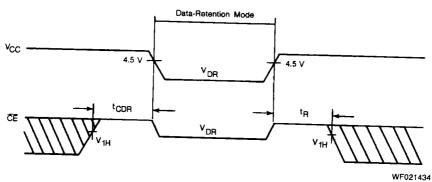

Low V<sub>CC</sub> Data Retention Characteristics (Low-Power Version Only)

| Parameter<br>Symbol | Parameter<br>Description                      | Test<br>Conditions                  |       | Min.  | Max. |               |

|---------------------|-----------------------------------------------|-------------------------------------|-------|-------|------|---------------|

| VDR                 | V <sub>CC</sub> for Data Retention            | <u>CE</u> ≥ V <sub>CC</sub> - 0.2 V | 2.0   | Units |      |               |

| ICCDR               | Data Retention Current                        | V <sub>CC</sub> = 2 V               | COM'L |       | 0.1  | <del></del> - |

|                     |                                               |                                     | MIL   |       | 0.3  | mA            |

| CCDR                | Data Retention Current                        | V <sub>CC</sub> = 3 V               | COM'L |       | 0.15 |               |

|                     | Chin Dandard D                                |                                     | MIL   |       | 0.45 | mA            |

| tCDR                | Chip Deselect to Data Retention Time (Note 1) | See Waveform (Note 2)               |       | 0     |      | ns            |

| t <sub>R</sub>      | Operating Recovery Time (Note 1)              |                                     |       | tRC   |      | ns            |

Notes: 1. Parameter not tested, guaranteed by design.

2. Waveforms shown are not actual and may vary in use.

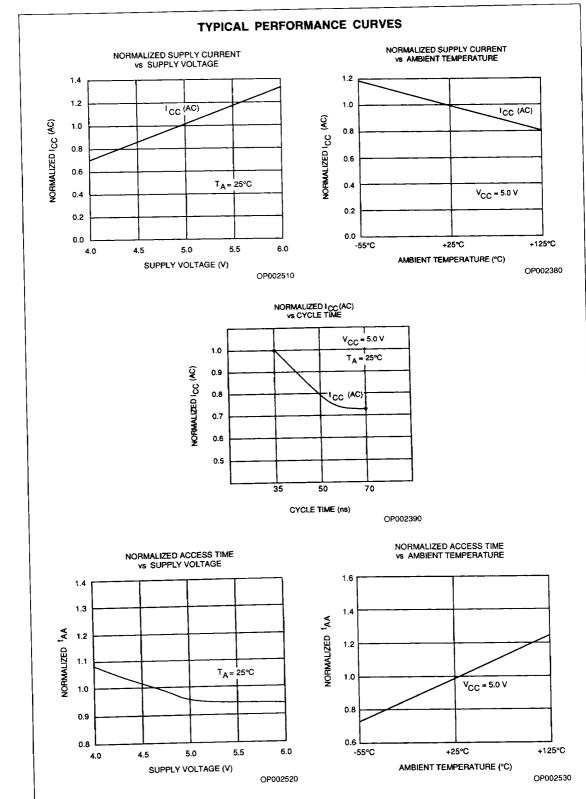

# **SWITCHING CHARACTERISTICS** over operating range unless otherwise specified (for APL Products, Group A, Subgroups 7, 8, 9 10, 11 are tested unless otherwise noted)

|     |                      |                 |                                                               |         |      |      | 99C164/<br>99C165/ |      |      |      |      |       |

|-----|----------------------|-----------------|---------------------------------------------------------------|---------|------|------|--------------------|------|------|------|------|-------|

|     | D                    |                 |                                                               | -35 -45 |      | _    | 55                 | -70  |      | 7    |      |       |

| No. | Parameter<br>Symbols |                 | Parameter<br>Description                                      | Min.    | Max. | Min. | Max.               | Min. | Max. | Min. | Max. | Units |

| RE  | AD CYCLES            | ONE, TW         | O, AND THREE (Note                                            | 9)      | •    |      |                    |      |      |      | 1    | 1     |

| 1   | tELQV                | tacs            | Chip Enable<br>Access Time                                    |         | 35   |      | 45                 |      | 55   |      | 70   | ns    |

| 2   | tavav                | t <sub>RC</sub> | Read Cycle Time                                               | 35      |      | 45   |                    | 55   |      | 70   |      | ns    |

| 3   | t <sub>AVQV</sub>    | taa             | Address Access<br>Time                                        |         | 35   |      | 45                 |      | 55   |      | 70   | ns    |

| 4   | t <sub>AXQX</sub>    | tон             | Output Hold After<br>Address                                  | 5       |      | 5    |                    | 5    |      | 5    |      | ns    |

| 5†  | tELQX                | tLZ             | Chip Enable to<br>Output Active<br>(Note 7)                   | 5       |      | 5    |                    | 5    |      | 5    |      | ns    |

| 6†  | t <sub>EHQZ</sub>    | tHZ             | Chip Disable to<br>Output Disable<br>(Note 7)                 |         | 15   |      | 15                 |      | 20   |      | 25   | ns    |

| 7†  | †ELICCH              | t <sub>PU</sub> | Chip Enable to<br>Power Up (Note 3)                           | 0       |      | 0    |                    | 0    |      | 0    |      | ns    |

| 8†  | †EHICCL              | tPD             | Chip Disable to<br>Power Down<br>(Note 3)                     | 0       | 35   | 0    | 45                 | 0    | 55   | 0    | 70   | ns    |

| WF  | RITE CYCLE           | S ONE AN        | D TWO (Note 9)                                                |         |      |      |                    |      |      | •    |      | _     |

| 9†  | tavav                | twc             | Write Cycle Time                                              | 35      |      | 45   |                    | 55   |      | 70   |      | ns    |

| 10† | twLwH                | twp             | Write Pulse Width (Note 5)                                    | 30      |      | 40   |                    | 50   |      | 60   |      | ns    |

| 11† | <sup>†</sup> ELWH    | tcw             | Chip Enable to<br>End of Write<br>(Note 5)                    | 35      |      | 40   |                    | 50   |      | 60   |      | ns    |

| 12  | tD∨WH                | t <sub>DW</sub> | Data Setup to End of Write                                    | 20      |      | 25   |                    | 30   |      | 30   |      | ns    |

| 13† | twHDX                | t <sub>DH</sub> | Data Hold After<br>End of Write                               | 0       |      | 0    |                    | 0    |      | 0    |      | ns    |

| 14† | t <sub>AVWH</sub>    | taw             | Address Setup to<br>End of Write<br>(Note 5)                  | 30      |      | 40   |                    | 50   |      | 60   |      | ns    |

| 15  | tavwl                | t <sub>AS</sub> | Address Setup to<br>Beginning of Write                        | 0       |      | 0    |                    | 0    |      | 0    |      | ns    |

| 16  | twhax                | twR             | Address Hold After<br>End of Write                            | 0       |      | 0    |                    | 0    |      | 0    |      | ns    |

| 17† | twLQZ                | t <sub>WZ</sub> | Write Enable to<br>Output Disable<br>(Notes 6 & 7)            | 0       | 10   | 0    | 15                 | 0    | 20   | 0    | 25   | ns    |

| 18† | twhqx                | tow             | Output Active After<br>End of Write<br>(Notes 6 & 7)          | 5       |      | 5    |                    | 5    |      | 5    |      | ns    |

| 19† | tGLQV                | <sup>t</sup> OE | Output Enable<br>Access Time<br>(Am99C165/<br>Am99CL165 only) |         | 15   |      | 20                 |      | 25   |      | 30   | ns    |

# SWITCHING CHARACTERISTICS (Cont'd.)

| No. |                      |      |                                                                                 | Am99C164/Am99CL164<br>Am99C165/Am99CL165 |      |      |      |      |      |      |      |       |

|-----|----------------------|------|---------------------------------------------------------------------------------|------------------------------------------|------|------|------|------|------|------|------|-------|

|     | Parameter<br>Symbols |      | Parameter<br>Description                                                        | -35                                      |      | -45  |      | -55  |      | -70  |      | 1     |

|     |                      |      |                                                                                 | Min.                                     | Max. | Min. | Max. | Min. | Max. | Min. | Max. | Units |

| 20† | <sup>†</sup> GLQX    | tolz | Output Enable to<br>Output Active<br>(Am99C165/<br>Am99CL165 only)<br>(Note 7)  | 5                                        |      | 5    |      | 5    |      | 5    |      | ns    |

| 21† | tgноz                | tонz | Output Enable to<br>Output Disable<br>(Am99C165/<br>Am99CL165 only)<br>(Note 7) | 0                                        | 15   | 0    | 15   | 0    | 15   | 0    | 15   | ns    |

Notes: 1. Absolute Maximum Ratings are intended for user guidelines and are not tested.

- 2. For test and correlation purposes, operating temperature is defined as the "instant-on" case temperature.

- 3. Parameter not tested—guaranteed by characterization.

- 4. Test conditions assume signal transition times of 5 ns or less, timing reference levels of 1.5 V, input-pulse levels of 0 to 3.0 V, and output loading of specified IOL/IOH and 30-pF load capacitance. Output timing reference is 1.5 V (see Test Load A in Switching Test Circuits section).

- 5. The internal write time of the memory is defined by the overlap of CE active and WE LOW. Both signals must be active to initiate a write and either signal can terminate a write by going inactive. The data input setup and hold timing should be referenced to the transition edge that terminates the write.

- 6. The minimum limit is not tested and is included for design information only.

- 7. Parameter not tested, guaranteed by characterization using the load shown in Test Load B-Switching Test Circuits. Transition is measured ±500 mV from steady state voltage.

- 8. Undershoot to -3.0 V for a duration of 10 ns between the 50% amplitude points is permissible.

- 9. Address input rise and fall times must not exceed 1  $\mu$ s when  $\overline{CE}$  is active. This limit is not tested and is intended for design information only.

† Not included in Group A tests

## SWITCHING WAVEFORMS

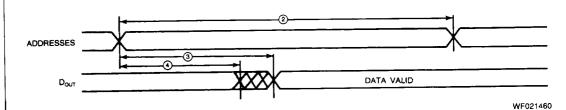

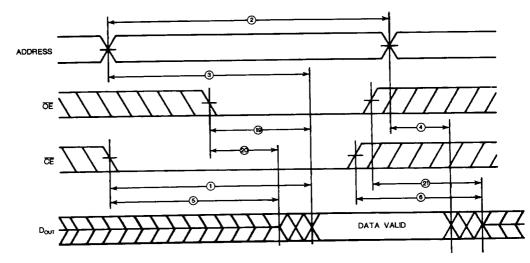

Read Cycle One (Notes 1, 2, & 4)

Read Cycle Two (Notes 1, 3, & 4)

WF022492

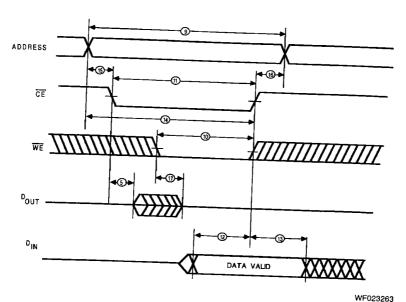

## Read Cycle Three (Notes 1 & 3) (Am99C165/Am99CL165 Only)

Notes: 1. WE is HIGH for Read Cycle.

- 2. CE is LOW for Read Cycle.

- 3. Address Valid prior to or coincident with CE transition LOW.

- 4.  $\overline{OE} = V_{IL}$  (Am99C165/Am99CL165 only)

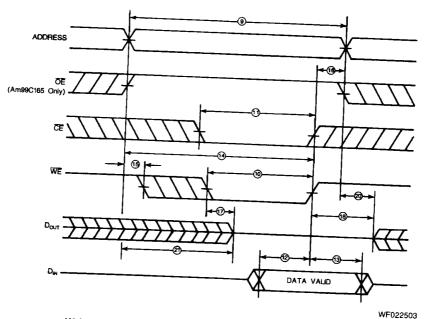

# SWITCHING WAVEFORMS (Cont'd.)

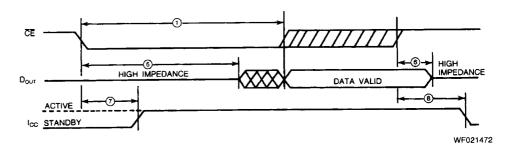

Write Cycle One (WE-Controlled) (Notes 1 & 3)

Write Cycle Two ( $\overline{\text{CE}}$ -Controlled) (Notes 1, 2, & 3)

Notes: 1. WE or CE must be HIGH during all address transitions.

- 2.  $\overline{OE}$  is continuously LOW ( $\overline{OE}$  = V<sub>IL</sub>) for Am99C165.

- 3. If CE LOW transition occurs simultaneously with WE LOW transition or after WE transition, outputs remain in a high-impedance state.

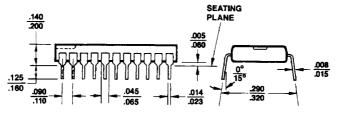

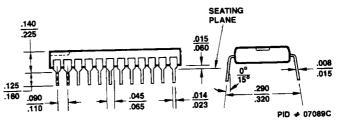

# PHYSICAL DIMENSIONS\* Am99C164

#### PD3022

PID # 07813B

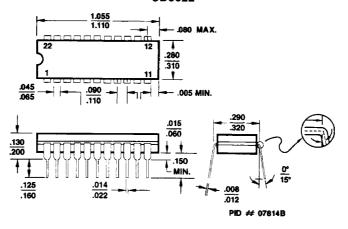

## CD3022

<sup>\*</sup>For reference only.

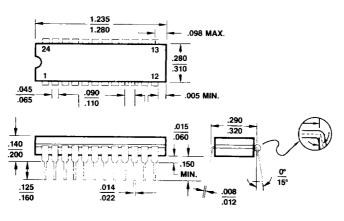

# PHYSICAL DIMENSIONS (Cont'd.)

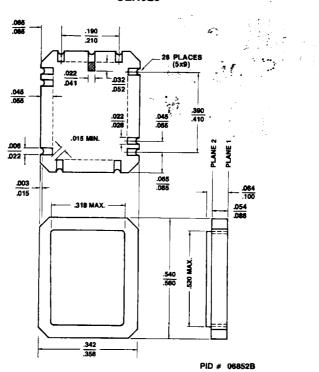

## CLR022\*

\*Preliminary; subject to change.

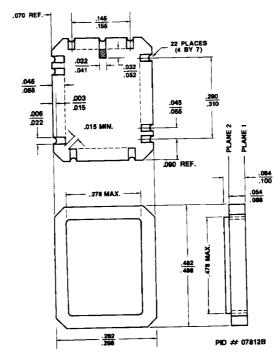

## Am99C165

# PD3024

# PHYSICAL DIMENSIONS (Cont'd.)

### CD3024

PID # 06850B

#### **CLR028**

Advanced Micro Devices reserves the right to make changes in its product without notice in order to improve design or performance characteristics. The performance characteristics listed in this document are guaranteed by specific testing certain guard banding, design and other practices common to the industry. For specific testing details, contact your local AMD sales representative. The company assumes no responsibility for the use of any circuits described herein.

ADVANCED MICRO DEVICES 901 Thompson Pl., P.O. Box 3453, Sunnyvale, CA 94088, USA TEL: (408) 732-2400 ● TWX: 910-339-9280 ● TELEX: 34-6306 ● TOLL FREE: (800) 538-8450

© 1987 Advanced Micro Devices, Inc. Printed in U.S.A. AIS-WCP-10M-7/87-0