## CMOS 2K x 8 ZEROPOWER SRAM

- LOW CURRENT (1µA @ 70°C) BATTERY INPUT FOR DATA RETENTION IN THE ABSENCE OF POWER

- DATA SECURITY PROVIDED BY AUTOMATIC WRITE PROTECTION DURING POWER FAILURE

- + 5 VOLT ONLY READ/WRITE

- CONVENTIONAL SRAM WRITE CYCLES

- LOW POWER 440mW ACTIVE; 5.5mW STANDBY

- READ-CYCLE TIME EQUALS WRITE-CYCLE TIME

- **LOW-BATTERY WARNING**

- TWO POWER-FAIL DESELECT TRIP POINTS AVAILABLE:

- $-MK48C02A4.75V \ge V_{PED} \ge 4.50V$

- $-MK48C12A4.50V \ge V_{PFD} \ge 4.20V$

- POWER FAIL INTERRUPT OUTPUT

#### DESCRIPTION

The MK48C02A/12A ZEROPOWER™ are CMOS RAM memories with internal power fail support circuitry for battery backup applications. The fully static RAM uses an HCMOS six transistor cell and is organized 2K x 8. Included in the device is a feature to conserve battery energy and a method of providing data security during V<sub>CC</sub> transients. A precision voltage detector write-protects the RAM to prevent inadvertent loss of data when V<sub>CC</sub> falls

#### PIN NAMES

| A0-A10         | Address Inputs                         |

|----------------|----------------------------------------|

| DQ0 - DQ7      | Data Inputs/Outputs                    |

| GND            | Ground                                 |

| Vcc            | 5 Volts                                |

| Ē              | Chip Enable                            |

| W              | Write Enable                           |

| G              | Output Enable                          |

| V <sub>B</sub> | Battery Input                          |

| INT            | Power Fail Interrupt (Open Drain Type) |

| NC             | No Connected                           |

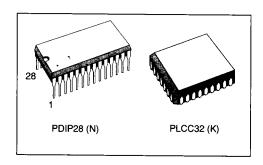

Figure 1. Pin Connections

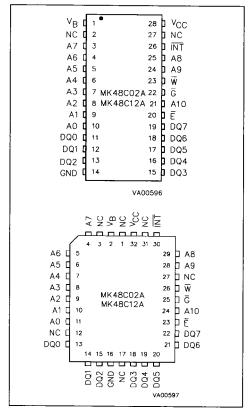

Figure 2. Block Diagram

### **DESCRIPTION** (Continued)

out of tolerance. In this way, all input and output pins (including  $\overline{E}$  and  $\overline{W}$ ) become "don't care". The device permits full functional ability of the RAM for V<sub>CC</sub> above 4.75V (MK48C02A) and 4.5V (MK48C12A). Data protection is provided for V<sub>CC</sub> below 4.5V (MK48C02A) and 4.2V (MK48C12A),

and maintains data in the absence of V<sub>CC</sub> with no additional support circuitry other than a primary cell. The current supplied by the battery during data retention is for junction leakage only (typically less than 5nA) because all power-consuming circuitry is turned off. The low battery drain allows use of a long life Lithium primary cell.

#### **TRUTH TABLE**

| Vcc                                       | Ē                        | G                    | w                      | Mode                              | DQ                                                      |

|-------------------------------------------|--------------------------|----------------------|------------------------|-----------------------------------|---------------------------------------------------------|

| <vcc(max)>Vcc(min)</vcc(max)>             | VIH<br>VIL<br>VIL<br>VIL | X<br>X<br>VIL<br>VIH | X<br>VIL<br>VIH<br>VIH | Deselect<br>Write<br>Read<br>Read | High-Z<br>D <sub>IN</sub><br>D <sub>OUT</sub><br>High-Z |

| <v<sub>PFD(min)&gt;V<sub>SO</sub></v<sub> | ×                        | ×                    | х                      | Power-Fail<br>Deselect            | High-Z                                                  |

| ≤V <sub>SO</sub>                          | ×                        | ×                    | ×                      | Battery<br>Back-up                | High-Z                                                  |

#### **ABSOLUTE MAXIMUM RATINGS**

| Symbol           | Parameter                                         | Value        | Unit |  |

|------------------|---------------------------------------------------|--------------|------|--|

| Vı               | Voltage On Any Pin Relative to Ground             | -0.3 to +7.0 | V    |  |

| TA               | Ambient Operating Temperature                     | 0 to +70     | °C   |  |

| T <sub>STG</sub> | Ambient Storage (V <sub>CC</sub> Off) Temperature | -55 to +125  | °C   |  |

| PD               | Total Device Power Dissipation                    | 1            | W    |  |

| lout             | Output Current Per Pin                            | 20           | mA   |  |

Notes: Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

CAUTION: Under no conditions can the "Absolute Maximum Ratings" for the voltage on any pin be exceeded since it will cause permanent damage. Specifically, do not perform the "standard" continuity test on any input or output pin, i.e. do not force these pins below - 0.3V DC.

## RECOMMENDED DC OPERATING CONDITIONS

$(0^{\circ}C \leq T_A \leq 70^{\circ}C)$

| Symbol          | Parameter                    | Min. | Max.                   | Unit | Notes |

|-----------------|------------------------------|------|------------------------|------|-------|

| Vcc             | Supply Voltage (MK48C02A)    | 4.75 | 5.5                    | ٧    | 1     |

| Vcc             | Supply Voltage (MK48C12A)    | 4.5  | 5.5                    | ٧    | 1     |

| GND             | Ground                       | 0    | 0                      | ٧    | 1     |

| V <sub>IH</sub> | Logic "1" Voltage All Inputs | 2.2  | V <sub>CC</sub> + 0.3V | V    | 1     |

| VIL             | Logic "0" Voltage All Inputs | -0.3 | 0.8                    | ٧    | 1, 2  |

| VB              | Battery Voltage              | 1.8  | 4.0                    | V    | 1     |

#### DC ELECTRICAL CHARACTERISTICS

$(0^{\circ}C \le T_A \le 70^{\circ}C \ V_{CC \ max} \ge V_{CC} \ge V_{CC \ min})$

| Symbol           | Parameter                                            | Min. | Max. | Unit | Note |

|------------------|------------------------------------------------------|------|------|------|------|

| lcc1             | Average V <sub>CC</sub> Power Supply Current         |      | 80   | mA   | 3    |

| I <sub>CC2</sub> | TTL Standby Current (E= V <sub>IH</sub> )            |      | 3    | mA   |      |

| Іссз             | CMOS Standby Current (E ≥ V <sub>CC</sub> -0.2V)     |      | 1    | mA   |      |

| lıL              | Input Leakage Current (Any Input)                    | -1   | 1    | μА   | 4    |

| loL              | Output Leakage Current                               | -5   | 5    | μА   | 4    |

| VoH              | Output Logic "1" Voltage (I <sub>OUT</sub> = -1.0mA) | 2.4  |      | ٧    |      |

| VOL              | Output Logic "0" Voltage (I <sub>OUT</sub> = 2.1mA)  |      | 0.4  | ٧    |      |

| V <sub>PFL</sub> | INT Logic "0" Voltage (I <sub>OUT</sub> = 0.5 mA)    |      | 0.4  | V    |      |

| IBATT            | Battery Backup Current V <sub>B</sub> = 4.0V         |      | 1    | μА   |      |

| Існа             | Battery Charging Current V <sub>CC</sub> = 5.5V      | -5   | 5    | nA   |      |

| V <sub>LB</sub>  | Battery OK Flag                                      | 1.8  | 2.6  | V    | -    |

#### **AC TEST CONDITIONS**

| Input Levels                             | 0.6 V to 2.4 V |

|------------------------------------------|----------------|

| Transition Times                         | 5 ns           |

| Input and Output Timing Reference Levels | 0.8 V or 2.2 V |

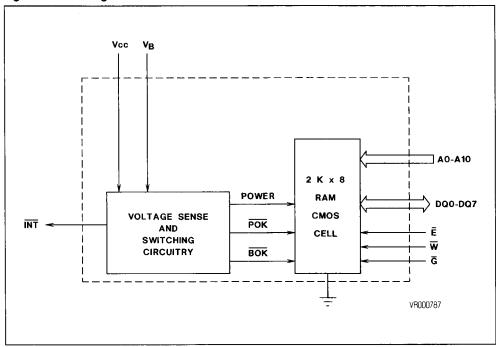

### **OUTPUT LOAD DIAGRAM**

## **CAPACITANCE**

$(T_A = 25^{\circ}C)$

| Symbol           | Parameter                            | Max.  | Notes |

|------------------|--------------------------------------|-------|-------|

| Cı               | Capacitance on all pins (except D/Q) | 7 pF  | 5     |

| C <sub>D/Q</sub> | Capacitance on D/Q pins and INT      | 10 pF | 4, 5  |

#### Notes:

- All voltages referenced to GND Negative spikes of -1.0 volts allowed for up to 10ns once per cycle. lcc: measured with outputs open. Measured with GND  $\leq$  V  $\leq$  Vcc and outputs deselected. Effective capacitance calculated from the equation C =  $1 \Delta t/\Delta V$  with  $\Delta V = 3$  volts and power supply at nominal level.

#### **OPERATION**

#### **Read Mode**

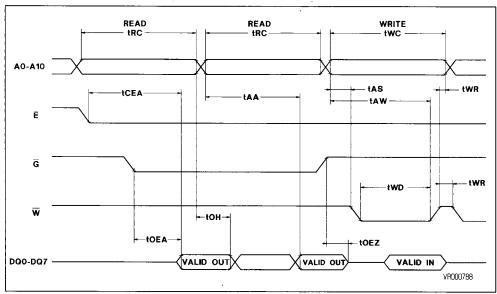

The MK48C02A/12A is in the Read Mode whenever W (Write Enable) is high and E (Chip Enable) is low, providing a ripple-through access of data from eight of 16,384 locations in the static storage array. Thus, the unique address specified by the 11 Address Inputs (An) defines which one of 2,048 bytes of data is to be accessed.

Valid data will be available to the eight data Output Drivers within  $t_{AA}$  after the last address input signal is stable, providing that the  $\overline{E}$  and  $\overline{G}$  access times are satisfied. If  $\overline{E}$  or  $\overline{G}$  access times are not met, data access will be measured from the limiting parameter ( $t_{CEA}$  or  $t_{OEA}$ ), rather than the address. The state of the eight Data I/O signals is controlled by the  $\overline{E}$  and  $\overline{G}$  control signals. The data lines may be in an indeterminate state between  $t_{OH}$  and  $t_{AA}$ , but the data lines will always have valid data at  $t_{AA}$ .

Figure 3. Read-Read-Write Timing

## AC ELECTRICAL CHARACTERISTICS (Read Cycle Timing)

$(0^{\circ}C \le T_A \le 70^{\circ}C; V_{CC \max} \ge V_{CC} \ge V_{CC \min})$

| Symbol          | Parameter                  | 48CX | 48CX2A-15 |      | 48CX2A-20 |      | 2A-25 | Unit | Notes |

|-----------------|----------------------------|------|-----------|------|-----------|------|-------|------|-------|

|                 |                            | Min. | Max.      | Min. | Max.      | Min. | Max.  | Oint | Notes |

| t <sub>RC</sub> | Read Cycle Time            | 150  |           | 200  |           | 250  |       | ns   |       |

| taa             | Address Access Time        |      | 150       |      | 200       |      | 250   | ns   | 1     |

| tcea            | Chip Enable Access Time    |      | 150       |      | 200       |      | 250   | ns   | 1     |

| toea            | Output Enable Access Time  |      | 75        |      | 80        |      | 90    | ns   | 1     |

| tcez            | Chip Enable Hi to High-Z   |      | 35        |      | 40        |      | 50    | ns   |       |

| toez            | Output Enable Hi to High-Z |      | 35        |      | 40        |      | 50    | ns   |       |

| tон             | Valid Data Out Hold Time   | 15   |           | 15   |           | 15   |       | ns   | 1     |

Note: Measured using the Output Load Diagram shown page 4.

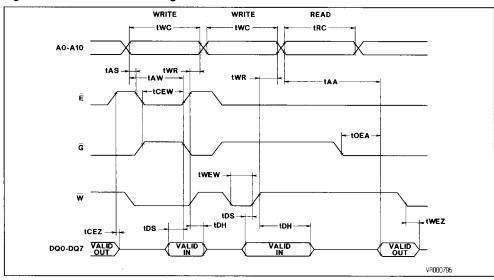

#### WRITE MODE

The MK48C02A/12A is in Write Mode whenever the  $\overline{W}$  and  $\overline{E}$  inputs are held low. The start of a Write is referenced to the latter occurring falling edge of either  $\overline{W}$  or  $\overline{E}$ . A Write is terminated by the earlier rising edge of  $\overline{W}$  or  $\overline{E}$ . The addresses must be held valid throughout the cycle.  $\overline{W}$  or  $\overline{E}$  must return high, for a minimum of  $t_{WR}$  prior to the initiation of another Read or Write Cycle. Data-in must be valid for  $t_{DH}$  prior to the End of Write and remain valid for  $t_{DH}$  afterwards.

Some processors thrash producing spurious Write Cycles during power-up, despite application of a power-on reset. Users should force  $\overline{W}$  or  $\overline{E}$  high during power-up to protect memory after Vcc reaches Vcc (min) but before the processor stabilizes

The MK48C02A/12A  $\overline{G}$  input is a DON'T CARE in the write mode.  $\overline{G}$  can be tied low and two-wire RAM control can be implemented. A low on  $\overline{W}$  will disable the outputs twez after  $\overline{W}$  falls. Take care to avoid bus contention when operating with two-wire control.

Figure 4. Write-Write-Read Timing

## AC ELECTRICAL CHARACTERISTICS (Write Cycle Timing)

$(0^{\circ}C \le T_A \le 70^{\circ}C; V_{CC \max} \ge V_{CC} \ge V_{CC \min})$

| Symbol      | Parameter                     | 48CX | 48CX2A-15 |      | 2A-20 | 48CX2A-25 |      | Unit |

|-------------|-------------------------------|------|-----------|------|-------|-----------|------|------|

| Jy111001    |                               | Min. | Max.      | Min. | Max.  | Min.      | Max. | Olim |

| twc         | Write Cycle Time              | 150  |           | 200  |       | 250       |      | ns   |

| tas         | Address Setup Time            | 0    |           | 0    |       | 0         |      | ns   |

| taw         | Address Valid to End of Write | 120  |           | 140  |       | 180       |      | ns   |

| tcew        | Chip Enable to End of Write   | 90   |           | 120  |       | 160       |      | ns   |

| twew        | Write Enable to End of Write  | 90   |           | 120  |       | 160       |      | ns   |

| twn         | Write Recovery Time           | 10   |           | 10   |       | 10        |      | ns   |

| tos         | Data Setup Time               | 40   |           | 60   |       | 100       |      | ns   |

| <b>t</b> DH | Data Hold Time                | 5    |           | 5    |       | 5         |      | ns   |

| twez        | Write Enable Low to High-Z    |      | 50        |      | 60    |           | 80   | ns   |

#### **DATA RETENTION MODE**

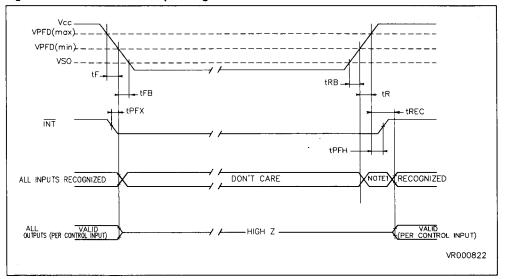

With V<sub>CC</sub> applied, the MK48C02A/12A operates as a conventional BYTEWIDE static RAM. However, V<sub>CC</sub> is being constantly monitored. Should the supply voltage decay, the RAM will automatically power-fail deselect, write protecting itself when V<sub>CC</sub> falls within the V<sub>PFD</sub> (max), V<sub>PFD</sub> (min) window. The MK48C02A has a V<sub>PFD</sub> (max) - V<sub>PFD</sub> (min) window of 4.75 volts to 4.5 volts, providing very high data security, particularly when all of the other system components are specified to 5.0 volts plus and minus 10%. The MK48C12A has a V<sub>PFD</sub> (max) - V<sub>PFD</sub> (min) window of 4.5 volts to 4.2 volts, allowing users constrained to a 10% power supply specification to use the device.

Note: A mid-write cycle power failure may corrupt data at the current address location, but does not jeopardize the rest of the RAM's content. At voltages below V<sub>PFD</sub> (min), the user can be assured the memory will be in a write protected state, provided the V<sub>CC</sub> fall time does not exceed t<sub>F</sub>. The MK48C02A/12A may respond to transient noise spikes that reach into the deselect window if they should occur during the time the device is sampling V<sub>CC</sub>. Therefore decoupling of power supply lines is recommended.

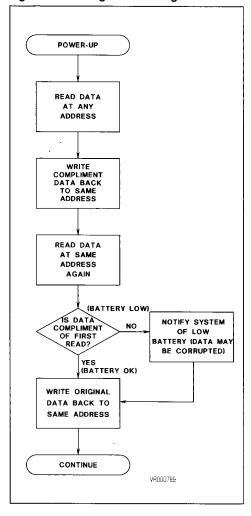

The power switching circuit connects external  $V_{CC}$  to the RAM and disconnects the battery when  $V_{CC}$  rises above  $V_{SO}$ . As  $V_{CC}$  rises the battery voltage is checked. If the voltage is too low, an internal Battery Not OK ( $\overline{BOK}$ ) flag will be set. The  $\overline{BOK}$  flag can be checked after power up. If the  $\overline{BOK}$  flag is set, the first write attempted will be blocked. The flag is automatically cleared after the first write, and normal RAM operation resumes. Figure 5 illustrates how a  $\overline{BOK}$  check routine could be structured.

Normal RAM operation can resume  $t_{REC}$  after  $V_{CC}$  exceeds  $V_{PED}$  (Max). Caution should be taken to keep  $\overline{E}$  or  $\overline{W}$  high as  $V_{CC}$  rises past  $V_{PED}$  (Min) as some systems may perform inadvertent write cycles after  $V_{CC}$  rises but before normal system operation begins.

#### INTERRUPT FUNCTION

The MK48C02A/12A provides a power-fail interrupt output labeled  $\overline{\text{INT}}$ . The  $\overline{\text{INT}}$  pin eliminates the need for external power sensing components in applications where an orderly shut down of the system is necessary. The  $\overline{\text{INT}}$  pin is open drain for "wire or" applications and provides the user with 10 $\mu$ s to 40 $\mu$ s advanced warning of an impending power-fail write protect.

Figure 5. Checking the BOK Flag Status

# AC ELECTRICAL CHARACTERISTICS (Power-Down/Power-Up Timing) $(0^{\circ}C \leq T_A \leq +70^{\circ}C)$

| Symbol           | Parameter                                                                  | Min. | Тур. | Max. | Unit | Note |

|------------------|----------------------------------------------------------------------------|------|------|------|------|------|

| tF               | V <sub>PFD</sub> (max) to V <sub>PFD</sub> (min) V <sub>CC</sub> Fall Time | 300  |      |      | μs   | 2    |

| t <sub>FB</sub>  | V <sub>PFD</sub> (min) to V <sub>SO</sub> V <sub>CC</sub> Fall Time        | 10   |      |      | μs   | 3    |

| t <sub>RB</sub>  | V <sub>SO</sub> to V <sub>PFD</sub> (min) V <sub>CC</sub> Rise Time        | 1    |      |      | μs   |      |

| t <sub>R</sub>   | V <sub>PFD</sub> (min) to V <sub>PFD</sub> (max) V <sub>CC</sub> Rise Time | 0    |      |      | μs   |      |

| trec             | E or W at V <sub>IH</sub> after V <sub>PFD</sub> (max)                     | 120  |      |      | μs   |      |

| t <sub>PFX</sub> | INT Low to Auto Deselect                                                   | 10   |      | 40   | μs   |      |

| tpfH             | V <sub>PFD</sub> (max) to INT High                                         |      |      | 120  | μs   | 4    |

# DC ELECTRICAL CHARACTERISTICS (Power-Down/Power-Up Trip Point Voltages) $(0^{\circ}C \le T_A \le +70^{\circ}C)$

| Symbol    | Parameter                              | Min. | Тур. | Max. | Unit | Note |

|-----------|----------------------------------------|------|------|------|------|------|

| $V_{PFD}$ | Power-Fail Deselect Voltage (MK48C02A) | 4.50 | 4.6  | 4.75 | ٧    | 1    |

| $V_{PFD}$ | Power-Fail Deselect Voltage (MK48C12A) | 4.20 | 4.3  | 4.50 | ٧    | 1    |

| Vso       | Battery Back-Up Switchover Voltage     |      | 3    |      | ٧    | 1    |

#### Notes :

- 1. All voltages referenced to GND.

- V<sub>PFD</sub> (Max) to V<sub>PFD</sub> (Min) fall times of less t<sub>F</sub> may result in deselection/write protection not occurring until 40µs after V<sub>CC</sub> passes V<sub>PFD</sub> (Min).

- 3. V<sub>PFD</sub> (Min) to V<sub>SO</sub> fall times of less than t<sub>FB</sub> may cause corruption of RAM data.

- 4. INT may go high anytime after V<sub>CC</sub> exceeds V<sub>PFD</sub> (min) and is guaranteed to go high t<sub>PFH</sub> after V<sub>CC</sub> exceeds V<sub>PFD</sub> (max).

CAUTION: Negative Undershoots Below -0.3V are not allowed on any pin while in Battery Back-up mode .

Figure 6. Power-Down/Power-Up Timing

#### Notes:

- 1. Inputs may or may not be recognized at this time.

- 2. Caution should be taken to keep \(\overline{E}\) or \(\overline{W}\) in the high state V<sub>CC</sub> rises past V<sub>PFD</sub> (min). Some systems may perform inadvertent write cycles after V<sub>CC</sub> rises but before normal system operation begins. Even though a power on reset is being applied to the processor a reset condition may not occur until after the system clock is running.

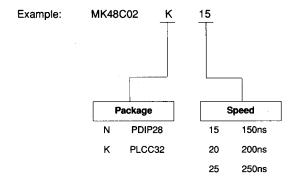

#### ORDERING INFORMATION

For a list of available options of Package and Speed refer to the Selector Guide in this Data Book or the current Memory Shortform that will be periodically up-dated.

For further information or any aspect of this device, please contact our Sales Office nearest to you.