#### TOSHIBA MOS DIGITAL INTEGRATED CIRCUIT SILICON GATE CMOS

# 524,288-WORD BY 8-BIT STATIC RAM

#### **DESCRIPTION**

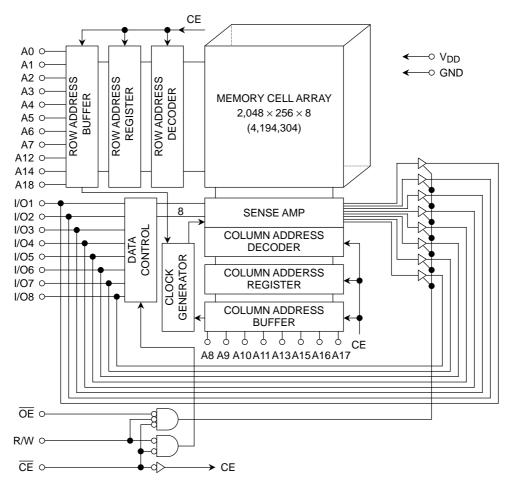

The TC554001AF/AFT/ATR is a 4,194,304-bit static random access memory (SRAM) organized as 524,288 words by 8 bits. Fabricated using Toshiba's CMOS Silicon gate process technology, this device operates from a single 2.7 to 5.5 V power supply. Advanced circuit technology provides both high speed and low power at an operating current of 10 mA/MHz (typ) and a minimum cycle time of 70 ns. It is automatically placed in low-power mode at 2  $\mu$ A standby current (typ) when chip enable ( $\overline{CE}$ ) is asserted high. There are two control inputs.  $\overline{CE}$  is used to select the device and for data retention control, and output enable ( $\overline{OE}$ ) provides fast memory access. This device is well suited to various microprocessor system applications where high speed, low power and battery backup are required. The TC554001AF/AFT/ATR is available in a standard plastic 32-pin small-outline package (SOP) and normal and reverse pinout plastic 32-pin thin-small-outline package (TSOP).

#### **FEATURES**

- Low-power dissipation Operating: 55 mW/MHz (typical)

- Standby current of 5  $\mu$ A (maximum) at Ta = 25°C

- Single power supply voltage of 2.7 to 5.5 V

- Power down features using  $\overline{CE}$ .

- Data retention supply voltage of 2.0 to 5.5 V

- Direct TTL compatibility for all inputs and outputs

#### Access Times (maximum):

|                | Ę     | 5 V ± 10% | 2.7 V~5.5 V |        |           |

|----------------|-------|-----------|-------------|--------|-----------|

|                | -70V  | -85V      | -10V        | -70V   | -85V/-10V |

| Access Time    | 70 ns | 85 ns     | 100 ns      | 120 ns | 150 ns    |

| CE Access Time | 70 ns | 85 ns     | 100 ns      | 120 ns | 150 ns    |

| OE Access Time | 35 ns | 45 ns     | 50 ns       | 70 ns  | 75 ns     |

Package:

SOP32-P-525-1.27 (AF) TSOP II32-P-400-1.27 (AFT) TSOP II32-P-400-1.27A (ATR)

**PIN NAMES**

(Weight: 1.14 g typ) (Weight: 0.53 g typ) (Weight: 0.53 g typ)

#### **PIN ASSIGNMENT (TOP VIEW)**

32 PIN SOP & TSOP

32 PIN TSOP

| A18 🗆  | 1       | 32 VDD           |          | 32    | 1 🗆 A18   |

|--------|---------|------------------|----------|-------|-----------|

| A16 🗆  | 2       | 31 🛛 A15         | A15 🔤    | 31    | 2 🛛 A16   |

| A14 🗆  | 3       | 30 🛛 A17         | A17 🔤    | 30    | 3 🛛 A14   |

| A12 🗆  | 4       | 29 🛛 R/W         | R/W □    | 29    | 4 🏳 A12   |

| A7 🗆   | 5       | 28 🛛 A13         | A13 🛛 🛛  | 28    | 5 🏽 A7    |

| A6 🗆   | 6       | 27 🛛 A8          | A8 🗆 :   | 27    | 6 🏳 A6    |

| A5 🗆   | 7       | 26 🛛 A9          | A9 🗆 :   | 26    | 7 🏳 A5    |

| A4 🗆   | 8       | 25 🛛 A11         | A11 🗆    | 25    | 8 🏽 A4    |

| A3 🗆   | 9       | 24 🛛 🖸           | OE 🗆     | 24    | 9 🏳 A3    |

| A2 🗆   | 10      | 23 🛛 <u>A1</u> 0 | A10 🗌    | 23    | 10 🏳 A2   |

| A1 🗆   | 11      | 22 🛛 CE          | CE 🛛     | 22    | 11 🏳 A1   |

| A0 🗆   | 12      | 21 🛛 I/O8        | I/O8 🛛 : | 21    | 12 🏳 A0   |

| I/O1 🗆 | 13      | 20 🛛 1/07        | I/O7 🛛 : | 20    | 13 🏳 I/O1 |

| I/O2 🗆 | 14      | 19 🛛 I/O6        | I/O6 🏼   | 19    | 14 🏳 I/O2 |

| I/O3 🗆 | 15      | 18 🛛 I/O5        | I/O5 🛛   | 18    | 15 🏳 I/O3 |

| GND 🛛  | 16      | 17 🛛 I/O4        | I/O4 🛛   | 17    | 16 🛛 GND  |

|        | (AF/AFT | )                |          | (ATR) |           |

| A0~A18          | Address Inputs      |

|-----------------|---------------------|

| R/W             | Read/Write Control  |

| ŌĒ              | Output Enable       |

| CE              | Chip Enable         |

| I/O1~I/O8       | Data Inputs/Outputs |

| V <sub>DD</sub> | Power (+5 V)        |

| GND             | Ground              |

# <u>TOSHIBA</u>

# **BLOCK DIAGRAM**

# **OPERATING MODE**

| MODE            | CE | ŌĒ | R/W | I/O1~I/O8 | POWER            |

|-----------------|----|----|-----|-----------|------------------|

| Read            | L  | L  | н   | Output    | I <sub>DDO</sub> |

| Write           | L  | *  | L   | Input     | I <sub>DDO</sub> |

| Output Deselect | L  | Н  | Н   | High-Z    | I <sub>DDO</sub> |

| Standby         | Н  | *  | *   | High-Z    | IDDS             |

\* = don't care

H = logic high

L = logic low

# **MAXIMUM RATINGS**

| SYMBOL              | RATING                      | VALUE                      | UNIT |

|---------------------|-----------------------------|----------------------------|------|

| V <sub>DD</sub>     | Power Supply Voltage        | -0.3~7.0                   | V    |

| V <sub>IN</sub>     | Input Voltage               | -0.3*~7.0                  | V    |

| V <sub>I/O</sub>    | Input/Output Voltage        | -0.5~V <sub>DD</sub> + 0.5 | V    |

| PD                  | Power Dissipation           | 0.6                        | W    |

| T <sub>solder</sub> | Soldering Temperature (10s) | 260                        | °C   |

| T <sub>stg</sub>    | Storage Temperature         | -55~150                    | °C   |

| T <sub>opr</sub>    | Operating Temperature       | 0~70                       | °C   |

\*: -3.0 V when measured at a pulse width of 50ns

# **DC RECOMMENDED OPERATING CONDITIONS** (Ta = $0^{\circ}$ to $70^{\circ}$ C)

| SYMBOL          | PARAMETER                     | $5 \text{ V} \pm 10\%$ |     |                       |                       | UNIT |                       |      |

|-----------------|-------------------------------|------------------------|-----|-----------------------|-----------------------|------|-----------------------|------|

| STNIBOL         | FARAIVIETER                   | MIN                    | TYP | MAX                   | MIN                   | TYP  | MAX                   | UNIT |

| V <sub>DD</sub> | Power Supply Voltage          | 4.5                    | 5.0 | 5.5                   | 2.7                   | 5.0  | 5.5                   | V    |

| VIH             | Input High Voltage            | 2.2                    | _   | V <sub>DD</sub> + 0.3 | V <sub>DD</sub> - 0.2 |      | V <sub>DD</sub> + 0.3 | V    |

| VIL             | Input Low Voltage             | -0.3*                  | _   | 0.8                   | -0.3*                 |      | 0.2                   | V    |

| V <sub>DH</sub> | Data Retention Supply Voltage | 2.0                    | _   | 5.5                   | 2.0                   | _    | 5.5                   | V    |

\*: -3.0V when measured at a pulse width of 50 ns

# <u>DC CHARACTERISTICS</u> (Ta = 0° to 70°C, V<sub>DD</sub> = 5 V $\pm$ 10%)

| SYMBOL            | PARAMETER                 | TEST                                                                       | CONDITION                           |                           | MIN  | TYP | MAX  | UNIT |  |

|-------------------|---------------------------|----------------------------------------------------------------------------|-------------------------------------|---------------------------|------|-----|------|------|--|

| IIL               | Input Leakage<br>Current  | $V_{IN} = 0 V \sim V_{DD}$                                                 |                                     |                           |      | _   | ±1.0 | μΑ   |  |

| ILO               | Output Leakage<br>Current | $\overline{CE} = V_{IH} \text{ or } R/W = V_{IL}$                          | or $\overline{OE} = V_{IH}, V_{IH}$ | OUT = 0 V~V <sub>DD</sub> |      | _   | ±1.0 | μΑ   |  |

| I <sub>OH</sub>   | Output High Current       | V <sub>OH</sub> = 2.4 V                                                    |                                     |                           | -1.0 | _   | _    | mA   |  |

| I <sub>OL</sub>   | Output Low Current        | $V_{OL} = 0.4 V$                                                           |                                     |                           | 2.1  | _   | _    | mA   |  |

|                   |                           | $\overline{CE} = V_{IL}$ and $R/W = V_{II}$                                | Ч,                                  | t <sub>cycle</sub> = MIN  |      |     | 70   |      |  |

| IDDO1             |                           | I <sub>OUT</sub> = 0 mA,<br>Other Input = V <sub>IH</sub> /V <sub>IL</sub> |                                     | $t_{cycle} = 1 \ \mu s$   | _    | 15  | _    | mA   |  |

|                   | Operating Current         | $\overline{CE} = 0.2 \text{ V} \text{ and } \text{R/W} = V$                | V <sub>DD</sub> – 0.2 V,            | t <sub>cycle</sub> = MIN  |      | _   | 60   |      |  |

| IDDO2             |                           | $I_{OUT} = 0 \text{ mA},$<br>Other Input = $V_{DD} - 0.2 \text{ V}$        | V/0.2 V                             | t <sub>cycle</sub> = 1 μs |      | 10  |      | mA   |  |

| I <sub>DDS1</sub> |                           | CE = V <sub>IH</sub>                                                       |                                     |                           |      |     | 3    | mA   |  |

|                   |                           |                                                                            | V <sub>DD</sub> =                   | Ta = 25°C                 |      | 2   | 5    |      |  |

|                   | Stondby Current           |                                                                            | 2.0 V~5.5 V                         | Ta = 0~70°C               |      |     | 50   |      |  |

| I <sub>DDS2</sub> | Standby Current           | $\overline{\text{CE}} = \text{V}_{DD} - 0.2 \text{ V},$                    |                                     | Ta = 25°C                 | _    | 2   | —    | μA   |  |

|                   |                           |                                                                            | $V_{DD} = 3.0 V$                    | Ta = 0~40°C               | —    | —   | 5    |      |  |

|                   |                           |                                                                            |                                     | Ta = 0~70°C               | _    | _   | 25   |      |  |

# **DC CHARACTERISTICS** (Ta = $0^{\circ}$ to $70^{\circ}$ C, V<sub>DD</sub> = 3.0 V ± 10%)

| SYMBOL            | PARAMETER                 | TES                                                                                                                    | CONDITION                           |                           | MIN  | TYP | MAX  | UNIT |

|-------------------|---------------------------|------------------------------------------------------------------------------------------------------------------------|-------------------------------------|---------------------------|------|-----|------|------|

| IIL               | Input Leakage<br>Current  | $V_{IN} = 0 V \sim V_{DD}$                                                                                             |                                     |                           |      |     | ±1.0 | μΑ   |

| ILO               | Output Leakage<br>Current | $\overline{CE} = V_{IH} \text{ or } R/W = V_{IL}$                                                                      | or $\overline{OE} = V_{IH}, V_{IH}$ | OUT = 0 V~V <sub>DD</sub> |      |     | ±1.0 | μΑ   |

| I <sub>OH</sub>   | Output High Current       | $V_{OH} = V_{DD} - 0.2 V$                                                                                              |                                     |                           | -1.0 |     |      | mA   |

| I <sub>OL</sub>   | Output Low Current        | $V_{OL} = 0.2 V$                                                                                                       |                                     |                           | 0.1  |     |      | mA   |

|                   | On contine of Course and  | $\overline{CE} = 0.2 \text{ V} \text{ and } \text{R/W} = \text{V}_{DD} - 0.2 \text{ V}, \qquad t_{cycle} = \text{MIN}$ |                                     |                           | _    | 30  |      |      |

| IDDO2             | Operating Current         | I <sub>OUT</sub> = 0 mA,<br>Other Input = V <sub>DD</sub> - 0.2                                                        | V/0.2 V                             | $t_{cycle} = 1 \ \mu s$   |      | 5   |      | mA   |

|                   |                           |                                                                                                                        | V <sub>DD</sub> =                   | Ta = 25°C                 |      | 2   | 3    |      |

|                   |                           |                                                                                                                        | $3.0\pm0.3$ V                       | Ta = 0~70°C               |      |     | 28   |      |

| I <sub>DDS2</sub> | Standby Current           | $\overline{\text{CE}} = \text{V}_{\text{DD}} - 0.2 \text{ V},$ $\text{V}_{\text{DD}} = 3.0 \text{ V}$                  |                                     | Ta = 25°C                 |      | 2   |      | μΑ   |

|                   |                           |                                                                                                                        |                                     | Ta = 0~40°C               |      |     | 5    |      |

|                   |                           |                                                                                                                        |                                     | Ta = 0~70°C               |      |     | 25   |      |

# CAPACITANCE (Ta = 25°C, f = 1 MHz)

| SYMBOL           | PARAMETER          | TEST CONDITION         | MAX | UNIT |

|------------------|--------------------|------------------------|-----|------|

| C <sub>IN</sub>  | Input Capacitance  | $V_{IN} = GND$         | 10  | pF   |

| C <sub>OUT</sub> | Output Capacitance | V <sub>OUT</sub> = GND | 10  | pF   |

Note: This parameter is periodically sampled and is not 100% tested.

# <u>AC CHARACTERISTICS AND OPERATING CONDITIONS</u> (Ta = 0° to 70°C, $V_{DD}$ = 5 V ± 10%)

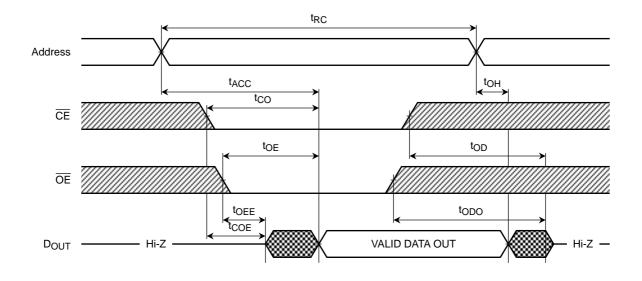

# READ CYCLE

| SYMBOL           | PARAMETER                           | -7  | 0V  | -8  | 5V  | -1  | 0V  | UNIT |

|------------------|-------------------------------------|-----|-----|-----|-----|-----|-----|------|

|                  |                                     | MIN | MAX | MIN | MAX | MIN | MAX |      |

| t <sub>RC</sub>  | Read Cycle Time                     | 70  |     | 85  | _   | 100 |     |      |

| tACC             | Address Access Time                 | _   | 70  | _   | 85  | _   | 100 |      |

| t <sub>CO</sub>  | Chip Enable Access Time             |     | 70  | _   | 85  | _   | 100 |      |

| t <sub>OE</sub>  | Output Enable Access Time           | _   | 35  | _   | 45  | _   | 50  |      |

| t <sub>COE</sub> | Chip Enable Low to Output Active    | 10  | _   | 10  | _   | 10  | _   | ns   |

| tOEE             | Output Enable Low to Output Active  | 5   |     | 5   | _   | 5   | _   |      |

| t <sub>OD</sub>  | Chip Enable High to Output High-Z   | _   | 25  | _   | 30  | _   | 35  |      |

| todo             | Output Enable High to Output High-Z |     | 25  |     | 30  |     | 35  |      |

| t <sub>OH</sub>  | Output Data Hold Time               | 10  |     | 10  |     | 10  |     |      |

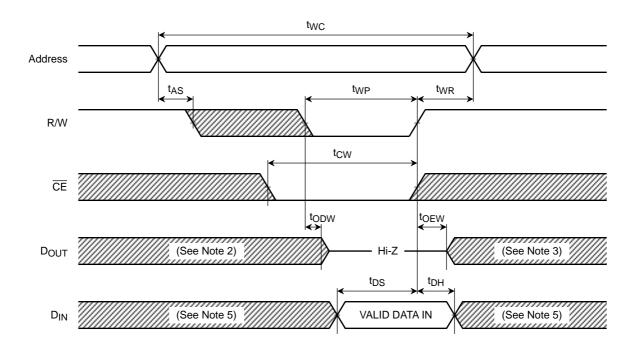

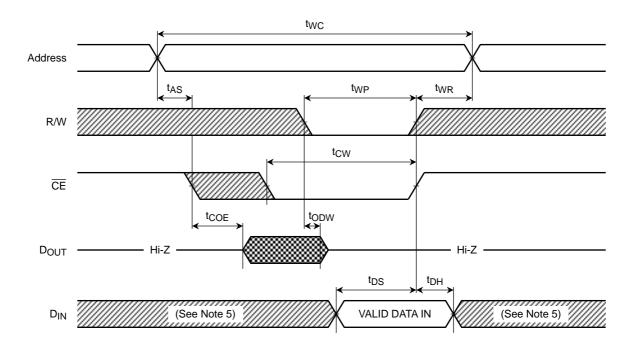

#### WRITE CYCLE

|                 |                             |     | Т   | C554001A | AF/AFT/AT | ſR  |     |      |

|-----------------|-----------------------------|-----|-----|----------|-----------|-----|-----|------|

| SYMBOL          | PARAMETER                   | -7  | 0V  | -8       | 5V        | -1  | 0V  | UNIT |

|                 |                             | MIN | MAX | MIN      | MAX       | MIN | MAX |      |

| t <sub>WC</sub> | Write Cycle Time            | 70  |     | 85       |           | 100 |     |      |

| t <sub>WP</sub> | Write Pulse Width           | 50  | _   | 55       | _         | 60  | _   |      |

| t <sub>CW</sub> | Chip Enable to End of Write | 60  |     | 70       |           | 80  | _   |      |

| t <sub>AS</sub> | Address Setup Time          | 0   | —   | 0        | —         | 0   | —   |      |

| t <sub>WR</sub> | Write Recovery Time         | 0   | _   | 0        | _         | 0   | —   | ns   |

| tODW            | R/W Low to Output High-Z    | _   | 25  | —        | 30        | _   | 35  |      |

| tOEW            | R/W High to Output Active   | 5   | —   | 5        | —         | 5   | —   |      |

| t <sub>DS</sub> | Data Setup Time             | 30  | _   | 35       | _         | 40  | —   |      |

| t <sub>DH</sub> | Data Hold Time              | 0   | _   | 0        | _         | 0   | _   |      |

# AC TEST CONDITIONS

| PARAMETER                       | TEST CONDITION      |

|---------------------------------|---------------------|

| Output load                     | 100 pF + 1 TTL Gate |

| Input pulse level               | 0.6 V, 2.4 V        |

| Timing measurements             | 1.5 V               |

| Reference level                 | 1.5 V               |

| t <sub>R</sub> , t <sub>F</sub> | 5 ns                |

# <u>AC CHARACTERISTICS AND OPERATING CONDITIONS</u> (Ta = 0° to 70°C, $V_{DD}$ = 2.7 V to 5.5 V)

# READ CYCLE

| SYMBOL           | PARAMETER                           | TC554001AF/AFT/ATR |     |           |     |      |

|------------------|-------------------------------------|--------------------|-----|-----------|-----|------|

|                  |                                     | -70V               |     | -85V/-10V |     | UNIT |

|                  |                                     | MIN                | MAX | MIN       | MAX |      |

| t <sub>RC</sub>  | Read Cycle Time                     | 120                | —   | 150       | _   | ns   |

| tACC             | Address Access Time                 | _                  | 120 | —         | 150 |      |

| t <sub>CO</sub>  | Chip Enable Access Time             | _                  | 120 | _         | 150 |      |

| t <sub>OE</sub>  | Output Enable Access Time           | _                  | 70  | —         | 75  |      |

| tCOE             | Chip Enable Low to Output Active    | 10                 | —   | 10        | —   |      |

| tOEE             | Output Enable Low to Output Active  | 5                  | _   | 5         | _   |      |

| t <sub>OD</sub>  | Chip Enable High to Output High-Z   | _                  | 50  | _         | 50  |      |

| t <sub>ODO</sub> | Output Enable High to Output High-Z | _                  | 50  | _         | 50  |      |

| t <sub>OH</sub>  | Output Data Hold Time               | 10                 |     | 10        | _   |      |

#### WRITE CYCLE

| SYMBOL          | PARAMETER                   | TC554001AF/AFT/ATR |     |           |     |      |

|-----------------|-----------------------------|--------------------|-----|-----------|-----|------|

|                 |                             | -70V               |     | -85V/-10V |     | UNIT |

|                 |                             | MIN                | MAX | MIN       | MAX | ]    |

| t <sub>WC</sub> | Write Cycle Time            | 120                | _   | 150       | _   |      |

| t <sub>WP</sub> | Write Pulse Width           | 80                 | —   | 100       | —   |      |

| t <sub>CW</sub> | Chip Enable to End of Write | 100                | —   | 120       | _   |      |

| t <sub>AS</sub> | Address Setup Time          | 0                  |     | 0         | _   |      |

| t <sub>WR</sub> | Write Recovery Time         | 0                  | —   | 0         | —   | ns   |

| todw            | R/W Low to Output High-Z    | —                  | 50  | _         | 50  |      |

| tOEW            | R/W High to Output Active   | 5                  | _   | 5         | _   |      |

| t <sub>DS</sub> | Data Setup Time             | 50                 | _   | 60        | _   | ]    |

| <sup>t</sup> DH | Data Hold Time              | 0                  | _   | 0         | _   |      |

# **AC TEST CONDITIONS**

| PARAMETER                       | TEST CONDITION                 |  |  |

|---------------------------------|--------------------------------|--|--|

| Output load                     | 100 pF (Include Jig)           |  |  |

| Input pulse level               | V <sub>DD</sub> – 0.2 V, 0.2 V |  |  |

| Timing measurements             | 1.5 V                          |  |  |

| Reference level                 | 1.5 V                          |  |  |

| t <sub>R</sub> , t <sub>F</sub> | 5 ns                           |  |  |

# TIMING DIAGRAMS

READ CYCLE (See Note 1)

# WRITE CYCLE 1 (R/W CONTROLLED) (See Note 4)

WRITE CYCLE 2 (CE CONTROLLED) (See Note 4)

#### Note:

- (1) R/W remains HIGH for the read cycle.

- (2) If  $\overline{CE}$  goes LOW coincident with or after R/W goes LOW, the outputs will remain at high impedance.

- (3) If  $\overline{CE}$  goes HIGH coincident with or before R/W goes HIGH, the outputs will remain at high impedance.

- (4) If  $\overline{OE}$  is HIGH during the write cycle, the outputs will remain at high impedance.

- (5) Because I/O signals may be in the output state at this time, input signals of reverse polarity must not be applied.

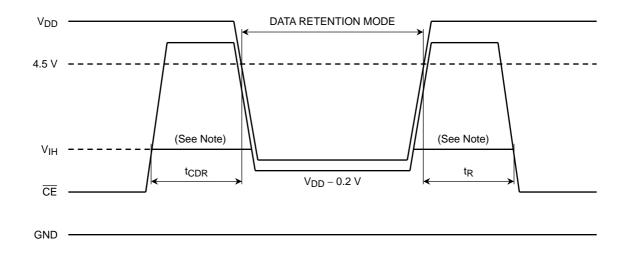

# DATA RETENTION CHARACTERISTICS (Ta = 0° to 70°C)

| SYMBOL           | PARAMETER                                 |                         | MIN | TYP | MAX | UNIT |

|------------------|-------------------------------------------|-------------------------|-----|-----|-----|------|

| V <sub>DH</sub>  | Data Retention Supply Voltage             |                         | 2.0 | _   | 5.5 | V    |

| IDDS2            | Standby Current                           | V <sub>DH</sub> = 3.0 V | _   |     | 25* | μA   |

|                  |                                           | V <sub>DH</sub> = 5.5 V | _   | _   | 50  |      |

| t <sub>CDR</sub> | Chip Deselect to Data Retention Mode Time |                         | 0   | _   | _   | ns   |

| t <sub>R</sub>   | Recovery Time                             |                         | 5   | _   | _   | ms   |

\*:  $5 \mu A$  (max) at Ta = 0° to 40°C

# CE CONTROLLED DATA RETENTION MODE

Note: When  $\overline{CE}$  is operating at the V<sub>IH</sub> level (2.2V), the standby current is given by I<sub>DDS1</sub> during the transition of V<sub>DD</sub> from 4.5 to 2.4V.

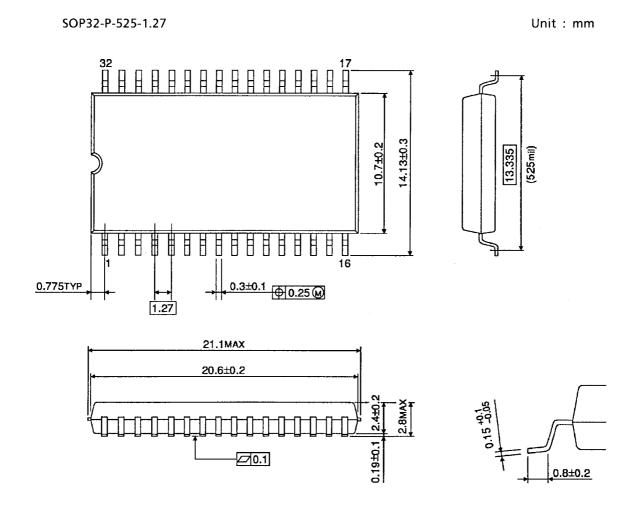

# PACKAGE DIMENSIONS

Weight: 1.14 g (typ)

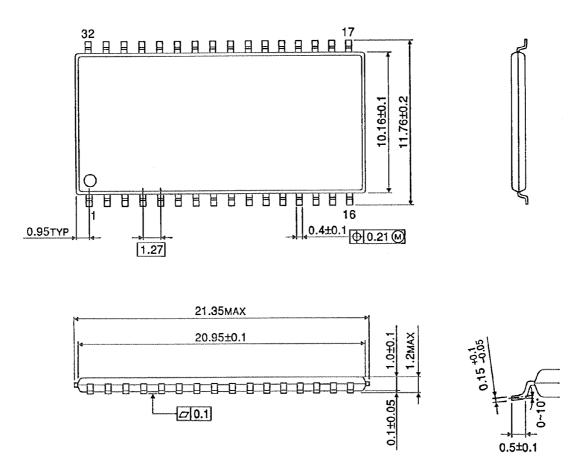

# PACKAGE DIMENSIONS

Unit: mm

Weight: 0.53 g (typ)

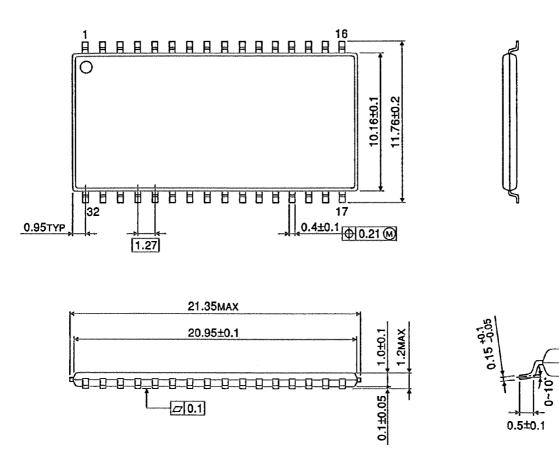

## PACKAGE DIMENSIONS

TSOPII32-P-400-1.27A

Unit: mm

Weight: 0.53 g (typ)

#### **RESTRICTIONS ON PRODUCT USE**

030619EBA

- The information contained herein is subject to change without notice.

- The information contained herein is presented only as a guide for the applications of our products. No

responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which

may result from its use. No license is granted by implication or otherwise under any patent or patent rights of

TOSHIBA or others.

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property.

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc..

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk.

- The products described in this document are subject to the foreign exchange and foreign trade laws.

- TOSHIBA products should not be embedded to the downstream products which are prohibited to be produced and sold, under any law and regulations.