D3449, MARCH 1990-REVISED OCTOBER 1990

- Inputs are TTL-Voltage Compatible

- High-Speed Bus Transceivers With Parity Generator/Checker

- Parity-Error-Flag Open-Drain Output

- Register for Storage of the Parity-Error Flag

- Flow-Through Architecture Optimizes PCB Layout

- Center-Pin V<sub>CC</sub> and GND Configurations Minimize High-Speed Switching Noise

- EPIC™ (Enhanced-Performance Implanted CMOS) 1-µm Process

- 500-mA Typical Latch-Up Immunity at 125°C

- Package Options Include Plastic "Small Outline" Packages, Ceramic Chip Carriers, and Standard Plastic and Ceramic 300-mil DIPs

### description

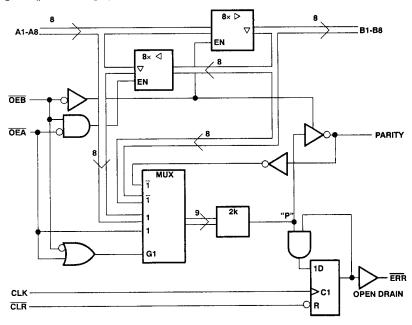

The 'ACT11833 is an 8-bit to 9-bit parity transceiver designed for two-way communication between data buses. When data is transmitted from the A bus to the B bus, a parity bit is generated. When data is transmitted from the B bus to the A bus with its corresponding parity bit, the  $\overline{ERR}$  output will indicate whether or not an error in the B data has occurred. The output enable inputs  $\overline{OEA}$  and  $\overline{OEB}$  can be used to disable the device so that the buses are effectively isolated.

A 9-bit parity generator/checker generates a parity-odd output (PARITY) and monitors the parity of the I/O ports with an open-drain parity

error flag (ERR). ERR is clocked into the register on the rising edge of the CLK input. The error flag register is cleared with a low pulse on the CLR input. When both OEA and OEB are low, data is transferred from the A bus to the B bus and inverted parity is generated. Inverted parity is a forced error condition that gives the designer more system diagnostic capability.

The 54ACT11833 is characterized for operation over the full military temperature range of  $\sim 55$ °C to 125°C. The 74ACT11833 is characterized for operation from -40°C to 85°C.

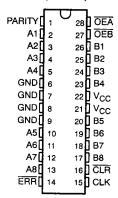

### 54ACT11833 ... JT PACKAGE 74ACT11833 ... DW OR NT PACKAGE (TOP VIEW)

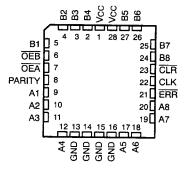

### 54ACT11833 . . . FK PACKAGE (TOP VIEW)

PRODUCT PREVIEW

EPIC is a trademark of Texas Instruments Incorporated.

2-59

# PRODUCT PREVIEW

### **Function Table**

|     | INPUTS |             |                 | S                     |                             |    | OUTF | UT AND I/O |      |                                                 |  |  |

|-----|--------|-------------|-----------------|-----------------------|-----------------------------|----|------|------------|------|-------------------------------------------------|--|--|

| OEB | OEA    | CLR         | CLK             | Ai<br>Σ of H's        | Bi <sup>†</sup><br>Σ of H's | А  | В    | PARITY     | ERR  | FUNCTION                                        |  |  |

| L   | Н      | Х           | Х               | Odd<br>Even           | NA                          | NA | Α    | L<br>H     | NA   | A data to B bus and<br>Generate Parity          |  |  |

| H   | L      | Н           | 1               | NA                    | Odd<br>Even                 | В  | NA   | NA         | H    | B Data to A Bus and<br>Check Parity             |  |  |

| Х   | ×      | L           | Х               | Х                     | Х                           | Х  | NA   | NA         | н    | Clear Error Flag Register                       |  |  |

| н   | н      | H<br>L<br>H | No†<br>No†<br>† | X<br>X<br>Odd<br>Even | ×                           | z  | z    | z          | rıığ | Isolation <sup>‡</sup>                          |  |  |

| L   | L      | х           | X               | Odd<br>Even           | NA                          | NA | Α    | H          | NA   | A Data to B Bus and<br>Generate Inverted Parity |  |  |

### logic diagram (positive logic)

NA = Not applicable, NC = No change, X = Don't care † Summation of high-level inputs includes PARITY along with Bi inputs.

<sup>‡</sup> In this mode, the ERR output, when clocked, shows inverted parity of the A bus.

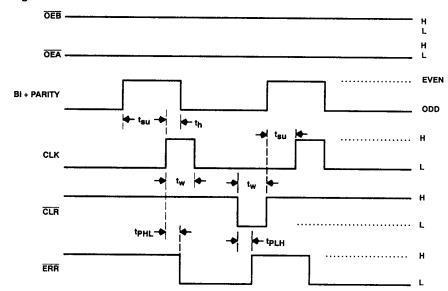

### **Error-Flag Function Table**

| INP | UTS | INTERNAL<br>TO DEVICE | OUTPUT<br>PRE-STATE | ООТРОТ | FUNCTION |

|-----|-----|-----------------------|---------------------|--------|----------|

| CLR | CLK | POINT "P"             | ERR n-1             | ERR    |          |

| H   | Ť   | н                     | Н                   | Н      |          |

| Н   | t   | x                     | Ĺ                   | L      | Sample   |

| Н   | t   | L                     | x                   | L      |          |

| L   | Х   | x                     | x                   | Н      | Clear    |

ERR n-1 represents the state of the ERR output before any changes at CLR, CLK, or point "P".

### error-flag waveforms

### 54ACT11833, 74ACT11833 8-BIT TO 9-BIT PARITY BUS TRANSCEIVERS

D3449, MARCH 1990-REVISED OCTOBER 1990

### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

| Supply voltage range, V <sub>CC</sub>                                                           | – 0.5 V to 7 V                   |

|-------------------------------------------------------------------------------------------------|----------------------------------|

| Input voltage range, V <sub>I</sub> (see Note 1)                                                | 0.5 V to V <sub>CC</sub> + 0.5 V |

| Output voltage range, VO (see Note 1)                                                           | 0.5 V to V <sub>CC</sub> + 0.5 V |

| Input clamp current, IIK (VI < 0 or VI > VCC)                                                   |                                  |

| Output clamp current, I <sub>OK</sub> (V <sub>O</sub> < 0 or V <sub>O</sub> > V <sub>CC</sub> ) | ±50 mA                           |

| Continuous output current, $I_O$ ( $V_O = 0$ to $V_{CC}$ )                                      | ±50 mA                           |

| Continuous current through V <sub>CC</sub> or GND pins                                          | ±225 mA                          |

| Storage temperature range                                                                       |                                  |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: The input and output voltage ratings may be exceeded if the input and output current ratings are observed.

### recommended operating conditions

|       |                                    | 54   | ACT118 | 833 74ACT1183 |      |     | 33   |      |

|-------|------------------------------------|------|--------|---------------|------|-----|------|------|

|       |                                    | MIN  | NOM    | MAX           | MIN  | NOM | MAX  | UNIT |

| Vcc   | Supply voltage                     | 4.5  | 5      | 5.5           | 4.5  | 5   | 5.5  | ٧    |

| VIH   | High-level input voltage           | 2    |        |               | 2    |     |      | ٧    |

| VIL   | Low-level input voltage            |      |        | 0.8           |      |     | 0.8  | V    |

| VI    | Input voltage                      | 0    |        | Vcc           | 0    |     | Vcc  | V    |

| Vo    | Output voltage                     | 0    |        | Vcc           | 0    |     | Vcc  | V    |

| ЮН    | High-level output current          |      |        | - 24          |      |     | - 24 | mA   |

| lOL   | Low-level output current           |      |        | 24            |      |     | 24   | mA   |

| Δt/Δν | Input transition rise or fall rate | 0    |        | 10            | 0    |     | 10   | ns/V |

| TA    | Operating free-air temperature     | - 55 |        | 125           | - 40 |     | 85   | °C   |

## electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

| PARAMETER       |                           | TEST CONSTITUTE                                |       | T    | A = 25°C | ;     | 54ACT | 11833 | 74ACT11833 |      |      |

|-----------------|---------------------------|------------------------------------------------|-------|------|----------|-------|-------|-------|------------|------|------|

|                 | FARAMETER                 | TEST CONDITIONS                                | Vcc   | MIN  | TYP      | MAX   | MIN   | MAX   | MIN        | MAX  | UNIT |

|                 |                           | ІОН ≃ − 50 μА                                  | 4.5 V | 4.4  |          |       | 4.4   |       | 4.4        |      |      |

|                 |                           |                                                | 5.5 V | 5.4  |          |       | 5.4   |       | 5.4        |      |      |

| ∨он             | All outputs except        | i <sub>OH</sub> = - 24 mA                      | 4.5 V | 3.94 |          |       | 3.7   |       | 3.8        |      |      |

| ∨он             | ERR                       |                                                | 5.5 V | 4.94 |          |       | 4.7   |       | 4.8        |      | V    |

|                 |                           | I <sub>OH</sub> = - 50 mA <sup>†</sup>         | 5.5 V |      |          |       | 3.85  |       |            |      |      |

|                 |                           | I <sub>OH</sub> = - 75 mA <sup>†</sup>         | 5.5 V |      |          |       |       |       | 3.85       |      |      |

|                 |                           |                                                | 4.5 V |      |          | 0.1   |       | 0.1   |            | 0.1  |      |

|                 |                           | I <sub>OL</sub> = 50 μA                        | 5.5 V |      |          | 0.1   |       | 0.1   |            | 0.1  |      |

| V               |                           |                                                | 4.5 V |      |          | 0.36  |       | 0.5   |            | 0.44 | V    |

| VOL             |                           | I <sub>OL</sub> = 24 mA                        | 5.5 V |      |          | 0.36  |       | 0.5   |            | 0.44 |      |

|                 |                           | IOL = 50 mA <sup>†</sup>                       | 5.5 V |      |          |       |       | 1.65  |            |      |      |

|                 |                           | I <sub>OL</sub> = 75 mA <sup>†</sup>           | 5.5 V |      |          |       |       |       |            | 1.65 |      |

| l <sub>1</sub>  | OEA, OEB, CLK,<br>and CLR | V <sub>I</sub> = V <sub>CC</sub> or GND        | 5.5 V |      |          | ± 0.1 | 44.   | ± 1   |            | ± 1  | μΑ   |

| loz             | A or B ports,<br>PARITY‡  | V <sub>O</sub> = V <sub>CC</sub> or GND        | 5.5 V |      |          | ± 0.5 |       | ± 10  |            | ± 5  | μА   |

| lcc             |                           | VI = VCC or GND, IO = 0                        | 5.5 V |      |          | 8     |       | 160   |            | 80   | μА   |

| ΔICC§           |                           | One input at 3.4 V, Other inputs at GND or VCC | 5.5 V | •    |          | 0.9   |       | 1     |            | 1    | mA   |

| Ci              | OEA, OEB, CLK,<br>and CLR | VI = VCC or GND                                | 5 V   |      | 4.5      |       |       |       |            |      |      |

| C <sub>iO</sub> | A or B ports,<br>PARITY   | VO = VCC or GND                                | 5 V   |      | 12       |       |       |       |            |      | рF   |

<sup>1</sup> Not more than one output should be tested at a time, and the duration of the test should not exceed 10 ms.

# timing requirements over recommended operating free-air temperature range, $V_{CC}$ = 5 V $_{\pm}$ 0.5 V (unless otherwise noted) (see Note 2)

|                 |                                      |               | T <sub>A</sub> = 25°0 | C 54ACT | 54ACT11833 |     | 74ACT11833 |      |

|-----------------|--------------------------------------|---------------|-----------------------|---------|------------|-----|------------|------|

|                 |                                      |               | MIN M                 | AX MIN  | MAX        | MIN | MAX        | UNIT |

|                 |                                      | CLK high      | 5                     | 5       |            | 5   |            |      |

| tw              | Pulse duration                       | CLK low       | 5                     | 5       |            | 5   |            | ns   |

|                 |                                      | CLR low       | 5                     | 5       |            | 5   |            |      |

| t <sub>su</sub> | 0-1                                  | Bi and PARITY | 14                    | 14      |            | 14  |            |      |

|                 | Setup time before CLK†               | CLR inactive  | 2                     | 2       |            | 2   |            | ns   |

| th              | Hold time after CLK †, Bi and PARITY |               | 0                     | 0       |            | 0   |            | ns   |

NOTE 2: Load circuit and voltage waveforms are shown in Section 1.

### operating characteristics, $V_{CC} = 5 \text{ V}$ , $T_A = 25^{\circ}\text{C}$

|                 | PARAMETER                                     |                    |        | TEST CO                 | TYP       | UNIT |    |

|-----------------|-----------------------------------------------|--------------------|--------|-------------------------|-----------|------|----|

|                 |                                               | Outrote analytical | A to B | 0 50 5                  |           | 87   | _  |

| C <sub>pd</sub> | Power dissipation capacitance per transceiver | Outputs enabled    | B to A | C <sub>L</sub> = 50 pF, | f = 1 MHz | 60   | pF |

|                 |                                               | Outputs disabled   | A to B | C <sub>L</sub> = 50 pF, | f = 1 MHz | 28   | ρF |

|                 |                                               |                    | B to A |                         |           | 8    |    |

$<sup>\</sup>ensuremath{^{\ddagger}}$  For I/O ports, the parameter IOZ includes the input leakage current.

<sup>§</sup> This is the increase in supply current for each input that is at one of the specified TTL voltage levels rather than 0 V to VCC.