# **Z16C30**CMOS USC<sup>™</sup> Universal Serial Controller

#### **FEATURES**

- Two Independent 0-to-10-mbps Full-Duplex Channels, each with Two Baud Rate Generators and One Digital Phase-Locked Loop for Clock Recovery

- 32-Byte Data FIFO's for each Receiver and Transmitter

- 110-ns Bus Cycle Time, 16-Bit Data Bus Bandwidth

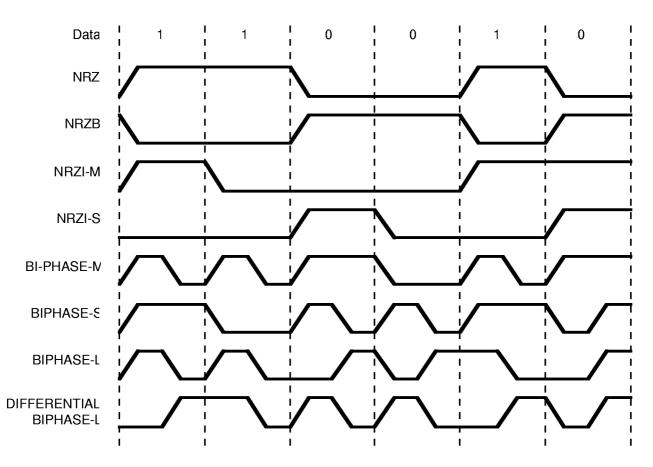

- Multi-Protocol Operation under Program Control with Independent Mode Selection for Receiver and Transmitter

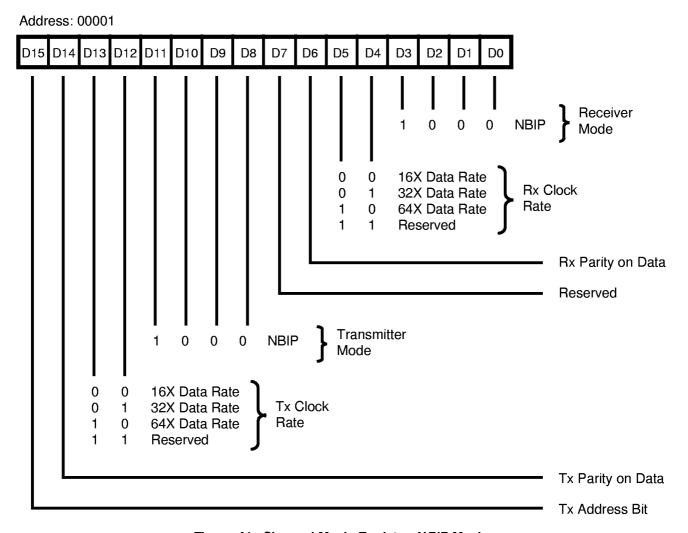

- Async Mode with 1 to 8 Bits/Character, 1/16 to 2 Stop Bits/Character in 1/16-Bit Increments; Programmable Clock Factor; Break Detect and Generation; Odd, Even, Mark, Space or no Parity and Framing Error Detection; Supports One Address/Data Bit and MIL STD 1553B Protocols

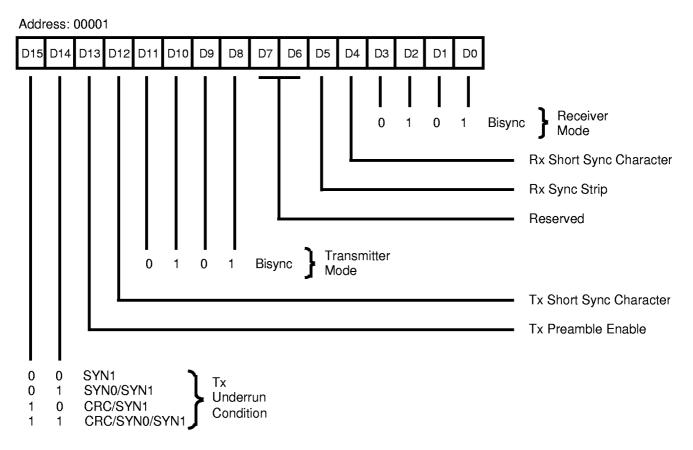

- Byte Oriented Synchronous Mode with One to Eight Bits/Character; Programmable Idle Line Condition; Optional Receive Sync Stripping; Optional Preamble Transmission; 16- or 32-Bit CRC and Transmit-to-Receive Slaving (for X.21)

- Bisync Mode with 2- to 16-Bit Programmable Sync Character; Programmable Idle Line Condition; Optional

- Receive Sync Stripping; Optional Preamble Transmission; 16- or 32-Bit CRC

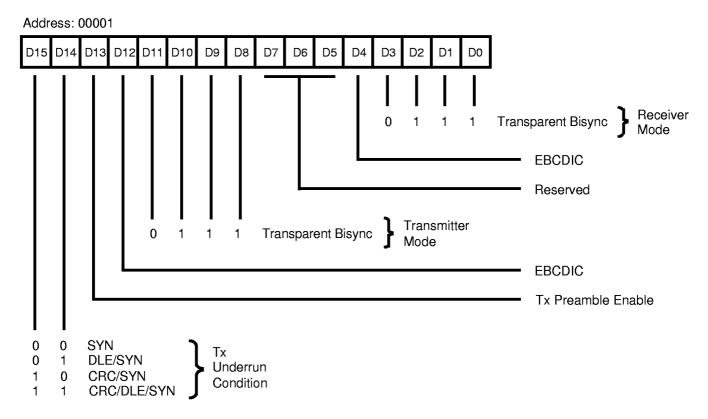

- Transparent Bisync Mode with EBCDIC or ASCII Character Code; Automatic CRC Handling; Programmable Idle Line Condition; Optional Preamble Transmission; Automatic Recognition of DLE, SYN, SOH, ITX, ETX, ETB, EOT, ENQ and ITB

- External Character Sync Mode for Receive

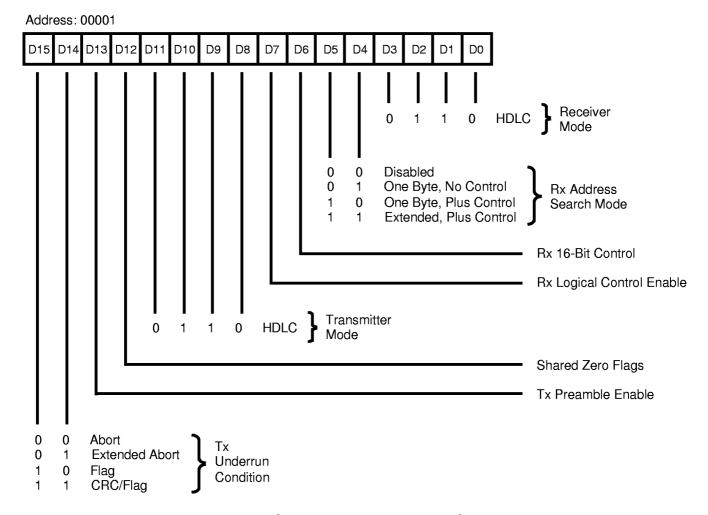

- HDLC/SDLC Mode with Eight-Bit Address Compare; Extended Address Field Option; 16- or 32-Bit CRC; Programmable Idle Line Condition; Optional Preamble Transmission and Loop Mode

- DMA Interface with Separate Request and Acknowledge for Each Receiver and Transmitter

- Channel Load Command for DMA Controlled Initialization

- Flexible Bus Interface for Direct Connection to Most Microprocessors; User Programmable for 8 or 16 Bits Wide. Directly Supports 680X0 Family or 8X86 Family Bus Interfaces

- Low Power CMOS

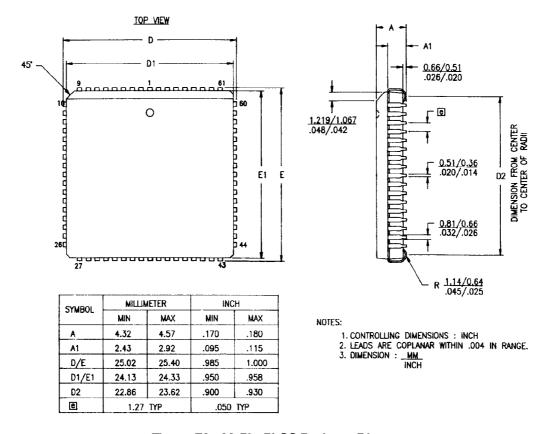

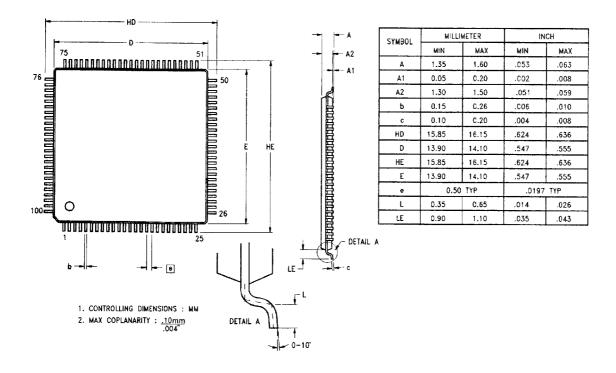

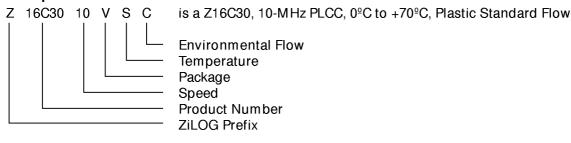

- 68-Pin PLCC/100-Pin VQFP Packages

### **GENERAL DESCRIPTION**

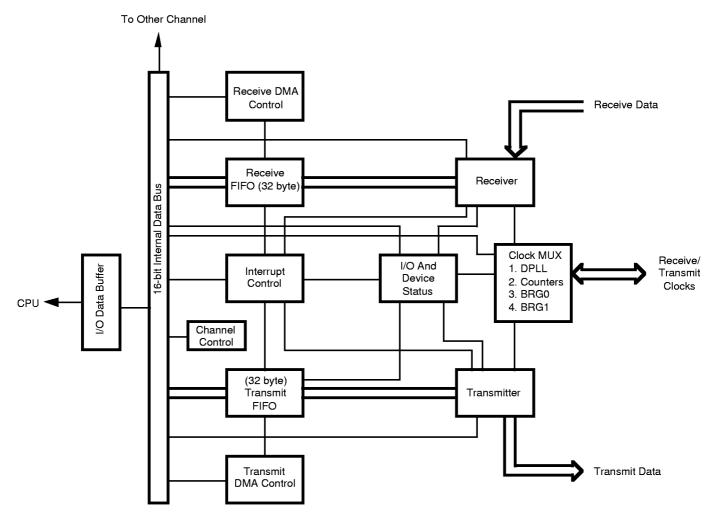

The Z16C30 USC<sup>TM</sup> Universal Serial Controller is a dualchannel multi-protocol data communications peripheral designed for use with any conventional multiplexed or nonmultiplexed bus. The USC functions as a serial-to-parallel, parallel-to-serial converter/controller and may be software configured to satisfy a wide variety of serial communications applications. The device contains a variety of new, sophisticated internal functions including two baud rate generators per channel, one digital phase-locked loop per channel, character counters for both receive and transmit in each channel and 32-byte data FIFO's for each receiver and transmitter (Figure 1).

ZiLOG now offers a high speed version of the USC with improved bus bandwidth. CPU bus accesses have been shortened from 160 ns per access to 110 ns per access. The USC has a transmit and receive clock range of up to 10 MHz

## **GENERAL DESCRIPTION** (Continued)

(20 MHz when using the DPLL, BRG, or CTR) and data transfer rates as high as 10 Mbits/sec full duplex.

The USC handles asynchronous formats, synchronous byte-oriented formats such as BISYNC and synchronous bit-oriented formats such as HDLC. This device supports virtually any serial data transfer application.

The device can generate and check CRC in any synchronous mode and can be programmed to check data integrity in various modes. The USC also has facilities for modem controls in both channels. In applications where these controls are not needed, the modem controls may be used for general-purpose I/O. The same is true for most of the other pins in each channel.

Interrupts are supported with a daisy-chain hierarchy, with the two channels having completely separate interrupt structures.

High-speed data transfers through DMA are supported by a Request/Acknowledge signal pair for each receiver and transmitter. The device supports automatic status transfer through DMA and also allows device initialization under DMA control.

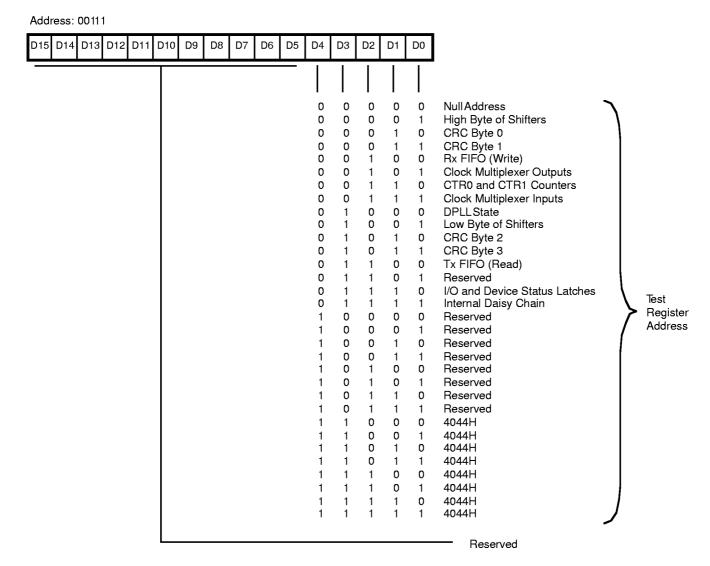

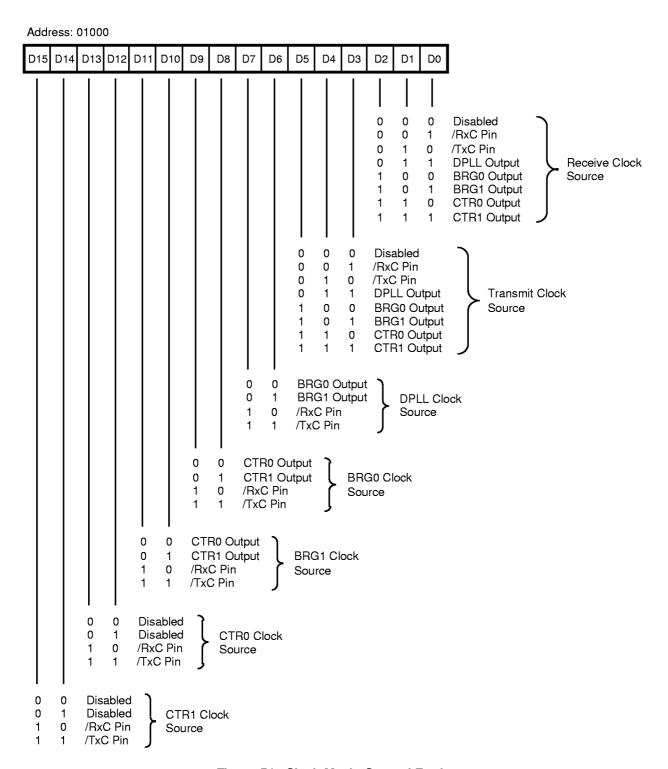

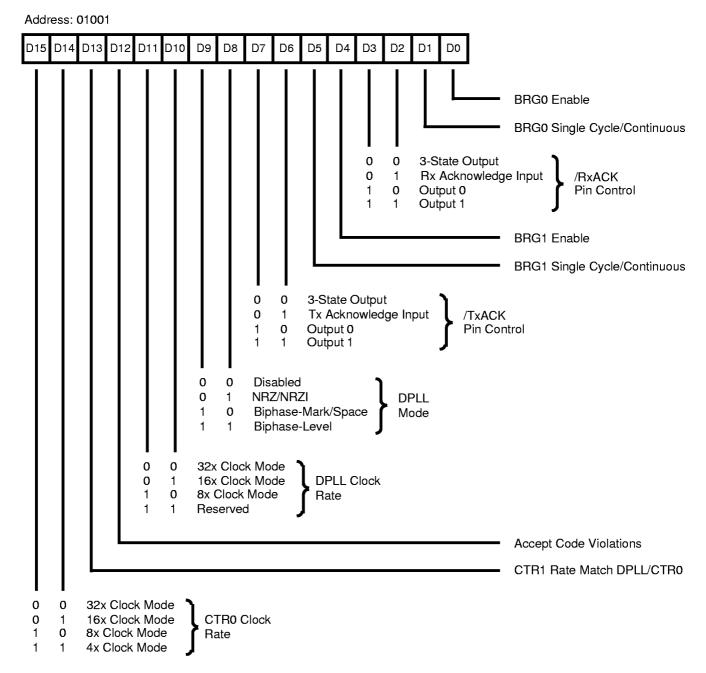

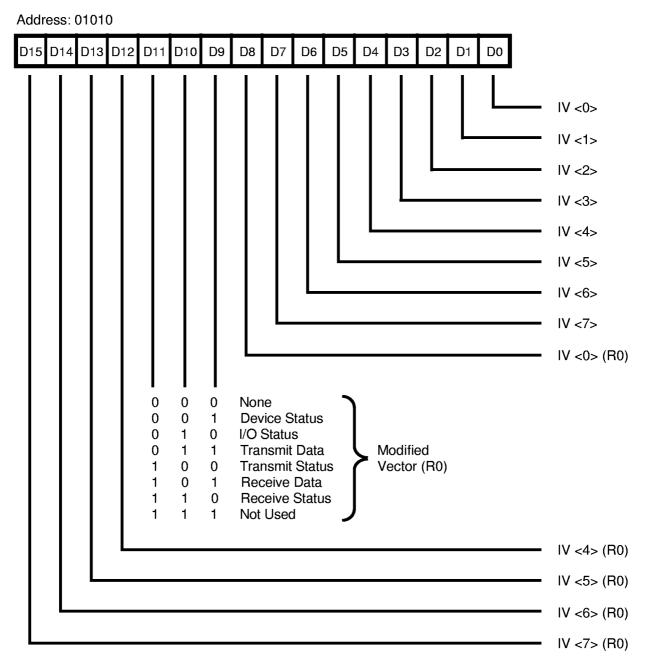

**Note:** When written to, all reserved bits must be programmed to 0.

To aid the designer in efficiently programming the USC, support tools are available. The Technical Manual describes in detail all features presented in this Product Specification and gives programming sequence hints. The Programmer's Assistant is a MS-DOS disk-based programming initialization tool to be used in conjunction with the Technical Manual. There are also available assorted application notes and development boards to assist the designer in the hardware/software development.

All Signals with an  $\overline{\text{overline}}$ , are active Low. For example:  $\overline{\text{B/W}}$ , in which WORD is active Low, and  $\overline{\text{B}}/\text{W}$ , in which BYTE is active Low.

Power connections follow these conventional descriptions:

| Connection | Circuit         | Device          |

|------------|-----------------|-----------------|

| Power      | V <sub>CC</sub> | $V_{DD}$        |

| Ground     | GND             | V <sub>SS</sub> |

Figure 1. Z16C30 Block Diagram

#### **PIN DESCRIPTION**

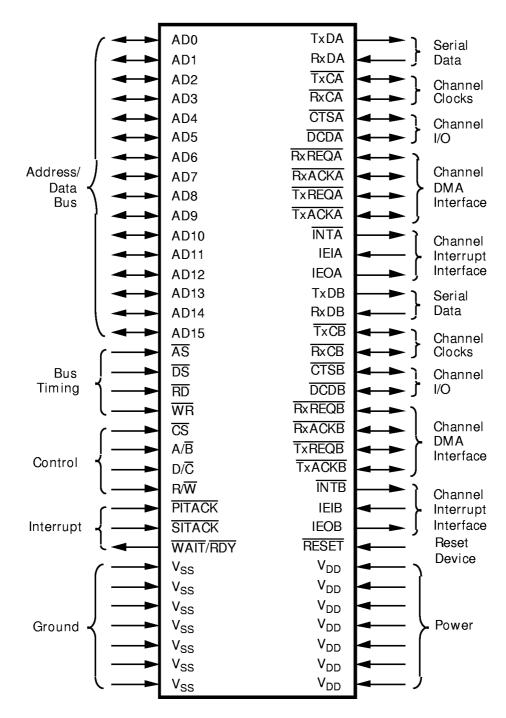

Figure 2. Z16C30 Pin Functions

Figure 3. Z16C30 68-Pin PLCC Pin Assignments

## **GENERAL DESCRIPTION** (Continued)

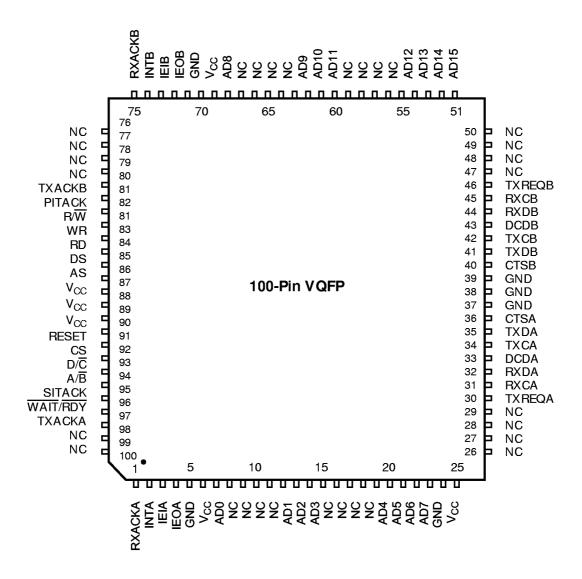

Figure 4. 100-Pin VQFP Pin Assignments

The Z16C30 contains 13 pins per channel for channel I/O, 16 pins for address and data, 12 pins for CPU handshake and 14 pins for power and ground.

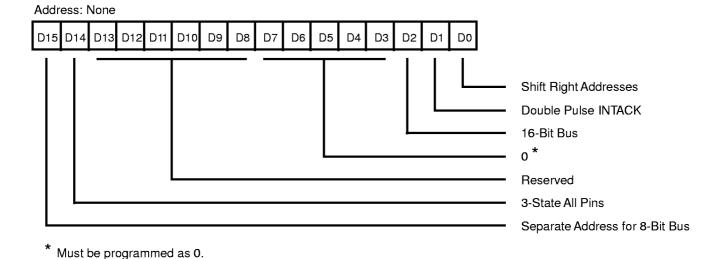

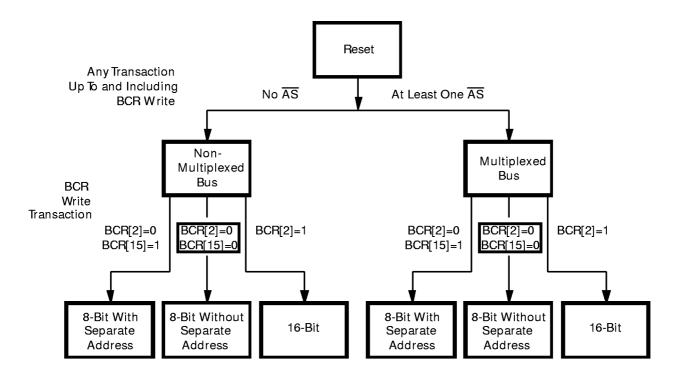

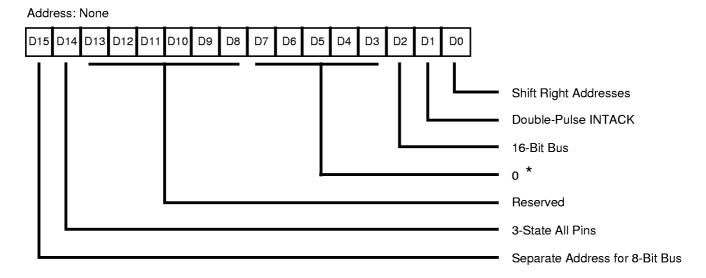

Three separate bus interface types are available for the device. The Bus Configuration Register (BCR) and external connections to the AD bus control selection of the bus type. A 16-bit bus is selected by setting BCR bit 2 to a 1. The 8-bit bus is selected by setting BCR bit 2 to zero and tying AD15–AD8 to  $V_{\rm SS}$ .

The 8-bit bus with separate address is selected by setting BCR bit 2 to zero and, during the BCR write, forcing AD15 to a 1 and forcing AD14—AD8 to zero.

The multiplexed bus is selected for the USC if there is an Address Strobe prior to or during the transaction which writes the BCR. If no Address Strobe is present prior to or during the transaction which writes the BCR, a nonmultiplexed bus is selected (see Figure 28).

## **ABSOLUTE MAXIMUM RATINGS**

| Symbol           | Description            | Min  | Max   | Units |

|------------------|------------------------|------|-------|-------|

| V <sub>CC</sub>  | Supply Voltage (*)     | -0.3 | +7.0  | V     |

| T <sub>STG</sub> | Storage Temp.          | –65° | +150° | С     |

| T <sub>A</sub>   | Oper. Ambient<br>Temp. |      | †     | С     |

|                  | Power Dissipation      |      | 2.2   | W     |

#### Notes:

Stresses greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; operation of the device at any condition above those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

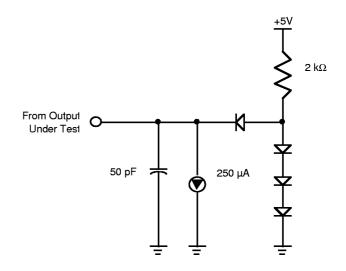

#### STANDARD TEST CONDITIONS

The DC Characteristics and Capacitance section below apply for the following standard test conditions, unless otherwise noted. All voltages are referenced to GND. Positive current flows into the referenced pin (Figure 54). Standard conditions are as follows:

- $+4.5 \text{ V} < \text{V}_{\text{CC}} < +5.5 \text{ V}$

- GND = 0 V

- T<sub>A</sub> as specified in Ordering Information

Figure 5. Test Load Diagram

<sup>\*</sup> Voltage on all pins with respect to GND. †See Ordering Information.

## **CAPACITANCE**

| Symbol                                            | Parameter                 | Min | Max | Unit | Condition           |  |  |  |

|---------------------------------------------------|---------------------------|-----|-----|------|---------------------|--|--|--|

| C <sub>IN</sub>                                   | Input Capacitance         |     | 10  | pF   | Unmeasured pins     |  |  |  |

| C <sub>OUT</sub>                                  | Output Capacitance        |     | 15  | pF   | returned to Ground. |  |  |  |

| CI/O                                              | Bidirectional Capacitance |     | 20  | pF   |                     |  |  |  |

| Note: f = 1 MHz over specified temperature range. |                           |     |     |      |                     |  |  |  |

## **MISCELLANEOUS**

Transistor Count: 174,000

#### **TEMPERATURE RATINGS**

Standard =  $0^{\circ}$ C to  $\pm 70^{\circ}$ C Extended =  $-40^{\circ}$ C to  $+85^{\circ}$ C

## **DC CHARACTERISTICS**

Z16C30

| Symbol           | Parameter                      | Min                  | Тур          | Max                  | Unit     | Condition                                 |

|------------------|--------------------------------|----------------------|--------------|----------------------|----------|-------------------------------------------|

| V <sub>IH</sub>  | Input High Voltage             | 2.2                  |              | V <sub>CC</sub> +0.3 | ٧        |                                           |

| V <sub>IL</sub>  | Input Low Voltage              | -0.3                 |              | 0.8                  | V        |                                           |

| V <sub>OH1</sub> | Output High Voltage            | 2.4                  |              |                      | V        | $I_{OH} = -1.6 \text{ mA}$                |

| V <sub>OH2</sub> | Output High Voltage            | V <sub>CC</sub> -0.8 |              |                      | V        | I <sub>OH</sub> = -250 μA                 |

| V <sub>OL</sub>  | Output Low Voltage             |                      |              | 0.4                  | V        | $I_{OL} = +2.0 \text{ mA}$                |

| I <sub>IL</sub>  | Input Leakage                  |                      |              | ±10.00               | μΑ       | $0.4 < V_{IN} < +2.4V$                    |

| I <sub>OL</sub>  | Output Leakage                 |                      |              | ±10.00               | μΑ       | 0.4 < V <sub>OUT</sub> < +2.4V            |

| I <sub>CCI</sub> | V <sub>CC</sub> Supply Current |                      | 7            | 50                   | m A      | $V_{CC} = 5V V_{IH} = 4.8V V_{IL} = 0.2V$ |

| Moto: V          | = 5\/ ±10% unloss athorwise s  | posified over        | coocified to | omporatura ran       | <b>~</b> |                                           |

Note:  $V_{CC}$ = 5V ±10% unless otherwise specified, over specified temperature range.

## **AC CHARACTERISTICS**

Z16C30

Table 1. AC Characteristics

| 1         Tcyc         Bus Cycle Time         110         ns           2         TwASI         ĀS Low Width         30         ns           3         TwASh         ĀS High Width         60         ns           4         TwDSI         DS Low Width         60         ns           5         TwDSh         DS High Width         50         ns           6         TdAS(DS)         ĀS Rise to DS Fall Delay Time         5         ns           7         TdDS(AS)         DS Rise to ĀS Fall Delay Time         5         ns           8         TdDS(DRa)         DS Fall to Data Active Delay         0         ns           9         TdDS(DRn)         DS Rise to Data Not Valid Delay         0         ns           10         TdDS(DRn)         DS Rise to Data Not Valid Delay         0         ns           11         TdDS(DRn)         DS Rise to Data Float Delay         20         ns           12         TsCS(AS)         CS to ĀS Rise Setup Time         15         ns           12         TsCS(AS)         CS to ĀS Rise Setup Time         15         ns           13         ThCS(AS)         Direct Address to ĀS Rise Hold Time         5         ns         1      <                                                                                                                                                                                         | No | Symbol     | Parameter                                         | Min | Мах | Units | Note |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|------------|---------------------------------------------------|-----|-----|-------|------|

| 3   TwASh   AS High Width   60   ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1  | Тсус       | Bus Cycle Time                                    | 110 |     | ns    |      |

| TwDSI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2  | TwASI      | AS Low Width                                      | 30  |     | ns    |      |

| 5         Tw DSh         DS High Width         50         ns           6         TdAS(DS)         AS Rise to DS Fall Delay Time         5         ns           7         TdDS(AS)         DS Rise to AS Fall Delay Time         5         ns           8         TdDS(DRA)         DS Fall to Data Active Delay         0         ns           9         TdDS(DRA)         DS Rise to Data Active Delay         0         ns           10         TdDS(DRA)         DS Rise to Data Roat Delay         0         ns           11         TdDS(DRA)         DS Rise to Data Roat Delay         20         ns           12         TsCS(AS)         CS to AS Rise Setup Time         15         ns           13         ThCS(AS)         CS to AS Rise Setup Time         15         ns           14         TsADD(AS)         Direct Address to AS Rise Setup Time         15         ns         1           15         ThADD(AS)         Direct Address to AS Rise Hold Time         5         ns         1           16         TsSIA(AS)         SITACK to AS Rise Hold Time         5         ns         1           17         ThAD(AS)         Address to AS Rise Hold Time         5         ns         1           18                                                                                                                                                                 | 3  | TwASh      | AS High Width                                     | 60  |     | ns    |      |

| 6         TdAS(DS)         ĀS Rise to DS Fall Delay Time         5         ns           7         TdDS(AS)         DS Rise to ĀS Fall Delay Time         5         ns           8         TdDS(DRa)         DS Fall to Data Active Delay         0         ns           9         TdDS(DRV)         DS Fall to Data Valid Delay         60         ns           10         TdDS(DRV)         DS Rise to Data Not Valid Delay         0         ns           11         TdDS(DRV)         DS Rise to Data Rise Valid Delay         0         ns           11         TdDS(DRV)         DS Rise to Data Rise Valid Delay         0         ns           11         TdDS(DRV)         DS Rise to Data Rise Setup Time         15         ns           12         TsCS(AS)         CS to ĀS Rise Setup Time         15         ns         1           12         TsCS(AS)         CS to ĀS Rise Setup Time         15         ns         1           13         ThCS(AS)         Direct Address to ĀS Rise Setup Time         15         ns         1           14         TsADD(AS)         Direct Address to ĀS Rise Setup Time         15         ns         1           15         ThADD(AS)         Address to ĀS Rise Setup Time         15                                                                                                                                                | 4  | TwDSI      | DS Low Width                                      | 60  |     | ns    |      |

| 7         TdDS(AS)         DS Rise to AS Fall Delay Time         5         ns           8         TdDS(DRa)         DS Fall to Data Active Delay         0         ns           9         TdDS(DRn)         DS Fall to Data Valid Delay         0         ns           10         TdDS(DRn)         DS Rise to Data Not Valid Delay         0         ns           11         TdDS(DRn)         DS Rise to Data Float Delay         20         ns           12         TsCS(AS)         CS to AS Rise Setup Time         15         ns           12         TsCS(AS)         CS to AS Rise Setup Time         15         ns           13         ThCS(AS)         CS to AS Rise Setup Time         15         ns           14         TsADD(AS)         Direct Address to AS Rise Setup Time         15         ns         1           15         ThADD(AS)         Direct Address to AS Rise Setup Time         15         ns         1           16         TsSIA(AS)         SITACK to AS Rise Setup Time         15         ns         1           16         TsSIA(AS)         Address to AS Rise Setup Time         15         ns         1           17         ThSIA(AS)         Address to AS Rise Setup Time         15         ns                                                                                                                                                 | 5  | TwDSh      | DS High Width                                     | 50  |     | ns    |      |

| 8         TdDS(DRa)         DS Fall to Data Active Delay         0         ns           9         TdDS(DRv)         DS Fall to Data Valid Delay         60         ns           10         TdDS(DRn)         DS Rise to Data Not Valid Delay         0         ns           11         TdDS(DRz)         DS Rise to Data Float Delay         20         ns           11         TdDS(DRz)         DS Rise to Data Roat Delay         20         ns           12         TsCS(AS)         CS to AS Rise Setup Time         15         ns           13         ThCS(AS)         CS to AS Rise Setup Time         15         ns           14         TsADD(AS)         Direct Address to AS Rise Setup Time         15         ns         1           15         ThADD(AS)         Direct Address to AS Rise Setup Time         15         ns         1           16         TsSIA(AS)         SITACK to AS Rise Setup Time         15         ns         1           16         TsSIA(AS)         SITACK to AS Rise Setup Time         15         ns         1           17         ThSIA(AS)         Address to AS Rise Setup Time         15         ns         ns           19         ThAD(AS)         Address to AS Rise Setup Time         15                                                                                                                                            | 6  | TdAS(DS)   | AS Rise to DS Fall Delay Time                     | 5   |     | ns    |      |

| 9         TdDS(DRV)         DS Fall to Data Valid Delay         60         ns           10         TdDS(DRn)         DS Rise to Data Not Valid Delay         0         ns           11         TdDS(DRz)         DS Rise to Data Float Delay         20         ns           12         TSCS(AS)         CS to AS Rise Setup Time         15         ns           13         ThCS(AS)         CS to AS Rise Setup Time         5         ns           14         TsADD(AS)         Direct Address to AS Rise Setup Time         15         ns         1           15         ThADD(AS)         Direct Address to AS Rise Setup Time         15         ns         1           16         TSSIA(AS)         SITACK to AS Rise Setup Time         15         ns         1           16         TSSIA(AS)         SITACK to AS Rise Setup Time         15         ns         1           17         ThSIA(AS)         SITACK to AS Rise Setup Time         15         ns         1           18         TsAD(AS)         Address to AS Rise Setup Time         15         ns         1           19         ThAD(AS)         Address to AS Rise Setup Time         5         ns         1           19         ThAD(AS)         Address to AS Ri                                                                                                                                                | 7  | TdDS(AS)   | DS Rise to AS Fall Delay Time                     | 5   |     | ns    |      |

| 10         TdDS(DRn)         DS Rise to Data Not Valid Delay         0         ns           11         TdDS(DRz)         DS Rise to Data Float Delay         20         ns           12         TscS(AS)         CS to AS Rise Setup Time         15         ns           13         ThCS(AS)         CS to AS Rise Hold Time         5         ns           14         TsADD(AS)         Direct Address to AS Rise Setup Time         15         ns         1           15         ThADD(AS)         Direct Address to AS Rise Setup Time         15         ns         1           16         TsSIA(AS)         SITACK to AS Rise Setup Time         15         ns         1           16         TsSIA(AS)         SITACK to AS Rise Setup Time         15         ns         1           17         ThSIA(AS)         Address to AS Rise Setup Time         15         ns         1           18         TsAD(AS)         Address to AS Rise Hold Time         5         ns         1           19         ThAD(AS)         Address to AS Rise Hold Time         5         ns         1           20         TsRW(DS)         RW to DS Fall Setup Time         0         ns         1           21         ThRW(DS)         RW t                                                                                                                                                         | 8  | TdDS(DRa)  | DS Fall to Data Active Delay                      | 0   |     | ns    |      |

| 11         TdDS(DRz)         DS Rise to Data Float Delay         20         ns           12         TsCS(AS)         CS to AS Rise Setup Time         15         ns           13         ThCS(AS)         CS to AS Rise Setup Time         5         ns           14         TsADD(AS)         Direct Address to AS Rise Setup Time         15         ns         1           15         ThADD(AS)         Direct Address to AS Rise Setup Time         5         ns         1           16         TsSIA(AS)         Direct Address to AS Rise Setup Time         15         ns         1           16         TsSIA(AS)         SITACK to AS Rise Setup Time         5         ns         1           17         ThSIA(AS)         Address to AS Rise Setup Time         5         ns         1           18         TsAD(AS)         Address to AS Rise Bold Time         5         ns         1           19         ThAD(AS)         Address to AS Rise Bold Time         0         ns         1           19         ThAD(AS)         Address to AS Rise Bold Time         0         ns         1           20         TsRW(DS)         RW to DS Fall Bold Time         0         ns         4           21         ThRW(DS) </td <td>9</td> <td>TdDS(DRv)</td> <td>DS Fall to Data Valid Delay</td> <td></td> <td>60</td> <td>ns</td> <td></td>                                       | 9  | TdDS(DRv)  | DS Fall to Data Valid Delay                       |     | 60  | ns    |      |

| 12         TsCS(AS)         CS to AS Rise Setup Time         15         ns           13         ThCS(AS)         CS to AS Rise Hold Time         5         ns           14         TsADD(AS)         Direct Address to AS Rise Setup Time         15         ns         1           15         ThADD(AS)         Direct Address to AS Rise Hold Time         5         ns         1           16         TsSIA(AS)         SITACK to AS Rise Hold Time         5         ns         1           16         TsSIA(AS)         SITACK to AS Rise Hold Time         5         ns         1           17         ThSIA(AS)         SITACK to AS Rise Hold Time         5         ns         1           18         TsAD(AS)         Address to AS Rise Hold Time         5         ns         1           19         ThAD(AS)         Address to AS Rise Hold Time         5         ns         1           19         ThAD(AS)         Address to AS Rise Hold Time         5         ns         1           20         TsRW(DS)         RW to DS Fall Betup Time         0         ns         4           21         ThRW(DS)         RW to DS Fall Hold Time         25         ns         4           23         TdDSr(RRQ                                                                                                                                                                   | 10 | TdDS(DRn)  | DS Rise to Data Not Valid Delay                   | 0   |     | ns    |      |

| 13         ThCS(AS)         CS to AS Rise Hold Time         5         ns           14         TsADD(AS)         Direct Address to AS Rise Setup Time         15         ns         1           15         ThADD(AS)         Direct Address to AS Rise Setup Time         5         ns         1           16         TsSIA(AS)         SITACK to AS Rise Setup Time         15         ns         1           17         ThSIA(AS)         SITACK to AS Rise Setup Time         5         ns         1           18         TsAD(AS)         Address to AS Rise Setup Time         15         ns         1           19         ThAD(AS)         Address to AS Rise Setup Time         5         ns         1           20         TsRW(DS)         RW to DS Fall Setup Time         0         ns         2           20         TsRW(DS)         RW to DS Fall Hold Time         25         ns         2           21         ThRW(DS)         PW to DS Fall Hold Time         25         ns         4           23         TdDSr(RRQ)         DS Rise to RREQ Active Delay         0         ns         4           23         TdDSr(RRQ)         DS Rise to TxREQ Inactive Delay         0         ns         5,6                                                                                                                                                                         | 11 | TdDS(DRz)  | DS Rise to Data Float Delay                       |     | 20  | ns    |      |

| 14         TsADD(AS)         Direct Address to AS Rise Setup Time         15         ns         1           15         ThADD(AS)         Direct Address to AS Rise Hold Time         5         ns         1           16         TsSIA(AS)         SITACK to AS Rise Setup Time         15         ns           17         ThSIA(AS)         SITACK to AS Rise Hold Time         5         ns           18         TsAD(AS)         Address to AS Rise Hold Time         5         ns           19         ThAD(AS)         Address to AS Rise Hold Time         5         ns           20         TsRW(DS)         Address to AS Rise Hold Time         5         ns           20         TsRW(DS)         RW to DS Fall Setup Time         0         ns           21         ThRW(DS)         RW to DS Fall to RXREQ Inactive Delay         60         ns         4           22         TsDSf(RRQ)         DS Rise to RXREQ Active Delay         0         ns         2           24         TsDW(DS)         Write Data to DS Rise Hold Time         0         ns         2           25         ThDW(DS)         Write Data to DS Rise Hold Time         0         ns         2           26         TdDSf(TRQ)         DS Fall to TXREQ Inactive                                                                                                                                       | 12 | TsCS(AS)   | CS to AS Rise Setup Time                          | 15  |     | ns    |      |

| 15         ThADD(AS)         Direct Address to AS Rise Hold Time         5         ns         1           16         TsSIA(AS)         SITACK to AS Rise Setup Time         15         ns           17         ThSIA(AS)         SITACK to AS Rise Setup Time         5         ns           18         TsAD(AS)         Address to AS Rise Setup Time         15         ns           19         ThAD(AS)         Address to AS Rise Hold Time         5         ns           20         TsRW(DS)         RW to DS Fall Setup Time         0         ns           20         TsRW(DS)         RW to DS Fall Setup Time         0         ns           21         ThRW(DS)         RW to DS Fall Hold Time         25         ns           22         TsDSf(RRQ)         DS Rise to RXREQ Inactive Delay         0         ns           24         TsDW(DS)         Write Data to DS Rise Setup Time         30         ns           25         ThDW(DS)         Write Data to DS Rise Hold Time         0         ns           25         ThDW(DS)         Write Data to TxREQ Inactive Delay         65         ns         5,6           25         ThDW(DS)         Write Data to TxREQ Inactive Delay         0         ns         5 <tr< td=""><td>13</td><td>ThCS(AS)</td><td>CS to AS Rise Hold Time</td><td>5</td><td></td><td>ns</td><td></td></tr<>                                | 13 | ThCS(AS)   | CS to AS Rise Hold Time                           | 5   |     | ns    |      |

| 16         TsSIA(AS)         SITACK to AS Rise Setup Time         15         ns           17         ThSIA(AS)         SITACK to AS Rise Hold Time         5         ns           18         TsAD(AS)         Address to AS Rise Hold Time         15         ns           19         ThAD(AS)         Address to AS Rise Hold Time         5         ns           20         TsRW(DS)         R/W to DS Fall Setup Time         0         ns           21         ThRW(DS)         R/W to DS Fall Hold Time         25         ns           22         TsDSf(RRQ)         DS Fall to RXREQ Inactive Delay         60         ns         4           23         TdDSr(RRQ)         DS Rise to RXREQ Active Delay         0         ns         4           24         TsDW(DS)         Write Data to DS Rise Setup Time         30         ns         30         ns           25         ThDW(DS)         Write Data to TxREQ Active Delay         65         ns         5,6           25         TdDSr(TRQ)         DS Rise to TxREQ Active Delay         0         ns         5,6           27         TdDSr(TRQ)         DS Rise to TxREQ Active Delay         0         ns         5,6           28         TwRDh         RD High Width <td>14</td> <td>TsADD(AS)</td> <td>Direct Address to <math>\overline{AS}</math> Rise Setup Time</td> <td>15</td> <td></td> <td>ns</td> <td>1</td> | 14 | TsADD(AS)  | Direct Address to $\overline{AS}$ Rise Setup Time | 15  |     | ns    | 1    |

| 17         ThSIA(AS)         SITACK to AS Rise Hold Time         5         ns           18         TsAD(AS)         Address to AS Rise Setup Time         15         ns           19         ThAD(AS)         Address to AS Rise Hold Time         5         ns           20         TsRW(DS)         R/W to DS Fall Setup Time         0         ns           21         ThRW(DS)         R/W to DS Fall Hold Time         25         ns           22         TsDSf(RRQ)         DS Fall to RXREQ Inactive Delay         60         ns         4           23         TdDSr(RRQ)         DS Rise to RXREQ Active Delay         0         ns         4           23         TdDSr(RRQ)         DS Rise to TXREQ Active Delay         0         ns         4           24         TsDW(DS)         Write Data to DS Rise Hold Time         0         ns         0         ns           25         ThDW(DS)         Write Data to DS Rise Betup Time         0         ns         0         ns           25         ThDW(DS)         Write Data to DS Rise Delay         0         ns         5,6           27         TdDSr(TRQ)         DS Rise to TXREQ Inactive Delay         0         ns         5,6           28         TwRDh </td <td>15</td> <td>ThADD(AS)</td> <td>Direct Address to <math>\overline{AS}</math> Rise Hold Time</td> <td>5</td> <td></td> <td>ns</td> <td>1</td>     | 15 | ThADD(AS)  | Direct Address to $\overline{AS}$ Rise Hold Time  | 5   |     | ns    | 1    |

| 18         TsAD(AS)         Address to AS Rise Setup Time         15         ns           19         ThAD(AS)         Address to AS Rise Hold Time         5         ns           20         TsRW(DS)         RW to DS Fall Setup Time         0         ns           21         ThRW(DS)         RW to DS Fall Hold Time         25         ns           22         TsDSf(RRQ)         DS Fall to RXREQ Inactive Delay         60         ns         4           23         TdDSr(RRQ)         DS Rise to RXREQ Active Delay         0         ns         4           23         TdDSr(RRQ)         DS Rise to RXREQ Active Delay         0         ns         0           24         TsDW(DS)         Write Data to DS Rise Setup Time         30         ns         0           25         ThDW(DS)         Write Data to DS Rise Hold Time         0         ns         0         ns           26         TdDSf(TRQ)         DS Fall to TxREQ Inactive Delay         65         ns         5,6           27         TdDSr(TRQ)         DS Rise to TxREQ Active Delay         0         ns         1           28         TwRDI         RD High Width         50         ns         1           29         TwRDh                                                                                                                                                                          | 16 | TsSIA(AS)  | SITACK to AS Rise Setup Time                      | 15  |     | ns    |      |

| 19         ThAD(AS)         Address to AS Rise Hold Time         5         ns           20         TsRW(DS)         R/W to DS Fall Setup Time         0         ns           21         ThRW(DS)         R/W to DS Fall Hold Time         25         ns           22         TsDSf(RRQ)         DS Fall to RxREQ Inactive Delay         60         ns         4           23         TdDSr(RRQ)         DS Rise to RxREQ Active Delay         0         ns         4           24         TsDW(DS)         Write Data to DS Rise Setup Time         30         ns         5           25         ThDW(DS)         Write Data to DS Rise Hold Time         0         ns         1           25         ThDW(DS)         Write Data to DS Rise Hold Time         0         ns         5           25         ThDW(DS)         Write Data to DS Rise Hold Time         0         ns         5           26         TdDSf(TRQ)         DS Fall to TxREQ Inactive Delay         0         ns         5           26         TdDSf(TRQ)         DS Rise to TxREQ Inactive Delay         0         ns         5           27         TdRD(TRQ)         RD Rise to RD Fall Delay Time         5         ns         1           28         Tw                                                                                                                                                         | 17 | ThSIA(AS)  | SITACK to AS Rise Hold Time                       | 5   |     | ns    |      |

| 20         TsRW(DS)         RW to DS Fall Setup Time         0         ns           21         ThRW(DS)         RW to DS Fall Hold Time         25         ns           22         TsDSf(RRQ)         DS Fall to RxREQ Inactive Delay         60         ns         4           23         TdDSr(RRQ)         DS Rise to RxREQ Active Delay         0         ns         4           24         TsDW(DS)         Write Data to DS Rise Setup Time         30         ns         5           25         ThDW(DS)         Write Data to DS Rise Hold Time         0         ns         65         ns         5,6           25         TdDSf(TRQ)         DS Fall to TxREQ Inactive Delay         65         ns         5,6         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         8         7         8         7         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8         8<                                                                                                                                                                                                  | 18 | TsAD(AS)   | Address to AS Rise Setup Time                     | 15  |     | ns    |      |

| 21         ThRW(DS)         RW to DS Fall Hold Time         25         ns           22         TsDSf(RRQ)         DS Fall to RxREQ Inactive Delay         60         ns         4           23         TdDSr(RRQ)         DS Rise to RxREQ Active Delay         0         ns         4           24         TsDW(DS)         Write Data to DS Rise Setup Time         30         ns         5           25         ThDW(DS)         Write Data to DS Rise Hold Time         0         ns         65         ns         5,6           26         TdDSf(TRQ)         DS Fall to TxREQ Inactive Delay         65         ns         5,6           27         TdDSr(TRQ)         DS Rise to TxREQ Active Delay         0         ns         5,6           27         TdDSr(TRQ)         DS Rise to TxREQ Active Delay         0         ns         5,6           27         TdDSr(TRQ)         DS Rise to TxREQ Active Delay         0         ns         5,6           28         TwRDI         RD High Width         50         ns         30         ns         30         ns         30         ns         30         ns         30         ns         30         ns         31         ns         31         ns         32                                                                                                                                                                  | 19 | ThAD(AS)   | Address to $\overline{AS}$ Rise Hold Time         | 5   |     | ns    |      |

| 22         TsDSf(RRQ)         DS Fall to RxREQ Inactive Delay         60         ns         4           23         TdDSr(RRQ)         DS Rise to RxREQ Active Delay         0         ns           24         TsDW(DS)         Write Data to DS Rise Setup Time         30         ns           25         ThDW(DS)         Write Data to DS Rise Hold Time         0         ns           26         TdDSf(TRQ)         DS Fall to TxREQ Inactive Delay         65         ns         5,6           27         TdDSr(TRQ)         DS Rise to TxREQ Active Delay         0         ns         5           28         TwRDI         RD Low Width         60         ns         60         ns           29         TwRDh         RD High Width         50         ns         5         ns           30         TdAS(RD)         AS Rise to RD Fall Delay Time         5         ns         1         ns           31         TdRD(AS)         RD Rise to AS Fall Delay Time         5         ns         1         ns           32         TdRD(DRa)         RD Fall to Data Active Delay         0         ns         1           33         TdRD(DRn)         RD Fall to Data Valid Delay         0         ns                                                                                                                                                                               | 20 | TsRW(DS)   | R/W to DS Fall Setup Time                         | 0   |     | ns    |      |

| 23         TdDSr(RRQ)         DS Rise to RxREQ Active Delay         0         ns           24         TsDW(DS)         Write Data to DS Rise Setup Time         30         ns           25         ThDW(DS)         Write Data to DS Rise Hold Time         0         ns           26         TdDSf(TRQ)         DS Fall to TxREQ Inactive Delay         65         ns         5,6           27         TdDSr(TRQ)         DS Rise to TxREQ Active Delay         0         ns         1           28         TwRDI         RD Low Width         60         ns         1         1           29         TwRDh         RD High Width         50         ns         30         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         <                                                                                                                                                                                                                | 21 | ThRW(DS)   | R/W to DS Fall Hold Time                          | 25  |     | ns    |      |

| 24         TsDW(DS)         Write Data to DS Rise Setup Time         30         ns           25         ThDW(DS)         Write Data to DS Rise Hold Time         0         ns           26         TdDSf(TRQ)         DS Fall to TxREQ Inactive Delay         65         ns         5,6           27         TdDSr(TRQ)         DS Rise to TxREQ Active Delay         0         ns           28         TwRDI         RD Low Width         60         ns           29         TwRDh         RD High Width         50         ns           30         TdAS(RD)         AS Rise to RD Fall Delay Time         5         ns           31         TdRD(AS)         RD Rise to AS Fall Delay Time         5         ns           32         TdRD(DRa)         RD Fall to Data Active Delay         0         ns           33         TdRD(DRa)         RD Fall to Data Valid Delay         60         ns           34         TdRD(DRn)         RD Rise to Data Not Valid Delay         0         ns           35         TdRD(DRz)         RD Rise to Data Float Delay         20         ns           36         TdRDf(RRQ)         RD Fall to RxREQ Inactive Delay         0         ns           37         TdRDr(RRQ)         RD Rise                                                                                                                                                        | 22 | TsDSf(RRQ) | DS Fall to RxREQ Inactive Delay                   |     | 60  | ns    | 4    |

| 25         ThDW(DS)         Write Data to DS Rise Hold Time         0         ns           26         TdDSf(TRQ)         DS Fall to TxREQ Inactive Delay         65         ns         5,6           27         TdDSr(TRQ)         DS Rise to TxREQ Active Delay         0         ns           28         TwRDI         RD Low Width         60         ns           29         TwRDh         RD High Width         50         ns           30         TdAS(RD)         AS Rise to RD Fall Delay Time         5         ns           31         TdRD(AS)         RD Rise to AS Fall Delay Time         5         ns           32         TdRD(DRa)         RD Fall to Data Active Delay         0         ns           33         TdRD(DRa)         RD Fall to Data Valid Delay         60         ns           34         TdRD(DRn)         RD Rise to Data Not Valid Delay         0         ns           35         TdRD(DRz)         RD Rise to Data Float Delay         20         ns           36         TdRD(RRQ)         RD Fall to RxREQ Inactive Delay         60         ns           37         TdRD(RRQ)         RD Rise to RxREQ Active Delay         0         ns                                                                                                                                                                                                           | 23 | TdDSr(RRQ) | DS Rise to RxREQ Active Delay                     | 0   |     | ns    |      |

| 26         TdDSf(TRQ)         DS Fall to TxREQ Inactive Delay         65         ns         5,6           27         TdDSr(TRQ)         DS Rise to TxREQ Active Delay         0         ns           28         TwRDI         RD Low Width         60         ns           29         TwRDh         RD High Width         50         ns           30         TdAS(RD)         AS Rise to RD Fall Delay Time         5         ns           31         TdRD(AS)         RD Rise to AS Fall Delay Time         5         ns           32         TdRD(DRa)         RD Fall to Data Active Delay         0         ns           33         TdRD(DRa)         RD Fall to Data Valid Delay         60         ns           34         TdRD(DRn)         RD Rise to Data Root Valid Delay         0         ns           35         TdRD(DRz)         RD Rise to Data Float Delay         20         ns           36         TdRDf(RRQ)         RD Fall to RxREQ Inactive Delay         0         ns           37         TdRDr(RRQ)         RD Rise to RxREQ Active Delay         0         ns                                                                                                                                                                                                                                                                                                    | 24 | TsDW(DS)   | Write Data to DS Rise Setup Time                  | 30  |     | ns    |      |

| 27         TdDSr(TRQ)         DS Rise to TxREQ Active Delay         0         ns           28         TwRDI         RD Low Width         60         ns           29         TwRDh         RD High Width         50         ns           30         TdAS(RD)         AS Rise to RD Fall Delay Time         5         ns           31         TdRD(AS)         RD Rise to AS Fall Delay Time         5         ns           32         TdRD(DRa)         RD Fall to Data Active Delay         0         ns           33         TdRD(DRa)         RD Fall to Data Valid Delay         60         ns           34         TdRD(DRn)         RD Rise to Data Not Valid Delay         0         ns           35         TdRD(DRz)         RD Rise to Data Float Delay         20         ns           36         TdRD(RRQ)         RD Fall to RxREQ Inactive Delay         60         ns         4           37         TdRDr(RRQ)         RD Rise to RxREQ Active Delay         0         ns                                                                                                                                                                                                                                                                                                                                                                                                     | 25 | ThDW(DS)   | Write Data to DS Rise Hold Time                   | 0   |     | ns    |      |

| 28         Tw RDI         RD Low Width         60         ns           29         Tw RDh         RD High Width         50         ns           30         TdAS(RD)         AS Rise to RD Fall Delay Time         5         ns           31         TdRD(AS)         RD Rise to AS Fall Delay Time         5         ns           32         TdRD(DRa)         RD Fall to Data Active Delay         0         ns           33         TdRD(DRv)         RD Fall to Data Valid Delay         60         ns           34         TdRD(DRn)         RD Rise to Data Not Valid Delay         0         ns           35         TdRD(DRz)         RD Rise to Data Float Delay         20         ns           36         TdRDf(RRQ)         RD Fall to RxREQ Inactive Delay         60         ns         4           37         TdRDr(RRQ)         RD Rise to RxREQ Active Delay         0         ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 26 | TdDSf(TRQ) | DS Fall to TxREQ Inactive Delay                   |     | 65  | ns    | 5,6  |

| 29TwRDhRDHigh Width50ns30TdAS(RD)ASRise to RDFall Delay Time5ns31TdRD(AS)RDRise to ASFall Delay Time5ns32TdRD(DRa)RDFall to Data Active Delay0ns33TdRD(DRv)RDFall to Data Valid Delay60ns34TdRD(DRn)RDRise to Data Not Valid Delay0ns35TdRD(DRz)RDRise to Data Float Delay20ns36TdRDf(RRQ)RDFall to RxREQ Inactive Delay60ns437TdRDr(RRQ)RDRise to RxREQ Active Delay0ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 27 | TdDSr(TRQ) | DS Rise to TxREQ Active Delay                     | 0   |     | ns    |      |

| 30TdAS(RD)AS Rise to RD Fall Delay Time5ns31TdRD(AS)RD Rise to AS Fall Delay Time5ns32TdRD(DRa)RD Fall to Data Active Delay0ns33TdRD(DRv)RD Fall to Data Valid Delay60ns34TdRD(DRn)RD Rise to Data Not Valid Delay0ns35TdRD(DRz)RD Rise to Data Float Delay20ns36TdRDf(RRQ)RD Fall to RxREQ Inactive Delay60ns437TdRDr(RRQ)RD Rise to RxREQ Active Delay0ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 28 | TwRDI      | RD Low Width                                      | 60  |     | ns    |      |

| 31TdRD(AS)RD Rise to AS Fall Delay Time5ns32TdRD(DRa)RD Fall to Data Active Delay0ns33TdRD(DRv)RD Fall to Data Valid Delay60ns34TdRD(DRn)RD Rise to Data Not Valid Delay0ns35TdRD(DRz)RD Rise to Data Float Delay20ns36TdRDf(RRQ)RD Fall to RxREQ Inactive Delay60ns437TdRDr(RRQ)RD Rise to RxREQ Active Delay0ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 29 | TwRDh      | RD High Width                                     | 50  |     | ns    |      |

| 32     TdRD(DRa)     RD Fall to Data Active Delay     0     ns       33     TdRD(DRv)     RD Fall to Data Valid Delay     60     ns       34     TdRD(DRn)     RD Rise to Data Not Valid Delay     0     ns       35     TdRD(DRz)     RD Rise to Data Float Delay     20     ns       36     TdRDf(RRQ)     RD Fall to RxREQ Inactive Delay     60     ns     4       37     TdRDr(RRQ)     RD Rise to RxREQ Active Delay     0     ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 30 | TdAS(RD)   | AS Rise to RD Fall Delay Time                     | 5   |     | ns    |      |

| 33TdRD(DRv)RD Fall to Data Valid Delay60ns34TdRD(DRn)RD Rise to Data Not Valid Delay0ns35TdRD(DRz)RD Rise to Data Float Delay20ns36TdRDf(RRQ)RD Fall to RxREQ Inactive Delay60ns437TdRDr(RRQ)RD Rise to RxREQ Active Delay0ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 31 | TdRD(AS)   | RD Rise to AS Fall Delay Time                     | 5   |     | ns    |      |

| 34     TdRD(DRn)     RD Rise to Data Not Valid Delay     0     ns       35     TdRD(DRz)     RD Rise to Data Float Delay     20     ns       36     TdRDf(RRQ)     RD Fall to RxREQ Inactive Delay     60     ns     4       37     TdRDr(RRQ)     RD Rise to RxREQ Active Delay     0     ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 32 | TdRD(DRa)  | RD Fall to Data Active Delay                      | 0   |     | ns    |      |

| 35TdRD(DRz)RD Rise to Data Float Delay20ns36TdRDf(RRQ)RD Fall to RxREQ Inactive Delay60ns437TdRDr(RRQ)RD Rise to RxREQ Active Delay0ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 33 | TdRD(DRv)  | RD Fall to Data Valid Delay                       |     | 60  | ns    |      |

| 36 TdRDf(RRQ) RD Fall to RxREQ Inactive Delay 60 ns 4  37 TdRDr(RRQ) RD Rise to RxREQ Active Delay 0 ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 34 | TdRD(DRn)  | RD Rise to Data Not Valid Delay                   | 0   |     | ns    |      |

| 37 TdRDr(RRQ) RD Rise to RxREQ Active Delay 0 ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 35 | TdRD(DRz)  | RD Rise to Data Float Delay                       |     | 20  | ns    |      |

| <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 36 | TdRDf(RRQ) | RD Fall to RxREQ Inactive Delay                   |     | 60  | ns    | 4    |

| 38 TwWRI WR Low Width 60 ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 37 | TdRDr(RRQ) | RD Rise to RxREQ Active Delay                     | 0   |     | ns    |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 38 | TwWRI      | WR Low Width                                      | 60  |     | ns    |      |

## AC CHARACTERISTICS (Continued)

Table 1. AC Characteristics (Continued)

| No | Symbol      | Parameter                            | Min | Max | Units | Note |

|----|-------------|--------------------------------------|-----|-----|-------|------|

| 39 | TwWRh       | WR High Width                        | 50  |     | ns    |      |

| 40 | TdAS(WR)    | AS Rise to WR Fall Delay Time        | 5   |     | ns    |      |

| 41 | TdWR(AS)    | WR Rise to AS Fall Delay Time        | 5   |     | ns    |      |

| 42 | TsDW(WR)    | Write Data to WR Rise Setup Time     | 30  |     | ns    |      |

| 43 | ThDW(WR)    | Write Data to WR Rise Hold Time      | 0   |     | ns    |      |

| 44 | TdWRf(TRQ)  | WR Fall to TxREQ Inactive Delay      |     | 65  | ns    | 5    |

| 45 | TdWRr(TRQ)  | WR Rise to TxREQ Active Delay        | 0   |     | ns    |      |

| 46 | TsCS(DS)    | CS to DS Fall Setup Time             | 0   |     | ns    | 2    |

| 47 | ThCS(DS)    | CS to DS Fall Hold Time              | 25  |     | ns    | 2    |

| 48 | TsADD(DS)   | Direct Address to DS Fall Setup Time | 5   |     | ns    | 1,2  |

| 49 | ThADD(DS)   | Direct Address to DS Fall Hold Time  | 25  |     | ns    | 1,2  |

| 50 | TsSIA(DS)   | SITACK to DS Fall Setup Time         | 5   |     | ns    | 2    |

| 51 | ThSIA(DS)   | SITACK to DS Fall Hold Time          | 25  |     | ns    | 2    |

| 52 | TsCS(RD)    | CS to RD Fall Setup Time             | 0   |     | ns    | 2    |

| 53 | ThCS(RD)    | CS to RD Fall Hold Time              | 25  |     | ns    | 2    |

| 54 | TsADD(RD)   | Direct Address to RD Fall Setup Time | 5   |     | ns    | 1,2  |

| 55 | ThADD(RD)   | Direct Address to RD Fall Hold Time  | 25  |     | ns    | 1,2  |

| 56 | TsSIA(RD)   | SITACK to RD Fall Setup Time         | 5   |     | ns    | 2    |

| 57 | ThSIA(RD)   | SITACK to RD Fall Hold Time          | 25  |     | ns    | 2    |

| 58 | TsCS(WR)    | CS to WR Fall Setup Time             | 0   |     | ns    | 2    |

| 59 | ThCS(WR)    | CS to WR Fall Hold Time              | 25  |     | ns    | 2    |

| 60 | TsADD(WR)   | Direct Address to WR Fall Setup Time | 5   |     | ns    | 1,2  |

| 61 | ThADD(WR)   | Direct Address to WR Fall Hold Time  | 25  |     | ns    | 1,2  |

| 62 | TsSIA(WR)   | SITACK to WR Fall Setup Time         | 5   |     | ns    | 2    |

| 63 | ThSIA(WR)   | SITACK to WR Fall Hold Time          | 25  |     | ns    | 2    |

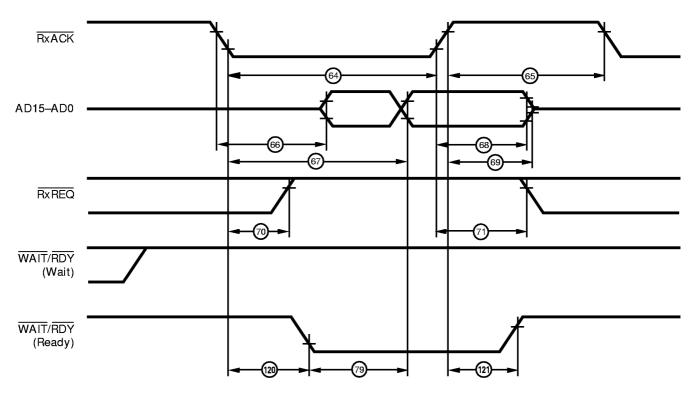

| 64 | TwRAKI      | RxACK Low Width                      | 60  |     | ns    |      |

| 65 | TwRAKh      | RxACK High Width                     | 50  |     | ns    |      |

| 66 | TdRAK(DRa)  | RxACK Fall to Data Active Delay      | 0   |     | ns    |      |

| 67 | TdRAK(DRv)  | RxACK Fall to Data Valid Delay       |     | 60  | ns    |      |

| 68 | TdRAK(DRn)  | RxACK Rise to Data Not Valid Delay   | 0   |     | ns    |      |

| 69 | TdRAK(DRz)  | RxACK Rise to Data Float Delay       |     | 20  | ns    |      |

| 70 | TdRAKf(RRQ) | RxACK Fall to RxREQ Inactive Delay   |     | 60  | ns    | 4    |

| 71 | TdRAKr(RRQ) | RxACK Rise to RxREQ Active Delay     | 0   |     | ns    |      |

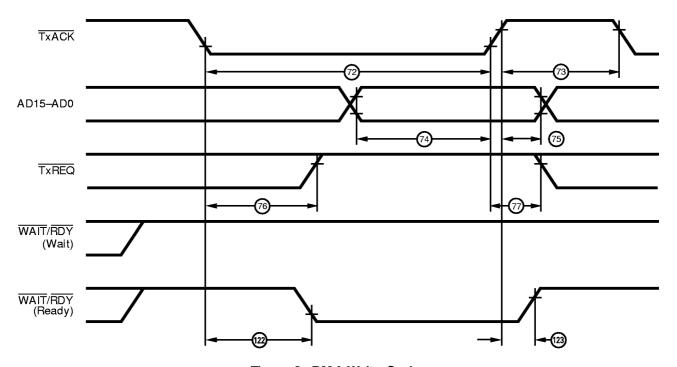

| 72 | TwTAKI      | TxACK Low Width                      | 60  |     | ns    |      |

| 73 | TwTAKh      | TxACK High Width                     | 50  |     | ns    |      |

| 74 | TsDW(TAK)   | Write Data to TxACK Rise Setup Time  | 30  |     | ns    |      |

| 75 | ThDW(TAK)   | Write Data to TxACK Rise Hold Time   | 0   |     | ns    |      |

| 76 | TdTAKf(TRQ) | TxACK Fall to TxREQ Inactive Delay   |     | 65  | ns    | 5    |

| 77 | TdTAKr(TRQ) | TxACK Rise to TxREQ Active Delay     | 0   |     | ns    |      |

| 78 | TdDSf(RDY)  | DS Fall (INTACK) to RDY Fall Delay   |     | 200 | ns    |      |

Table 1. AC Characteristics (Continued)

| No  | Symbol      | Parameter                              | Min | Max | Units | Note |

|-----|-------------|----------------------------------------|-----|-----|-------|------|

| 79  | TdRDY(DRv)  | RDY Fall to Data Valid Delay           |     | 40  | ns    |      |

| 80  | TdDSr(RDY)  | DS Rise to RDY Rise Delay              |     | 40  | ns    |      |

| 81  | TsIEI(DSI)  | IEI to DS Fall (INTACK) Setup Time     | 10  |     | ns    |      |

| 82  | ThIEI(DSI)  | IEI to DS Rise (INTACK) Hold Time      | 0   |     | ns    |      |

| 83  | TdIEI(IEO)  | IEI to IEO Delay                       |     | 30  | ns    |      |

| 84  | TdAS(IEO)   | AS Rise (Intack) to IEO Delay          |     | 60  | ns    |      |

| 85  | TdDSI(INT)  | DS Fall (INTACK) to INT Inactive Delay |     | 200 | ns    | 7    |

| 87  | TdDSI(Wr)   | DS Fall (INTACK) to WAIT Rise Delay    |     | 200 | ns    |      |

| 88  | TdW(DRv)    | WAIT Rise to Data Valid Delay          |     | 40  | ns    |      |

| 89  | TdRDf(RDY)  | RD Fall (INTACK) to RDY Fall Delay     |     | 200 | ns    |      |

| 90  | TdRDr(RDY)  | RD Rise to RDY Rise Delay              |     | 40  | ns    |      |

| 91  | TsIEI(RDI)  | IEI to RD Fall (INTACK) Setup Time     | 10  |     | ns    |      |

| 92  | ThIEI(RDI)  | IEI to RD Rise (INTACK) Hold Time      | 0   |     | ns    |      |

| 93  | TdRDI(INT)  | RD Fall (INTACK) to INT Inactive Delay |     | 200 | ns    |      |

| 94  | TdRDI(Wf)   | RD Fall (INTACK) to WAIT Fall Delay    |     | 40  | ns    |      |

| 95  | TdRDI(Wr)   | RD Fall (INTACK) to WAIT Rise Delay    |     | 200 | ns    |      |

| 96  | TwPIAI      | PITACK Low Width                       | 60  |     | ns    |      |

| 97  | TwPlAh      | PITACK High Width                      | 50  |     | ns    |      |

| 98  | TdAS(PIA)   | AS Rise to PITACK Fall Delay Time      | 5   |     | ns    |      |

| 99  | TdPIA(AS)   | PITACK Rise to AS Fall Delay Time      | 5   |     | ns    |      |

| 100 | TdPIA(DRa)  | PITACK Fall to Data Active Delay       | 0   |     | ns    |      |

| 101 | TdPIA(DRn)  | PITACK Rise to Data Not Valid Delay    | 0   |     | ns    |      |

| 102 | TdPIA(DRz)  | PITACK Rise to Data Float Delay        |     | 20  | ns    |      |

| 103 | TsIEI(PIA)  | IEI to PITACK Fall Setup Time          | 10  |     | ns    |      |

| 104 | ThIEI(PIA)  | IEI to PITACK Rise Hold Time           | 0   |     | ns    |      |

| 105 | TdPIA(IEO)  | PITACK Fall to IEO Delay               |     | 60  | ns    |      |

| 106 | TdPIA(INT)  | PITACK Fall to INT Inactive Delay      |     | 200 | ns    |      |

| 107 | TdPIAf(RDY) | PITACK Fall to RDY Fall Delay          |     | 200 | ns    |      |

| 108 | TdPlAr(RDY) | PITACK Rise to RDY Rise Delay          |     | 40  | ns    |      |

| 109 | TdPIA(Wf)   | PITACK Fall to WAIT Fall Delay         |     | 40  | ns    |      |

| 110 | TdPIA(Wr)   | PITACK Fall to WAIT Rise Delay         |     | 200 | ns    |      |

| 111 | TdSIA(INT)  | SITACK Fall to IEO Inactive Delay      |     | 200 | ns    | 2    |

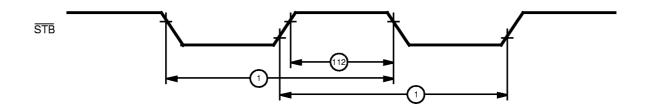

| 112 | TwSTBh      | Strobe High Width                      | 50  |     | ns    | 3    |

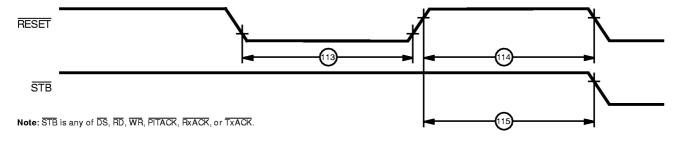

| 113 | TwRESI      | RESET Low Width                        | 170 |     | ns    |      |

| 114 | TwRESh      | RESET High Width                       | 60  |     | ns    |      |

| 115 | Tdres(STB)  | RESET Rise to STB Fall                 | 60  |     | ns    | 3    |

| 116 | TdDSf(RDY)  | DS Fall to RDY Fall Delay              |     | 50  | ns    |      |

| 117 | TdWRf(RDY)  | WR Fall to RDY Fall Delay              |     | 50  | ns    |      |

| 118 | TdWRr(RDY)  | WR Rise to RDY Rise Delay              |     | 40  | ns    |      |

| 119 | TdRDf(RDY)  | RD Fall to RDY Fall Delay              |     | 50  | ns    |      |

| 120 | TdRAKf(RDY) | RxACK Fall to RDY Fall Delay           |     | 50  | ns    |      |

## **AC CHARACTERISTICS** (Continued)

Table 1. AC Characteristics (Continued)

| No  | Symbol      | Parameter                    | Min | Max | Units | Note |

|-----|-------------|------------------------------|-----|-----|-------|------|

| 121 | TdRAKr(RDY) | RXACK Rise to RDY Rise Delay |     | 40  | ns    |      |

| 122 | TdTAKf(RDY) | TxACK Fall to RDY Fall Delay |     | 50  | ns    |      |

| 123 | TdTAKr(RDY) | TxACK Rise to RDY Rise Delay |     | 40  | ns    |      |

#### Notes:

- 1. Direct address is any of  $A/\overline{B}$ ,  $D/\overline{C}$  or AD15–AD8 used as an address bus.

- 2. The parameter applies only when  $\overline{AS}$  is not present.

- 3. Strobe (STB) is any of DS, RD, WR, PITACK, RXACK or TXACK.

- 4. Parameter applies only if read empties the receive FIFO.

- 5. Parameter applies only if write fills the transmit FIFO.

- 6. For extended temperature part TdDSI(Wf) max = 220 ns.

- 7. For extended temperature part TdDSF(TRQ) max = 75 ns.

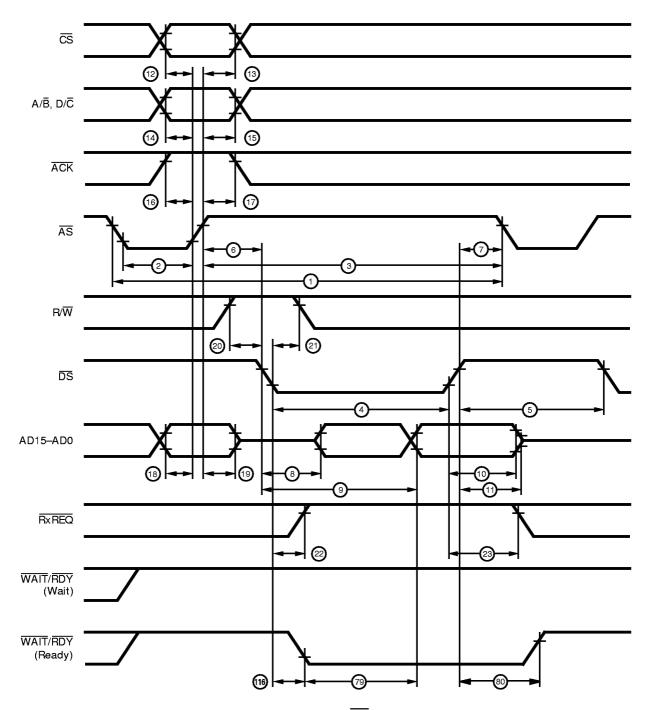

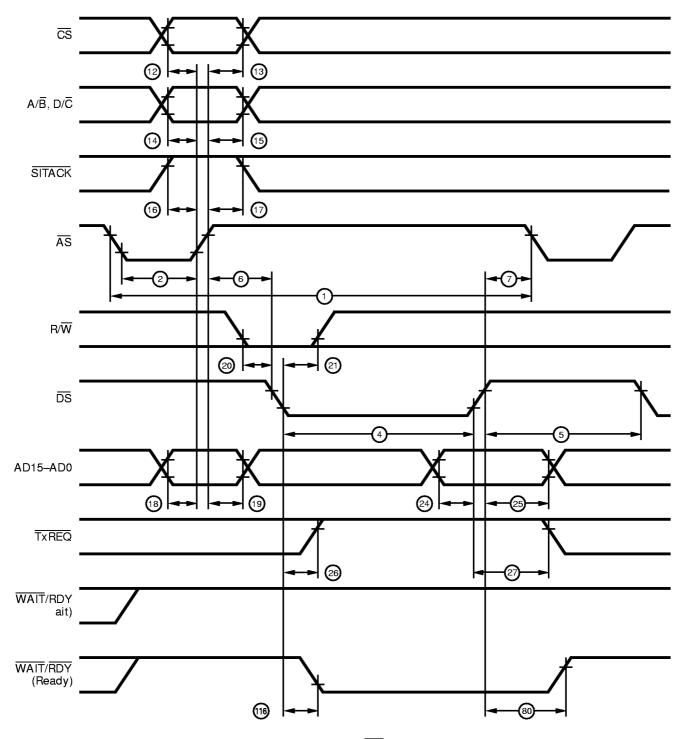

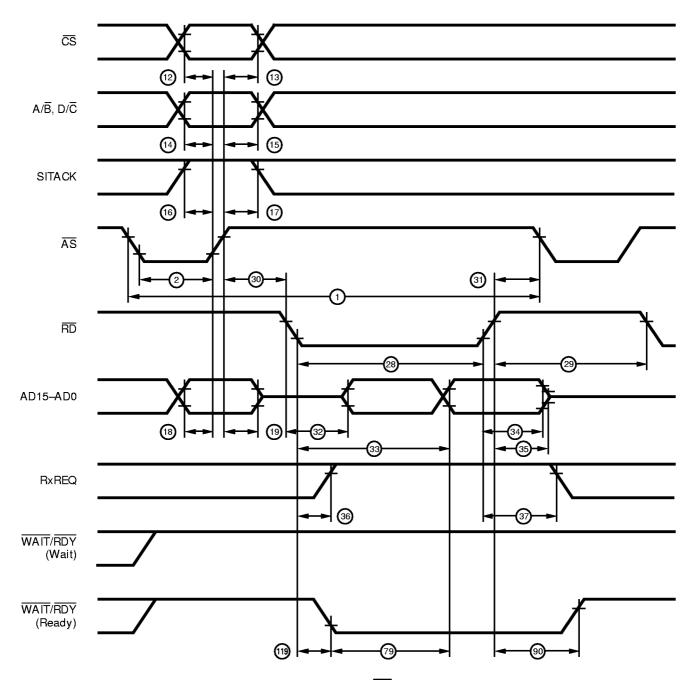

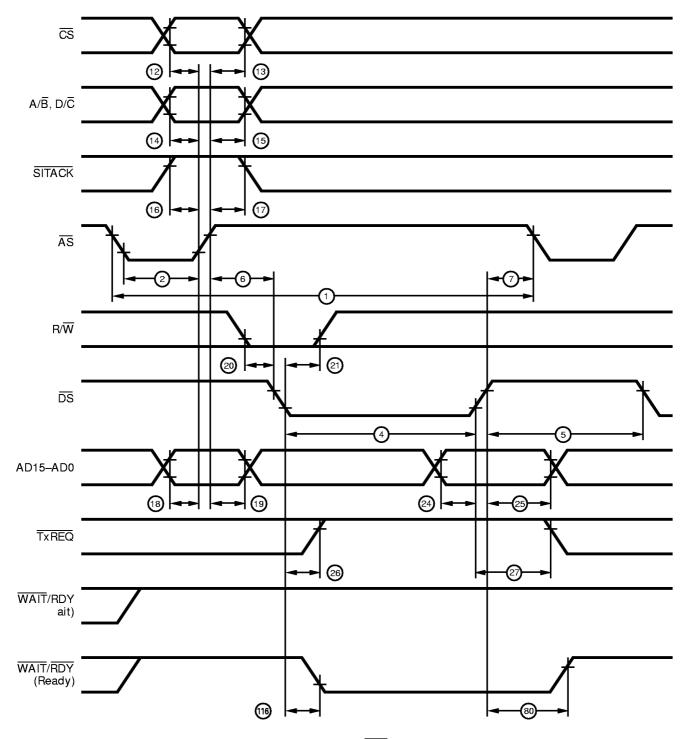

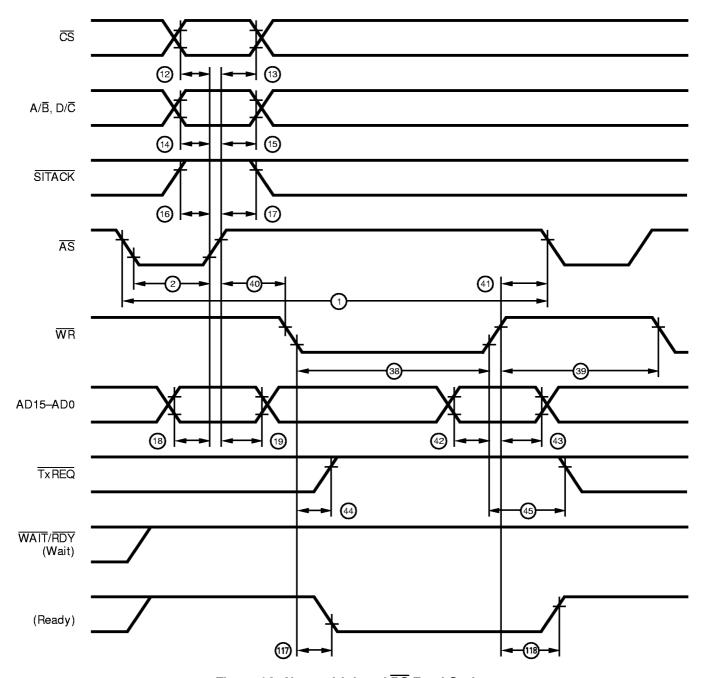

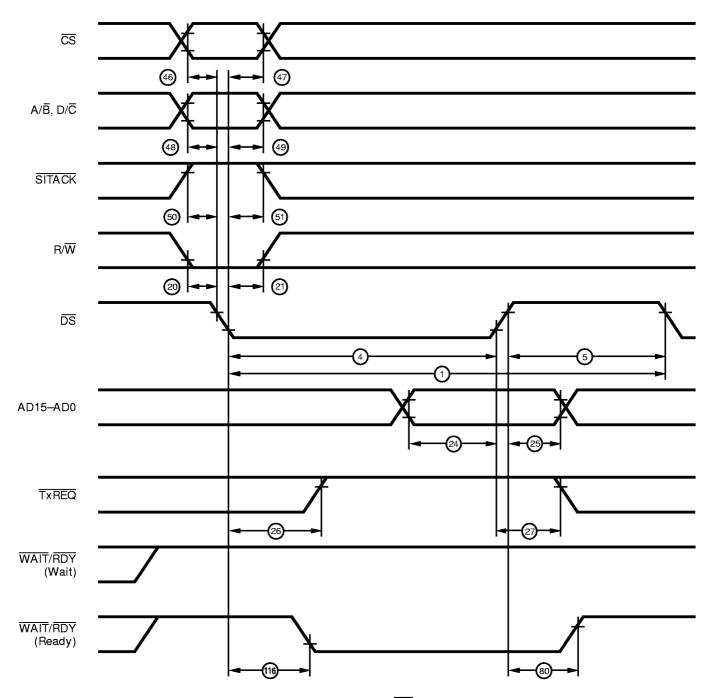

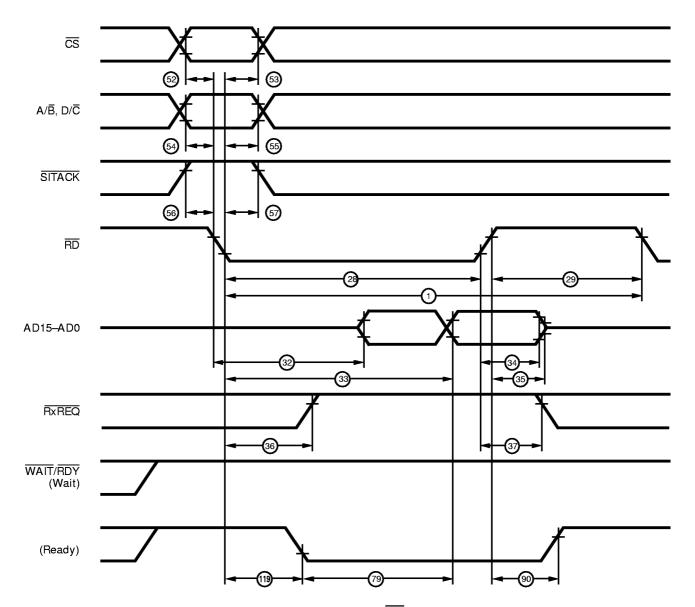

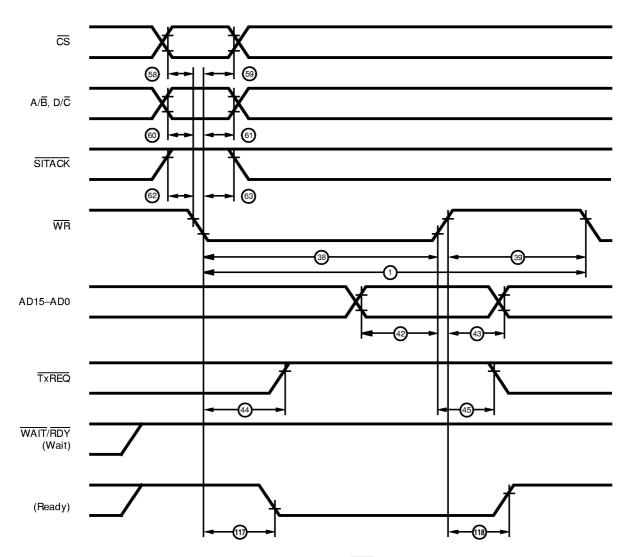

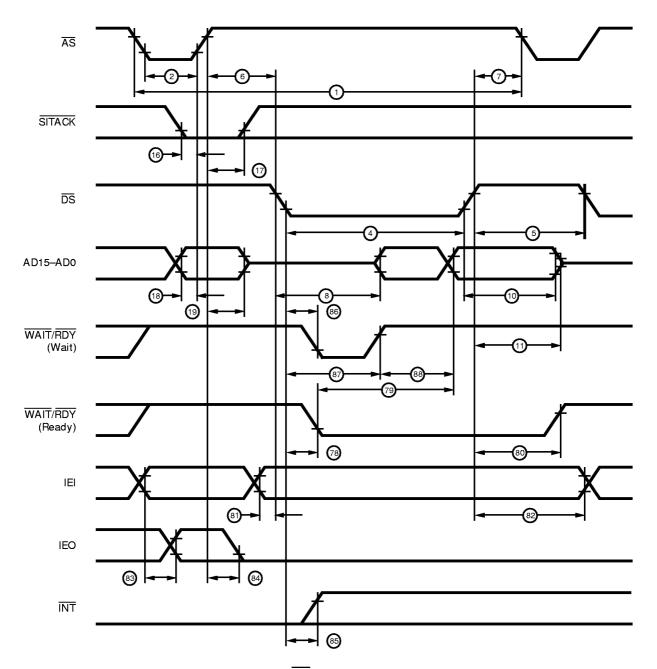

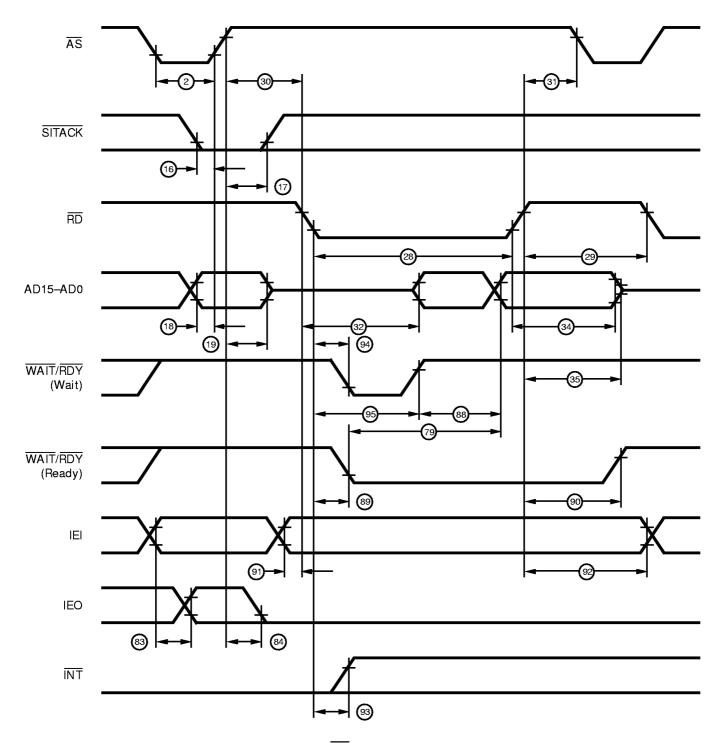

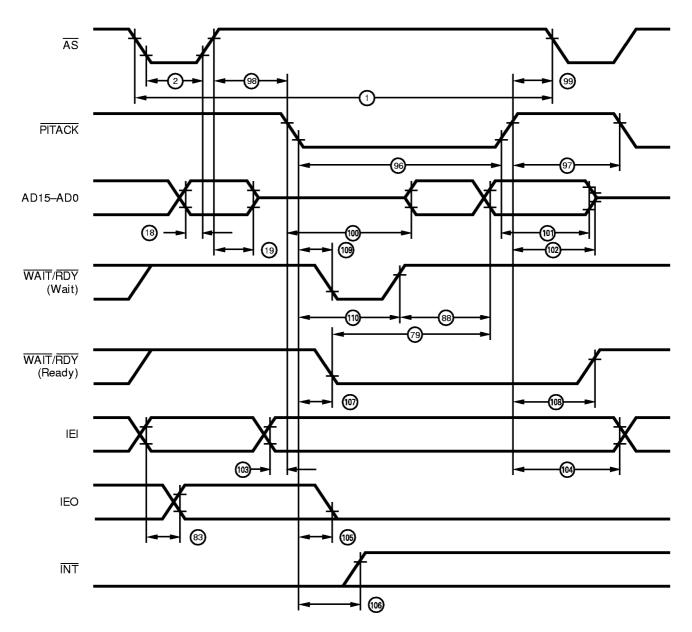

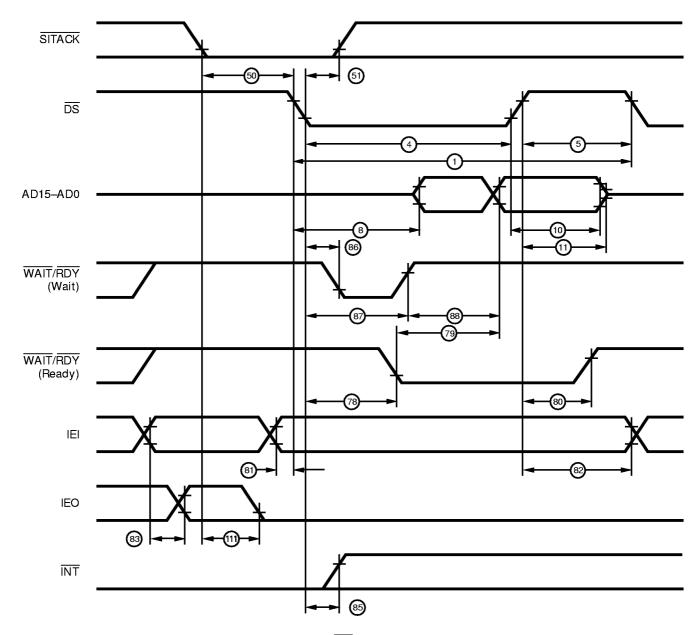

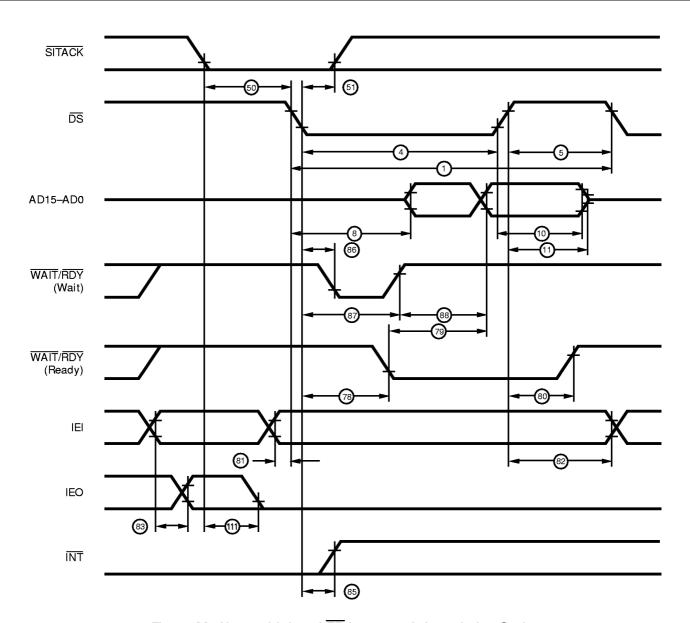

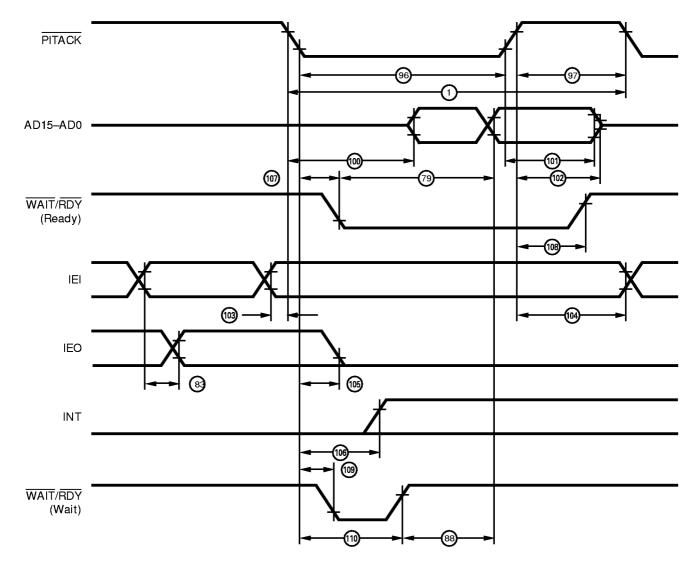

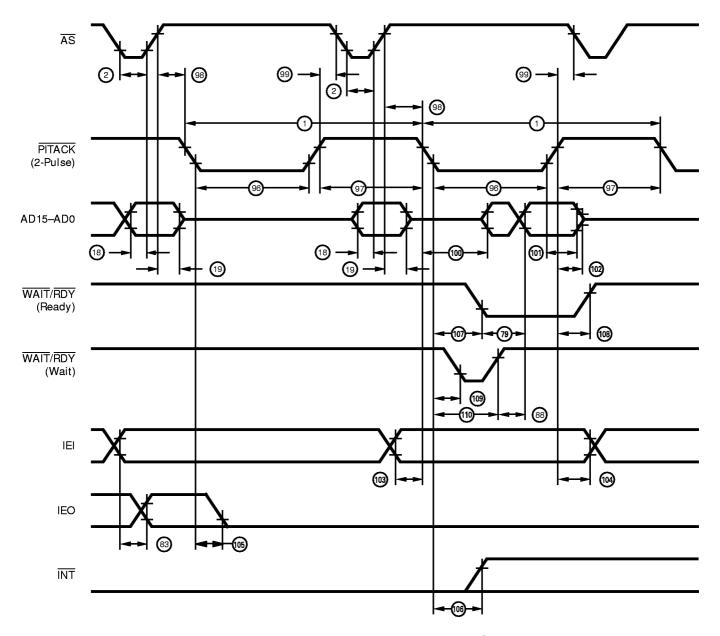

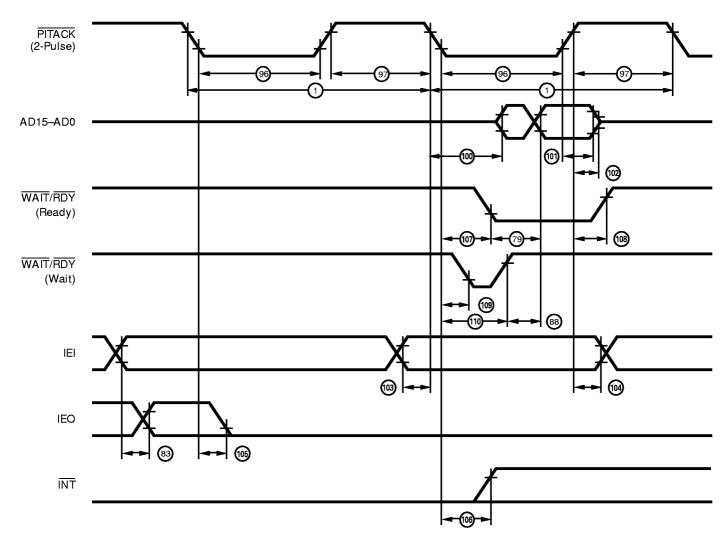

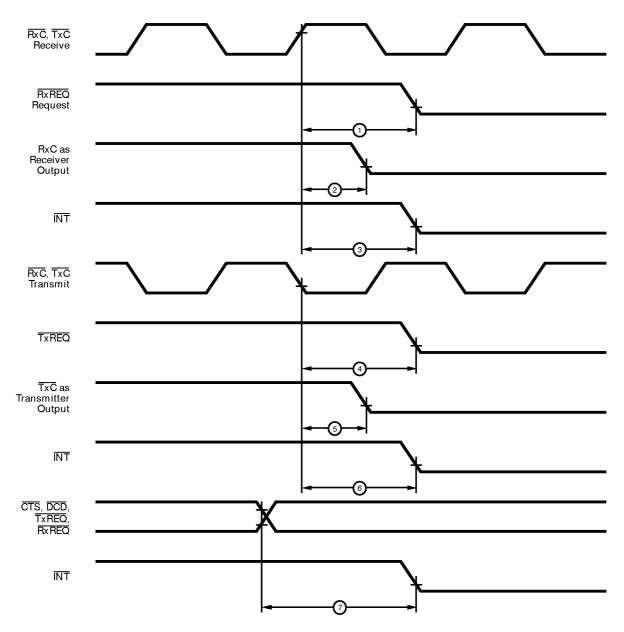

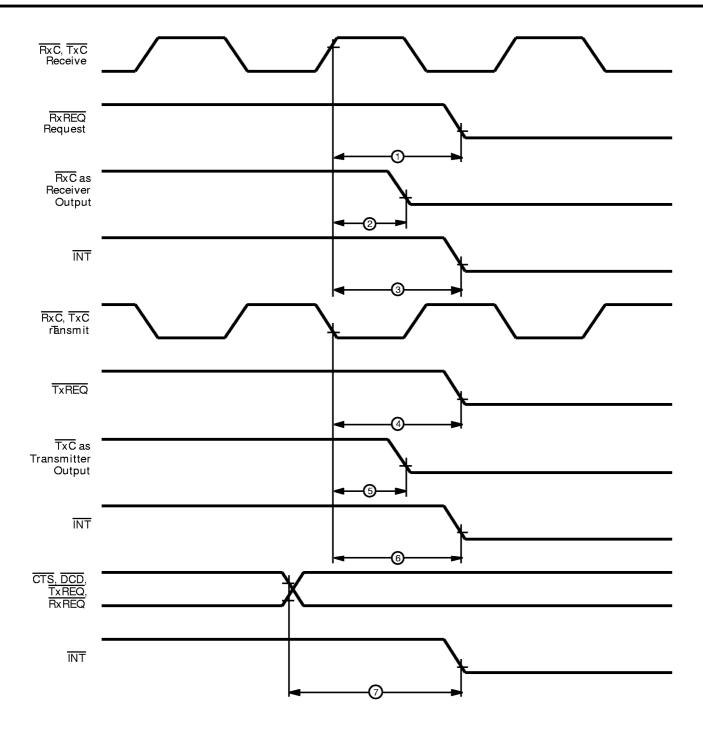

#### **USC TIMING**

The USC interface timing is similar to that found on a static RAM, except that it is much more flexible. Up to eight separate timing strobe signals may be present on the interface:  $\overline{DS}$ ,  $\overline{RD}$ ,  $\overline{WR}$ ,  $\overline{PITACK}$ ,  $\overline{RXACKA}$ ,  $\overline{RXACKB}$ ,  $\overline{TXACKA}$  and  $\overline{TXACKB}$ . Only one of these timing strobes may be active at any time. Should the external logic activate more than

one of these strobes at the same time the USC will enter a pre-reset state that is only exited by a hardware reset. Do not allow overlap of timing strobes. The timing diagrams, beginning on the next page, illustrate the different bus transactions possible, with the necessary setup, hold and delay times.

Figure 6. Reset Timing

Figure 7. Bus Cycle Timing

Note:  $\overline{\text{CLK}}$  is  $\overline{\text{RxC}}$  or  $\overline{\text{TxC}}$  when supplying DPLL, BRG, or CTR clock.

Figure 8. DM A Read Cycle

Figure 9. DM A Write Cycle

Figure 10. Multiplexed DS Read Cycle

Figure 11. Multiplexed DS Write Cycle

Figure 12. Multiplexed RD Read Cycle

Figure 13. Multiplexed WR Write Cycle

Figure 14. Nonmultiplexed  $\overline{\rm DS}$  Read Cycle

Figure 15. Nonmultiplexed  $\overline{\text{DS}}$  Write Cycle

Figure 16. Nonmultiplexed RD Read Cycle

Figure 17. Nonmultiplexed WR Write Cycle

Figure 18. Multiplexed DS Interrupt Acknowledged Cycle

Figure 19. Multiplexed  $\overline{RD}$  Interrupt Acknowledge Cycle

Figure 20. Multiplexed Pulsed Acknowledge Cycle

Figure 21. Nonmultiplexed  $\overline{\rm DS}$  Interrupt Acknowledge Cycle

Figure 22. Nonmultiplexed  $\overline{RD}$  Interrupt Acknowledge Cycle

Figure 23. Nonmultiplexed Pulsed Interrupt Acknowledge Cycle

Figure 24. Multiplexed Double-Pulse Intack Cycle