2

**Q**

# High-Speed CMOS 32Kx8 SRAM with Common I/O

QS83280

### FEATURES/BENEFITS

- · Equal access and cycle times

- 12ns/15ns Commercial

- 15ns/20ns Military

- TTL compatible I/O

- Available in 28-pin 300 DIP, SOJ, LCC

- · 6-Transistor memory cell for high reliability

- JEDEC standard pinout

- Military product compliant to MIL-STD-883

- Low power, high-speed QCMOS™ technology

#### DESCRIPTION

The QS83280 is a high-speed 256K SRAM organized as 32K words of 8 bits. It is manufactured in a high-performance CMOS process, and it based on a 6-transistor cell design for high reliability and excellent data retention. The high-speed access times of the QS83280 make it useful in cache data RAM, cache tag RAMs, high-speed scratchpad memories, look-up tables, pipelined DSP and bit-slice systems. Low operating power and excellent latch-up and ESD protection are provided.

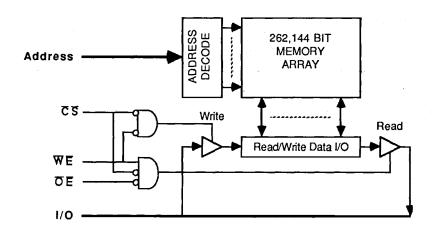

### FUNCTIONAL BLOCK DIAGRAM

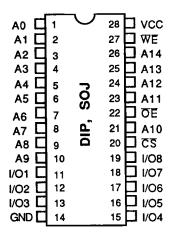

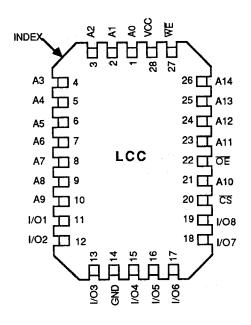

# PIN CONFIGURATIONS

ALL PINS TOP VIEW

### PIN DESCRIPTION

| Pin Name    | 1/0 | Function      |

|-------------|-----|---------------|

| Α           | 1   | Address       |

| I/O1 - I/O8 | 1/0 | Data          |

| cs          | - 1 | Chip Select   |

| WE          | I   | Write Enable  |

| ŌĒ          | 1   | Output Enable |

**FUNCTION TABLE**

| Function          | C S | WE | ΩE | 1/0      | Power   |  |  |  |

|-------------------|-----|----|----|----------|---------|--|--|--|

| Deselect          | Н   | Х  | Х  | High Z   | Standby |  |  |  |

| Read              | L   | Н  | L  | Data out | Active  |  |  |  |

| Write             | L   | L  | Х  | Data In  | Active  |  |  |  |

| Output<br>Disable | L   | Н  | Н  | High Z   | Active  |  |  |  |

### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage to Ground0.5V to +7.0V                           |

|-----------------------------------------------------------------|

| DC Output Voltage V <sub>O</sub> 0.5V to V <sub>CC</sub> + 0.5V |

| DC Input Voltage V <sub>1</sub> 0.5V to V <sub>CC</sub> + 0.5V  |

| AC Input Voltage (for a pulse width ≤20 ns)3.0V                 |

| DC Output Current Max. sink current/pin 50 mA                   |

| DC Output Current Max. source current/pin                       |

| TBIAS Temperature Under Bias, COM65° to +125°C                  |

| TSTG Storage Temperature, COM65° to +125°C                      |

| TBIAS Temperature Under Bias, MIL65° to +135°C                  |

| TSTG Storage Temperature, MIL65° to +155°C                      |

Note: Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to the maximum ratings for extended periods may affect reliability.

### CAPACITANCE

Ta=+25°C, f=1 MHz

| Name | Description        | Conditions           | Тур | Max | Unit |

|------|--------------------|----------------------|-----|-----|------|

| Cin  | Input Capacitance  | Vin = 0 V PDIP Pkg.  | 3   | 6   | pF   |

| Cin  | Input Capacitance  | Vin = 0 V SOJ Pkg.   | 2.5 | 5   | рF   |

| Cout | Output Capacitance | Vout = 0 V PDIP Pkg. |     | 7   | pF   |

| Cout | Output Capacitance | Vout = 0 V SOJ Pkg.  |     | 7   | pF   |

Note: Capacitance is measured at characterization but not tested at final production.

### DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE

Commercial TA =  $0^{\circ}$  C to  $70^{\circ}$ C,  $Vcc = 5.0V \pm 10\%$

Military TA = -55°C to 125° C, Vcc =  $5.0V\pm10$ %

| Symbol | Parameter             | Test Conditions                                   | Commercial |     | Military |     | Unit  |

|--------|-----------------------|---------------------------------------------------|------------|-----|----------|-----|-------|

|        |                       |                                                   | Min        | Max | Min      | Max |       |

| Vih    | Input HIGH Voltage    | Logic High for All Inputs                         | 2.2        | 6.0 | 2.2      | 6.0 | Volts |

| Vil    | Input LOW Voltage (1) | Logic Low for All Inputs                          |            | 0.8 |          | 0.8 |       |

| Voh    | Output HIGH Voltage   | loh = -4 mA, Vcc = MIN                            | 2.4        |     | 2.4      |     |       |

| Vol    | Output LOW Voltage    | lol = 8 mA, Vcc = MIN                             |            | 0.4 |          | 0.4 |       |

| 16     | Input Leakage         | Vcc = MAX,<br>Vin = GND to Vcc                    |            | 5   |          | 10  | μА    |

| llo    | Output Leakage        | Vcc = MAX,<br>Vout = GND to Vcc<br>Chip deselcted |            | 5   |          | 10  |       |

#### Notes:

### POWER SUPPLY CHARACTERISTICS

Commercial TA =  $0^{\circ}$  C to  $70^{\circ}$ C, Vcc =  $5.0V\pm10\%$  Military TA =  $-55^{\circ}$ C to  $125^{\circ}$  C, Vcc =  $5.0V\pm10\%$  VIc = 0.2 V, Vhc = Vcc - 0.2V At f = 0, no input lines switch; At f = f MAX, RAM is cycling at 1 / t RC

| Symbol | Parameter                                                                           | -12 | -15 |     | -20 | Unit |

|--------|-------------------------------------------------------------------------------------|-----|-----|-----|-----|------|

|        |                                                                                     | С   | C   | М   | М   |      |

| lcc    | Dynamic Operating<br>Current, Vcc = MAX<br>Outputs open<br>CS ≤ Vil, f = f MAX      | 180 | 170 | 180 | 170 | mA   |

| Isb    | TTL Standby Current, Vcc = MAX Outputs open CS ≥ Vih, f = f MAX                     | 90  | 90  | 100 | 100 |      |

| lsb1   | Full Standby Current, Vcc = MAX Outputs open CS ≥ Vhc, f = 0 Vin ≤ Vlc or Vin ≥ Vhc | 15  | 15  | 20  | 20  |      |

note: 12 ns is Advanced Information, 12 and 15 ns are Vcc = 5±5%

<sup>1.</sup> Transient inputs with Vil not more negative than -3.0 volts are permitted for pulse widths < 20 ns.

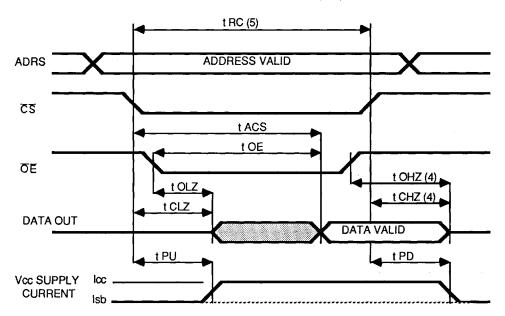

## SWITCHING CHARACTERISTICS OVER OPERATING RANGE

Commercial TA = 0° C to 70°C, Vcc =  $5.0V\pm10\%$  Military TA = -55°C to 125° C, Vcc =  $5.0V\pm10\%$  See Read Timing Diagrams. All values in nanoseconds unless otherwise noted

| Symbol     | Parameter                              | -12(3) |     | -15(3) |     | -2  | 0   |

|------------|----------------------------------------|--------|-----|--------|-----|-----|-----|

|            |                                        | Min    | Max | Min    | Max | Min | Max |

| READ CYCLE |                                        |        |     |        |     |     |     |

| t RC       | Read Cycle Time<br>(1)                 | 12     | 1   | 15     | -   | 20  | -   |

| t AA       | Address<br>Access Time                 | 1      | 12  | -      | 15  | -   | 20  |

| t ACS      | Chip Select<br>Access Time             | -      | 12  | -      | 15  | -   | 20  |

| t OH       | Output Hold from<br>Address Change     | 2      | -   | 2      | -   | 2   | -   |

| t CLZ      | Chip Select to<br>Output in Low Z (2)  | 2      |     | 2      | -   | 2   | -   |

| tCHZ       | Chip Select to<br>Output in High Z (2) | •      | 6   | •      | 7   | •   | 8   |

| tOE        | Output Enable<br>Access Time           |        | 7   |        | 8   |     | 10  |

| tOHZ       | Output enable to output in High Z (2)  | -      | 6   | •      | 7   | -   | 8   |

| tOLZ       | Output enable to output in Low Z (2)   | 0      | -   | 0      | -   | 0   | -   |

| tPU        | Chip select to<br>Power-Up time(2)     | 0      | -   | 0      | -   | 0   | -   |

| tPD        | Chip select to<br>Power-Down time(2)   | -      | 12  | •      | 15  | -   | 20  |

- 1) See Test Circuit and Waveforms. Minimums guaranteed but not tested.

- This parameter is guaranteed by design but not tested.

For Vcc±5% Commercial Only.

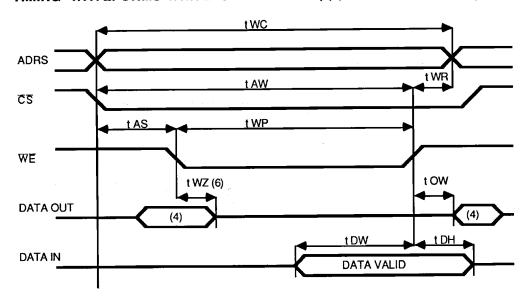

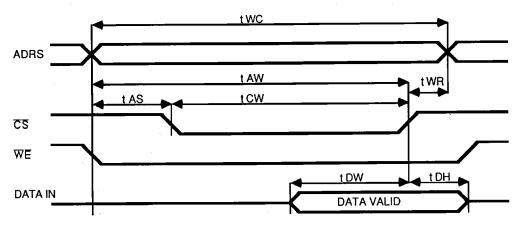

Commercial TA = 0° C to 70°C, Vcc =  $5.0V\pm10\%$  Military TA = -55°C to 125° C, Vcc =  $5.0V\pm10\%$  See Write Timing Diagrams. All values in nanoseconds unless otherwise noted

| Symbol      | Parameter                               | -12( | 3)  | -15( | (3) | -20 |     |  |

|-------------|-----------------------------------------|------|-----|------|-----|-----|-----|--|

|             |                                         | Min  | Max | Min  | Max | Min | Max |  |

| WRITE CYCLE |                                         |      |     |      |     |     |     |  |

| t WC        | Write Cycle Time<br>(1)                 | 12   |     | 15   | -   | 20  | 1   |  |

| t CW        | Chip Select Valid to<br>End of Write    | 10   | •   | 13   |     | 17  |     |  |

| t AS        | Address<br>Setup Time                   | 0    | -   | 0    | -   | 0   | _   |  |

| t WP        | Write Pulse width                       | 10   | -   | 12   | -   | 16  |     |  |

| t WR        | Write<br>Recovery Time                  | 0    | -   | 0    | •   | 0   |     |  |

| t DW        | Data Valid to<br>End of Write           | 7    | •   | 8    | -   | 10  | ,   |  |

| t DH        | Data Hold Time                          | 0    | •   | 0    | -   | ,O  | •   |  |

| t WZ        | Write Enable to<br>Output in High Z (2) | •    | 6   | -    | 7   | -   | 8   |  |

| t OW        | Output Active from<br>End of Write (2)  | 0    | -   | 0    | -   | 0   | -   |  |

| t AW        | Address Valid to<br>End of Write        | 10   | -   | 13   | -   | 17  | -   |  |

- See Test Circuit and Waveforms. Minimums guaranteed but not tested.

This parameter is guaranteed by design but not tested.

For Vcc±5% Commercial Only.

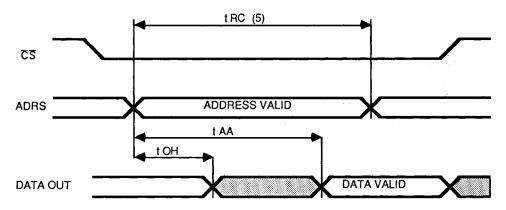

## TIMING WAVEFORMS - READ CYCLE NO. 1 (1,2,3)

## TIMING WAVEFORMS - READ CYCLE NO. 2 (1,3)

- WE is high for Read cycle.

CS is low for Read cycle #1.

- 3. Address is valid to or coincident with CS transition time for Read Cycle #2.

- 4. Transition to Hi-Z is measured ± 200 mV change from the prior steady state voltage.

- 5. All read timings are referenced from the last valid address to the first transitioning address.

## TIMING WAVEFORMS-WRITE CYCLE No. 1 (1,2,3 WE controlled timing)

## TIMING WAVEFORMS-WRITE CYCLE No. 2 (1,2,3,5 CS controlled timing)

- WE or CS must be high during address transitions.

- A write occurs during the overlap of a low CS and a low WE.

t WR is measured from the earlier of CS and WE going high to end of the write cycle.

During this period the I/O pins are in the output state and input signals must not be applied.

If the CS low transition occurs simultaneously with or after the WE low transition, the output remains in the high impedance state.

- Transition to Hi-Z is measured ± 200 mV change from the previous steady state voltage.