Creation Date: October 7, 1997 Revision: October 30, 1998

# ADVANCED INFORMATION AP9B134/AP9B134L

# 3.3V, 256K x 16 High-Speed, Low-Power CMOS Static RAM with Optional 2V Data Retention

#### **Features**

- Fast access times: 10, 12 and 15 ns

- Drives a 50 pF load vs. 30 pF industry standard load

- Multiple center power and ground pins for improved noise immunity

- 2V/200 μA data retention ("L" version)

- Low active power: 414 mW (Max.) at 15 ns

- Low standby current: 18mW (Max.)

- Individual byte controls for both Read and Write cycles

- TTL and CMOS-compatible inputs and outputs

- Single 3.0 V to 3.6 V power supply

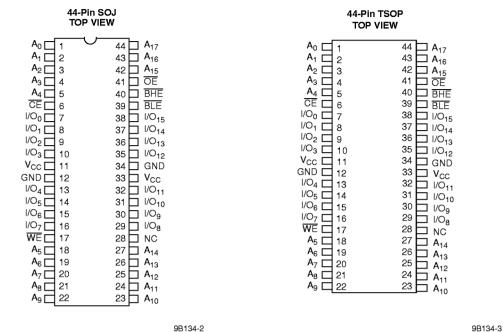

- Packaged in 44-pin, 400-mil SOJ and TSOP (Type II)

- · Commercial and industrial temperature range

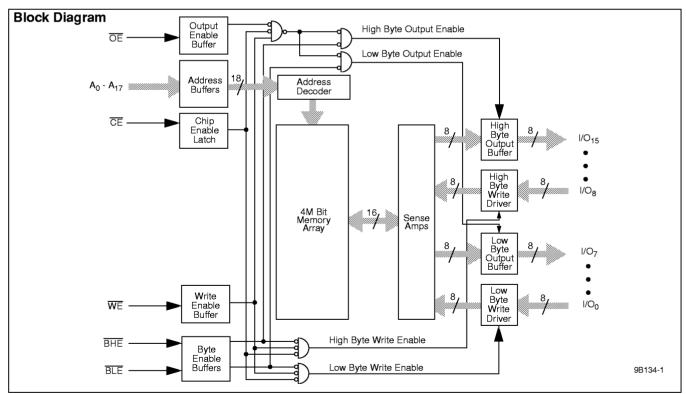

## **Functional Description**

The Aptos AP9B134/AP9B134L is a high-speed, low-power, 128K x 16, CMOS static RAM. It is fabricated using Aptos' high-performance CMOS, 0.35µ technology. This highly reli-

able process, coupled with innovative circuit design techniques, yields high-performance at low power consumption.

Writing to the device is accomplished by bringing Chip Enable  $(\overline{CE})$  and Write Enable  $(\overline{WE})$  inputs LOW. If Byte Enable Low  $(\overline{BLE})$  is LOW, then data from I/O $_0$  through I/O $_7$  is written into the location specified on the address pins  $A_0$  through  $A_{17}.$  If Byte Enable High  $(\overline{BHE})$  is LOW, then data from I/O $_8$  through I/O $_{15}$  is written into the location specified on the address pins  $A_0$  through  $A_{17}.$  The use of  $\overline{BHE}$  and  $\overline{BLE}$  in conjunction with  $\overline{WE}$  being held LOW, across several cycles, allows for 'back-to-back' writes as required by some industry DSPs.

Reading from the AP9B134/AP9B134L is accomplished by taking  $\overline{CE}$  and  $\overline{OE}$  LOW while forcing  $\overline{WE}$  HIGH. If  $\overline{BLE}$  is LOW, then data from the memory location specified by the address pins will appear on I/O<sub>0</sub> through I/O<sub>7</sub>. If  $\overline{BHE}$  is LOW, then data from memory will appear on I/O<sub>8</sub> through I/O<sub>15</sub> (See Truth Table).

This device offers multiple center power and ground pins for improved noise and speed characteristics.

## **Selection Guide**

|                                | AP9B134/L-10 | AP9B134/L-12 | AP9B134/L-15 |

|--------------------------------|--------------|--------------|--------------|

| Maximum Access Time (ns)       | 10           | 12           | 15           |

| Maximum Operating Current (mA) | 140          | 130          | 115          |

| Maximum Standby Current (mA)   | 5            | 5            | 5            |

#### **Pin Configurations**

## AP9B134/AP9B134L

## **Maximum Ratings**

(Above which the useful life may be impaired. For user guidelines, not tested.)

Storage Temperature .....-65 °C to +150 °C Ambient Temperature

with Power Applied ......-55 °C to +125 °C

| V <sub>CC</sub> Supply Relative to GND0.5 V to             | +7.0 V |

|------------------------------------------------------------|--------|

| Voltage on any Pin Relative to GND0.5 V to V <sub>CC</sub> | +0.5 V |

| Short Circuit Output Current <sup>1</sup> ±                | 20 mA  |

| Power Dissipation                                          | 1.0 W  |

# **Electrical Characteristics** Over the Operating Range ( $0^{\circ}C \le T_A \le 70^{\circ}$ C, $V_{CC} = 3.0$ V Min. to 3.6 V Max.) - Commercial

|                   |                                 |                                                               | 9B134/L-10   9B134/L-12   9B1 |          | 9B134 | 4/L-15   |      |          |      |

|-------------------|---------------------------------|---------------------------------------------------------------|-------------------------------|----------|-------|----------|------|----------|------|

| Symbol            | Parameter                       | Test Conditions                                               | Min.                          | Max.     | Min.  | Max.     | Min. | Max.     | Unit |

| $I_{CC1}$         | Dynamic Operating               | $V_{CC} = Max., I_{OUT} = 0 mA,$                              |                               | 140      |       | 130      |      | 115      | mA   |

|                   | Current <sup>2</sup>            | $\overline{\text{CE}} = V_{\text{IL}}$ , $f = \text{fmax}$    |                               |          |       |          |      |          |      |

| $I_{CC2}$         | Static Operating                | $V_{CC} = Max., I_{OUT} = 0 mA,$                              |                               | 75       |       | 75       |      | 75       | mA   |

|                   | Current <sup>2</sup>            | $\overline{\text{CE}} = V_{\text{IL}}, f = 0$                 |                               |          |       |          |      |          |      |

| $I_{SB1}$         | TTL Standby Current             | $V_{CC} = Max., V_{IN} = V_{IH} \text{ or } V_{IL},$          |                               | 35       |       | 30       |      | 25       | mA   |

|                   | -TTL Inputs                     | $\overline{\text{CE}} \ge V_{\text{IH}}$ , $f = \text{Max}$ . |                               |          |       |          |      |          |      |

| $I_{SB2}$         | CMOS Standby Current            | $V_{CC} = Max., \overline{CE} \ge V_{CC}$                     |                               | 5        |       | 5        |      | 5        | mA   |

|                   | -CMOS Inputs                    | $ -0.2V, V_{IN} \ge V_{CC} - 0.2V $                           |                               |          |       |          |      |          |      |

|                   |                                 | or $V_{IN} \le 0.2V$ , $f = 0$                                |                               |          |       |          |      |          |      |

| $I_{LI}$          | Input Leakage Current           | $GND \le V_{IN} \le V_{CC}$                                   | -1                            | 1        | -1    | 1        | -1   | 1        | μΑ   |

| $I_{LO}$          | Output Leakage Current          | $GND \le V_{OUT} \le V_{CC}$                                  | -1                            | 1        | -1    | 1        | -1   | 1        | μA   |

|                   |                                 | Output Disabled                                               |                               |          |       |          |      |          |      |

| $V_{OH}$          | Output High Voltage             | $V_{\rm CC}$ = Min., $I_{\rm OH}$ = -4.0 mA                   | 2.4                           |          | 2.4   |          | 2.4  |          | V    |

| $V_{OL}$          | Output Low Voltage              | $V_{\rm CC}$ = Min., $I_{\rm OL}$ = 8.0 mA                    |                               | 0.4      |       | 0.4      |      | 0.4      | V    |

| $V_{\mathrm{IH}}$ | Input High Voltage <sup>3</sup> |                                                               | 2.0                           | $V_{CC}$ | 2.0   | $V_{CC}$ | 2.0  | $v_{cc}$ | V    |

|                   |                                 |                                                               |                               | +0.3     |       | +0.3     |      | +0.3     |      |

| $V_{\mathrm{IL}}$ | Input Low Voltage <sup>3</sup>  |                                                               | -0.3                          | 0.8      | -0.3  | 0.8      | -0.3 | 0.8      | V    |

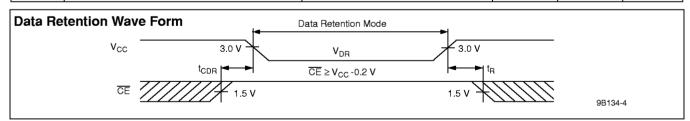

## Data Retention Characteristics ("L" Version) -Commercial

| Symbol           | Description                          | Test Conditions <sup>4</sup>                                 | Min.            | Max. | Unit |

|------------------|--------------------------------------|--------------------------------------------------------------|-----------------|------|------|

| V <sub>DR</sub>  | V <sub>CC</sub> for Data Retention   | $V_{CC} = V_{DR} = 2.0V,$                                    | 2.0             |      | V    |

| $I_{CCDR}$       | Data Retention Current               | $\overline{CE} \ge V_{CC}$ -0.2 V,                           |                 | 200  | μΑ   |

| t <sub>CDR</sub> | Chip Deselect to Data Retention Time | $V_{\rm IN} \ge V_{\rm CC}$ -0.2 V or $V_{\rm IN} \le 0.2$ V | 0               |      | ns   |

| t <sub>R</sub>   | Operation Recovery Time              |                                                              | t <sub>RC</sub> |      | ns   |

# Capacitance 5

| Symbol            | Description       | Max. | Unit |

|-------------------|-------------------|------|------|

| $C_{\mathrm{IN}}$ | Input Capacitance | 5    | pF   |

| $C_{OUT}$         | I/O Capacitance   | 5    | pF   |

#### Notes:

- 1. No more than one output should be shorted at one time. Duration of the short circuit should not exceed 30 seconds.

- 2.  $I_{\rm CC}$  is dependent upon output loading and cycle rates. Specified values are with outputs open.

- 3.  $V_{IL}$  undershoot = -1.0V where t=t<sub>RC</sub>/4 per cycle.  $V_{IH}$  overshoot

- =  $V_{CC}$  +1.0V where t=t<sub>RC</sub>/4 per cycle.

- 4. No input may exceed  $V_{CC}$  +0.3V (DC).

- 5. Tested initially and after any design or process changes that may effect these parameters.

# AP9B134/AP9B134L

## **Electrical Characteristics** Over the Operating Range (-40°C ≤ T<sub>A</sub> ≤ 85°C, V<sub>CC</sub> = 3.0V Min. to 3.6V Max.) -Industrial

|                   |                                        |                                                                                                                                     |      | 9B134/L-12              |      | 9B134/L-15              |      |

|-------------------|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|------|-------------------------|------|-------------------------|------|

| Symbol            | Parameter                              | Test Conditions                                                                                                                     | Min. | Max.                    | Min. | Max.                    | Unit |

| $I_{CC1}$         | Dynamic Operating Current <sup>2</sup> | $V_{CC}$ = Max., $I_{OUT}$ = 0 mA,<br>$\overline{CE}$ = $V_{IL}$ , f = fmax                                                         |      | 140                     |      | 125                     | mA   |

| $I_{CC2}$         | Operating Current <sup>2</sup>         | $V_{CC}$ = Max., $I_{OUT}$ = 0 mA,<br>$\overline{CE}$ = $V_{IL}$ , f = 0                                                            |      | 85                      |      | 85                      | mA   |

| $I_{SB1}$         | TTL Standby Current -TTL Inputs        | $V_{CC} = Max., V_{IN} = V_{IH} \text{ or } V_{IL},$<br>$\overline{CE} \ge V_{IH}, f = Max.$                                        |      | 35                      |      | 30                      | mA   |

| $I_{SB2}$         | CMOS Standby<br>Current -CMOS Inputs   | $V_{CC} = Max., \overline{CE} \ge V_{CC} -0.2 \text{ V},$<br>$V_{IN} \ge V_{CC} -0.2 \text{ V or } V_{IN} \le 0.2 \text{ V}, f = 0$ |      | 10                      |      | 10                      | mA   |

| $I_{LI}$          | Input Leakage Current                  | $GND \le V_{IN} \le V_{CC}$                                                                                                         | -5   | 5                       | -5   | 5                       | μΑ   |

| $I_{LO}$          | Output Leakage Current                 | $GND \le V_{OUT} \le V_{CC}$ , Output Disabled                                                                                      | -5   | 5                       | -5   | 5                       | μΑ   |

| $V_{\mathrm{OH}}$ | Output High Voltage                    | $V_{\rm CC}$ = Min., $I_{\rm OH}$ = -4.0 mA                                                                                         | 2.4  |                         | 2.4  |                         | V    |

| $V_{\mathrm{OL}}$ | Output Low Voltage                     | $V_{\rm CC}$ = Min., $I_{\rm OL}$ = 8.0 mA                                                                                          |      | 0.4                     |      | 0.4                     | V    |

| $V_{\mathrm{IH}}$ | Input High Voltage <sup>3</sup>        |                                                                                                                                     | 2.0  | V <sub>CC</sub><br>+0.3 | 2.0  | V <sub>CC</sub><br>+0.3 | V    |

| $V_{\mathrm{IL}}$ | Input Low Voltage <sup>3</sup>         |                                                                                                                                     | -0.3 | 0.8                     | -0.3 | 0.8                     | V    |

# Data Retention Characteristics ("L" Version) -Industrial

| Symbol            | Description                          | Test Conditions <sup>4</sup>                                                            | Min.            | Max. | Unit |

|-------------------|--------------------------------------|-----------------------------------------------------------------------------------------|-----------------|------|------|

| $V_{\mathrm{DR}}$ | V <sub>CC</sub> for Data Retention   | $V_{CC} = V_{DR} = 2.0V$ ,                                                              | 2.0             |      | V    |

| I <sub>CCDR</sub> | Data Retention Current               | $\overline{\text{CE}} \ge V_{\text{CC}}$ -0.2V, $V_{\text{IN}} \ge V_{\text{CC}}$ -0.2V |                 | 2    | mA   |

| $t_{\rm CDR}$     | Chip Deselect to Data Retention Time | or $V_{IN} \le 0.2V$                                                                    | 0               |      | ns   |

| t <sub>R</sub>    | Operation Recovery Time              |                                                                                         | t <sub>RC</sub> |      | ns   |

## AP9B134/AP9B134L

## Switching Characteristics Over the Operating Range 6,7

|                           |                                    | 9B134/L-10 |      | 9B134 | I/L-12 | L-12 9B134/L-15 |      |      |  |

|---------------------------|------------------------------------|------------|------|-------|--------|-----------------|------|------|--|

| Parameter                 | Description                        | Min.       | Max. | Min.  | Max.   | Min.            | Max. | Unit |  |

| Read Cycle 8              |                                    | •          |      |       |        |                 |      |      |  |

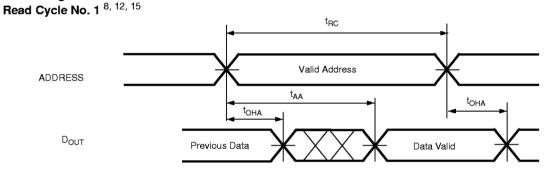

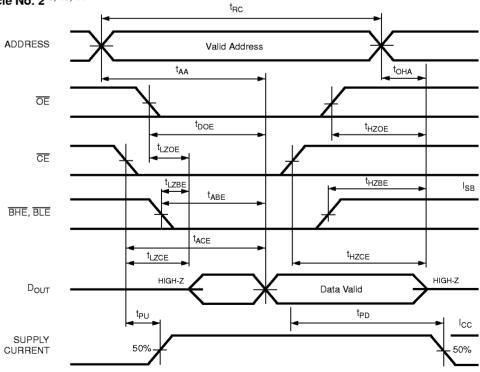

| $t_{RC}$                  | Read Cycle Time                    | 10         |      | 12    |        | 15              |      | ns   |  |

| t <sub>AA</sub>           | Address Access Time                |            | 10   |       | 12     |                 | 15   | ns   |  |

| t <sub>OHA</sub>          | Output Hold Time                   | 3          |      | 3     |        | 3               |      | ns   |  |

| t <sub>ACE</sub>          | CE Access Time                     |            | 10   |       | 12     |                 | 15   | ns   |  |

| $t_{\rm DOE}$             | OE Access Time                     |            | 4    |       | 5      |                 | 7    | ns   |  |

| t <sub>LZOE</sub> 9       | OE to Low-Z Output                 | 0          |      | 0     |        | 0               |      | ns   |  |

| t <sub>HZOE</sub> 9       | OE to High-Z Output                |            | 4    |       | 5      |                 | 6    | ns   |  |

| t <sub>LZCE</sub> 9       | CE to Low-Z Output                 | 3          |      | 3     |        | 3               |      | ns   |  |

| t <sub>HZCE</sub> 9       | CE to High-Z Output                |            | 4    |       | 6      |                 | 8    | ns   |  |

| $t_{ m PU}$               | CE to Power Up                     | 0          |      | 0     |        | 0               |      | ns   |  |

| $t_{ m PD}$               | CE to Power Down                   |            | 10   |       | 12     |                 | 15   | ns   |  |

| t <sub>ABE</sub>          | Byte Enable Access Time            |            | 3    |       | 4      |                 | 5    | ns   |  |

| t <sub>LZBE</sub> 9       | Byte Enable to Output Low-Z        | 0          |      | 0     |        | 0               |      | ns   |  |

| t <sub>HZBE</sub> 9       | Byte Enable to Output High-Z       |            | 3    |       | 4      |                 | 5    | ns   |  |

| Write Cycle <sup>10</sup> |                                    |            |      |       |        |                 |      |      |  |

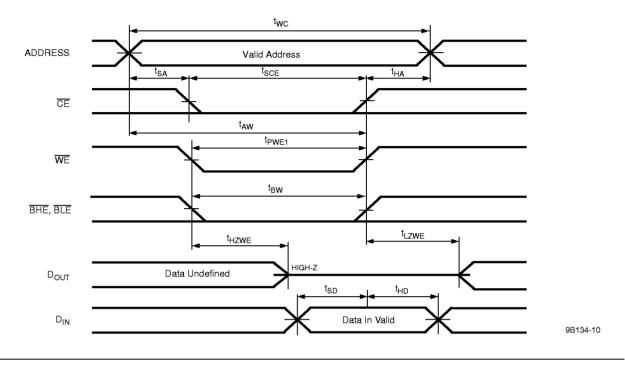

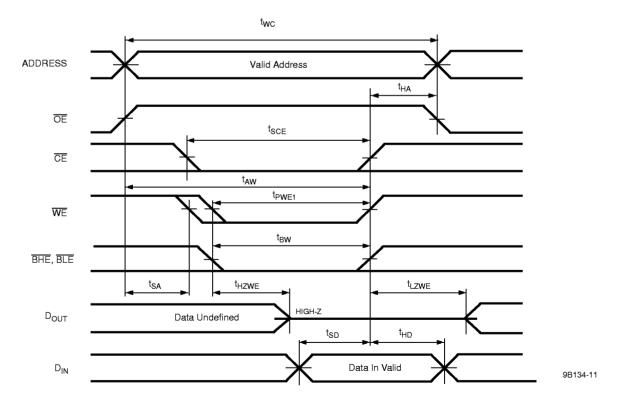

| $t_{WC}$                  | Write Cycle Time                   | 10         |      | 12    |        | 15              |      | ns   |  |

| t <sub>SCE</sub>          | CE to Write End                    | 8          |      | 8     |        | 10              |      | ns   |  |

| t <sub>AW</sub>           | Address Set-up Time to Write End   | 8          |      | 8     |        | 10              |      | ns   |  |

| t <sub>HA</sub>           | Address Hold to Write End          | 0          |      | 0     |        | 0               |      | ns   |  |

| $t_{SA}$                  | Address Set-up Time to Write Start | 0          |      | 0     |        | 0               |      | ns   |  |

| t <sub>PWE1</sub> 11      | WE Pulse Width (OE =HIGH)          | 8          |      | 8     |        | 10              |      | ns   |  |

| t <sub>PWE2</sub>         | WE Pulse Width (OE =LOW)           | 10         |      | 12    |        | 12              |      | ns   |  |

| $t_{ m SD}$               | Data Set-up to Write End           | 6          |      | 6     |        | 7               |      | ns   |  |

| $t_{ m HD}$               | Data Hold from Write End           | 0          |      | 0     |        | 0               |      | ns   |  |

| t <sub>HZWE</sub> 9       | WE LOW to High-Z Output            |            | 5    |       | 6      |                 | 7    | ns   |  |

| t <sub>LZWE</sub> 9       | WE HIGH to Low-Z Output            | 2          |      | 2     |        | 2               |      | ns   |  |

| $t_{ m BW}$               | Byte Enable to End of Write        | 8          |      | 8     |        | 10              |      | ns   |  |

#### **Notes:**

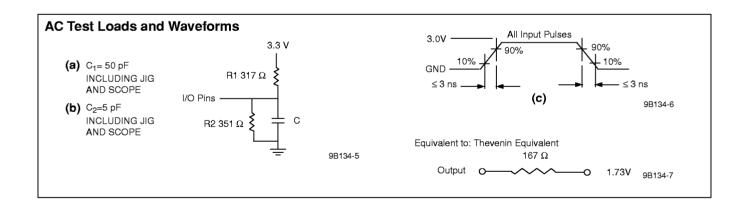

6. Test conditions assume signal transition times of 3 ns or less, timing reference levels of 1.5 V, input pulse levels of 0 V to 3.0 V and output loading specified in AC Test Loads and Waveforms  $Figure\ (a)$ , unless otherwise noted.

- 7. I/O will assume the High-Z state if  $\overline{\text{OE}} \ge V_{\text{IH}}$ .

- 8. WE is HIGH for a Read Cycle.

- 9. Tested with the load in AC Test Loads and Waveforms *Figure* (b). Transition is measured ±500mV from steady state voltage.

- 10. The internal write time is defined by the overlap of  $\overline{CE}$  LOW and  $\overline{WE}$  LOW. All signals must be in valid states to initiate a Write,

but any can be deasserted to terminate the Write. The Data Input Set-up and Hold timing is referenced to the rising or falling edge of the signal that terminates the write.

- 11. Tested with  $\overline{OE}$  HIGH for a minimum of 4 ns before  $\overline{WE}$  = LOW to place I/O in High-Z state.

- 12. The device is continuously selected.  $\overline{OE}$ ,  $\overline{CE} = V_{IL}$ .

- 13. Address is valid prior to, or coincident with,  $\overline{\text{CE}}$  LOW transitions.

- 14. At any given temperature and voltage condition,  $t_{\mbox{HZCE}}$  is less than  $t_{\mbox{LZCE}}$ ,  $t_{\mbox{HZOE}}$  is less than  $t_{\mbox{LZOE}}$  and  $t_{\mbox{HZBE}}$  is less than  $t_{\mbox{LZDE}}$ .

- 15. BHE and BLE are held in their asserted state (LOW).

# AP9B134/AP9B134L

## **Pin Descriptions**

#### A<sub>0</sub> - A<sub>17</sub>: Address Inputs

These 18 address inputs select one of the 262,144, 16-bit words in the RAM.

### **CE**: Chip Enable Input

$\overline{\text{CE}}$  is asserted LOW. The Chip Enable is asserted LOW to read from or write to the device. If Chip Enable is deasserted, the device is deselected and is in a standby power mode. The I/O pins will be in the High-Z state when the device is deselected.

#### OE: Output Enable Input

The Output Enable input is asserted LOW. If the Output Enable is asserted LOW while  $\overline{CE}$  is asserted (LOW) and  $\overline{WE}$  is deasserted (HIGH), data from the SRAM will be present on the I/O pins. The I/O pins will be in the High-Z state when  $\overline{OE}$  is deasserted.

## WE: Write Enable Input

The Write Enable input is asserted LOW and controls read and write operations. When  $\overline{CE}$  and  $\overline{WE}$  are both asserted (LOW) input data present on the I/O pins will be written into the selected memory location.

#### BHE, BLE: Byte Enables

These active LOW inputs allow individual bytes to be written to, or read. When  $\overline{BLE}$  is LOW, data is written to, or read from, the lower byte (I/O<sub>0</sub> - I/O<sub>7</sub>). When  $\overline{BHE}$  is LOW, data is written to, or read from, the upper byte (I/O<sub>8</sub> - I/O<sub>15</sub>).

## I/O<sub>0</sub> - I/O<sub>15</sub>: Common Input/Output Pins

**GND: Ground**

# Switching Waveforms

9B134-8

## **Read Cycle No. 2** 8, 13, 14

9B134-9

Switching Waveforms (continued)

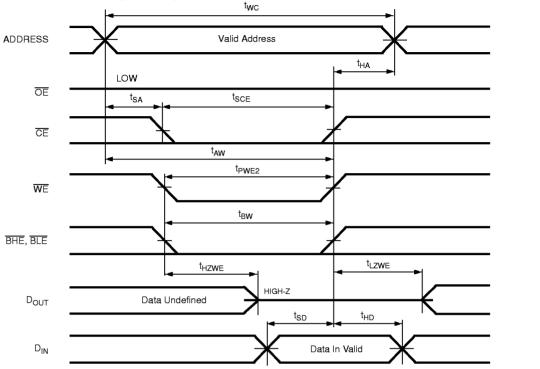

Write Cycle No.1 (CE controlled, OE is HIGH or LOW) 10

Write Cycle No.2 (OE is HIGH During Write Cycle) 10

# Switching Waveforms (continued) Write Cycle No.3 (OE is LOW During Write Cycle) 10

9B134-12

9B134-13

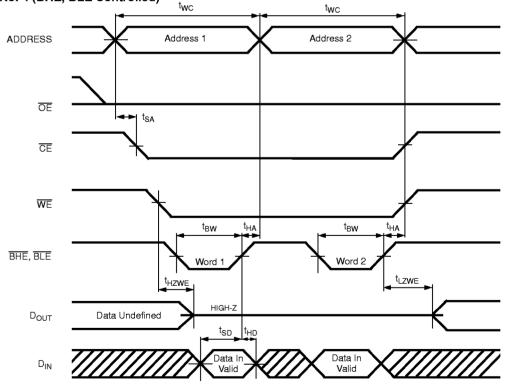

# Write Cycle No. 4 (BHE, BLE Controlled) 16

Note:

16.  $\overline{WE}$  may be held LOW across many address cycles and the  $\overline{BHE}$ ,  $\overline{BLE}$  pins can be used to control the write function.

# AP9B134/AP9B134L

## **Truth Table**

| Mode                                                    | CE | ŌĒ | WE | BLE | BHE | I/O <sub>0</sub> - I/O <sub>7</sub> | I/O <sub>8</sub> - I/O <sub>15</sub> | Power              |

|---------------------------------------------------------|----|----|----|-----|-----|-------------------------------------|--------------------------------------|--------------------|

| Standby                                                 | Н  | X  | X  | X   | X   | High-Z                              | High-Z                               | $I_{SB1}, I_{SB2}$ |

| Low Byte Read (I/O <sub>0</sub> - I/O <sub>8</sub> )    | L  | L  | Н  | L   | Н   | $D_{ m OUT}$                        | High-Z                               | $I_{CC1}, I_{CC2}$ |

| High Byte Read (I/O <sub>9</sub> - I/O <sub>15</sub> )  | L  | L  | Н  | Н   | L   | High-Z                              | $D_{ m OUT}$                         | $I_{CC1}, I_{CC2}$ |

| Word Read (I/O <sub>0</sub> - I/O <sub>15</sub> )       | L  | L  | Н  | L   | L   | $D_{OUT}$                           | $D_{ m OUT}$                         | $I_{CC1}, I_{CC2}$ |

| Word Write (I/O <sub>0</sub> - I/O <sub>15</sub> )      | L  | X  | L  | L   | L   | $D_{\mathrm{IN}}$                   | $D_{\mathrm{IN}}$                    | $I_{CC1}, I_{CC2}$ |

| Low Byte Write (I/O <sub>0</sub> - I/O <sub>8</sub> )   | L  | X  | L  | L   | Н   | $\mathrm{D_{IN}}$                   | High-Z                               | $I_{CC1}, I_{CC2}$ |

| High Byte Write (I/O <sub>9</sub> - I/O <sub>15</sub> ) | L  | X  | L  | Н   | L   | High-Z                              | $\mathrm{D_{IN}}$                    | $I_{CC1}, I_{CC2}$ |

| Output Disable                                          | L  | Н  | Н  | X   | X   | High-Z                              | High-Z                               | $I_{CC1}, I_{CC2}$ |

|                                                         | L  | X  | X  | Н   | Н   | High-Z                              | High-Z                               | $I_{CC1}, I_{CC2}$ |

# **Ordering Information**

Standard - AP9B134

| Speed | Part Number  | Package Name | Package Type                      | Temperature Range |

|-------|--------------|--------------|-----------------------------------|-------------------|

| 10    | AP9B134-10VC | V44.1        | 44-Pin Small Outline J-Bend       | Commercial        |

|       | AP9B134-10TC | T44.1        | 44-Pin Thin Small Outline Package | Commercial        |

| 12    | AP9B134-12VC | V44.1        | 44-Pin Small Outline J-Bend       | Commercial        |

|       | AP9B134-12VI | V44.1        | 44-Pin Small Outline J-Bend       | Industrial        |

|       | AP9B134-12TC | T44.1        | 44-Pin Thin Small Outline Package | Commercial        |

|       | AP9B134-12TI | T44.1        | 44-Pin Thin Small Outline Package | Industrial        |

| 15    | AP9B134-15VC | V44.1        | 44-Pin Small Outline J-Bend       | Commercial        |

|       | AP9B134-15VI | V44.1        | 44-Pin Small Outline J-Bend       | Industrial        |

|       | AP9B134-15TC | T44.1        | 44-Pin Thin Small Outline Package | Commercial        |

|       | AP9B134-15TI | T44.1        | 44-Pin Thin Small Outline Package | Industrial        |

## With Optional 2V Data Retention - AP9B134L

| Speed | Part Number   | Package Name | Package Type                      | Temperature Range |

|-------|---------------|--------------|-----------------------------------|-------------------|

| 10    | AP9B134L-10VC | V44.1        | 44-Pin Small Outline J-Bend       | Commercial        |

|       | AP9B134L-10TC | T44.1        | 44-Pin Thin Small Outline Package | Commercial        |

| 12    | AP9B134L-12VC | V44.1        | 44-Pin Small Outline J-Bend       | Commercial        |

|       | AP9B134L-12VI | V44.1        | 44-Pin Small Outline J-Bend       | Industrial        |

|       | AP9B134L-12TC | T44.1        | 44-Pin Thin Small Outline Package | Commercial        |

|       | AP9B134L-12TI | T44.1        | 44-Pin Thin Small Outline Package | Industrial        |

| 15    | AP9B134L-15VC | V44.1        | 44-Pin Small Outline J-Bend       | Commercial        |

|       | AP9B134L-15VI | V44.1        | 44-Pin Small Outline J-Bend       | Industrial        |

|       | AP9B134L-15TC | T44.1        | 44-Pin Thin Small Outline Package | Commercial        |

|       | AP9B134L-15TI | T44.1        | 44-Pin Thin Small Outline Package | Industrial        |

Document # DS-00065-Rev A

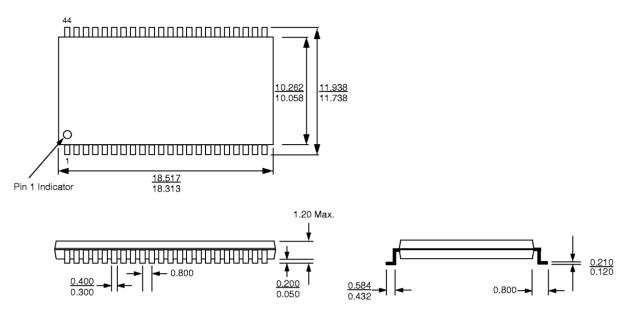

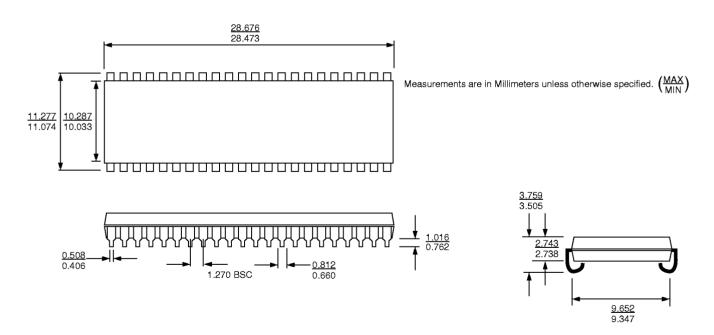

#### **Package Diagrams**

### T44.1 - 44-Pin (400-Mil) Thin Small Outline Package (TSOP)

Measurements are in Millimeters unless otherwise specified.  $\left(\frac{MAX}{MIN}\right)$

#### V44.1 - 44-Pin (400-Mil) Small Outline J-Bend (SOJ)

<sup>©</sup> Aptos Semiconductor Corporation, 1998. The information contained herein is subject to change without notice. Aptos assumes no responsibility for the use of any circuitry other than circuitry embodied in an Aptos Semiconductor product. Nor does it convey or imply any license under patent or other rights. Aptos Semiconductor does not authorize its products for use as critical components in life-support systems where a malfunction or failure of the product may reasonably be expected to result in significant injury to the user. The inclusion of Aptos Semiconductor products in life-support systems applications implies that the manufacturer assumes all risk of such use and in so doing indemnifies Aptos Semiconductor against all damages.