## CD54HC4514/3A CD54HCT4514/3A

# 4-to-16-Line Decoder/Demultiplexer w/Input Latches

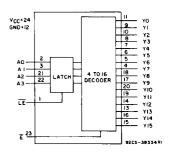

The RCA CD54HC4514 and CD54HCT4514 are high-speed silicon-gate devices consisting of a 4-bit strobed latch and a 4-to-16-line decoder. The selected output is enabled by a low on the enable input (Ē). A high on Ē inhibits selection of any output. Demultiplexing is accomplished by using the E input as the data input and the select inputs (A0-A3) as addresses. This Ē input also serves as a chip select when these devices are cascaded.

When Latch Enable (LE) is high the output follows changes in the inputs. When LE is low the output is isolated from changes in the input and remains at the level (high) it had before the latches were enabled. These devices, enhanced versions of the equivalent CMOS types, can drive 10 LSTTL loads.

### **Package Specifications**

See Section 11, Fig. 15

#### **FUNCTIONAL DIAGRAM**

#### Static Electrical Characteristics (Limits with black dots (•) are tested 100%)

|                 |        | TEST CONDITIONS                               |                           |                                       |                                       |           |   |       |      |    |

|-----------------|--------|-----------------------------------------------|---------------------------|---------------------------------------|---------------------------------------|-----------|---|-------|------|----|

|                 | нс/нст |                                               |                           |                                       | Vin                                   |           | 1 |       |      |    |

|                 |        |                                               | HU                        | /HC1                                  |                                       | нс нст    |   | LIN   |      |    |

| CHARACTERISTICS |        | V <sub>DD</sub> V <sub>O</sub> I <sub>O</sub> | V <sub>cc</sub> or<br>GND | V <sub>IL</sub><br>or V <sub>IH</sub> | V <sub>IL</sub><br>or V <sub>IH</sub> | MIN. MAX. |   | UNITS |      |    |

| Quiescent       | 25°C   | 6                                             |                           |                                       | 6, 0                                  | _         | _ | _     | 8•   |    |

| Device Current  | -55°C  | 6                                             |                           |                                       | 6, 0                                  |           | _ |       | 160• | μA |

| loc             | +125°C |                                               |                           |                                       | 0,0                                   |           |   |       | 1000 |    |

The complete static electrical test specification consists of the above by-type static tests combined with the standard static tests in the beginning of this section.

#### **HCT INPUT LOADING TABLE**

| INPUT   | UNIT LOAD* |

|---------|------------|

| A0 - A3 | 0.15       |

| ΙĒ      | 0.85       |

| Ē       | 0.3        |

\*Unit load is ΔI<sub>CC</sub> limit specified in Static Characteristics Chart, e.g., 360 μA max. @ 25° C.

## CD54HC4514/3A CD54HCT4514/3A

Switching Speed (Limits with black dots (\*) are tested 100%.) SWITCHING CHARACTERISTICS (C<sub>L</sub> = 50 pF, Input t, t<sub>l</sub> = 6 ns)

| CHARACTERISTIC         | T                |     | 25°C |      |          |      | -55°C to +125°C |      |          |                |       |

|------------------------|------------------|-----|------|------|----------|------|-----------------|------|----------|----------------|-------|

|                        | SYMBOL           | Vcc | нс   |      | HCT      |      | 54HC            |      | 54HCT    |                | UNITS |

|                        |                  | V   | Min. | Max. | Min.     | Max. | Min.            | Max. | Min.     | Max.           |       |

| Propagation Delay      | †                | 2   | _    | 275  | _        | _    | _               | 115  |          | -              |       |

| Select to Outputs      |                  | 4.5 | _    | 55•  | l —      | 55•  | l —             | 83•  | <u> </u> | 83•            |       |

|                        | t <sub>PLH</sub> | 6   | _    | 47   | _        |      |                 | 71   | <u> </u> |                | ns    |

|                        |                  | 2   |      | 225  |          | _    |                 | 340  | _        | — <sup>1</sup> |       |

| LE to Outputs          |                  | 4.5 |      | 45•  | l —      | 50∙  | -               | 68•  |          | 75∙            |       |

|                        |                  | 6   | _    | 38   | _        | l —  | _               | 58   | _        | -              |       |

|                        |                  | 2   |      | 175  | _        |      |                 | 265  | _        | -              | 113   |

| E to Outputs           |                  | 4.5 | _    | 35∙  | _        | 40•  | _               | 53•  | -        | 60•            |       |

|                        |                  | 6   | l –  | 30   |          | l –  | _               | 45   | -        |                |       |

| Output Transition Time | t <sub>TLH</sub> | 2   |      | 75   | _        | T —  | _               | 110  | _        | —              |       |

|                        |                  | 4.5 | _    | 15   | <u> </u> | 15   |                 | 22   | -        | 22             | İ     |

|                        |                  | 6   | l –  | 13   | -        |      |                 | 19   | <u> </u> |                |       |

| Input Capacitance      | Cı               | 1 – | T    | 10   | T        | 10   | T —             | 10   |          | 10             | pF    |

#### Burn-In Test-Circuit Connections (Use Static II for /3A burn-in and Dynamic for Life Test.)

|                |            | STATIC BURN-I | NI                       | STATIC BURN-IN II    |            |                      |  |  |

|----------------|------------|---------------|--------------------------|----------------------|------------|----------------------|--|--|

| Static         | OPEN       | GROUND        | V <sub>cc</sub> (6V)     | OPEN                 | GROUND     | V <sub>cc</sub> (6V) |  |  |

| CD54HC/HCT4514 | 4-11,13-20 | 1-3,12,21-23  | 24                       | 4-11,13-20           | 12         | 1-3,21-24            |  |  |

|                |            |               |                          |                      | OSCILLATOR |                      |  |  |

| Dynamic        | OPEN       | GROUND        | 1/2 V <sub>cc</sub> (3V) | V <sub>cc</sub> (6V) | 50 kHz     | 25 kHz               |  |  |

| CD54HC/HCT4514 |            | 2,3,12        | 4-11,13-20               | 21,22,24             | 1          | 23                   |  |  |

NOTE: Each pin except Vcc and Gnd will have a resistor of 2k-47k ohms.

# 4-to-16-Line Decoder with Input Latches

# CD54HC4515/3A CD54HCT4515/3A

The RCA CD54HC4515 and CD54HCT4515 are high-speed silicon-gate devices consisting of a 4-bit strobed latch and a 4-to-16-line decoder. The selected output is enabled by a low on the enable input (Ē). A high on Ē inhibits selection of any output. Demultiplexing is accomplished by using the Ē input as the data input and the select inputs (A0-A3) as addresses. This Ē input also serves as a chip select when these devices are cascaded.

When Latch Enable (LE) is high the output follows changes in the inputs. When LE is low the output is isolated from changes in the input and remains at the level (low) it had before the latches were enabled. These devices, enhanced versions of the equivalent CMOS types, can drive 10 LSTTL loads.

#### **Package Specifications**

See Section 11, Fig. 15

**FUNCTIONAL DIAGRAM**