DESCRIPTION — The SN54LS/74LS259 is a high-speed 8-Bit Addressable Latch designed for general purpose storage applications in digital systems. It is a multifunctional device capable of storing single line data in eight addressable latches, and also a 1-of-8 decoder and demultiplexer with active HIGH outputs. The device also incorporates an active LOW common Clear for resetting all latches, as welf as, an active LOW Enable.

- SERIAL-TO-PARALLEL CONVERSION

- EIGHT BITS OF STORAGE WITH OUTPUT OF EACH BIT AVAILABLE

- RANDOM (ADDRESSABLE) DATA ENTRY

- ACTIVE HIGH DEMULTIPLEXING OR DECODING CAPABILITY

- EASILY EXPANDABLE

- COMMON CLEAR

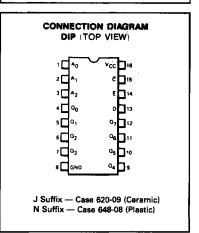

| PIN NAMES                        | •                               | LOADIN   | G (Note a)  |

|----------------------------------|---------------------------------|----------|-------------|

|                                  |                                 | HIGH     | LOW         |

| Ag. A1. A2                       | Address Inputs                  | 0.5 U.L. | 0.25 U.L.   |

| D E                              | Data Input                      | 0.5 U.L. | 0.25 U.L.   |

| Ē                                | Enable (Active LOW) Input       | 1.0 U.L. | 0.5 U.L.    |

| Ē                                | Clear (Active LOW) Input        | 0.5 U.L. | 0.25 U.L.   |

| O <sub>O</sub> to O <sub>7</sub> | Parallel Latch Outputs (Note b) | 10 U.L.  | 5(2.5) U.L. |

#### NOTES:

- a. 1 TTL Unit Load (U.L.) = 40 µA HIGH/1.6 mA LOW.

- b. The Output LOW drive factor is 2.5 U.L. for Militery (54) and 5 U.L. for Commercial (74) Temperature Ranges.

## SN54/74LS259

### 8-BIT ADDRESSABLE LATCH

LOW POWER SCHOTTKY

### SN54/74LS259

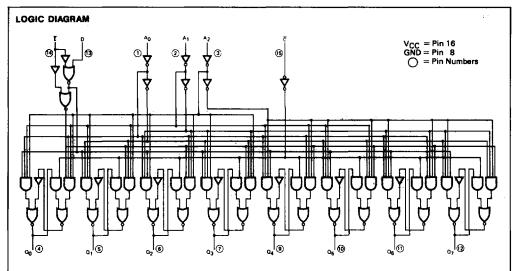

FUNCTIONAL DESCRIPTION — The SN54LS/74LS259 has four modes of operation as shown in the mode selection table. In the addressable latch mode, data on the Data line (D) is written into the addressed latch. The addressed latch will follow the data input with all non-addressed latches remain in their previous states. In the memory mode, all latches remain in their previous state and are unaffected by the Data or Address inputs.

In the one-of-eight decoding or demultiplexing mode, the addressed output will follow the state of the D input with all other inputs in the LOW state. In the clear mode all outputs are LOW and unaffected by the address and data inputs.

When operating the SN54LS/74LS259 as an addressable latch, changing more than one bit of the address could impose a transient wrong address. Therefore, this should only be done while in the memory mode.

The truth table below summarizes the operations.

### MODE SELECTION

# TRUTH TABLE

|      | c | MODE                      |

|------|---|---------------------------|

| LH   | н | Addressable Latch         |

| H  t | н | Memory                    |

| L 1  | 니 | Active HIGH Eight-Channel |

|      |   | Demultiplexer             |

| HI   | 니 | Clear                     |

|          |   |   |    |    |                |                  | F              | PRESEN | IT OUTP          | UTST | ATES           |      |    |             |

|----------|---|---|----|----|----------------|------------------|----------------|--------|------------------|------|----------------|------|----|-------------|

| ĉ        | Ē | D | Αo | Αţ | A <sub>2</sub> | Qo               | Q <sub>1</sub> | 02     | Qз               | 04   | Q <sub>5</sub> | Q6   | Ω7 | MODE        |

| L        | Н | х | х  | х  | х              | L                |                | L      | L                | L    | L              | L    | L  | Clear       |

| L        | Ł | L | L  | Ļ  | L              | L                | L              | L      | L                | L    | L              | Ĺ    | Ē  | Demultiplex |

| L        | L | Н | L  | Ł  | L              | H                | L              | L      | L                | L    | L              | L    | L  |             |

| L        | L | L | н  | L  | L              | L                | L              | Ļ      | L                | L    | L              | L    | L  |             |

| L        | L | Н | Н  | L  | L              | l                | Н              | L      | Ł                | L    | L              | L    | L  |             |

| •        | • | • |    | ٠  |                |                  |                |        | •                |      |                |      |    |             |

| •        | • | • |    | •  |                |                  |                |        | •                |      |                |      |    |             |

| •        | • | • |    | •  |                |                  |                |        | •                |      |                |      |    |             |

| •        | • | ٠ |    | •  |                |                  |                |        | •                |      |                |      |    |             |

| •        | • | • |    | •  |                |                  |                |        | •                |      |                |      |    |             |

| ᆫ        | L | Н | н  |    | Н              | L                | L              | L      | L                | L    | L              | L    | н  |             |

| Н        | Н | х | х  | Х  | Х              | Q <sub>N-1</sub> |                |        |                  |      |                |      | -  | Memory      |

| Н        | 1 | 1 | L  | L  | L              | L                | QN-1           | QN-1   | Q <sub>N-1</sub> |      |                |      |    | Addressable |

| Н        | L | Н | L  | L  | L              | H                |                | QN-1   |                  |      |                |      | -  | Latch       |

| Н        | L | L | Н  | L  | i.             | Q <sub>N-1</sub> |                | QN-1   |                  |      |                |      |    |             |

| Н        | L | Н | Н  | L  | Ł              | Q <sub>N-1</sub> | н              | QN-1   |                  |      |                |      |    |             |

| •        | • | • |    | •  |                | ļ                |                |        | •                |      |                |      |    |             |

| •        | • | • |    | •  |                |                  |                |        | •                |      |                |      |    |             |

| •        | • | • |    | •  |                |                  |                |        | •                |      |                |      |    |             |

| •        | • | • |    | •  |                |                  |                |        | •                |      |                |      |    |             |

| <b>!</b> | • | • |    | •  |                | _                |                |        | •                |      |                |      |    |             |

| н        | L | L | Н  | Н  | н              | Q <sub>N-1</sub> |                |        |                  |      | -              | QN-1 | L  |             |

| Н        | L | Н | Н  | Н  | Н              | Q <sub>N-1</sub> |                |        |                  |      |                | QN-1 | Н  |             |

X = Don't Care Condition

L = LOW Voltage Level H = HIGH Voltage Level

Q<sub>N-1</sub> = Previous Output State

### GUARANTEED OPERATING RANGES

| SYMBOL | PARAMETER                           |          | MIN         | TYP        | MÁX         | UNIT |

|--------|-------------------------------------|----------|-------------|------------|-------------|------|

| Vcc    | Supply Voltage                      | 54<br>74 | 4.5<br>4.75 | 5.0<br>5.0 | 5.5<br>5.25 | ٧    |

| TA     | Operating Ambient Temperature Range | 54<br>74 | 65<br>0     | 25<br>25   | 125<br>70   | °C   |

| ЮН     | Output Current — High               | 54,74    |             |            | -0.4        | mA   |

| lOL    | Output Current — Low                | 54<br>74 |             |            | 4.0<br>8.0  | mA   |

### SN54/74L8259

DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE (unless otherwise specified)

| OVERDO:         | PARAMETER                 |       | LIMITS    |       |      | LINUTO                      | TEST COMPETIONS                  |                                     |  |

|-----------------|---------------------------|-------|-----------|-------|------|-----------------------------|----------------------------------|-------------------------------------|--|

| SYMBOL          |                           |       | MIN TYP I |       | MAX  | UNITS                       | TEST CONDITIONS                  |                                     |  |

| VIH             | Input HIGH Voltage        | 2.0   |           |       | ٧    | Guaranteed in<br>All Inputs | put HIGH Voltage for             |                                     |  |

|                 |                           | 54    |           |       | 0.7  | .,                          | Guaranteed Input LOW Voltage for |                                     |  |

| V <sub>IL</sub> | Input LOW Voltage 74      |       |           |       | 0.8  | V                           | All Inputs                       |                                     |  |

| VIK             | Input Clamp Diode Voltage | je    |           | -0.65 | -1.5 | <b>v</b>                    | VCC = MIN, IIN = -18 mA          |                                     |  |

|                 |                           | 54    | 2.5       | 3.5   |      | ٧                           | VCC = MIN, IOH = MAX, VIN =      |                                     |  |

| Vон             | Output HIGH Voltage       | 74    | 2.7       | 3.5   |      | ٧                           | or VIL per Trut                  | Table                               |  |

|                 |                           | 54,74 |           | 0.25  | 0.4  | ٧                           | IOL = 4.0 mA                     | VCC = VCC MIN,                      |  |

| VOL             | Output LOW Voltage        | 74    |           | 0.35  | 0.5  | ٧                           | IOL = 8.0 mA                     | VIN = VIL or VIH<br>per Truth Table |  |

|                 |                           |       |           | [     | 20   | μΑ                          | VCC = MAX, V                     | / <sub>IN</sub> = 2.7 ∨             |  |

| ЧН              | Input HIGH Current        |       |           | 0.1   | mA   | VCC = MAX, V                | /IN = 7.0 V                      |                                     |  |

| կլ_             | Input LOW Current         |       |           | -0.4  | mA   | VCC = MAX, V                | /IN = 0.4 V                      |                                     |  |

| ios             | Short Circuit Current     | -20   |           | -100  | mA   | V <sub>CC</sub> = MAX       |                                  |                                     |  |

| lcc             | Power Supply Current      | ;-    |           | 36    | mA   | V <sub>CC</sub> = MAX       |                                  |                                     |  |

AC CHARACTERISTICS:  $T_A = 25$ °C,  $V_{CC} = 5.0 \text{ V}$

| SYMBOL      |                                   | [   | LIMITS |     | UNITS | CONDITIONS             |  |

|-------------|-----------------------------------|-----|--------|-----|-------|------------------------|--|

|             | PARAMETER                         | MIN | TYP    | MAX | UNITS |                        |  |

| tPLH        | Turn-Off Delay, Enable to Output  | 1   | 22     | 35  | ns    |                        |  |

| <b>PHL</b>  | Turn-On Delay, Enable to Output   |     | 15     | 24  | ns    |                        |  |

| †PLH        | Turn-Off Delay, Data to Output    |     | 20     | 32  | ns    |                        |  |

| <b>TPHL</b> | Turn-On Delay, Data to Output     |     | 13     | 21  | ns    | C <sub>L</sub> = 15 pF |  |

| tPLH        | Turn-Off Delay, Address to Output |     | 24     | 38  | ns    | · ·                    |  |

| tPHL .      | Turn-On Delay, Address to Output  |     | 18     | 29  | ns    |                        |  |

| tPHL        | Turn-On Delay, Clear to Output    |     | 17     | 27  | กร    |                        |  |

AC SETUP REQUIREMENTS:  $T_A = 25$ °C,  $V_{CC} = 5.0 \text{ V}$

| SYMBOL | DADAMETER                    |     | LIMITS | 1   | LIMITO |

|--------|------------------------------|-----|--------|-----|--------|

|        | PARAMETER                    |     | TYP    | MAX | UNITS  |

| ts     | Input Setup Time             | 20  |        |     | ns     |

| w      | Pulse Width, Clear or Enable | 15  |        |     | ns     |

| th     | Hold Time, Data              | 5.0 |        |     | ns     |

| th     | Hold Time, Address           | 20  |        |     | ns     |

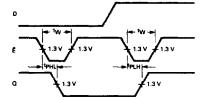

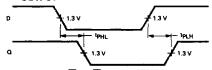

### **AC WAVEFORMS**

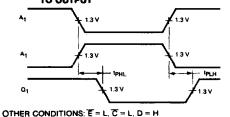

Fig. 1 TURN-ON AND TURN-OFF DELAYS, ENABLE TO OUTPUT AND ENABLE PULSE WIDTH

OTHER CONDITIONS: C = H, A = STABLE

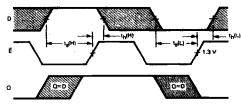

Fig. 2 TURN-ON AND TURN-OFF DELAYS, DATA TO OUTPUT

OTHER CONDITIONS: E = L, C = H, A = STABLE

Fig. 3 TURN-ON AND TURN-OFF DELAYS, ADDRESS TO OUTPUT

Fig. 4 SETUP AND HOLD TIME, DATA TO ENABLE

OTHER CONDITIONS: T = H, A = STABLE

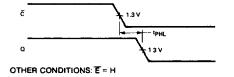

Fig. 5 TURN-ON DELAY, CLEAR TO OUTPUT

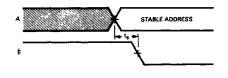

Fig. 6 SETUP TIME, ADDRESS TO ENABLE (SEE NOTES 1 AND 2)

OTHER CONDITIONS: C = H

### NOTES:

- The Address to Enable Setup Time is the time before the HIGH-to-LOW Enable transition that the Address must be stable so that the correct latch is addressed and the other latches are not affected.

- 2. The shaded areas indicate when the inputs are permitted to change for predictable output performance.