## TYPES SN54S226, SN74S226 4-BIT PARALLEL LATCHED BUS TRANCEIVERS

OCTOBER 1976-REVISED DECEMBER 1983

- Universal Transceivers for Implementing System Bus Controllers

- Dual-Rank 4-Bit Transparent Latches Provide:

- Exchange of Data Between 2 Buses In One Clock Pulse

- Bus-to-Bus Isolation

- Rapid Data Transfer

- Full Storage Capability

- Hysteresis at Data Inputs Enhances Noise Rejection

- Separate Output-Control Inputs Provide Independent Enable/Disable for Either Bus Output

- 3-State Outputs Drive Bus Lines Directly

### description

These high-performance Schottky TTL quadruple bus transceivers employ dual-rank bidirectional four-bit transparent latches and feature three-state outputs designed specifically for driving highly-capacitive or relatively low-impedance loads. The bus-management functions implemented and the high-impedance controls offered provide the designer with a controller/transceiver that interfaces and drives system bus-organized lines directly. They are particularly attractive for implementing:

Bidirectional bus transceivers Data-bus controllers SN54S226 ... J OR W PACKAGE SN74S226 ... D, J OR N PACKAGE (TOP VIEW)

| GBA 🛛 1       | U <sub>16</sub> | □vcc        |

|---------------|-----------------|-------------|

| S1 🔲 2        | 15              | GAB         |

| A1 <b>□</b> 3 | 14              | <b>□</b> S2 |

| A2 🛮 4        | 13              | ]B1         |

| A3 🛮 5        | 12              | ∏B2         |

| <b>A4</b> ☐ 6 | 11              | <b>□</b> B3 |

| СВА 🛮 7       | 10              | B4          |

| GND Da        | 9               | Посав       |

SN54S226 ... FK PACKAGE SN74S226 ... FN PACKAGE (TOP VIEW)

NC - No internal correction

The bus-management functions, under control of the function-select (S1, S2) inputs, provide complete data integrity for each of the four modes described in the function table. Directional transparency provides for routing data from or to either bus, and the dual store and dual readout capabilities can be used to perform the exchange of data between the two bus lines in the equivalent of a single clock pulse. Storage of data is accomplished by selecting the latch function, setting up the data, and taking the appropriate strobe input low. As long as the strobe is held high, the data is latched for the selected function. Further control is offered through the availability of independent output controls that can be used to enable or disable the outputs as shown in the output-control function table, regardless of the latch function in process. Store operations can be performed with the outputs disabled to a high impedance (Hi-Z). In the Hi-Z state the inputs/outputs neither load nor drive the bus lines significantly. The p-n-p inputs feature typically 400 millivolts of hysteresis to enhance noise rejection.

#### **BUS-MANAGEMENT FUNCTION TABLE**

|    | MODE STROBES LATCHES  GAB GBA LATCHES |      |     | B-T   |       | OPERATION |       |                      |       |                      |

|----|---------------------------------------|------|-----|-------|-------|-----------|-------|----------------------|-------|----------------------|

| S2 | _S1                                   | UAB  | UBA | 1 2   |       | 1         | 2     |                      |       |                      |

|    |                                       | х    | L   | 1     | +     | Trans     | Trans | Pass B to A          |       |                      |

|    |                                       | L_^_ | н   | Latch | Trans | Latch     | Trans | Read out stored data |       |                      |

| L  | Н                                     | X    | X   | Latch | Trans | Latch     | Trans | Read out stored data |       |                      |

| н  |                                       | L    |     | Trans | Trans | 1         | T     | Pass A to B          |       |                      |

| п  | _                                     | н    | X   | Latch | Trans | Latti     | Latch | Latch                | Trans | Read out stored data |

| н  | Н                                     | L    | L   | Trans | Latch | Trans     | Latch | Read in both buses   |       |                      |

|    | н                                     | н    | н   | Latch | Latch | Latch     | Latch | Store bus data       |       |                      |

H = high level

L = low level

X = irrelevant

Latch = latched

Trans = transparent

PRODUCTION DATA

This document contains information current as of publication data. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

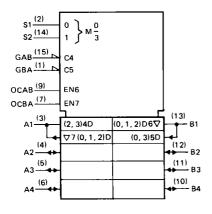

## logic symbol<sup>†</sup>

<sup>1</sup>This symbol is in accordance with IEEE Std 91/ANSI Y32.14 and current discussions in IEC and IEEE.

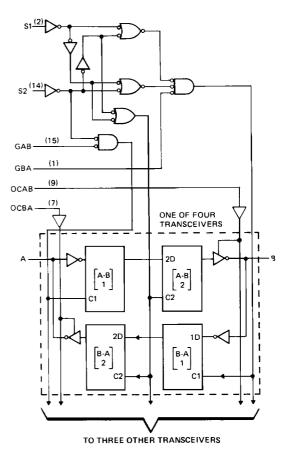

## logic diagram (positive logic)

Pin numbers shown on logic notation are for D. J or N packages

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage, VCC (see Note 1)      |         |        |      |    |  |  |  |  |  | 7 V                                |

|---------------------------------------|---------|--------|------|----|--|--|--|--|--|------------------------------------|

| Input voltage                         |         |        |      |    |  |  |  |  |  | 5.5 V                              |

| Off-state output voltage              |         |        |      |    |  |  |  |  |  | 5.5 V                              |

| Operating free-air temperature range: | SN54S22 | 6 (see | Note | 2) |  |  |  |  |  | -55°C to 125°C                     |

|                                       | SN74S22 | 6      |      |    |  |  |  |  |  | . 0°C to 70°C                      |

| Storage temperature range             |         |        |      |    |  |  |  |  |  | $-65^{\circ}$ C to $150^{\circ}$ C |

NOTES: 1. Voltage values are with respect to network ground terminal.

An SN54S226 in the J package operating at temperatures above 113°C requires a heat-sink that provides a thermal resistance from

case to free air, R<sub>θCA</sub>, of not more than 48°C/W.

## recommended operating conditions

|                                                 |           | s   | N54S22 | :6  | S    | UNIT  |      |          |

|-------------------------------------------------|-----------|-----|--------|-----|------|-------|------|----------|

|                                                 |           | MIN | NOM    | MAX | MIN  | NOM   | MAX  | - I      |

| Supply voltage, VCC                             |           | 4.5 | 5      | 5.5 | 4.75 | 5     | 5.25 | γ        |

| High-level output voltage, VOH                  |           |     |        | 5.5 |      |       | 5.5  | V        |

| High-level output current, IOH                  |           |     | -6.5   |     |      | -10.3 | mΑ   |          |

| Width of strobe pulse                           |           | 30  |        |     | 20   |       |      | ns       |

|                                                 | To Strobe | 30† | 30†    |     | 20↑  |       |      | ns       |

| Setup time, t <sub>su</sub>                     | To Select | 30  |        |     | 20   | -     |      |          |

|                                                 | To Strobe | 01  |        |     | 0↑   |       |      | ns       |

| Hold time, th                                   | To Select | 0   |        |     | 0    |       |      | <u> </u> |

| Operating free-air temperature, TA (see Note 2) |           | -55 |        | 125 | 0    |       | 70   | °C       |

<sup>†</sup> The arrow indicates that the low-to-high transition of the strobe input is used for reference.

# electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|      | PARAMETER                              |                  | TEST CONDITIONS†                                 | MIN | TYP‡ | MAX   | UNIT |

|------|----------------------------------------|------------------|--------------------------------------------------|-----|------|-------|------|

| VIH  | High-level input voltage               |                  |                                                  | 2   |      |       | ٧    |

| VIL  | Low-level input voltage                |                  |                                                  |     |      | 0.8   | ٧    |

| VIK  | Input clamp voltage                    |                  | V <sub>CC</sub> = MIN, I <sub>1</sub> = -18 mA   |     |      | -1.2  | ٧    |

|      |                                        | SN54S226         | VCC = MIN, VIH = 2 V,                            | 2.4 | 3.3  |       | ∫v   |

| Vон  | High-level output voltage              | SN74S226         | VIL = 0.8 V, IOH = MAX                           | 2.4 | 2.9  |       |      |

|      |                                        |                  | VCC = MIN, VIH = 2 V,                            |     |      | 0.5   | l v  |

| VOL  | Low-level output voltage               |                  | V <sub>IL</sub> = 0.8 V, I <sub>OL</sub> = 15 mA |     |      |       |      |

|      | Off-state output current,              |                  | VCC = MAX, VIH = 2 V,                            |     | 100  | μA    |      |

| IOZH | high-level voltage applied             |                  | V <sub>O</sub> = 2.4 V                           |     |      |       |      |

|      | Off-state output current,              |                  | VCC = MAX, VIH = 2 V,                            |     |      | -250  | μA   |

| OZL  | low-level voltage applied              |                  | V <sub>O</sub> = 0.5 V                           |     |      |       |      |

| lı . | Input current at maximum input voltage |                  | V <sub>CC</sub> = MAX, V <sub>I</sub> = 5.5 V    |     |      | 1     | mA   |

| ήн   | High-level input current               |                  | V <sub>CC</sub> = MAX, V <sub>1</sub> = 2.7 V    |     |      | 100   | μА   |

|      |                                        | GAB, GBA         | VCC = MAX, VI = 0.5 V                            |     |      | -0.38 |      |

| 11L  | Low-level input current                | All other inputs | <b>↑</b> (€ = MAX; <b>↑</b> 1 €:5 <b>↑</b>       |     |      | -1.6  |      |

| los  | Short-circuit output current §         |                  | V <sub>CC</sub> = MAX                            | -50 |      | _180  |      |

| Icc  | Supply current                         |                  | V <sub>CC</sub> = MAX, See Note 3                |     | 125  | 185   | mA   |

<sup>†</sup>For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.

<sup>‡</sup>All typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25°C.

<sup>§</sup>Not more than one output should be shorted at a time and duration of the short-circuit should-not exceed one second.

NOTES: 2. An SN545226 in the J package operating at temperatures above 113°C requires a heat-sink that provides a thermal resistance from case to free air,  $R_{\theta CA}$ , of not more than 48°C/W.

<sup>3.</sup> ICC is measured with all inputs (and outputs) grounded.

## switching characteristics, $V_{CC} = 5 \text{ V}$ , $T_A = 25^{\circ} \text{C}$

| PARAMETER    | FROM<br>(INPUT) | TO<br>(OUTPUT) | TEST COM                | IDITIONS             | MIN        | ТҮР | мах | UNIT |    |    |

|--------------|-----------------|----------------|-------------------------|----------------------|------------|-----|-----|------|----|----|

| tPLH         |                 |                |                         |                      |            | 20  | 30  | ns   |    |    |

| tPHL         | A or B          | B or A         |                         |                      |            | 15  | 30  |      |    |    |

| tPLH         |                 |                | C <sub>L</sub> = 50 pF, |                      |            |     | 25  | 37   | Ţ  |    |

| tPHL         | Select          | Any            |                         | $R_L = 280 \Omega$ , |            | 19  | 30  | ns   |    |    |

| tPLH         | Strobe GBA      | A or B         | A or B                  | A or B               | See Note 4 |     |     | 25   | 37 | Γ  |

| tPHL         | or GAB          |                |                         |                      |            |     |     | 19   | 30 | ns |

| tPZH         | Output Control  |                | 1                       |                      |            | 12  | 20  |      |    |    |

| tPZL         | OCBA or OCAB    | A or B         |                         |                      |            | 12  | 20  | ns   |    |    |

|              | Output Control  |                | CL = 5 pF,              | $R_1 = 280 \Omega$   |            | 10  | 15  |      |    |    |

| tPHZ<br>tPLZ | OCBA or OCAB    | A or B         | See Note 4              |                      |            | 10  | 15  | ns   |    |    |

$t_{PLH} \equiv propagation delay time, low-to-high-level output$

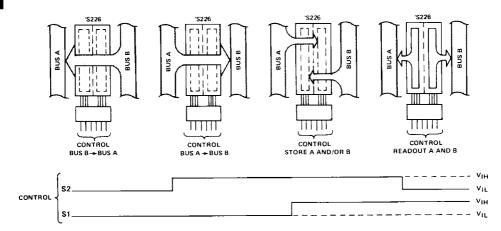

#### applications

The following examples demonstrate four fundamental bus-management functions that can be performed with the '\$226. Exchange of data on the two bus lines can be accomplished with a single high-to-low transition at \$2 when \$1 is high.

tpHL = propagation delay time, high to-low level

tPZH :- output enable time to high level

$t_{PZL} \equiv output$  enable time to low level

tpHZ ≅output disable time from high level

tpLZ ≡ output disable time from low level

NOTE 4: See General Information Section for load circuits and voltage waveforms