### SN74ALVC74 DUAL POSITIVE-EDGE-TRIGGERED D-TYPE FLIP-FLOP WITH CLEAR AND PRESET

SCES109E - JULY 1997 - REVISED JANUARY 1999

- EPIC™ (Enhanced-Performance Implanted CMOS) Submicron Process

- Package Options Include Plastic Small-Outline (D), Thin Very Small-Outline (DGV), and Thin Shrink Small-Outline (PW) Packages

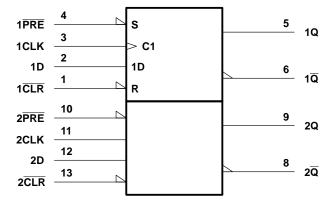

#### (TOP VIEW) 1CLR [ □ v<sub>cc</sub> 1D [ 13 2 CLR 2 1CLK [] 3 12 ¶ 2D 1PRE 14 11 2CLK 1Q [ 10 1 2 PRE 1Q [ 9 2Q 6 8 2 Q GND

D, DGV, OR PW PACKAGE

#### description

This dual positive-edge-triggered D-type flip-flop is designed for 1.65-V to 3.6-V V<sub>CC</sub> operation.

A low level at the preset (PRE) or clear (CLR) inputs sets or resets the outputs, regardless of the levels of the other inputs. When PRE and CLR are inactive (high), data at the data (D) input meeting the setup time requirements is transferred to the outputs on the positive-going edge of the clock pulse. Clock triggering occurs at a voltage level and is not directly related to the rise time of the clock pulse. Following the hold-time interval, data at the D input may be changed without affecting the levels at the outputs.

The SN74ALVC74 is characterized for operation from -40°C to 85°C.

#### **FUNCTION TABLE**

|     | INP | OUTI       | PUTS |       |                           |

|-----|-----|------------|------|-------|---------------------------|

| PRE | CLR | CLK        | D    | Q     | Q                         |

| L   | Н   | Х          | Х    | Н     | L                         |

| Н   | L   | X          | Χ    | L     | Н                         |

| L   | L   | X          | Χ    | н†    | H <sup>†</sup>            |

| Н   | Н   | $\uparrow$ | Н    | Н     | L                         |

| Н   | Н   | $\uparrow$ | L    | L     | Н                         |

| Н   | Н   | L          | Χ    | $Q_0$ | $\overline{\mathtt{Q}}_0$ |

<sup>†</sup> This configuration is unstable; that is, it does not persist when PRE or CLR returns to its inactive (high) level.

### logic symbol†

<sup>†</sup> This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

EPIC is a trademark of Texas Instruments Incorporated

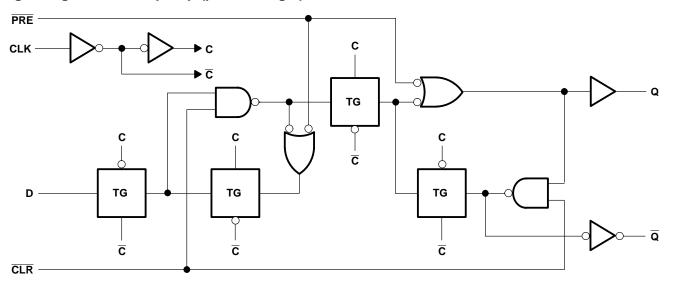

#### logic diagram, each flip-flop (positive logic)

## absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage range, V <sub>CC</sub>                              | –0.5 V to 4.6 V                  |

|--------------------------------------------------------------------|----------------------------------|

| Input voltage range, V <sub>I</sub> (see Note 1)                   | –0.5 V to 4.6 V                  |

| Output voltage range, VO (see Notes 1 and 2)                       | 0.5 V to V <sub>CC</sub> + 0.5 V |

| Input clamp current, I <sub>IK</sub> (V <sub>I</sub> < 0)          |                                  |

| Output clamp current, I <sub>OK</sub> (V <sub>O</sub> < 0)         | –50 mA                           |

| Continuous output current, IO                                      | ±50 mA                           |

| Continuous current through V <sub>CC</sub> or GND                  | ±100 mA                          |

| Package thermal impedance, θ <sub>JA</sub> (see Note 3): D package | 127°C/W                          |

| DGV package                                                        | 182°C/W                          |

| PW package                                                         | 170°C/W                          |

| Storage temperature range, T <sub>stg</sub>                        | –65°C to 150°C                   |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- NOTES: 1. The input negative-voltage and output voltage ratings may be exceeded if the input and output current ratings are observed.

- 2. This value is limited to 4.6 V maximum.

- 3. The package thermal impedance is calculated in accordance with JESD 51.

PRODUCT PREVIEW

### SN74ALVC74 DUAL POSITIVE-EDGE-TRIGGERED D-TYPE FLIP-FLOP WITH CLEAR AND PRESET

SCES109E - JULY 1997 - REVISED JANUARY 1999

#### recommended operating conditions (see Note 4)

|                 |                                    |                                              | MIN                    | MAX                  | UNIT |  |

|-----------------|------------------------------------|----------------------------------------------|------------------------|----------------------|------|--|

| Vcc             | Supply voltage                     |                                              | 1.65                   | 3.6                  | V    |  |

|                 |                                    | V <sub>CC</sub> = 1.65 V to 1.95 V           | 0.65 × V <sub>CC</sub> |                      | V    |  |

| ٧ıH             | High-level input voltage           | $V_{CC} = 2.3 \text{ V to } 2.7 \text{ V}$   | 1.7                    |                      |      |  |

|                 |                                    | $V_{CC} = 2.7 \text{ V to } 3.6 \text{ V}$   | 2                      |                      |      |  |

|                 |                                    | $V_{CC} = 1.65 \text{ V to } 1.95 \text{ V}$ |                        | $0.35 \times V_{CC}$ |      |  |

| ٧ <sub>IL</sub> | Low-level input voltage            | $V_{CC} = 2.3 \text{ V to } 2.7 \text{ V}$   |                        | 0.7                  | ٧    |  |

|                 |                                    | $V_{CC} = 2.7 \text{ V to } 3.6 \text{ V}$   |                        | 0.8                  |      |  |

| ٧ı              | Input voltage                      |                                              | 0                      | VCC                  | V    |  |

| ٧o              | Output voltage                     |                                              | 0                      | Vcc                  | V    |  |

|                 |                                    | V <sub>CC</sub> = 1.65 V                     |                        | -4                   |      |  |

| lau             | High level output gurrent          | V <sub>CC</sub> = 2.3 V                      |                        | -12                  | mA   |  |

| ІОН             | High-level output current          | V <sub>CC</sub> = 2.7 V                      |                        | -12                  |      |  |

|                 |                                    | V <sub>CC</sub> = 3 V                        |                        | -24                  |      |  |

|                 |                                    | V <sub>CC</sub> = 1.65 V                     |                        | 4                    |      |  |

| la.             | Lavidaval autout avenat            | V <sub>CC</sub> = 2.3 V                      |                        | 12                   |      |  |

| IOL             | Low-level output current           | V <sub>CC</sub> = 2.7 V                      |                        | 12                   | mA   |  |

|                 | V <sub>CC</sub> = 3 V              |                                              |                        | 24                   |      |  |

| Δt/Δν           | Input transition rise or fall rate |                                              |                        | 10                   | ns/V |  |

| TA              | Operating free-air temperature     |                                              | -40                    | 85                   | °C   |  |

NOTE 4: All unused inputs of the device must be held at V<sub>CC</sub> or GND to ensure proper device operation. Refer to the TI application report, *Implications of Slow or Floating CMOS Inputs*, literature number SCBA004.

# electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

| PARAMETER      | TEST CONDITIONS                                                | v <sub>cc</sub> | MIN                  | TYPT MA | X UNIT |

|----------------|----------------------------------------------------------------|-----------------|----------------------|---------|--------|

|                | $I_{OH} = -100 \mu\text{A}$                                    | 1.65 V to 3.6 V | V <sub>CC</sub> -0.2 | 2       |        |

|                | $I_{OH} = -4 \text{ mA}$                                       | 1.65 V          | 1.2                  |         |        |

|                | $I_{OH} = -6 \text{ mA}$                                       | 2.3 V           | 2                    |         |        |

| Voн            |                                                                | 2.3 V           | 1.7                  |         | V      |

|                | I <sub>OH</sub> = -12 mA                                       | 2.7 V           | 2.2                  |         |        |

|                |                                                                | 3 V             | 2.4                  |         |        |

|                | I <sub>OH</sub> = -24 mA                                       | 3 V             | 2                    |         |        |

|                | I <sub>OL</sub> = 100 μA                                       | 1.65 V to 3.6 V |                      | (       | .2     |

|                | I <sub>OL</sub> = 4 mA                                         | 1.65 V          |                      | 0.      | 15     |

| W = .          | I <sub>OL</sub> = 6 mA                                         | 2.3 V           |                      | (       | .4 V   |

| VOL            | In. 42 mA                                                      | 2.3 V           |                      | (       | .7 V   |

|                | I <sub>OL</sub> = 12 mA                                        | 2.7 V           |                      | (       | .4     |

|                | I <sub>OL</sub> = 24 mA                                        | 3 V             |                      | 0.      | 55     |

| lı             | V <sub>I</sub> = V <sub>CC</sub> or GND                        | 3.6 V           |                      | :       | -5 μA  |

| Icc            | $V_I = V_{CC}$ or GND, $I_O = 0$                               | 3.6 V           |                      |         | 20 μΑ  |

| ∆lcc           | One input at $V_{CC}$ – 0.6 V, Other inputs at $V_{CC}$ or GND | 3 V to 3.6 V    |                      | 7       | 50 μΑ  |

| C <sub>i</sub> | $V_I = V_{CC}$ or GND                                          | 3.3 V           |                      |         | pF     |

<sup>†</sup> All typical values are at  $V_{CC} = 3.3 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ .

## SN74ALVC74 DUAL POSITIVE-EDGE-TRIGGERED D-TYPE FLIP-FLOP WITH CLEAR AND PRESET

SCES109E - JULY 1997 - REVISED JANUARY 1999

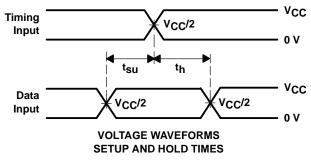

# timing requirements over recommended operating free-air temperature range (unless otherwise noted) (see Figures 1 through 3)

|                 |                 |                     | V <sub>CC</sub> = | 1.8 V | V <sub>CC</sub> = | 2.5 V<br>2 V | VCC = | 2.7 V | V <sub>CC</sub> = | 3.3 V<br>3 V | UNIT |  |

|-----------------|-----------------|---------------------|-------------------|-------|-------------------|--------------|-------|-------|-------------------|--------------|------|--|

|                 |                 |                     | MIN               | MAX   | MIN               | MAX          | MIN   | MAX   | MIN               | MAX          |      |  |

| fclock          | Clock frequency |                     |                   |       |                   |              |       |       |                   |              | MHz  |  |

| _               | Pulse duration  | PRE or CLR low      |                   |       |                   |              |       |       |                   |              | ns   |  |

| t <sub>W</sub>  | Puise duration  | CLK high or low     |                   |       |                   |              |       |       |                   |              | 115  |  |

|                 | Catum time      | Data before CLK↑    |                   |       |                   |              |       |       |                   |              | no   |  |

| t <sub>su</sub> | Setup time      | PRE or CLR inactive |                   |       |                   |              |       |       |                   |              | ns   |  |

| th              | Hold time       | Data after CLK↑     |                   |       |                   |              |       |       |                   |              | ns   |  |

# switching characteristics over recommended operating free-air temperature range (unless otherwise noted) (see Figures 1 through 3)

| PARAMETER        | FROM TO (INPUT) (OUTPUT) |                       | V <sub>CC</sub> = 1.8 V | V <sub>CC</sub> = 2.5 V<br>± 0.2 V | V <sub>CC</sub> = 2.7 V | V <sub>CC</sub> = 3.3 V<br>± 0.3 V | UNIT |

|------------------|--------------------------|-----------------------|-------------------------|------------------------------------|-------------------------|------------------------------------|------|

|                  | (INFOT)                  | (OUTFUT)              | TYP                     | MIN MAX                            | MIN MAX                 | MIN MAX                            |      |

| f <sub>max</sub> |                          |                       |                         |                                    |                         |                                    | MHz  |

| + .              | CLK                      | $Q$ or $\overline{Q}$ |                         |                                    |                         |                                    | ns   |

| <sup>t</sup> pd  | PRE or CLR               | Q OF Q                |                         |                                    |                         |                                    | 115  |

## operating characteristics, $T_A = 25^{\circ}C$

| PARAMETER                                                   |  | TEST CONDITIONS |            | V <sub>CC</sub> = 1.8V | V <sub>CC</sub> = 2.5 V | V <sub>CC</sub> = 3.3 V | UNIT |

|-------------------------------------------------------------|--|-----------------|------------|------------------------|-------------------------|-------------------------|------|

|                                                             |  |                 |            | TYP                    | TYP                     | TYP                     | ONIT |

| C <sub>pd</sub> Power dissipation capacitance per flip-flop |  | $C_{L} = 0$ ,   | f = 10 MHz |                        |                         |                         | pF   |

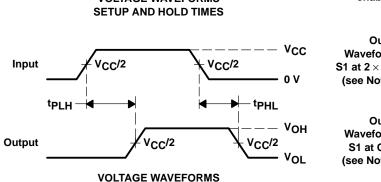

**VCC**

0 V

V<sub>CC</sub>/2

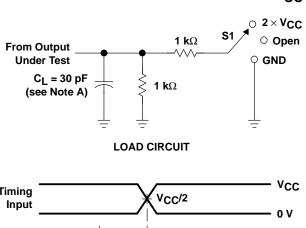

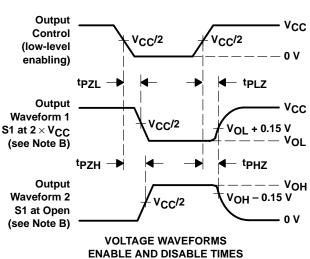

# PARAMETER MEASUREMENT INFORMATION V<sub>CC</sub> = 1.8 V

| TEST            | <b>S</b> 1        |

|-----------------|-------------------|

| <sup>t</sup> pd | Open              |

| tPLZ/tPZL       | 2×V <sub>CC</sub> |

| tPHZ/tPZH       | GND               |

V<sub>CC</sub>/2

VOLTAGE WAVEFORMS PULSE DURATION

Input

NOTES: A. C<sub>L</sub> includes probe and jig capacitance.

- B. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

- C. All input pulses are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz,  $Z_Q = 50 \Omega$ ,  $t_f \leq$  2 ns.  $t_f \leq$  2 ns.

- D. The outputs are measured one at a time with one transition per measurement.

- E. tpLZ and tpHZ are the same as tdis.

**PROPAGATION DELAY TIMES**

- F. tpz and tpzH are the same as ten.

- G. tpLH and tpHL are the same as tod.

Figure 1. Load Circuit and Voltage Waveforms

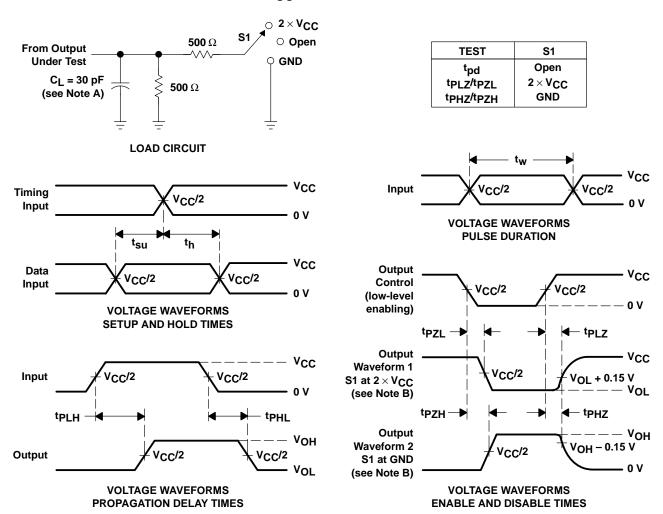

# PARAMETER MEASUREMENT INFORMATION $V_{CC} = 2.5 \text{ V} \pm 0.2 \text{ V}$

- NOTES: A. C<sub>L</sub> includes probe and jig capacitance.

- B. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

- C. All input pulses are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz,  $Z_Q = 50 \Omega$ ,  $t_f \leq 2$  ns.

- D. The outputs are measured one at a time with one transition per measurement.

- E. tpLz and tpHz are the same as tdis.

- F. tpzL and tpzH are the same as ten.

- G. tpLH and tpHL are the same as tpd.

Figure 2. Load Circuit and Voltage Waveforms

PRODUCT PREVIEW

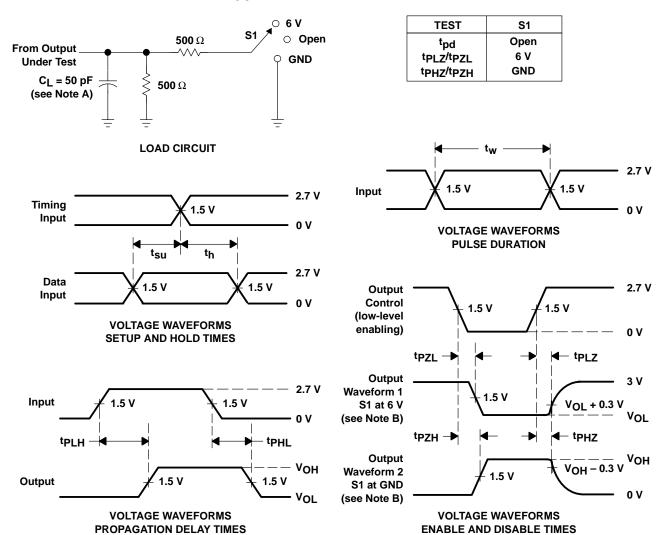

# PARAMETER MEASUREMENT INFORMATION $V_{CC}$ = 2.7 V AND 3.3 V $\pm$ 0.3 V

NOTES: A. C<sub>I</sub> includes probe and jig capacitance.

- B. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

- C. All input pulses are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz,  $Z_O = 50 \Omega$ ,  $t_f \leq$  2.5 ns,  $t_f \leq$  2.5 ns.

- D. The outputs are measured one at a time with one transition per measurement.

- E. tpLz and tpHz are the same as tdis.

- F. tpZL and tpZH are the same as ten.

- G. tpLH and tpHL are the same as tpd.

Figure 3. Load Circuit and Voltage Waveforms