## FCT Interface Logic

# CD54/74FCT640, CD54/74FCT640AT CD54/74FCT643, CD54/74FCT643AT

July 1990

## Octal Bus Transceivers, 3-State

CD54/74FCT640, CD54/74FCT640AT - Inverting CD54/74FCT643, CD54/74FCT643AT - True-Inverting

### Type Features:

- Buffered inputs

- Typical propagation delay:

6ns @ VCC = 5V, TA = +25°C, CL = 50pF (FCT640, FCT643)

The CD54/74FCT640, 640AT, 643 and 643AT use a small-geometry BiCMOS technology. The output stage is a combination of bipolar and CMOS transistors that limits the output-HIGH level to two diode drops below VCC. This resultant lowering of output swing (0V to 3.7V) reduces power bus ringing (a source of EMI) and minimizes VCC bounce and ground bounce and their effects during simultaneous output switching. The output configuration also enhances switching speed and is capable of sinking 48 to 64 milliamperes.

These octal bus transceivers are designed for asynchronous two-way communication between data buses.

The CD54/74FCT640, 640AT are octal inverting buffers; the CD54/74FCT643, 643AT are octal true/inverting buffers.

The direction of data flow (A to B, B to A) is controlled by the DIR input.

Outputs are enabled by a low on the Output Enable input  $(\overline{OE})$ ; a high  $\overline{OE}$  puts these devices in the high-impedance mode.

The CD54/74FCT640, 640AT, 643 and 643AT are supplied in 20-lead dual-in-line plastic packages (E suffix) and in 20-lead dual-in-line small-outline plastic packages (M suffix). Both package types are operable over two temperature ranges: Commercial (0°C to +70°C) and Extended Industrial (-55°C to +125°C).

The CD54FCT640 and 643 are also available in chip form (H suffix). These unpackaged devices are operable over the -55°C to +125°C temperature range.

### **Family Features:**

- SCR-latchup-resistant BiCMOS process and circuit design

- FCTXXX Speed of bipolar FAST\*/AS/S; FCTXXXAT - 30% faster than FAST/AS/S with significantly reduced power consumption

- 64/48-mA output sink current (commercial/extended industrial)

- Output voltage swing limited to 3.7V @ VCC = 5V

- Controlled output-edge rates

- Input/output isolation to VCC

- BiCMOS technology with low quiescent power

- \* FAST is a registered trademark of Fairchild Semiconductor Corp.

FCT843, FCT843AT FUNCTIONAL DIAGRAM

### TRUTH TABLE

| CONTROLINPUTS |     | FCT640 |    | FCT643, 643AT<br>DATA PORT STATUS |    |  |  |

|---------------|-----|--------|----|-----------------------------------|----|--|--|

| ŌĒ            | DIR | An     | Bn | An                                | Bn |  |  |

| L             | L   | ō      | ı  | 0                                 | 1  |  |  |

| н :           | н   | z      | z  | z                                 | z  |  |  |

| Н             | L   | z      | z  | z                                 | z  |  |  |

| L             | н   | 1      | ō  | 1                                 | ō  |  |  |

To prevent excess currents in the High-Z modes, all I/O terminals should be termilnated with 10k $\Omega$  to 1M $\Omega$  resistors.

H = HIGH

L = LOW

I = Input

O = Output (Same Level as Input)

$\overline{O}$  = Output (Inversion of Input Level)

Z = High Impedance

### MAXIMUM RATINGS, Absolute-Maximum Values:

| DC SUPPLY-VOLTAGE (VCC)                                                                             | 0.5V to 6V                         |

|-----------------------------------------------------------------------------------------------------|------------------------------------|

| DC INPUT DIODE CURRENT, IIK (for VI < -0.5V)                                                        |                                    |

| DC OUTPUT DIODE CURRENT, IOK (for VO < -0.5V)                                                       |                                    |

| DC OUTPUT SINK CURRENT per Output Pin, IO                                                           |                                    |

| DC OUTPUT SOURCE CURRENT per Output Pin, IO                                                         | 30mA                               |

| DC VCC CURRENT (ICC)                                                                                | 140mA                              |

| DC GROUND CURRENT (IGND)                                                                            | 528mA                              |

| POWER DISSIPATION PER PACKAGE (PD)                                                                  |                                    |

| For TA = -55°C to +100°C (PACKAGE TYPE E)                                                           | 500mW                              |

| For TA = +100°C to +125°C (PACKAGE TYPE E)                                                          | Derate Linearly at 8mW/°C to 300mW |

| For TA = -55°C to +70°C (PACKAGE TYPE M)                                                            | 400mW                              |

| For TA = +70°C to +125°C (PACKAGE TYPE M)                                                           | Derate Linearly at 6mW/OC to 70mW  |

| OPERATING-TEMPERATURE RANGE (TA):                                                                   |                                    |

| PACKAGE TYPE E, M                                                                                   | 55°C to +125°C                     |

| STORAGE TEMPERATURE (Tstg)                                                                          | 65°C to +150°C                     |

| LEAD TEMPERATURE (DURING SOLDERING):                                                                |                                    |

| At distance 1/16 in. ± 1/32 in. (1.59mm ± 0.79mm) from case for 10s maximum                         | +265°C                             |

| Unit inserted into PC board min, thickness 1/16 in. (1.59mm) with solder contacting lead tips only. | +300°C                             |

### **RECOMMENDED OPERATING CONDITIONS:**

The following are normal operating ranges for these devices. For maximum reliability, devices should always be operated within these ranges.

|                                     |                                   | LIN  |      |       |

|-------------------------------------|-----------------------------------|------|------|-------|

| CHARACTERISTIC                      |                                   | MIN  | MAX  | UNITS |

| Supply-Voltage Range, VCC*:         | CD74 Series, TA = 0°C to 70°C     | 4.75 | 5.25 | V     |

|                                     | CD54 Series, TA = -55°C to +125°C | 4.5  | 5.5  | ٧     |

| DC Input Voltage, VI                |                                   | 0    | VCC  | ٧     |

| DC Output Voltage, VO               |                                   | 0    | ≤VCC | ٧     |

| Operating Temperature, TA           |                                   | -55  | +125 | oc    |

| Input Rise and Fall Slew Rate, dt/d | lv                                | 0    | 10   | ns/V  |

<sup>\*</sup> Unless otherwise specified, all voltages are referenced to ground.

## FCT Interface Logic

### CD54/74FCT640, CD54/74FCT640AT CD54/74FCT643, CD54/74FCT643AT

July 1990

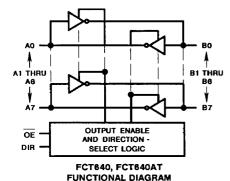

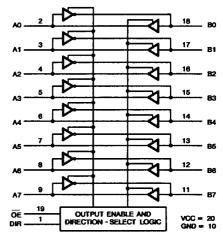

**FUNCTIONAL DIAGRAM**

## Octal Bus Transceivers, 3-State

CD54/74FCT640, CD54/74FCT640AT - Inverting CD54/74FCT643, CD54/74FCT643AT - True-Inverting

### Type Features:

- Buffered inputs

- Typical propagation delay: 6ns @ VCC = 5V, TA = +25°C, CL = 50pF (FCT640, FCT643)

The CD54/74FCT640, 640AT, 643 and 643AT use a small-geometry BiCMOS technology. The output stage is a combination of bipolar and CMOS transistors that limits the output-HIGH level to two diode drops below VCC. This resultant lowering of output swing (OV to 3.7V) reduces power bus ringing (a source of EMI) and minimizes VCC bounce and ground bounce and their effects during simultaneous output switching. The output configuration also enhances switching speed and is capable of sinking 48 to 64 milliamperes.

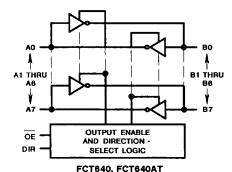

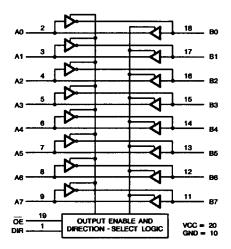

These octal bus transceivers are designed for asynchronous two-way communication between data buses.

The CD54/74FCT640, 640AT are octal inverting buffers; the CD54/74FCT643, 643AT are octal true/inverting buffers.

The direction of data flow (A to B, B to A) is controlled by the DIR input.

Outputs are enabled by a low on the Output Enable input  $(\overline{OE})$ ; a high  $\overline{OE}$  puts these devices in the high-impedance mode.

The CD54/74FCT640, 640AT, 643 and 643AT are supplied in 20-lead dual-in-line plastic packages (E suffix) and in 20-lead dual-in-line small-outline plastic packages (M suffix). Both package types are operable over two temperature ranges: Commercial (0°C to +70°C) and Extended Industrial (-55°C to +125°C).

The CD54FCT640 and 643 are also available in chip form (H suffix). These unpackaged devices are operable over the -55°C to +125°C temperature range.

#### Family Features:

- SCR-latchup-resistant BiCMOS process and circuit design

- FCTXXX Speed of bipolar FAST\*/AS/S; FCTXXXAT - 30% faster than FAST/AS/S with significantly reduced power consumption

- 64/48-mA output sink current (commercial/extended industrial)

- Output voltage swing limited to 3.7V @ VCC = 5V

- Controlled output~edge rates

- Input/output isolation to VCC

- BiCMOS technology with low quiescent power

<sup>\*</sup> FAST is a registered trademark of Fairchild Semiconductor Corp.

FCT643, FCT643AT FUNCTIONAL DIAGRAM

### SWITCHING CHARACTERISTICS

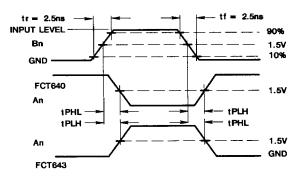

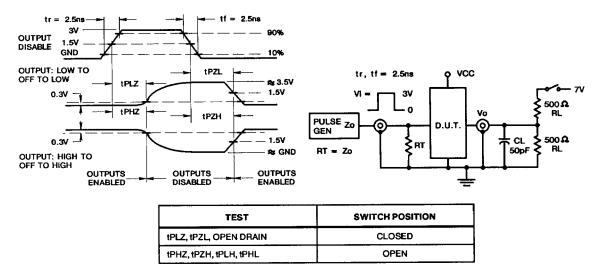

FCT Series: tr, tf = 2.5ns, CL = 50pF, RL - See Figure 3

|                                                                                                                                |                                                |            |                 | CD54/74FCT640, 643       |     |       |                 |     | CD54/74FCT640AT, 643AT |     |       |                 |     |                    |  |  |

|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|------------|-----------------|--------------------------|-----|-------|-----------------|-----|------------------------|-----|-------|-----------------|-----|--------------------|--|--|

|                                                                                                                                |                                                |            |                 | AMBIENT TEMPERATURE (TA) |     |       |                 |     |                        |     |       |                 |     |                    |  |  |

| CHARACTERISTICS                                                                                                                |                                                | SYMBOL     | ļ               |                          |     | +25°C | 0°C to<br>+70°C |     | -55°C to<br>+125°C     |     | +25°C | 0°C to<br>+70°C |     | -55°C to<br>+125°C |  |  |

|                                                                                                                                |                                                |            | A <sup>CC</sup> | TYP                      | MIN | MAX   | MIN             | MAX | ТҮР                    | MIN | MAX   | MIN             | MAX | UNITS              |  |  |

| Prop.<br>Delays:<br>Data to                                                                                                    | 640/AT An→Bn,<br>640/AT Bn→An,<br>643/AT An→Bn | tPLH, tPHL | 5†              | 6                        | 2   | 7     | 2               | 8   |                        | CO, | 7 A   | CT.             |     | ns                 |  |  |

| Outputs                                                                                                                        | 643/AT Bn→An,                                  | tPLH, tPHL | 5†              | 4.9                      | 2   | 6.5   | 2               | 7   |                        | boo |       | FFI             |     | ns                 |  |  |

| Output                                                                                                                         | 640/AT                                         | tPLZ, tPHZ | 5               | 7                        | 2   | 10    | 2               | 12  | 9)                     | ALE | 20    | 2               |     | пв                 |  |  |

| Disable to<br>Output                                                                                                           | 643/AT                                         | tPLZ, tPHZ | 5               | 7.5                      | 2   | 10    | 2               | 12  |                        |     | A II  | BILI            | 14  | ns                 |  |  |

| Output                                                                                                                         | 640/AT                                         | tPZL, tPZH | 5               | 11                       | 2   | 13    | 2               | 16  |                        | AVI |       |                 |     | ns                 |  |  |

| Enable to<br>Output                                                                                                            | 643/AT                                         | tPZL, tPZH | 5               | 9.8                      | 2   | 13    | 2               | 16  |                        |     |       |                 |     | ns                 |  |  |

| Power Diss<br>Capacitano                                                                                                       | CPD§                                           | -          |                 |                          |     |       |                 |     |                        |     |       |                 | pF  |                    |  |  |

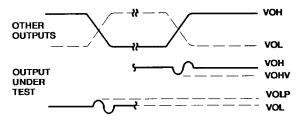

| Min. (Valley) VCHV During Switching of Other Outputs (Output Under Not Switching)  VCHV See Test Figure 1                      |                                                |            | 5               | 0.5 Typ. @ +25°C         |     |       |                 |     |                        |     |       | v               |     |                    |  |  |

| Max. {Peak} VOLP During Switching of Other Outputs (Output Under Test Not Switching)  VOLP See 5 1 Typ. @ +25°C 1 Typ. @ +25°C |                                                |            |                 |                          |     | v     |                 |     |                        |     |       |                 |     |                    |  |  |

| Input Capacitance CI                                                                                                           |                                                | CI         |                 | -                        | -   | 10    | -               | 10  | -                      | -   | 10    | -               | 10  | pF                 |  |  |

| Input/Outp                                                                                                                     | ut Capacitance                                 | CI/O       |                 | -                        | -   | 15    | -               | 15  | -                      | -   | 15    | -               | 15  | pF                 |  |  |

†5V: min. is @ 5.5V max. is @ 4.5V

5V: min. is @ 5.25V for 0°C to +70°C max. is @ 4.75V for 0°C to +70°C typ.is @ 5V

§CPD, measured per function, is used to determine the dynamic power consumption. PD (per package) = VCC ICC +  $\Sigma$  (VCC<sup>2</sup> fi CPD + VO<sup>2</sup> fo CL + VCC  $\Delta$ ICC D) where:

VCC = supply voltage

$\Delta iCC =$  flow through current x unit load

CL = output load capacitance

D = duty cycle of input high

to = output frequency

fi = input frequency

### PARAMETER MEASUREMENT INFORMATION

### NOTES:

- VOLP is measured with respect to a ground reference near the output under test. VOHV is measured with respect to VOH.

- Input pulses have the following characteristics: PRR ≤ 1MHz, tr = 2.5ns, tf = 2.5ns, skew 1ns.

- R.F. fixture with 700-MHz design rules required. IC should be soldered into test board and bypassed with 0.1μF capacitor. Scope and probes require 700-MHz bandwidth.

Figure 1 - Simultaneous switching transient waveforms.

Figure 2 - Propagation delay times.

Figure 3 - Three-state propagation delay times and test circuit.