#### **PRODUCT FEATURES**

- Designed to the Intel spec. for supporting next generation Intel processor and Pentium-pro's with 2.5V clocking requirements with the Intel 440FX chipset.

- 4 host (CPU) clocks.

- IOAPIC for multiprocessing.

- Power management for Mobile applications.

- < 250 pS skew on CPU buffers</p>

- < 250 pS skew on PCI buffers</p>

- 48 Pin SSOP package for minimum board space

| BLOCK DIAGRAM  XIN                                          |

|-------------------------------------------------------------|

| SEL1 SEL0  POWER CPU_en PWR_DWN#  PLL2  PLL2  A8 MHZ  8 MHZ |

|     | FREQUENCY TABLE |      |          |          |  |  |  |  |  |  |  |

|-----|-----------------|------|----------|----------|--|--|--|--|--|--|--|

| STM | SEL1            | SEL0 | CPU      | PCI      |  |  |  |  |  |  |  |

| Х   | 0               | 0    | Tristate | Tristate |  |  |  |  |  |  |  |

| 0   | 0               | 1    | 63.0     | 31.5     |  |  |  |  |  |  |  |

| 0   | 1               | 0 🥢  | 69.87    | 34.94    |  |  |  |  |  |  |  |

| Х   | 1               |      | XIN/2    | XIN/4    |  |  |  |  |  |  |  |

| 1   | 0               | 1    | 60       | 30       |  |  |  |  |  |  |  |

| 1   | 1               | U    | F44      | 33.22    |  |  |  |  |  |  |  |

X = Don't Ca

| RE 7         | 48 VDD 47 REF2 46 VDDq2 45 IOAPIC 44 VSS 43 VSS 42 CPUCLK0 41 CPUCLK1 40 VDDq2 39 CPUCLK2 38 CPUCLK3 37 VSS 36 8 MHZ 35 n/c 34 VDDq3 33 24 MHZ 32 VSS 31 STM |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCICLK7 = 17 | 32 VSS                                                                                                                                                       |

| n/c          | 29 CPU_en 28 PWR_DWN# 27 SEL0 26 SEL1 25 VDD                                                                                                                 |

#### PIN DESCRIPTION

XIN, XOUT - These pins form an on-chip reference oscillator when connected to terminals of an external parallel resonant crystal (nominally 14.318 MHz). XIN may also serve as input for an externally generated reference signal.

**SEL(0:1)** - Standard frequency select inputs. They have internal pull-ups.

**CPUCLK(0:3)** - Low skew (<250 pS) clock outputs for host frequencies such as CPU, Chipset, Cache. VDDq2 is the supply voltage for these outputs.

**PCICLK(0:7)** - Low skew (<250pS) clock outputs for PCI frequencies. They are synchronous to CPUCLK's.

REF(0:2) - Buffered outputs of reference 14.3 MHz.

**IOAPIC** - Buffered output of 14.3 MHz for multiprocessor support. It is powered by VDDq2.

48 MHz - Frequency output for USB.

24 MHz - Frequency output for super I/O.

8 MHz - 8 MHz output frequency.

**PWR\_DWN# -** Power down pin to turn the power of the whole chip down including the VCOs and the crystal buffer. It has an internal Pull-Up

CPU\_en - Active low signal to stop the CPU clocks when low. It is high in national operation and has an internal Pull-Up.

PCI\_en - Active lov signal stop the CI clocks, when low. It is high in ormal ope tion id has an internal Pull-Up.

STM - System test moo. Increased PCI and CPU clocks y 4.75% for system timing testing when low.

VSS - read pins for the chip.

**VDD** - Pow ply pins for analog and core circuitry.

Da4 - wer supply pins for 3.3V for PCI bus.

VDD 3 - Power supply pins for 3.3V IO pins.

**IDDq2** - Power supply pins for 2.5V/3.3V IO pins.

**N/C** - No connection pins.

|      | TION TABLE |          |        |            |            |          |          |          |  |  |  |

|------|------------|----------|--------|------------|------------|----------|----------|----------|--|--|--|

| SEL1 | SEL0       | CPU      | PC     | REF(0:2)   | IOAPIC     | 24 MHz   | 48 MHz   | 8 MHz    |  |  |  |

| 0    | 0          | Trietata | i tate | Tristate   | Tristate   | Tristate | Tristate | Tristate |  |  |  |

| 0    | 1          | √ote1    | Note   | 14.318 MHz | 14.318 MHZ | 24 MHZ   | 48 MHZ   | 8 MHZ    |  |  |  |

| 1    | 0          | Note1    | ote1   | 14.318 MHZ | 14.318 MHZ | 24 MHZ   | 48 MHZ   | 8 MHZ    |  |  |  |

| 1    | 1          | 'IN/2    | JN/4   | XIN        | XIN        | XIN/4    | XIN/2    | XIN/12   |  |  |  |

Note1: See Frequency, , Page 1

#### **POWER MANAGEMENT FUNCTIONS**

The IMISC672 clocks may be disabled according to the following table in order to reduce power consumption. All clocks are stopped in the low state. All clocks maintain a valid high period on transitions from running to stopped. On low to high transitions of PWR\_DWN#, external circuitry should allow 2-3 mS for the VCOs to stabilize prior to releasing PCI\_en or CPU\_en to a high level. The CPU and PCI clocks transition between running and stopped following the latency table bellow. CPU and PCI clocks are stopped after a complete period in their low state.

| CPU_en | PCI_en | PWR_DWN# | CPUCLK | PCICLK | OTHER Collis | XTAL & VCOs |

|--------|--------|----------|--------|--------|--------------|-------------|

| Х      | Х      | 0        | LOW    | LOW    | LO.          | OFF         |

| 0      | 0      | 1        | LOW    | LOW    | P' NNN       | RU'NING     |

| 0      | 1      | 1        | LOW    | Note2  | UNNING       | 「」NNING     |

| 1      | 0      | 1        | Note2  | LOW    | h NNING      | RUNNING     |

| 1      | 1      | 1        | Note2  | Note2  | RUi 'ING     | RUNNING     |

Note2: See Frequency Table, Page 1

| Signal   | Signal State  | Min Pulse Width   | Mir. ate .y        | Max Latency           |

|----------|---------------|-------------------|--------------------|-----------------------|

|          |               | (count by clocks) | (count by C clock, | (count by CPU clocks) |

| CPU_en   | 0 (disabled)  | 100 CPU           | 1                  | 4                     |

|          | 1 (enabled)   | 10 CPU            | 1                  | 4                     |

| PCI_en   | 0 (disabled)  | 10 PCI            |                    | 4                     |

|          | 1 (enabled)   | 10 PCI            | 2                  | 4                     |

| PWR_DWN# | 0 (power off) | 3mS               | 1                  | 4                     |

|          | 1 (normal)    | 3mS               | 2 mS               | 3 mS                  |

#### .AXIN JM RATINGS

Voltage Relative to 'CO. -0.3V

Voltage Relative VDD: 0.3V

Storage Temper Jre: -65°C to + 150°C

Operating Temper Jre: -0°C to + 70°C

Maximum Power Suppry. 7V

This device contains circuitry to protect the inputs against damage due to high static voltages or electric field; however, precautions should be taken to avoid application of any voltage higher than the maximum rated voltages to this circuit. For proper operation, Vin and Vout should be constrained to the range:

VSS<(Vin or Vout)<VDD

Unused inputs must always be tied to an appropriate logic voltage level (either VSS or VDD).

| ELECTRICAL CHARACTERISTICS |                                                      |     |     |     |       |                                  |  |  |  |  |

|----------------------------|------------------------------------------------------|-----|-----|-----|-------|----------------------------------|--|--|--|--|

| Characteristic             | Symbol                                               | Min | Тур | Max | Units | Conditions                       |  |  |  |  |

| Input Low Voltage          | VIL                                                  | -   | -   | 0.8 | Vdc   | -                                |  |  |  |  |

| Input High Voltage         | VIH                                                  | 2.0 | -   | -   | Vdc   | -                                |  |  |  |  |

| Input Low Current          | IIL                                                  |     |     | -66 | μA    |                                  |  |  |  |  |

| Input High Current         | IIH                                                  |     |     | 5   | μA    |                                  |  |  |  |  |

| Output Low Voltage         | VOL                                                  | -   | -   | 0.4 | Vdc   | All Outputs (see switching spec) |  |  |  |  |

| IOL = 12 mA                |                                                      |     |     |     |       |                                  |  |  |  |  |

| Output High Voltage        | VOH                                                  | 2.4 | -   | -   | Vdc   | All Outputs see switching spec)  |  |  |  |  |

| IOH = 12 m <b>A</b>        |                                                      |     |     |     |       |                                  |  |  |  |  |

| Tri-State leakage Current  | loz                                                  | -   | -   | 10  | μA    |                                  |  |  |  |  |

| Dynamic Supply Current     | IDD                                                  | -   | 40  | 90  | mA    | U = 66.6 N₁ 7 No Load            |  |  |  |  |

| Static Supply Current      | IDD                                                  | -   | 20  | 30  | mA    | CPU 66.6 MHZ, No Load            |  |  |  |  |

|                            |                                                      |     |     |     |       |                                  |  |  |  |  |

| Short Circuit Current      | ISC                                                  | 25  |     | -   | mA    | 1 output at a time - 30 seconds  |  |  |  |  |

|                            | VDD = VDDq2 = VDDq3 VDDq4 3.3V+5%, TA = 0°C to +70°C |     |     |     |       |                                  |  |  |  |  |

|                                                                                                                             | SWITCHING CHARACI. RISTIC |                                                  |     |              |    |                                                     |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------|---------------------------|--------------------------------------------------|-----|--------------|----|-----------------------------------------------------|--|--|--|--|

| Characteristic                                                                                                              | Symbol                    | Min                                              | Тур | Max          | Un | Conditions                                          |  |  |  |  |

| Output Duty Cycle                                                                                                           | -                         | 45                                               | 5(  | 55           | %  | See note 3                                          |  |  |  |  |

| CPUCLK(0:3) High Time                                                                                                       | tHKH                      | 5.2                                              |     | - /          | nS | @ 66.6 MHZ, Measured at 2.0V                        |  |  |  |  |

| CPUCLK(0:3) Low Time                                                                                                        | tHKL                      | <i>"</i> ປ                                       | -   |              | nS | @ 66.6 MHZ, Measured at 0.4V                        |  |  |  |  |

| CPUCLK(0:3) High Time                                                                                                       | tHKH                      | 0                                                |     | -            | nS | @ 60 MHZ, Measured at 2.0V                          |  |  |  |  |

| CPUCLK(0:3) Low Time                                                                                                        | tHKI                      | 5.8                                              | -   | -            | nS | @ 60 MHZ, Measured at 0.4V                          |  |  |  |  |

| CPU to PCI Offset                                                                                                           | t/ F                      | 1                                                |     | 4            | nS | See Note 3                                          |  |  |  |  |

| Buffer out Skew All CPU and PCI Buffer Outputs                                                                              | te FW                     | -                                                | -   | 250          | pS | See Note 3                                          |  |  |  |  |

| ΔPeriod Adjacent Cycle                                                                                                      |                           | <del>                                     </del> | -   | <u>+</u> 250 | pS | -                                                   |  |  |  |  |

| Jitter Aboslute, CPU                                                                                                        | tja                       |                                                  |     | 500          | pS | (long term jitter measured over a 3 minute period)  |  |  |  |  |

| Overshoot/Undershoot<br>Beyond Power Rails                                                                                  | V ,er                     | -                                                | -   | 1.5          | V  | 22 ohms @ source of 8 inch PCB run<br>to 15 pf load |  |  |  |  |

| Ring Back Exclusion                                                                                                         | $V_{RBE}$                 | 0.7                                              |     | 2.1          | V  | See Note 4                                          |  |  |  |  |

| $VDD$ = $VDD$ q3 = $VDD$ q4 = 3.3 $V$ $\pm 5\%$ , $VDD$ q2 = 2.375 $V$ to 2.9 $V$ , TA = 0 $^{\circ}$ C to +70 $^{\circ}$ C |                           |                                                  |     |              |    |                                                     |  |  |  |  |

Note 3: CPUCLK(0:3) are measured at 1.25 V. All other signals are measured at 1.5V.

Note 4: Ring Back must not enter this range.

| TYPE TB4L BUFFER CHARACTERISTICS FOR CPUCLK(0:3) and IOAPIC |                    |     |     |     |       |                    |  |  |  |  |

|-------------------------------------------------------------|--------------------|-----|-----|-----|-------|--------------------|--|--|--|--|

| Characteristic                                              | Symbol             | Min | Тур | Max | Units | Conditio           |  |  |  |  |

| Pull-Up Current Min                                         | IOH <sub>min</sub> | 22  | -   | -   | mA    | Vc∴t = 1.25 V      |  |  |  |  |

| Pull-Up Current Max                                         | IOH <sub>max</sub> | 13  | -   | -   | mA    | Vc. = Vdda2 - 0.5V |  |  |  |  |

| Pull-Down Current Min                                       | IOL <sub>min</sub> | 50  | -   | -   | mA    | Vout 1.5 V         |  |  |  |  |

| Pull-Down Current Max                                       | IOL <sub>max</sub> | 18  | -   | -   | mA    | / _it = 0.4 V      |  |  |  |  |

| Rise/Fall Time Min                                          | TRF                | 0.4 | -   | 1.8 | าร    | 20 pF Load         |  |  |  |  |

| Between 0.4 V and 2.0 V                                     |                    |     |     |     |       |                    |  |  |  |  |

| Rise/Fall Time Max                                          | TRF <sub>max</sub> | -   | -   | 2.3 | ı nS  | 20 pF Load         |  |  |  |  |

| Between 0.4 V and 2.0 V                                     |                    |     |     |     | ı     |                    |  |  |  |  |

$VDD = VDDq3 = VDDq4 = 3.3V \pm 5\%$   $VDF_q2 = 2.375V \text{ to } 2.9V, TA = 0°C \text{ to } +70°C$

#### TYPE TB5L BUFFER CHARACTERICTICS FOR REF(1:2) and 48/24 MHZ

| Characteristic                                | Symbol              | Min | іур | _Max     | nitsر | Conditions      |

|-----------------------------------------------|---------------------|-----|-----|----------|-------|-----------------|

| Pull-Up Current Min                           | IOH <sub>min</sub>  | 30  | -   | <u> </u> | mA    | Vout = 1.5 V    |

| Pull-Up Current Max                           | IOH <sub>max</sub>  | 13  | -   | -        | mA    | Vout = Vdd-0.5V |

| Pull-Down Current Min                         | IOL <sub>m</sub>    | 32  |     | -        | mA    | Vout = 1.5 V    |

| Pull-Down Current Max                         | IOL <sub>×</sub>    |     | -   | 29       | mA    | Vout = 0.4 V    |

| Rise/Fall Time Min<br>Between 0.4 V and 2.4 V | TRF <sub>mirr</sub> | 1.0 | -   | -        | nS    | 20 pF Load      |

| Rise/Fall Time Max<br>Between 0.4 V and 2.4 V | TF -                | -   | -   | 4.0      | nS    | 20 pF Load      |

$V\Gamma$  =  $VDDq3 = VDDq4 = 3.3V \pm 5\%$ , VDDQ2 = 2.375V to 2.9V,  $TA = 0^{\circ}C$  to  $+70^{\circ}C$

| TYPE 34L BUFFER CHARACTERISTICS FOR REF0 and PCI |                    |     |     |     |            |                 |  |  |

|--------------------------------------------------|--------------------|-----|-----|-----|------------|-----------------|--|--|

| Characteristic                                   | Symbol             | Min | Тур | Max | Units      | Conditions      |  |  |

| Pull-Up Current Min                              | IOH <sub>min</sub> | 44  | -   | -   | mA         | Vout = 1.5 V    |  |  |

| Pull-Up Current Max                              | IOH <sub>max</sub> | 18  | -   | -   | mA         | Vout = Vdd-0.5V |  |  |

| Pull-Down Current Min                            | IOL <sub>min</sub> | 50  | -   | -   | m <b>A</b> | Vout = 1.5 V    |  |  |

| Pull-Down Current Max                            | IOL <sub>max</sub> | 18  | -   | -   | m <b>A</b> | Vout = 0.4 V    |  |  |

| Rise/Fall Time Min<br>Between 0.4 V and 2.4 V    | TRF <sub>min</sub> | 0.5 | -   | 1.4 | nS         | 30 pF Load      |  |  |

| Rise/Fall Time Max<br>Between 0.4 V and 2.4 V    | TRF <sub>max</sub> | -   | -   | 2.4 | nS         | 30 pF Load      |  |  |

$VDD = VDDq3 = VDDq4 = 3.3V \pm 5\%$ , VDDq2 = 2.375V to 2.9V,  $TA = 0^{\circ}C$  to  $+70^{\circ}C$

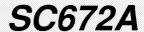

This is only a layout recommendation for best performance and lower EMI. The designer may choose a different approach but C4, C5, C6, C7, C8, C9, C10, and C11 (all are  $0.1\mu f$ ) should always be used and placed close to their VDD pins.

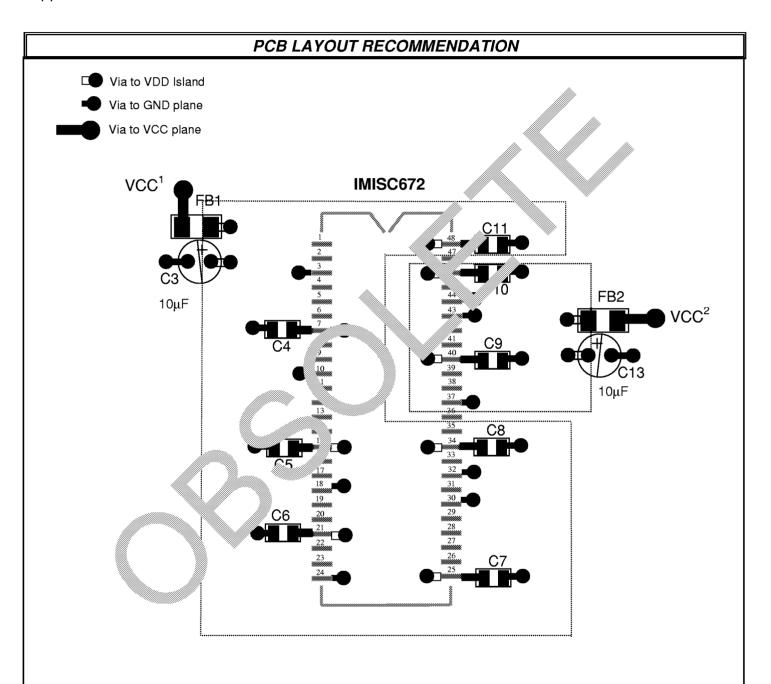

#### PACKAGE DRAWING AND DIMENSIONS

| 48 PI          | N SSC | P OU      | TL'NE       | DIMEI  | NSION   | IS    |

|----------------|-------|-----------|-------------|--------|---------|-------|

|                |       | INCH      | MILLIMETERS |        |         |       |

| SYMBOL         | MIN   | NO.       | MA'         | MIN    | NOM     | MAX   |

| Α              | 0.095 | ົ່ງ.102   | i10         | 2 .    | 2.59    | 2.79  |

| A <sub>1</sub> | 0.00  | 0.012     | 0. 3        | ົ້ນ.20 | 0.31    | 0.41  |

| A2             | ( 88  | 190       | 0.092       | 2.24   | 2.29    | 2.34  |

| В              | 0.008 | 0.0       | 0.0135      | 0.203  | 0.254   | 0.343 |

| С              | 0.005 | -         | 0.010       | 0.127  | -       | 0.254 |

|                | r_20  | 0.625     | 0.630       | 15.75  | 15.88   | 16.00 |

| E              | ა.292 | 296       | 0.299       | 7.42   | 7.52    | 7.59  |

| e              |       | J.025 BS0 |             | C      | .635 BS | O     |

| Н              | ر ا   | 0.406     | 0.410       | 10.16  | 10.31   | 10.41 |

| a              | 0.10  | 0.013     | 0.016       | 0.25   | 0.33    | 0.41  |

| L              | 0.024 | 0.032     | 0.040       | 0.61   | 0.81    | 1.02  |

|                | 0.085 | 0.093     | 0.100       | 2.16   | 2.36    | 2.54  |

| ORDERING INFORMATION |              |                         |

|----------------------|--------------|-------------------------|

| Part Number          | Package Type | Production Flow         |

| IMISC672AYB          | 48 PIN 🐸 🤼   | ommercial, 0°C to +70°C |

Note: The ordering park simble is to ned by a combination of device number, device revision, package style, and screening as shown w.

Marking: Example: IMI

SC672A ' Date Cod Lot #

IMISC672 'B

B = Commercial, 0°C to + 70°C

<u>Package</u> Y = SSOP

Revision

**IMI Device Number**