### SN74CBT3384 DUAL 5-BIT CROSSBAR SWITCH

NOVEMBER 1992 - REVISED APRIL 1993

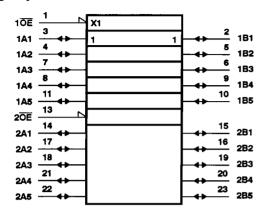

| <ul> <li>Space-Saving Package Option:</li> <li>Shrink Small-Outline Package</li> </ul>                                                       | DB, DW, NT, OR PW PACKAGE<br>(TOP VIEW)    |

|----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| Features EIAJ 0.65-mm Lead Pitch                                                                                                             | 10E (1 24) VCC                             |

| <ul> <li>5-Ω Switch Connection Between Two Ports</li> </ul>                                                                                  | 1OE 1 1 24 V <sub>CC</sub><br>1B1 2 23 2B5 |

| Near-Zero Propagation Delay                                                                                                                  | 1A1 [] 3 22 [] 2A5                         |

| TTL-Compatible Input and Output Levels                                                                                                       | 1A2 🚺 4 21 🗍 2A4                           |

| Package Options Include Plastic DIP                                                                                                          | 1B2 <b>[</b> ] 5 20 <b>]</b> ] 2B4         |

| Packages and Small-Outline and Thin                                                                                                          | 1B3 🛛 6 19 🗍 2B3                           |

| Shrink Small-Outline Packages                                                                                                                | 1A3 [ <b>]</b> 7 18 <b>]</b> 2A3           |

|                                                                                                                                              | 1A4 🛛 8 17 🗍 2A2                           |

| description                                                                                                                                  | 1B4 🛛 9 16 🕽 2B2                           |

| ·                                                                                                                                            | 1B5 🛛 10 15 🕽 2B1                          |

| The SN74CBT3384 provides 10 bits of high-                                                                                                    | 1A5 🛛 11 14 🗍 2A1                          |

| speed TTL-compatible bus switching. The low<br>on-state resistance of the switch allows<br>bidirectional connections to be made while adding | GND [ 12 13] 2 <del>0E</del>               |

The device is organized as two 5-bit switches with separate output-enable  $(\overline{OE})$  inputs. When  $\overline{OE}$  is low, the switch is on and port A is connected to port B. When  $\overline{OE}$  is high, the switch is open and a high-impedance state exists between the two ports.

The SN74CBT3384 is packaged in TI's shrink small-outline package (DB), which provides the same I/O pin count and functionality of standard small-outline packages in less than half the printed-circuit-board area.

The SN74CBT3384 is characterized for operation from -40°C to 85°C.

### **FUNCTION TABLE**

| OE1 | OE2 | B1-B5 | B6-B10 | FUNCTION   |

|-----|-----|-------|--------|------------|

| L   | L   | A1-A5 | A6-A10 | Connect    |

| L   | н   | A1-A5 | z      | Connect    |

| н   | L   | Z     | A6-A10 | Connect    |

| н   | н   | Z     | z      | Disconnect |

near-zero propagation delay.

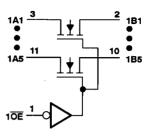

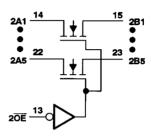

### logic symbol†

<sup>&</sup>lt;sup>†</sup> This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

### logic diagram (positive logic)

### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

| Supply voltage range, V <sub>CC</sub>                     |                | 0.5 V to 7 V  |

|-----------------------------------------------------------|----------------|---------------|

| Input voltage range, V <sub>I</sub> (see Note 1)          |                | 0.5 V to 7 V  |

| Current into any pin, IO                                  |                | 128 mA        |

| Input clamp current, I <sub>IK</sub> (V <sub>I</sub> < 0) |                | 50 mA         |

| Maximum power dissipation at TA = 55°C (in still air      | r): DB package | 0.5 W         |

|                                                           | DW package     | 0.85 W        |

|                                                           | NT package     |               |

|                                                           | PW package     | 0.5 W         |

| Storage temperature range                                 |                | 65°C to 150°C |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### recommended operating conditions

|     |                                | MIN | MAX | UNIT |

|-----|--------------------------------|-----|-----|------|

| Vcc | Supply voltage                 | 4.5 | 5.5 | V    |

| VIН | High-level input voltage       | 2   |     | V    |

| VIL | Low-level input voltage        |     | 0.8 | ٧    |

| TA  | Operating free-air temperature | -40 | 85  | °C   |

NOTE 1: The input and output negative-voltage ratings may be exceeded if the input and output clamp-current ratings are observed.

# PRODUCT PREVIEW

## electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

| PARAMETER                   |                            | TEST CONDITIO                 | ns                                      | MIN | TYP | MAX  | UNIT  |  |

|-----------------------------|----------------------------|-------------------------------|-----------------------------------------|-----|-----|------|-------|--|

| VIK                         | V <sub>CC</sub> = 4.5 V,   | l <sub>l</sub> = -18 mA       |                                         |     |     | -1.2 | ٧     |  |

| 1.                          | V <sub>CC</sub> = 0,       | V <sub>I</sub> = 5.5 V        |                                         |     |     | 10   |       |  |

| Jl .                        | V <sub>CC</sub> = 5.5 V,   | V <sub>I</sub> = 5.5 V or GND |                                         |     |     | ±1   | ±1 μA |  |

| los                         | V <sub>CC</sub> = 4.5 V,   | V <sub>I</sub> (A) = 0,       | V <sub>I(B)</sub> = 4.5 V               | 100 |     |      | mA    |  |

| lcc                         | V <sub>CC</sub> = 5.5 V,   | IO = 0,                       | V <sub>I</sub> = V <sub>CC</sub> or GND |     |     | 1    | mA    |  |

| ΔICC <sup>‡</sup>           | V <sub>CC</sub> = 3.6 V,   | One input at 2.7 V,           | Other inputs at VCC or GND              |     |     | 0.2  | mA    |  |

| C <sub>i</sub> Control pins | V <sub>I</sub> = 3 V or 0  |                               |                                         |     | 4   |      | pF    |  |

| C <sub>o(ON)</sub>          | V <sub>O</sub> = 3 V or 0, | Switch on                     |                                         |     | 8   |      | pF    |  |

| C <sub>o(OFF)</sub>         | V <sub>O</sub> = 3 V or 0, | Switch off                    |                                         |     | 6   |      | pF    |  |

| 2                           | V <sub>CC</sub> = 4.5 V,   | V <sub>I</sub> = 0,           | l <sub>I</sub> = 64 mA                  |     |     | 6    |       |  |

| r <sub>on</sub> §           | V <sub>CC</sub> = 4.5 V,   | V <sub>1</sub> = 2.4 V,       | I <sub>I</sub> = 15 mA                  |     |     | 12   | Ω     |  |

<sup>†</sup> All typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25°C.

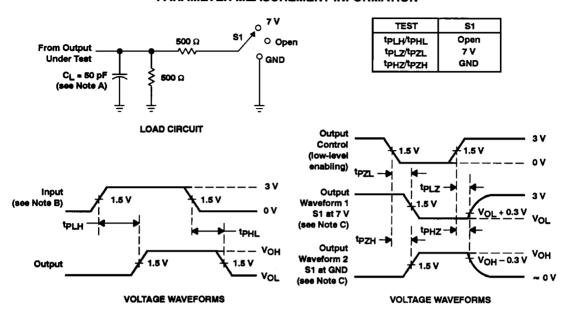

# switching characteristics over recommended operating free-air temperature range, $C_L = 50 \text{ pF}$ (unless otherwise noted) (see Figure 1)

| PARAMETER          | FROM<br>(INPUT) | то<br>(оитрит) | T <sub>A</sub> = - | T <sub>A</sub> = -40°C<br>TO 85°C |     | T <sub>A</sub> = 0°C<br>TO 70°C |      |

|--------------------|-----------------|----------------|--------------------|-----------------------------------|-----|---------------------------------|------|

|                    |                 |                | MIN                | MAX                               | MIN | MAX                             | ]    |

| tPLH <sup>¶</sup>  | A or B          | B or A         |                    |                                   |     | 0.25                            | ns   |

| t <sub>PHL</sub> ¶ |                 |                |                    |                                   |     | 0.25                            |      |

| <sup>t</sup> PZH   | ŌĒ              | A or B         |                    |                                   | 1.5 | 7.5                             | ns   |

| tpZL               |                 |                |                    |                                   | 1.5 | 7.5                             | 113  |

| tpHZ               | ŌĒ              |                |                    |                                   | 1.5 | 6.5                             | ns   |

| tPLZ               |                 | t              |                    |                                   | 1.5 | 6.5                             | i is |

This parameter is characterized but not tested. This propagation delay is due to the RC delay of the on-state resistance of the switch and the load capacitance.

<sup>&</sup>lt;sup>‡</sup> This is the increase in supply current for each input that is at the specified TTL voltage level rather than V<sub>CC</sub> or GND.

Measured by the voltage drop between the A and B pin at the indicated current through the switch. On-state resistance (ron) is determined by the lower of the voltages of the two (A or B) pins.

### PARAMETER MEASUREMENT INFORMATION

NOTES: A. C<sub>I</sub> includes probe and jig capacitance.

- B. All input pulses are supplied by generators having the following characteristics: PRR ≤ 10 MHz, Z<sub>O</sub> = 50 Ω, t<sub>f</sub> ≤ 2.5 ns, t<sub>f</sub> ≤ 2.5 ns.

- C. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

- D. The outputs are measured one at a time with one input transition per measurement.

Figure 1. Load Circuit and Voltage Waveforms