# **OKI** Semiconductor

This version: Jan. 1998 Previous version: Aug. 1996

## MSM82C84A-2RS/GS/JS

#### **CLOCK GENERATOR AND DRIVER**

#### **GENERAL DESCRIPTION**

The MSM82C84A-2RS/GS is a clock generator designed to generate MSM80C86A-10 and MSM80C88A-10 system clocks of 8MHz.

Due to the use of silicon gate CMOS technology, standby current is only  $40\,\mu\text{A}$  (MAX.), and the power consumption is very low with  $16\,\text{mA}$  (MAX.) when a  $8\,\text{MHz}$  clock is generated.

#### **FEATURES**

- Operating frequency of 6 to 24 MHz (CLK output 2 to 8 MHz)

- 3 µ silicon gate CMOS technology for low power consumption

- Built-in crystal oscillator circuit

- 3 V to 6 V single power supply

- Built-in synchronized circuit for MSM80C86A-10 and MSM80C88A-10 READY and RESET

- TTL compatible

- Built-in Schmitt trigger circuit (RES input)

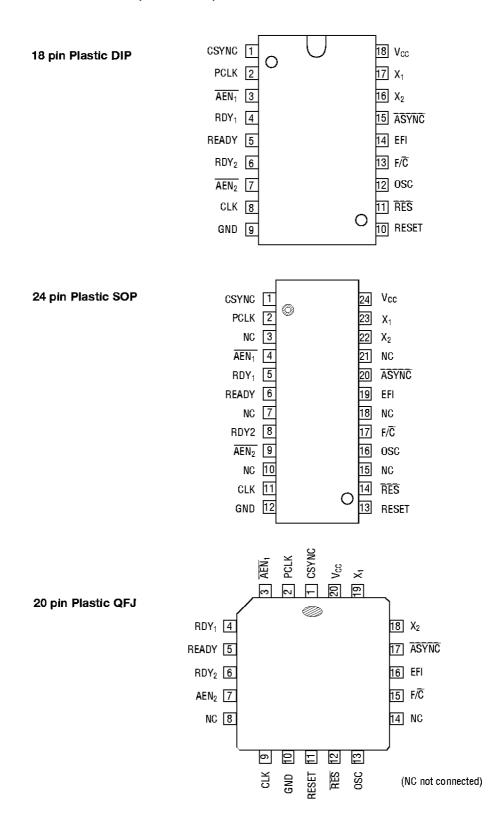

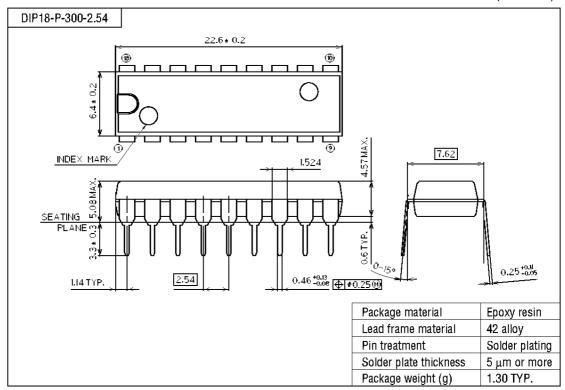

- 18-pin Plastic DIP (DIP18-P-300-2.54): (Product name: MSM82C84A-2RS)

- 20-pin Plastic QFJ (QFJ20-P-S350-1.27): (Product name: MSM82C84A-2JS)

- 24-pin Plastic SOP (SOP24-P-430-1.27-K): (Product name: MSM82C84A-2GS-K)

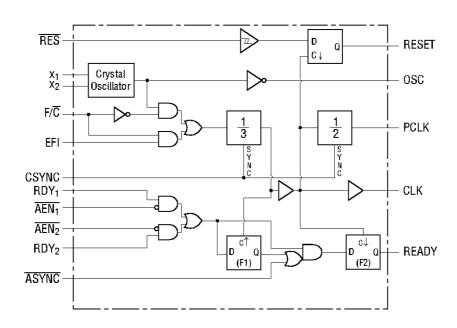

#### **FUNCTIONAL BLOCK DIAGRAM**

## **PIN CONFIGURATION (TOP VIEW)**

#### **ABSOLUTE MAXIMUM RATINGS**

| Parameter           | Symbol           | Condition         | Rat              | Unit                 |      |

|---------------------|------------------|-------------------|------------------|----------------------|------|

| Farameter           | Symbol           | Condition         | MSM82C84A-2RS/JS | MSM82C84A-2GS        | Unit |

| Supply Voltage      | V <sub>CC</sub>  | Deenset           | − <b>0.</b> 5 t  | :0 +7                | V    |

| Input Voltage       | V <sub>IN</sub>  | Respect<br>to GND | −0.5 to \        | V                    |      |

| Output Voltage      | V <sub>OUT</sub> | to divid          | −0.5 to \        | / <sub>CC</sub> +0.5 | V    |

| Storage Temperature | T <sub>STG</sub> | _                 | −55 to +150      |                      | °C   |

| Power Dissipation   | PD               | Ta = 25°C         | 0.8              | 0.7                  | W    |

#### **OPERATING RANGES**

| Parameter             | Symbol          | Range      | Unit |

|-----------------------|-----------------|------------|------|

| Supply Voltage        | V <sub>CC</sub> | 3 to 6     | V    |

| Operating Temperature | T <sub>op</sub> | -40 to +85 | °C   |

#### RECOMMENDED OPERATING CONDITIONS

| Parameter                            | Symbol          | Min.                | Тур.     | Max.                 | Unit |

|--------------------------------------|-----------------|---------------------|----------|----------------------|------|

| Supply Voltage                       | V <sub>CC</sub> | 4.5                 | 5        | 5.5                  | ٧    |

| Operating Temperature                | T <sub>op</sub> | -40                 | +25      | +85                  | °C   |

| "L" Level Input Voltage              | VIL             | -0.5                | _        | +0.8                 | V    |

| "H" Level Input Voltage (except RES) | V               | 2.2                 |          | V .0.5               | V    |

| "H" Level Input Voltage (RES)        | V <sub>IH</sub> | 0.6*V <sub>CC</sub> | <u> </u> | V <sub>CC</sub> +0.5 | V    |

#### DC CHARACTERISTICS

$(V_{CC} = 5 \text{ V} \pm 10\%, \text{ Ta} = -40 \text{ to } 85^{\circ}\text{C})$

| Parameter                                        | Symbol                                | Condition                                | Min.                 | Max. | Unit |

|--------------------------------------------------|---------------------------------------|------------------------------------------|----------------------|------|------|

| "L" Level Output Voltage (CLK)                   | V <sub>OL</sub>                       | I <sub>OL</sub> = 4 mA                   | _                    | 0.4  | V    |

| "L" Level Output Voltage (Others)                | V <sub>OL</sub>                       | $I_{OL} = 2.5 \text{ mA}$                | _                    | 0.4  | V    |

| "H" Output Voltage (CLK)                         | V <sub>OH</sub>                       | I <sub>OH</sub> = -4 mA                  | V <sub>CC</sub> -0.4 | _    | ٧    |

| "H" Output Voltage (Others)                      | V <sub>OH</sub>                       | I <sub>OH</sub> = -1 mA                  | V <sub>CC</sub> -0.4 | _    | V    |

| RES Input Hysteresis                             | V <sub>IHR</sub><br>-V <sub>ILR</sub> |                                          | 0.2*V <sub>CC</sub>  | _    | V    |

| Input Leak Current<br>(Except <del>ASYNC</del> ) | lu                                    | $0 \leq V_{IN} \leq V_{CC}$              | -1                   | +1   | μА   |

| Input Current (ASYNC)                            | ILIA                                  | $0 \le V_{IN} \le V_{CC}$                | -100                 | +10  | μА   |

| Standby Supply Current                           | lccs                                  | Note 1                                   | _                    | 40   | μА   |

| Operating Supply Current                         | Icc                                   | $f = 24 \text{ MHz}, C_L = 0 \text{ PF}$ | _                    | 16   | mA   |

| Input Capacitance                                | C <sub>IN</sub>                       | f=1 MHz                                  | _                    | 7    | pF   |

Note:

1.  $X1 \ge V_{CC} - 0.2 \text{ V}, X2 \le 0.2 \text{ V}$

$F/C \ge V_{CC} - 0.2 \text{ V}$ , ASYNC =  $V_{CC}$  or open

$VIH \ge V_{CC} - 0.2 \text{ V}, VIL \le 0.2 \text{ V}$

#### **AC CHARACTERISTICS**

(1)

$(V_{CC} = 5 \text{ V} \pm 10\%, \text{ Ta} = -40 \text{ to } 85^{\circ}\text{C})$

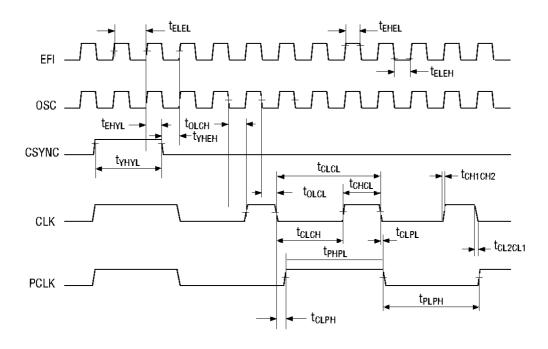

| Parameter                                                                                    | Symbol             | Min.                | Max. | Unit | Cor             | nditions                                |

|----------------------------------------------------------------------------------------------|--------------------|---------------------|------|------|-----------------|-----------------------------------------|

| EFI "H" Pulse Width                                                                          | t <sub>EHEL</sub>  | 13                  | _    | ns   | 90% to 90%      |                                         |

| EFI "L" Pulse Width                                                                          | t <sub>ELEH</sub>  | 17                  | _    | ns   | 10% to 10%      |                                         |

| EFI Cycle Time                                                                               | telel              | 36                  | _    | ns   | _               |                                         |

| Crystal Oscillator Frequency                                                                 | _                  | 6                   | 24   | MHz  | _               |                                         |

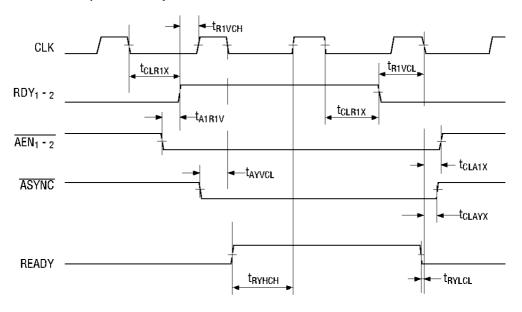

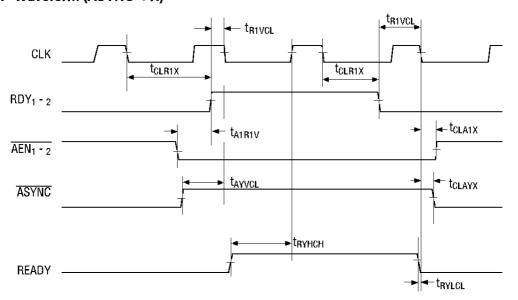

| Set up Time of RDY <sub>1</sub> or RDY <sub>2</sub> to CLK Falling Edge (Active)             | t <sub>R1VCL</sub> | 35                  | _    | ns   | ASYNC<br>= High |                                         |

| Set up Time of RDY <sub>1</sub> or RDY <sub>2</sub> to CLK Rising Edge (Active)              | t <sub>R1VCH</sub> | 35                  | _    | ns   | ASYNC<br>= Low  |                                         |

| Set up Time of RDY <sub>1</sub> or RDY <sub>2</sub> to CLK Falling Edge (Inactive)           | t <sub>R1VCL</sub> | 35                  | _    | ns   | _               |                                         |

| Hold Time of RDY <sub>1</sub> or RDY <sub>2</sub> to CLK Falling Edge                        | t <sub>CLR1X</sub> | 0                   | _    | ns   | _               | Output Load<br>Capacitance              |

| Set up Time of ASYNC to CLK Falling Edge                                                     | t <sub>AYVCL</sub> | 50                  | _    | ns   | _               | CLK output                              |

| Hold Time of ASYNC to<br>CLK Falling Edge                                                    | t <sub>CLAYX</sub> | 0                   | _    | ns   | _               | C <sub>L</sub> = 100 pF<br>Others 30 pF |

| Set up Time of $\overline{AEN}_1$ ( $\overline{AEN}_2$ ) to RDY $_1$ (RDY $_2$ ) Rising Edge | t <sub>A1R1V</sub> | 15                  | _    | ns   | _               |                                         |

| Hold Time of $\overline{\text{AEN}_1}$ ( $\overline{\text{AEN}_2}$ ) to CLK Falling Edge     | t <sub>CLA1X</sub> | 0                   | _    | ns   | _               |                                         |

| Set up Time of CSYNC to EFI<br>Rising Edge                                                   | t <sub>YHEH</sub>  | 20                  | _    | ns   | _               |                                         |

| Hold Time of CSYNC to EFI<br>Rising Edge                                                     | t <sub>EHYL</sub>  | 10                  | _    | ns   | _               |                                         |

| CSYNC Pulse Width                                                                            | t <sub>YHYL</sub>  | 2×t <sub>ELEL</sub> | _    | ns   | _               |                                         |

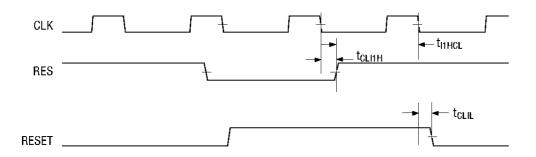

| Set up Time of RES to CLK Falling Edge                                                       | tinecl             | 65                  | _    | ns   | _               |                                         |

| Hold Time of RES to CLK Falling Edge                                                         | t <sub>CLI1H</sub> | 20                  |      | ns   | _               |                                         |

| Input Rising Edge Time                                                                       | t <sub>ILIH</sub>  |                     | 15   | ns   | _               |                                         |

| Input Falling Edge Time                                                                      | tiHIL              | _                   | 15   | ns   | _               |                                         |

Note: Parameters where timing has not been indicated in the above table are measured at  $V_L$  = 1.5 V and  $V_H$  = 1.5 V for both inputs and outputs.

#### **AC CHARACTERISTICS**

(2)

$(V_{CC} = 5 \text{ V} \pm 10\%, \text{ Ta} = -40 \text{ to } 85^{\circ}\text{C})$

| Parameter                                            | Symbol              | Con            | ditions                                 | Min.                                | Max. | Unit |

|------------------------------------------------------|---------------------|----------------|-----------------------------------------|-------------------------------------|------|------|

| CLK Cycle Time                                       | t <sub>CLCL</sub>   | _              |                                         | 125                                 | _    | пѕ   |

| CLK "H" Pulse Width                                  | t <sub>CHCL</sub>   | _              |                                         | $\frac{1}{3}$ T <sub>CLCL</sub> + 2 | _    | ns   |

| CLK "L" Pulse Width                                  | t <sub>CLCH</sub>   | _              |                                         | 2<br>3 T <sub>CLCL</sub> -15        | _    | ns   |

| CLK Rising and Falling Edge<br>Times                 | t <sub>CH1CH2</sub> | 1.0 V to 3.5 V |                                         | _                                   | 10   | ns   |

| PCLK "H" Pulse Width                                 | tphpl               | _              |                                         | T <sub>CLCL</sub> -20               | _    | ns   |

| PCLK "L" Pulse Width                                 | t <sub>PLPH</sub>   | _              |                                         | T <sub>CLCL</sub> -20               | _    |      |

| Time from READY Falling Edge<br>to CLK Falling Edge  | t <sub>RYLCL</sub>  | _              |                                         | -8                                  | _    | ns   |

| Time from READY Rising Edge to CLK Rising Edge       | t <sub>RYHCH</sub>  | _              | Output Load<br>Capacitance              | 2 T <sub>CLCL</sub> -15             | _    | ns   |

| Delay from CLK Falling Edge<br>to RESET Falling Edge | t <sub>CLIL</sub>   | _              | CLK Output                              | _                                   | 40   | ns   |

| Delay from CLK Falling Edge<br>to PCLK Rising Edge   | t <sub>CLPH</sub>   | _              | C <sub>L</sub> = 100 pF<br>Others 30 pF | _                                   | 22   | ns   |

| Delay from CLK Falling Edge<br>to PCLK Falling Edge  | t <sub>CLPL</sub>   | _              |                                         | _                                   | 22   | ns   |

| Delay from OSC Falling Edge<br>to CLK Rising Edge    | tolch               | _              |                                         | -5                                  | 22   | ns   |

| Delay from OSC Falling Edge<br>to CLK Falling Edge   | tolcl               | _              |                                         | 2                                   | 35   | ns   |

| Output Rising Edge Time<br>(Except CLK)              | toLOH               | 0.8 V to 2.2 V |                                         | _                                   | 15   | ns   |

| Output Falling Edge Time<br>(Except CLK)             | toHoL               | 2.2 V to 0.8 V |                                         | _                                   | 15   | ns   |

Note: Parameters where timing has not been indicated in the above table are measured at  $V_L$  = 1.5 V and  $V_H$  = 1.5 V for both inputs and outputs.

## PIN DESCRIPTION

| Pin Symbol                           | Name                                  | Input/Output | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------------------------|---------------------------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CSYNC                                | Clock<br>Synchronization<br>Single    | Input        | Synchronizing signal for output of in-phase CLK signals when more than one MSM82C84A-2 is used.  The internal counter is reset when this signal is at high level, and a high level CLK output is generated. The internal counter is subsequently activated and a 33% duty CLK output is generated when this signal is switched to low level.  When this signal is used, external synchronization of EFI is necessary. When the internal oscillator is used, it is necessary for this pin to be kept to be low level. |

| PCLK                                 | Peripheral Clock<br>Output            | Output       | This peripheral circuit clock signal is output in a 50% duty cycle at a frequency half that of the clock signal.                                                                                                                                                                                                                                                                                                                                                                                                     |

| AEN <sub>1</sub> AEN <sub>2</sub>    | Address Enable<br>Signals             | Input        | The AEN <sub>1</sub> signal enables RDY <sub>1</sub> , and the AEN <sub>2</sub> signal RDY <sub>2</sub> . The respective RDY inputs are activated when the level applied to these pins is low.  Although two separate inputs are used in multi-master systems, only the AEN which enables the RDY input to be used is to be switched to low level in the case of not using multi-master systems.                                                                                                                     |

| RDY <sub>1</sub><br>RDY <sub>2</sub> | Bus Ready<br>Signals                  | Input        | Completion of data bus reading and writing by the device connected to the system data bus is indicated when one of these signals is switched to high level.  The relevant RDY input is enables only when the corresponding AEN is at low level.                                                                                                                                                                                                                                                                      |

| READY                                | Ready Output                          | Output       | This signal is obtained by synchronizing the bus ready signal with CLK. This signal is output after guaranteeing the hold time for the CPU in phase with the RDY input.                                                                                                                                                                                                                                                                                                                                              |

| CLK                                  | Clock Output                          | Output       | This signal is the clock used by the CPU and peripheral devices connected to the CPU system data bus. The output waveform is generated in a 33% duty cycle at a frequency 1/3 the oscillating frequency of the crystal oscillator connected to the $X_1$ and $X_2$ pins, or at a frequency 1/3 the EFI input frequency.                                                                                                                                                                                              |

| RES                                  | Reset in                              | Input        | This low-level active input is used to generate a CPU reset signal. Since a Schmitt trigger is included in the input circuit for this signal, "power on resetting" can be achieved by connection of a simple RC circuit.                                                                                                                                                                                                                                                                                             |

| RESET                                | Reset Output                          | Output       | This signal is obtained by CLK synchronization of the input signal applied to RES and is output in opposite phase to the RES input. This signal is applied to the CPU as the system reset signal.                                                                                                                                                                                                                                                                                                                    |

| F/C                                  | Clock Select<br>Signal                | Input        | This signal selects the fundamental signal for generation of the CLK signal. The CLK is generated from the crystal oscillator output when this signal is at low level, and from the EFI input signal when at high level.                                                                                                                                                                                                                                                                                             |

| EFI                                  | External Clock<br>Signal              | Input        | The signal applied to this input pin generaters the CLK signal when F/C is at high level. The frequency of the input signal needs to be three times greater than the desired CLK frequency.                                                                                                                                                                                                                                                                                                                          |

| X <sub>1</sub> , X <sub>2</sub>      | Crystal Oscillator<br>Connecting Pins | Input        | Crystal oscillator connections. The crystal oscillator frequency needs to be three times greater than the desired CLK frequency.                                                                                                                                                                                                                                                                                                                                                                                     |

| OSC                                  | Crystal<br>Resonator<br>Output        | Output       | Crystal oscillator output. This output frequency is the same as the oscillating frequency of the oscillator connected to the $X_1$ and $X_2$ pins. As long as a Xtal oscillator is connected to the $X_1$ and $X_2$ pins, this output signal can be obtained independently even if F/C is set to high level to enable the EFI input to be used CLK generation purpose.                                                                                                                                               |

| Pin Symbol | Name                                      | Input/Output | Function                                                                                                                                                                                                                                                                                                                 |

|------------|-------------------------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ASYNC      | Ready<br>synchronization<br>select signal | Input        | Signal for selection of the synchronization mode of the READY signal generator circuit. When this signal is at low level, the READY signal is generated by double synchronization. And when at high level, the READY signal is generated by single synchronization. This pin is equipped with internal pull-up resistor. |

| $V_{CC}$   | _                                         | _            | +5 V power supply                                                                                                                                                                                                                                                                                                        |

| GND        | _                                         | _            | GND                                                                                                                                                                                                                                                                                                                      |

## **TIMING DIAGRAM**

#### **CLK • PCLK • OSC Waveforms**

#### **RESET Waveform**

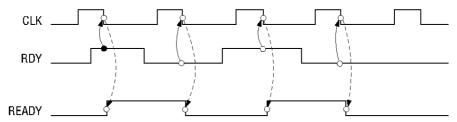

## READY Waveform (ASYNC = L)

## **READY Waveform (ASYNC = H)**

#### **OPERATIONAL DESCRIPTION**

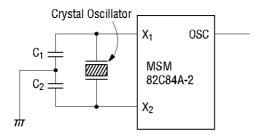

#### (1) Oscillator Circuit

The MSM82C84A-2 internal oscillator circuit can be driven by connecting a crystal oscillator to the  $X_1$  and  $X_2$  pins.

The frequency of the crystal oscillator in this case needs to be three times greater than the desired CLK frequency.

Since the oscillator circuit output (the same output as for the crystal resonator frequency) appears at the OSC pin, independent use of this output is also possible.

#### **Oscillator Circuit Example**

When input frequency is 6 to 15 MHz

$C_1 = C_2 = 33 \text{ pF}$

When input frequency is 15 to 24 MHz

$C_1 = C_2 = 10 \text{ pF}$

**Note:** Because Oscillator circuit and values depend on crystal oscillator characteristics, OKI recommends to make contact with crystal oscillator vendor to determine the best circuit and values for customers' application.

#### (2) Clock Generator Circuit

This circuit generates two clock outputs-CLK obtained by dividing the input external clock or crystal oscillator circuit output by three, and PCLK obtained by halving CLK. CLK and PCLK are generated from the external clock applied to the EFI pin when  $F/\overline{C}$  is at high level, and are generated from the crystal oscillator circuit when at low level.

#### (3) Reset Circuit

Since a Schmitt trigger circuit is used in the  $\overline{RES}$  input, the MSM82C84A-2 can be reset by "power on" by connection to a simple RC circuit. If the MSM80C86A-10 or MSM80C88A-10 is used as the CPU in this case, it is necessary to keep the  $\overline{RES}$  input at low level for at least 50 ms after Vcc reaches the 4.5V level.

#### (4) Ready Circuit

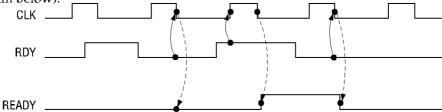

The READY signal generator circuit can be set to synchronization mode by ASYNC.

#### (i) When $\overline{ASYNC}$ is at low level

The RDY input is output as the READY signal by double synchronization. The high-level RDY input is synchronized once by the rising edge of the CLK of the first stage flip-flop (F1 in the circuit diagram), and then synchronized again by the falling edge of the CLK of the next stage flip-flop (F2 in the circuit diagram), resulting in output of a high-level READY output signal (see diagram below).

The low-level RDY input is synchronized directly by the falling-edge of the CLK of the next stage flip-flop, resulting in output of a low-level READY output signal (see diagram below).

# (ii) When ASYNC is at high level The RDY input is output as the READY signal by single synchronization.

Both low-level and high-level RDY inputs are synchronized by the falling edge of the CLK of the next stage flip-flop, resulting output of respective low-level and high-level READY output signals (see diagram below).

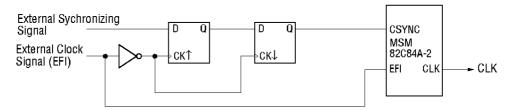

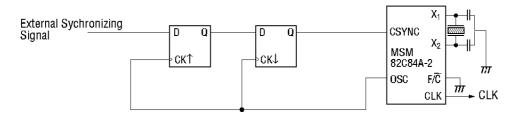

## **EXAMPLE OF USE (CSYNC)**

The MSM82C84A-21/3 frequency divider counter is unsettled when the power is switched on. Therefore, the CSYNC pin has been included to synchronize CLK with another signal. When CSYNC is at high level, both CLK and PCLK are high-level outputs. If CSYNC is then switched to low level, CLK is output from the next input clock rising edge, and is divided by 3.

If CSYNC has not been synchronized with the input clock, use the following circuit to achieve the required synchronization

When an external clock EFI is used as the clock source

When the crystal oscillator is used as the clock source

#### **NOTES ON USE**

The MSM82C84A-2 cannot be used if the MSM80C86A-10 or MSM80C88A-10 is used within the range of 8 MHz < operating frequency  $\leq$  10 MHz.

#### NOTICE ON REPLACING LOW-SPEED DEVICES WITH HIGH-SPEED DEVICES

The conventional low speed devices are replaced by high-speed devices as shown below. When you want to replace your low speed devices with high-speed devices, read the replacement notice given on the next pages.

| High-speed device (New) | Low-speed device (Old) | Remarks         |

|-------------------------|------------------------|-----------------|

| M80C85AH                | M80C85A/M80C85A-2      | 8bit MPU        |

| M80C86A-10              | M80C86A/M80C86A-2      | 16bit MPU       |

| M80C88A-10              | M80C88A/M80C88A-2      | 8bit MPU        |

| M82C84A-2               | M82C84A/M82C84A-5      | Clock generator |

| M81C55-5                | M81C55                 | RAM.I/O, timer  |

| M82C37B-5               | M82C37A/M82C37A-5      | DMA controller  |

| M82C51A-2               | M82C51A                | USART           |

| M82C53-2                | M82C53-5               | Timer           |

| M82C55A-2               | M82C55A-5              | PPI             |

#### Differences between MSM82C84A and MSM82C84A-5/MSM82C84A-2

#### 1) Manufacturing Process

All these devices use a 3  $\mu$  Si-Gate CMOS process technology.

The chip size of these devices is same.

The chip of the MSM82C84A-5 is entirely identical to that of the MSM82C84A-2.

#### 2) Functions

| Item                             | MSM82C84A                                                          | MSM82C84A-5/-2                                                       |  |

|----------------------------------|--------------------------------------------------------------------|----------------------------------------------------------------------|--|

| Internal processing of ASYNC pin | Internal processing of ASYNC pin Normal CMOS input pin             |                                                                      |  |

| Notes on use                     | The pin should have a pullup or pulldown resistor if it is unused. | The value of pulldown resistor (when used) is limited. (See page 3.) |  |

#### 3) Electrical Characteristics

#### 3-1) DC Characteristics

| Parameter                                   | Symbol        | MSM82C84A              | MSM82C84A-5/-2            |

|---------------------------------------------|---------------|------------------------|---------------------------|

| "L"Level Output Voltage (CLK)               | Vol           | 0.45 V maximum (+5 mA) | 0.40 V maximum (+4 mA)    |

| "L"Level Output Voltage<br>(Other than CLK) | Vol           | 0.45 V maximum (+5 mA) | 0.40 V maximum (+2.5 mA)  |

| "H"Level Output Voltage (CLK)               | Vон           | 3.7 V minimum (-1 mA)  | Vcc-0.1 V minimum (-4 mA) |

| "H"Level Output Voltage<br>(Other than CLK) | Voн           | 3.7 V minimum (-1 mA)  | Vcc-0.1 V minimum (-1 mA) |

| RES Input Hysteresis Width                  | VIHR-<br>VILR | 0.25 V minimum         | 0.2 × Vcc min             |

| Input Current (ASYNC)                       | ILIA          | -10 μA to +10 μA       | -100 μA~+10 μA            |

| Input Leak Current                          | lLi           | -10 μA to +10 μA       | -1 μA~+1 μA               |

| Supply Current (Standby)                    | lccs          | 100 μA maximum         | 40 μA maximum             |

As shown above, the MSM82C84A-5/MSM82C84A-2 satisfies the characteristics (except for  $V_{\text{OL}}$  and input current (ASYNC) of the MSM82C84A.

#### 3-2) AC Charasteristics

## 1) MSM82C84A and MSM82C84A-2

| Parameter                   | Symbol  | MSM82C84A      | MSM82C84A-2              |  |

|-----------------------------|---------|----------------|--------------------------|--|

| Input Rise Time             | tiLiH   | 20 ns maximum  | 15 ns maximum            |  |

| Input Fall Time             | tilih   | 20 ns maximum  | 15 ns maximum            |  |

| CLK High Time               | tchcl   | 65 ns minimum  | 1/3 tclcl +2 ns minimum  |  |

| CLK Low Time                | tclch   | 119 ns minimum | 2/3 tolol -15 ns minimum |  |

| CLK Rise/Fall Time          | tcH1CH2 | 15 ns maximum  | 10 ns maximum            |  |

| GLK RISE/FAII TITTE         | tcl1cl2 | 15 IIS MAXIMUM | TO IIS IIIAXIIIIUIII     |  |

| PCLK High Time              | tphpl   | 180 ns minimum | tolol -20 ns minimum     |  |

| PCLK Low Time               | tplph   | 180 ns minimum | tolol -20 ns minimum     |  |

| READY Falling to CLK Rising | trynch  | 114 ns minimum | 2/3 tolol -15 ns minimum |  |

As shown above, the MSM82C84A-2 satisfies the characteristics (except for Input Rise/Fall Time) of the MSM82C84A.

#### 1) MSM82C84A-5 and MSM82C84A-2

| Parameter         | Symbol | MSM82C84A-5    | MSM82C84A-2    |

|-------------------|--------|----------------|----------------|

| EFI High Time     | tehel  | 20 ns minimum  | 13 ns minimum  |

| EFI Low Time      | teleh  | 20 ns minimum  | 17 ns minimum  |

| EFI Period        | telel  | 66 ns minimum  | 36 ns minimum  |

| Crystal Frequency | _      | 15 MHz maximum | 24 MHz maximum |

| CLK Period        | tchcl  | 200 ns minimum | 125 ns minimum |

As shown above, the MSM82C84A-2 satisfies the characteristics of the MSM82C84A-5.

#### 4) Notices on use

Note the following when replacing devices as the ASYNC pin is differently treated between the MSM82C84A and the MSM82C84A-5/MSM82C84A-2:

Case 1: When only a pullup resistor is externally connected to. The MSM82C84A can be replaced by the MSM82C84A-2.

Case 2: When only pulldown resistor is externally connected to.

When the pulldown resistor is 8 kiloohms or less, the MSM82C84A can be replaced by the MSM82C84A-2.

When the pulldown resistor is greater than 8 kiloohms, use a pulldown resistor of 8 kiloohms or less.

Case 3: When an output of the other IC device is connected to the device.

The MSM82C84A can be replaced by the MSM82C84A-2 when the  $I_{OL}$  pin of the device to drive the  $\overline{ASYNC}$  pin of the MSM82C84A-2 has an allowance of 100  $\mu A$  or more.

#### **PACKAGE DIMENSIONS**

(Unit: mm)

Notes for Mounting the Surface Mount Type Package

The SOP, QFP, TSOP, SOJ, QFJ (PLCC), SHP and BGA are surface mount type packages, which are very susceptible to heat in reflow mounting and humidity absorbed in storage.

Therefore, before you perform reflow mounting, contact Oki's responsible sales person for the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).

QFJ20-P-S350-1.27 4.35± 0.2 2.**55** TYP. ® 4 08.97 ± 0.08 0.91± 0.13 5 1 1 1 9 88. INDEX MARK Spherical surface (a) (8) 0.55 MIN. 1.27 0.81MAX. SEATING PLANE 0.41± 0.1 **⊕**10.18⊕ Package material Epoxy resin  $7.88 \pm 0.25$ Lead frame material Cu alloy Pin treatment Solder plating Solder plate thickness 5 μm or more 0.59 TYP. Package weight (g)

(Unit: mm)

Notes for Mounting the Surface Mount Type Package

The SOP, QFP, TSOP, SOJ, QFJ (PLCC), SHP and BGA are surface mount type packages, which are very susceptible to heat in reflow mounting and humidity absorbed in storage.

Therefore, before you perform reflow mounting, contact Oki's responsible sales person for the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).

SOP24-P-430-1.27-K  $15.95 \pm 0.1$ (24) 12.0 ± 0.5 <u></u> ±6.7 0.2 +0.1  $2.05 \pm 0.3$ INDEX MARK Mirror finish 0.99 TYP 1.27 0,35 ± 0,1 <del>(0</del>0.25) 0~10° 0~0.3 1.2 ± 0.2 1.23 TYP. SEATING PLANE Package material Epoxy resin Lead frame material 42 alloy Pin treatment Solder plating Solder plate thickness 5 μm or more 0.58 TYP. Package weight (g)

(Unit: mm)

Notes for Mounting the Surface Mount Type Package

The SOP, QFP, TSOP, SOJ, QFJ (PLCC), SHP and BGA are surface mount type packages, which are very susceptible to heat in reflow mounting and humidity absorbed in storage.

Therefore, before you perform reflow mounting, contact Oki's responsible sales person for the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).