July 1998

# NM93C56 2048-Bit Serial EEPROM (MICROWIRE<sup>™</sup> Bus Interface)

## **General Description**

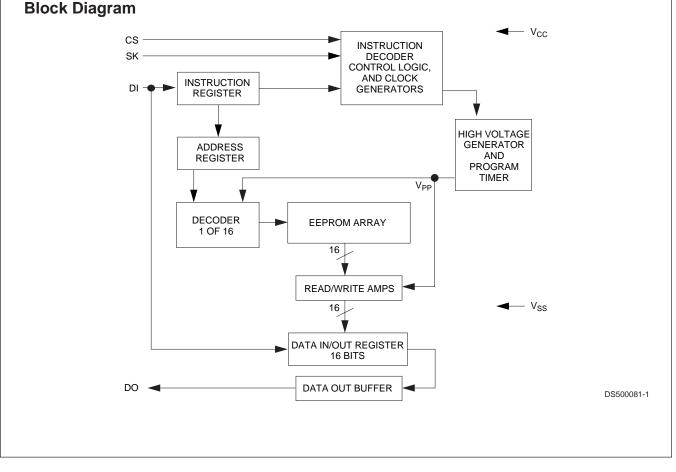

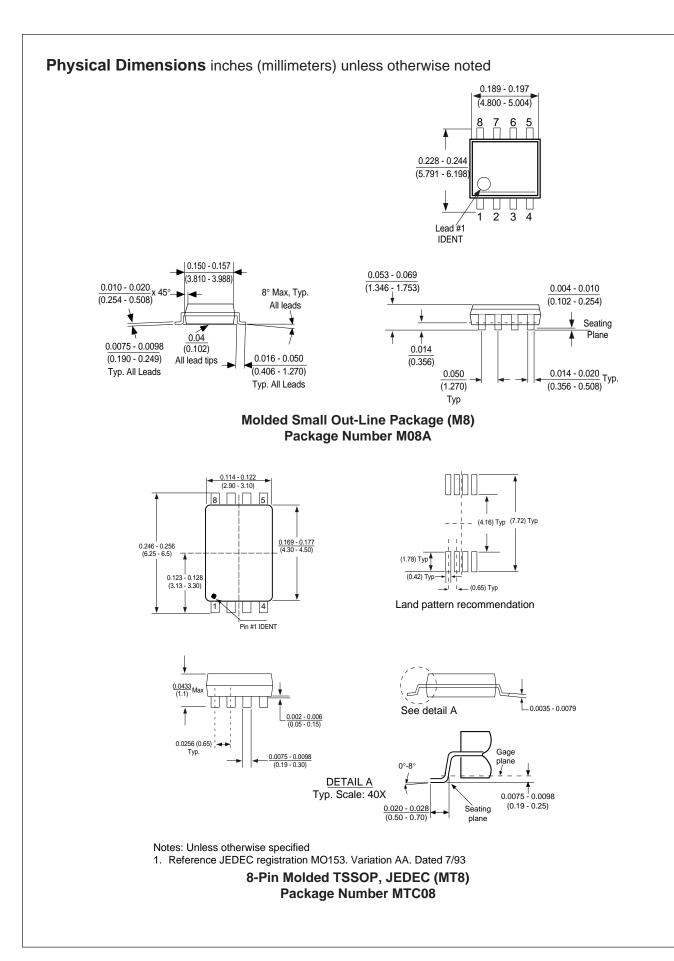

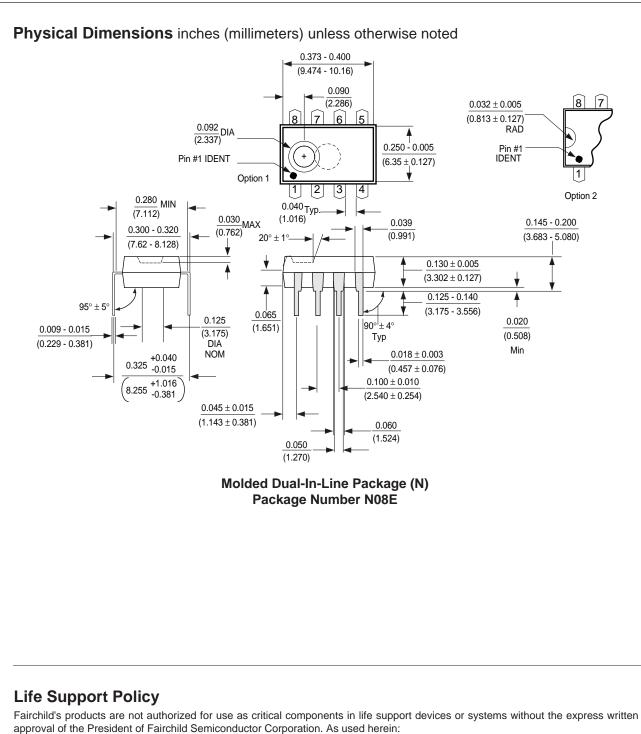

The NM93C56 devices are 2048 bits of CMOS non-volatile electrically erasable memory divided into 128 16-bit registers. They are fabricated using Fairchild Semiconductor's floating-gate CMOS process for high reliability, high endurance and low power consumption. These memory devices are available in an 8-pin SOIC or 8-pin TSSOP package for small space considerations.

The serial interface that operates this EEPROM is MICROWIRE compatible for simple interface to standard microcontrollers and microprocessors. There are 7 instructions which control this device: Read, Write Enable, Erase, Erase All, Write, Write All, and Write Disable. The ready/busy status is available on the DO pin to indicate the completion of a programming cycle.

## Features

- Device status during programming mode

- Typical active current of 200μA

10μA standby current typical

1μA standby current typical (L)

0.1μA standby current typical (LZ)

- No erase required before write

- Reliable CMOS floating gate technology

- 2.7V to 5.5V operation in all modes

- MICROWIRE compatible serial I/O

- Self-timed programming cycle

- 40 years data retention

- Endurance: 1,000,000 data changes

- Packages available: 8-pin SO, 8-pin DIP, 8-pin TSSOP

- Schmitt Trigger inputs and V<sub>CC</sub> lock-out to prevent data corruption.

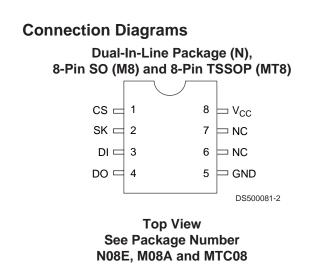

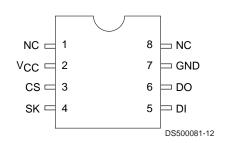

#### Rotated Die (93C56T)

#### **Pin Names**

| CS              | Chip Select        |

|-----------------|--------------------|

| SK              | Serial Data Clock  |

| DI              | Serial Data Input  |

| DO              | Serial Data Output |

| GND             | Ground             |

| V <sub>CC</sub> | Power Supply       |

|                 |                    |

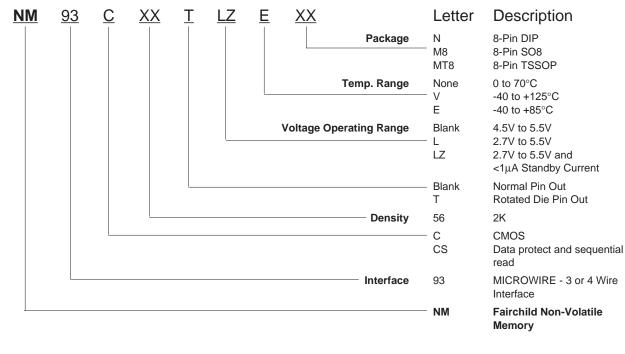

## **Ordering Information**

## Absolute Maximum Ratings (Note 1) Operating Range

| Ambient Storage Temperature                           | –65°C to +150°C |

|-------------------------------------------------------|-----------------|

| All Input or Output Voltage<br>with Respect to Ground | +6.5V to -0.3V  |

| Lead Temperature (Soldering, 10 sec.)                 | +300°C          |

| ESD Rating                                            | 2000V           |

| Ambient Operating Temperature   |                 |

|---------------------------------|-----------------|

| NM93C56                         | 0°C to +70°C    |

| NM93C56E                        | -40°C to +85°C  |

| NM93C56V                        | -40°C to +125°C |

| Power Supply (V <sub>CC</sub> ) | 4.5V to 5.5V    |

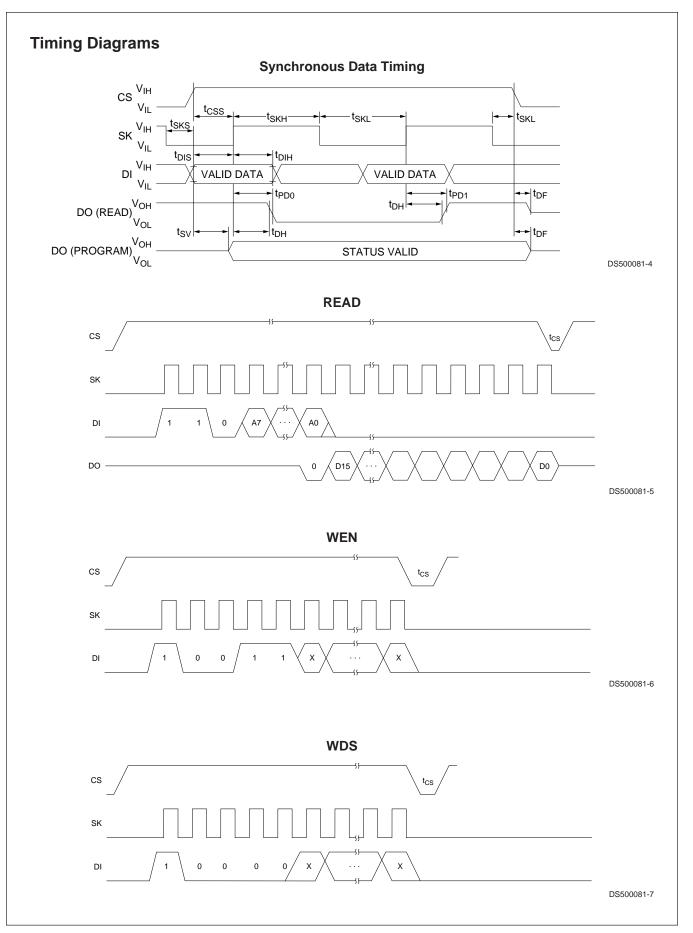

# Standard $V_{CC}$ (4.5V to 5.5V) DC and AC Electrical Characteristics

| Symbol                               | Parameter                                 | Part Number                                                                  | Conditions                                           | Min.                 | Max.                      | Units  |

|--------------------------------------|-------------------------------------------|------------------------------------------------------------------------------|------------------------------------------------------|----------------------|---------------------------|--------|

| I <sub>CCA</sub>                     | Operating Current                         |                                                                              | CS = V <sub>IH</sub> , SK = 1MHz                     |                      | 1                         | mA     |

| I <sub>CCS</sub>                     | Standby Current                           |                                                                              | $CS = V_{IL}$                                        |                      | 50                        | μΑ     |

| I <sub>IL</sub><br>I <sub>OL</sub>   | Input Leakage<br>Output Leakage           |                                                                              | V <sub>IN</sub> = 0V to V <sub>CC</sub><br>(Note 2)  |                      | ±1                        | μΑ     |

| V <sub>IL</sub><br>V <sub>IH</sub>   | Input Low Voltage<br>Input High Voltage   |                                                                              |                                                      | -0.1<br>2            | 0.8<br>V <sub>CC</sub> +1 | V      |

| V <sub>OL1</sub><br>V <sub>OH1</sub> | Output Low Voltage<br>Output High Voltage |                                                                              | I <sub>OL</sub> = 2.1mA<br>I <sub>OH</sub> = -400 μA | 2.4                  | 0.4                       | V<br>V |

| V <sub>OL2</sub><br>V <sub>OH2</sub> | Output Low Voltage<br>Output High Voltage |                                                                              | I <sub>OL</sub> = 10 μA<br>I <sub>OH</sub> = -10 μA  | V <sub>CC</sub> -0.2 | 0.2                       | V<br>V |

| f <sub>SK</sub>                      | SK Clock Frequency                        |                                                                              | (Note 3)                                             | 0                    | 1                         | MHz    |

| t <sub>SKH</sub>                     | SK High Time                              | NM93C56<br>NM93C56E/V                                                        |                                                      | 250<br>300           |                           | ns     |

| t <sub>SKL</sub>                     | SK Low Time                               |                                                                              |                                                      | 250                  |                           | ns     |

| t <sub>SKS</sub>                     | SK Setup Time                             | SK must be at V <sub>IL</sub> for<br>t <sub>SKS</sub> before CS goes<br>high |                                                      | 50                   |                           | ns     |

| t <sub>cs</sub>                      | Minimum CS<br>Low Time                    |                                                                              | (Note 4)                                             | 250                  |                           | ns     |

| t <sub>css</sub>                     | CS Setup Time                             |                                                                              |                                                      | 50                   |                           | ns     |

| t <sub>DH</sub>                      | DO Hold Time                              |                                                                              |                                                      | 70                   |                           | ns     |

| t <sub>DIS</sub>                     | DI Setup Time                             | NM93C56<br>NM93C56E/V                                                        |                                                      | 100<br>200           |                           | ns     |

| t <sub>CSH</sub>                     | CS Hold Time                              |                                                                              |                                                      | 0                    |                           | ns     |

| t <sub>DIH</sub>                     | DI Hold Time                              |                                                                              |                                                      | 20                   |                           | ns     |

| t <sub>PD1</sub>                     | Output Delay to "1"                       |                                                                              |                                                      |                      | 500                       | ns     |

| t <sub>PD0</sub>                     | Output Delay to "0"                       |                                                                              |                                                      |                      | 500                       | ns     |

| t <sub>SV</sub>                      | CS to Status Valid                        |                                                                              |                                                      |                      | 500                       | ns     |

| t <sub>DF</sub>                      | CS to DO in<br>TRI-STATE                  |                                                                              | CS = V <sub>IL</sub>                                 |                      | 100                       | ns     |

| t <sub>WP</sub>                      | Write Cycle Time                          |                                                                              |                                                      |                      | 10                        | ms     |

## Absolute Maximum Ratings (Note 1)

| Ambient Storage Temperature                           | –65°C to +150°C |

|-------------------------------------------------------|-----------------|

| All Input or Output Voltage<br>with Respect to Ground | +6.5V to -0.3V  |

| Lead Temperature (Soldering, 10 sec.)                 | +300°C          |

| ESD Rating                                            | 2000V           |

## **Operating Range**

| Ambient Operating Temperature   |                 |

|---------------------------------|-----------------|

| NM93C56L/LZ                     | 0°C to +70°C    |

| NM93C56LE/LZE                   | -40°C to +85°C  |

| NM93C56LV/LZV                   | -40°C to +125°C |

| Power Supply (V <sub>CC</sub> ) | 2.7V to 5.5V    |

## Low $V_{CC}$ (2.7V to 5.5V) DC and AC Electrical Characteristics

| Symbol                             | Parameter Part Number Conditions          |  | Conditions                                                             | Min.                        | Max.                                       | Units    |  |

|------------------------------------|-------------------------------------------|--|------------------------------------------------------------------------|-----------------------------|--------------------------------------------|----------|--|

| I <sub>CCA</sub>                   | Operating Current                         |  | CS = V <sub>IH</sub> , SK = 250KHz                                     |                             | 1                                          | mA       |  |

| I <sub>CCS</sub>                   | Standby Current<br>L<br>LZ                |  | CS = V <sub>IL</sub>                                                   |                             | 10<br>1                                    | μA<br>μA |  |

| I <sub>IL</sub><br>I <sub>OL</sub> | Input Leakage<br>Output Leakage           |  | V <sub>IN</sub> = 0V to V <sub>CC</sub><br>(Note 2)                    |                             | ±1                                         | μA       |  |

| V <sub>IL</sub><br>V <sub>IH</sub> | Input Low Voltage<br>Input High Voltage   |  |                                                                        | -0.1<br>0.8 V <sub>CC</sub> | 0.15 V <sub>CC</sub><br>V <sub>CC</sub> +1 | V        |  |

| V <sub>OL</sub><br>V <sub>OH</sub> | Output Low Voltage<br>Output High Voltage |  | I <sub>OL</sub> = 10 μA<br>I <sub>OH</sub> = -10 μA                    | 0.9 V <sub>CC</sub>         | 0.1 V <sub>CC</sub>                        | V<br>V   |  |

| f <sub>SK</sub>                    | SK Clock Frequency                        |  | (Note 3)                                                               | 0                           | 1                                          | MHz      |  |

| t <sub>sĸH</sub>                   | SK High Time                              |  |                                                                        | 1                           |                                            | μs       |  |

| t <sub>SKL</sub>                   | SK Low Time                               |  |                                                                        | 1                           |                                            | μs       |  |

| t <sub>SKS</sub>                   | SK Setup Time                             |  | SK must be at $V_{\text{IL}}$ for $t_{\text{SKS}}$ before CS goes high | 0.2                         |                                            | μs       |  |

| t <sub>CS</sub>                    | Minimum CS<br>Low Time                    |  | (Note 4)                                                               | 1                           |                                            | μs       |  |

| t <sub>CSS</sub>                   | CS Setup Time                             |  |                                                                        | 0.2                         |                                            | μs       |  |

| t <sub>DH</sub>                    | DO Hold Time                              |  |                                                                        | 70                          |                                            | ns       |  |

| t <sub>DIS</sub>                   | DI Setup Time                             |  |                                                                        | 0.4                         |                                            | μs       |  |

| t <sub>CSH</sub>                   | CS Hold Time                              |  |                                                                        | 0                           |                                            | μs       |  |

| t <sub>DIH</sub>                   | DI Hold Time                              |  |                                                                        | 0.4                         |                                            | μs       |  |

| t <sub>PD1</sub>                   | Output Delay to "1"                       |  |                                                                        |                             | 2                                          | μs       |  |

| t <sub>PD0</sub>                   | Output Delay to "0"                       |  |                                                                        |                             | 2                                          | μs       |  |

| t <sub>SV</sub>                    | CS to Status Valid                        |  |                                                                        |                             | 1                                          | μs       |  |

| t <sub>DF</sub>                    | CS to DO in<br>TRI-STATE                  |  | CS = V <sub>IL</sub>                                                   |                             | 0.4                                        | μs       |  |

| t <sub>WP</sub>                    | Write Cycle Time                          |  |                                                                        |                             | 15                                         | ms       |  |

## **Capacitance** $T_A = 25^{\circ}C$ , f = 1 MHz (Note 5)

| Symbol           | Test               | Тур | Max | Units |

|------------------|--------------------|-----|-----|-------|

| C <sub>OUT</sub> | Output Capacitance |     | 5   | pF    |

| C <sub>IN</sub>  | Input Capacitance  |     | 5   | pF    |

Note 1: Stress above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of the specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Note 2: Typical leakage values are in the 20nA range.

Note 3: The shortest allowable SK clock period =  $1/f_{SK}$  (as shown under the  $f_{SK}$  parameter). Maximum SK clock speed (minimum SK period) is determined by the interaction of several AC parameters stated in the datasheet. Within this SK period, both  $t_{SK4}$  and  $t_{SK4}$ . Imits must be observed. Therefore, it is not allowable to set  $1/f_{SK} = t_{SK4}$ -minimum, for shorter SK cycle time operation. Note 4: CS (Chip Select) must be brought low (to  $V_{IL}$ ) for an interval of  $t_{CS}$  in order to reset all

Note 4: CS (Chip Select) must be brought low (to  $V_{ll}$ ) for an interval of  $t_{CS}$  in order to reset all internal device registers (device reset) prior to beginning another opcode cycle. (This is shown in the opcode diagram on the following page.)

Note 5: This parameter is periodically sampled and not 100% tested.

## **AC Test Conditions**

| V <sub>CC</sub> Range                                   | V <sub>IL</sub> /V <sub>IH</sub><br>Input Levels | V <sub>IL</sub> /V <sub>IH</sub><br>Timing Level | V <sub>oL</sub> /V <sub>он</sub><br>Timing Level | I <sub>oL</sub> /I <sub>он</sub> |  |  |

|---------------------------------------------------------|--------------------------------------------------|--------------------------------------------------|--------------------------------------------------|----------------------------------|--|--|

| $2.7V \le V_{CC} \le 5.5V$<br>(Extended Voltage Levels) | .03V/1.8V                                        | 1.0V                                             | 0.8V/1.5V                                        | ±10μA                            |  |  |

| $4.5V \le V_{CC} \le 5.5V$                              | 0.4V/2.4V                                        | 1.0V/2.0V                                        | 0.4V/2.4V                                        | -2.1mA/0.4mA                     |  |  |

| (TTL Levels)                                            |                                                  |                                                  |                                                  |                                  |  |  |

| Output Load: 1 TTL Gate ( $C_L = 100 \text{ pF}$ )      |                                                  |                                                  |                                                  |                                  |  |  |

## **Functional Description**

The NM93C56 device has 7 instructions as described below. Note that the MSB of any instruction is a "1" and is viewed as a start bit in the interface sequence. The next 10 bits carry the op code and the 8-bit address for register selection.

#### Read (READ):

The READ instruction outputs serial data on the D0 pin. After a READ instruction is received, the instruction and address are decoded, followed by data transfer from the selected memory register into a 16-bit serial-out shift register. A dummy bit (logical 0) precedes the 16-bit data output string. Output data changes are initiated by a low to high transition of the SK clock.

#### Write Enable (WEN):

When V<sub>CC</sub> is applied to the part, it 'powers-up' in the Write Disable (WDS) state. Therefore, all programming modes must be preceded by a Write Enable (WEN) instruction. Once a Write Enable instruction is executed, programming remains enabled until aWrite Disable (WDS) instruction is executed or V<sub>CC</sub> is removed from the part.

#### Erase (ERASE):

The ERASE instruction will program all bits in the specified register to the logical "1" state. CS is brought low following the loading of the last address bit. This falling edge of the CS pin initiates the self-timed programming cycle.

The DO pin indicates the READY/BUSY status of the chip if CS is brought high after a minimum of 250 ns ( $t_{CS}$ ). DO = logical "0" indicates that the register, at the address specified in the instruction, has been erased, and the part is ready for another instruction.

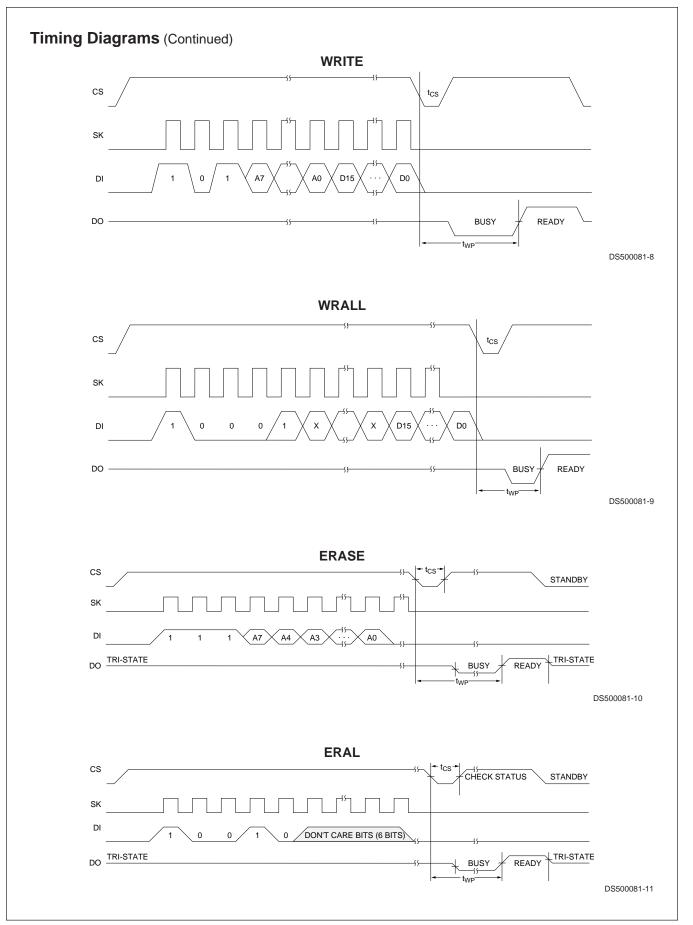

## Write (WRITE):

The WRITE instruction is followed by the 16 bits of data to be written into the specified address. After the last bit of data is put in the datain (DI) pin, CS must be brought low before the next rising edge of the SK clock. This falling edge of the CS initiates the self-timed programming cycle. The D0 pin indicates the READY/BUSY status of the chip if CS is brought high after a minimum of 250 ns ( $t_{CS}$ ). D0 = logical 1 indicates that the register at the address specified in the instruction has been written with the data pattern specified in the instruction and the part is ready for another instruction.

#### Erase All (ERAL):

The ERAL instruction will simultaneously program all registers in the memory array and set each bit to the logical "1" state. The Erase All cycle is identical to the ERASE cycle except for the different opcode. As in the ERASE mode, the DO pin indicates the READY/BUSY status of the chip if CS is brought high after the  $t_{CS}$  interval.

#### Write All (WRALL):

The WRALL instruction will simultaneously program all registers with the data pattern specified in the instruction. As in the WRITE mode, the DO pin indicates the READY/BUSY status of the chip if CS is brought high after the  $t_{CS}$  interval.

### Write Disable (WDS):

To protect against accidental data disturb, the WDS instruction disables all programming modes and should follow all programming operations. Execution of a READ instruction is independent of both the WEN and WDS instructions.

Note: The Fairchild CMOS EEPROMs do not require an "ERASE" or "ERASE ALL" operation prior to the "WRITE" and "WRITE ALL" instructions. The "ERASE" and "ERASE ALL" instructions are included to maintain compatibility with earlier technology EEPROMs.

| Instruction | SB | Op. Code | Address  | Data   | Comments                                           |

|-------------|----|----------|----------|--------|----------------------------------------------------|

| READ        | 1  | 10       | A7-A0    |        | Reads data stored in memory, at specified address. |

| WEN         | 1  | 00       | 11xxxxxx |        | Write enable must precede all programming modes.   |

| ERASE       | 1  | 11       | A7-A0    |        | Erase selected register.                           |

| WRITE       | 1  | 01       | A7-A0    | D15-D0 | Writes selected register.                          |

| ERAL        | 1  | 00       | 10xxxxxx |        | Erases all registers.                              |

| WRALL       | 1  | 00       | 01xxxxxx | D15-D0 | Writes all registers.                              |

| WDS         | 1  | 00       | 00xxxxxx |        | Disables all programming instructions.             |

## Instruction Set for the NM93C56

Note: A7 is "don't care."

Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

Fairchild Semiconductor Fairchild Semiconductor Americas Customer Response Center Europe +44 (0) 1793-856858 Fax Deutsch Tel. 1-888-522-5372 Tel: +49 (0) 8141-6102-0 English Français Tel +44 (0) 1793-856856 +33 (0) 1-6930-3696 +39 (0) 2-249111-1 Tel: Italiano Tel

Fairchild Semiconductor Hong Kong 8/F, Room 808, Empire Centre 68 Mody Road, Tsimshatsui East Kowloon. Hong Kong Tel; +852-2722-8388 Fax: +852-2722-8383 Fairchild Semiconductor Japan Ltd. 4F, Natsume Bldg. 2-18-6, Yushima, Bunkyo-ku Tokyo, 113-0034 Japan Tel: 81-3-3818-8840 Fax: 81-3-3818-8841

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications

9