# Low-Voltage 1:20 Differential ECL/PECL Clock Driver

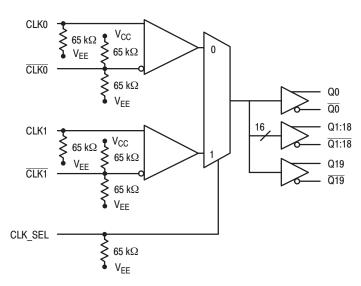

The MC100EP221 is a low skew 1–to–20 differential driver, designed with clock distribution in mind. It accepts two clock sources into an input multiplexer. The input signals can be either differential or single–ended if the  $V_{BB}$  output is used. The selected signal is fanned out to 20 identical differential outputs.

- 270ps max. Part-to-Part Skew

- 50ps max. Output-to-Output Skew

- Differential Design

- V<sub>BB</sub> Output

- Voltage and Temperature Compensated Outputs

- Supports 3.3V and 2.5V, ECL and PECL Operation

- Supports HSTL and PECL Clock Systems

The EP221 is specifically designed, modeled and produced with low skew as the key goal. Optimal design and layout serve to minimize gate—to—gate skew within a device, and empirical modeling is used to determine process control limits that ensure consistent  $t_{pd}$  distributions from lot to lot. The net result is a dependable, guaranteed low skew device.

To ensure that the tight skew specification is met it is necessary that both sides of the differential output are terminated into  $50\Omega$ , even if only one side is being used. In most applications, all ten differential pairs will be used and therefore terminated. In the case where fewer than ten pairs are used, it is necessary to terminate at least the output pairs on the same package side as the pair(s) being used on that side, in order to maintain minimum skew. Failure to do this will result in small degradations of propagation delay (on the order of 10–20ps) of the output(s) being used which, while not being catastrophic to most designs, will mean a loss of skew margin.

#### MC100EP221

See Upgrade Product - MC100ES6221

LOW-VOLTAGE 1:20 DIFFERENTIAL ECL/PECL CLOCK DRIVER

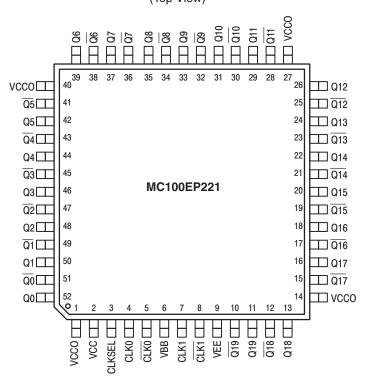

TB SUFFIX 52-LEAD LQFP PACKAGE EXPOSED PAD CASE 1336

The MC100EP221, as with most other ECL devices, can be operated from a positive  $V_{CC}$  supply in PECL mode. This allows the EP221 to be used for high performance clock distribution in +3.3V or +2.5V systems. Designers can take advantage of the EP221's performance to distribute low skew clocks across the backplane. In a PECL environment, series or Thevenin line terminations are typically used as they require no additional power supplies.

Rev 1

## Pinout: 52-Lead LQFP (Top View)

#### **FUNCTION**

| CLK_SEL | Active Input                           |

|---------|----------------------------------------|

| 0       | CLK0, <u>CLK0</u><br>CLK1, <u>CLK1</u> |

#### **LOGIC SYMBOL**

**Table 1: PIN CONFIGURATION**

| Pin                                | I/O    | Туре               | Function                                                                                                                              |

|------------------------------------|--------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| CLK0, CLK0                         | Input  | ECL/LVPECL         | Differential reference clock signal input                                                                                             |

| CLK1, CLK1                         | Input  | ECL/LVPECL or HSTL | Alternative differential reference clock signal input                                                                                 |

| CLK_SEL                            | Input  | LVPECL             | Output frequency divider select                                                                                                       |

| Q[0-19], Q[0-19]                   | Output | LVPECL             | Differential clock outputs                                                                                                            |

| VEE <sup>a</sup>                   | Supply |                    | Negative power supply                                                                                                                 |

| V <sub>CC</sub> , V <sub>CCO</sub> | Supply |                    | Positive power supply. All $V_{CC}$ and $V_{CCO}$ pins must be connected to the positive power supply for correct DC and AC operation |

| VBB                                | Output |                    | DC bias output for single ended input operation                                                                                       |

a. In ECL mode (negative power supply mode), VEE is either -3.3V or -2.5V and VCC is connected to GND (0V).

In PECL mode (positive power supply mode), VEE is connected to GND (0V) and VCC is either +3.3V or +2.5V.

In both modes, the input and output levels are referrenced to the most positive supply (VCC).

Table 2: ABSOLUTE MAXIMUM RATINGS<sup>a</sup>

| Symbol           | Characteristics     | Min  | Max                  | Unit | Condition |

|------------------|---------------------|------|----------------------|------|-----------|

| V <sub>CC</sub>  | Supply Voltage      | -0.3 | 4.6                  | V    |           |

| V <sub>IN</sub>  | DC Input Voltage    | -0.3 | V <sub>CC</sub> +0.3 | V    |           |

| V <sub>OUT</sub> | DC Output Voltage   | -0.3 | V <sub>CC</sub> +0.3 | V    |           |

| I <sub>IN</sub>  | DC Input Current    |      | ±20                  | mA   |           |

| I <sub>OUT</sub> | DC Output Current   |      | ±50                  | mA   |           |

| T <sub>S</sub>   | Storage temperature | -65  | 125                  | °C   |           |

a. Absolute maximum continuos ratings are those maximum values beyond which damage to the device may occur. Exposure to these conditions

or conditions beyond those indicated may adversely affect device reliability. Functional operation at absolute-maximum-rated conditions is not

implied.

#### **Table 3: GENERAL SPECIFICATIONS**

| Symbol          | Characteristics                        | Min            | Тур                                      | Max | Unit | Condition |

|-----------------|----------------------------------------|----------------|------------------------------------------|-----|------|-----------|

| V <sub>TT</sub> | Output termination voltage             |                | V <sub>CC</sub> - 2 <sup>a</sup>         |     | V    |           |

| MM              | ESD Protection (Machine model)         | 75             |                                          |     | V    |           |

| HBM             | ESD Protection (Human body model)      | 1500           |                                          |     | V    |           |

| CDM             | ESD Protection (Charged device model)  | 500            |                                          |     | V    |           |

| LU              | Latch-up immunity                      | 200            |                                          |     | mA   |           |

| C <sub>IN</sub> |                                        |                | 4.0                                      |     | pF   | Inputs    |

| $\theta_{JA}$   | Thermal resistance junction to ambient | See applicatio | See application information <sup>b</sup> |     |      |           |

| θЈС             | Thermal resistance junction to case    | See applicatio | n information                            |     |      |           |

- a. Output termination voltage  $V_{TT}$  = 0V for  $V_{CC}$ =2.5V operation is supported but the power consumption of the device will increase.

- b. Proper thermal management is critical for reliable system operation. This especially true for high-fanout and high drive capability products. Thermal package information and exposed pad land pattern design recommendations are available in the applications section of this datasheet. In addition, the means of calculating die power consumption, the corresponding die temperature and the relationsship to long-term reliability is addressed in the Motorola application note AN1545. Thermal modeling is recommended for the MC100EP221.

Table 4: PECL and HSTL DC Characteristics ( $V_{CCO} = V_{CC} = 2.375V$  to 3.8V,  $V_{EE} = GND$ )

| Symbol           | Characteristics                                                                     | T <sub>A</sub> = -                             | -40°C                                          | T <sub>A</sub> =                               | 25°C                                           | T <sub>A</sub> =                               | 85°C                                           | Unit   | Condition                            |

|------------------|-------------------------------------------------------------------------------------|------------------------------------------------|------------------------------------------------|------------------------------------------------|------------------------------------------------|------------------------------------------------|------------------------------------------------|--------|--------------------------------------|

|                  |                                                                                     | Min                                            | Min Max Min Max                                |                                                |                                                |                                                | Max                                            |        |                                      |

| Clock in         | put pair CLK0, CLK0, CLK1                                                           | , CLK1 <sup>a</sup> (LVF                       | ECL different                                  | ial signals)                                   | •                                              | •                                              | •                                              |        |                                      |

| V <sub>PP</sub>  | Differential input voltage <sup>b</sup> V <sub>CC</sub> =3.3V V <sub>CC</sub> =2.5V | 0.10<br>0.15                                   |                                                | 0.10<br>0.15                                   |                                                | 0.10<br>0.15                                   |                                                | V<br>V |                                      |

| V <sub>CMR</sub> | Differential cross point voltage <sup>c</sup> CLK0 CLK1                             | 1.0<br>0.1                                     | V <sub>CC</sub> -0.4<br>V <sub>CC</sub> -1.0   | 1.0 V <sub>CC</sub> -0.4 V <sub>CC</sub> -1.0  |                                                | 1.0<br>0.1                                     | V <sub>CC</sub> -0.4<br>V <sub>CC</sub> -1.0   | V<br>V |                                      |

| Clock in         | put pair CLK1, CLK1d (HS                                                            | TL differential                                | signals)                                       |                                                |                                                |                                                |                                                |        |                                      |

| V <sub>DIF</sub> | Differential input voltage <sup>e</sup> V <sub>CC</sub> =3.3V V <sub>CC</sub> =2.5V | 0.4<br>0.4                                     | 1.0<br>1.0                                     | 0.4<br>0.4                                     | 1.0<br>1.0                                     | 0.4<br>0.4                                     | 1.0<br>1.0                                     | V<br>V |                                      |

| V <sub>X</sub>   | Differential cross point voltage <sup>f</sup>                                       | 0.68                                           | 0.9                                            | 0.68                                           | 0.9                                            | 0.68                                           | 0.9                                            | V      |                                      |

| V <sub>IH</sub>  | Input high voltage                                                                  | V <sub>X</sub> +0.2                            | V <sub>X</sub> +0.5                            | V <sub>X</sub> +0.2                            | V <sub>X</sub> +0.5                            | V <sub>X</sub> +0.2                            | V <sub>X</sub> +0.5                            | V      |                                      |

| $V_{IL}$         | Input low voltage                                                                   | V <sub>X</sub> -0.5                            | V <sub>X</sub> -0.2                            | V <sub>X</sub> -0.5                            | V <sub>X</sub> -0.2                            | V <sub>X</sub> -0.5                            | V <sub>X</sub> -0.2                            | V      |                                      |

| All input        | s (LVPECL single ended sig                                                          | gnals)                                         |                                                |                                                |                                                |                                                |                                                |        |                                      |

| V <sub>IH</sub>  | Input high voltage                                                                  | V <sub>CC</sub> -1.165                         | V <sub>CC</sub> -0.880                         | V <sub>CC</sub> -1.165                         | V <sub>CC</sub> -0.880                         | V <sub>CC</sub> -1.165                         | V <sub>CC</sub> -0.880                         | V      |                                      |

| $V_{IL}$         | Input low voltage                                                                   | V <sub>CC</sub> -1.810                         | V <sub>CC</sub> -1.480                         | V <sub>CC</sub> -1.810                         | V <sub>CC</sub> -1.480                         | V <sub>CC</sub> -1.810                         | V <sub>CC</sub> -1.480                         | V      |                                      |

| I <sub>IH</sub>  | Input Current                                                                       |                                                | 150                                            |                                                | 150                                            |                                                | 150                                            | μА     | $V_{IN} = V_{CC}$ to $V_{EE}$        |

| LVPECL           | clock outputs (Q0-19, Q0-                                                           | 19)                                            |                                                |                                                |                                                |                                                |                                                | •      |                                      |

| V <sub>OH</sub>  | Output High Voltage                                                                 | V <sub>CC</sub> -1.20                          | V <sub>CC</sub> -0.82                          | V <sub>CC</sub> -1.15                          | V <sub>CC</sub> -0.82                          | V <sub>CC</sub> -1.15                          | V <sub>CC</sub> -0.82                          | V      | I <sub>OH</sub> = -30mA <sup>g</sup> |

| V <sub>OL</sub>  | Output Low Voltage                                                                  | V <sub>CC</sub> -1.90                          | V <sub>CC</sub> -1.40                          | V <sub>CC</sub> -1.90                          | V <sub>CC</sub> -1.40                          | V <sub>CC</sub> -1.9                           | V <sub>CC</sub> -1.40                          | V      | I <sub>OL</sub> = -5mA <sup>g</sup>  |

| Supply           | current and V <sub>BB</sub>                                                         |                                                |                                                |                                                |                                                |                                                |                                                | •      |                                      |

| I <sub>EE</sub>  | Max. Supply Current                                                                 |                                                | 190                                            |                                                | 190                                            |                                                | 190                                            | mA     | V <sub>EE</sub> pin                  |

| I <sub>CC</sub>  | Max. Supply Currenth                                                                |                                                | 750                                            |                                                | 750                                            |                                                | 750                                            | mA     | V <sub>CC</sub> pins                 |

| V <sub>BB</sub>  | Output reference voltage <sup>i</sup> V <sub>CC</sub> =3.3V V <sub>CC</sub> =2.5V   | V <sub>CC</sub> -1.35<br>V <sub>CC</sub> -1.35 | V <sub>CC</sub> -1.24<br>V <sub>CC</sub> -1.24 | V <sub>CC</sub> -1.35<br>V <sub>CC</sub> -1.35 | V <sub>CC</sub> -1.24<br>V <sub>CC</sub> -1.22 | V <sub>CC</sub> -1.35<br>V <sub>CC</sub> -1.35 | V <sub>CC</sub> -1.24<br>V <sub>CC</sub> -1.22 | V      |                                      |

a. The input pairs CLK0, CLK1 are compatible to differential signaling standards. CLK0 is compatible to LVPECL signals and CLK1 meets both HSTL and LVPECL differential signal specifications. The difference between CLK0 and CLK1 is the differential input threshold voltage (V<sub>CMB</sub>).

- b. V<sub>PP</sub> is the minimum differential input voltage swing required to maintain device functionality.

- c.  $V_{CMR}$  (DC) is the crosspoint of the differential input signal. Functional operation is obtained when the crosspoint is within the  $V_{CMR}$  (DC) range and the input swing lies within the  $V_{PP}$  (DC) specification.

- d. Clock inputs driven by differential HSTL compatible signals. Only applicable to CLK1, CLK1.

- e. V<sub>DIF</sub> (DC) is the minimum differential HSTL input voltage swing required for device functionality. Only applicable to CLK1, CLK1.

- f. V<sub>CMR</sub> (DC) is the crosspoint of the differential input signal. Functional operation is obtained when the crosspoint is within the V<sub>CMR</sub> (DC) range and the input swing lies within the V<sub>PP</sub> (DC) specification.

- g. Equivalent to an output termination of  $50\Omega$  to  $V_{TT}$ .

- h.  $I_{CC}$  includes current through the output resistors (all outputs terminated  $50\Omega$  to  $V_{TT}$ ).

- V<sub>BB</sub> output can be used to bias the complementary input when the device is used with single ended clock signals. V<sub>BB</sub> can sink max. 0.3 mA DC current.

Table 5: ECL DC Characteristics ( $V_{CC} = V_{CCO} = GND$ ,  $V_{EE} = -3.8V$  to -2.375V)

| Symbol           | Characteristics                                                                       | T <sub>A</sub> = -                           | -40°C          | T <sub>A</sub> =                             | 25°C           | T <sub>A</sub> =                             | 85°C           | Unit | Condition                             |  |

|------------------|---------------------------------------------------------------------------------------|----------------------------------------------|----------------|----------------------------------------------|----------------|----------------------------------------------|----------------|------|---------------------------------------|--|

|                  |                                                                                       | Min                                          | Max            | Min                                          | Max            | Min                                          | Max            |      |                                       |  |

| Clock inp        | Clock input pair CLK0, CLK1, CLK1 for ECL differential signals                        |                                              |                |                                              |                |                                              |                |      |                                       |  |

| V <sub>PP</sub>  | Differential input voltage <sup>b</sup> V <sub>EE</sub> =-3.3V V <sub>EE</sub> =-2.5V | 0.10<br>0.15                                 |                | 0.10<br>0.15                                 |                | 0.10<br>0.15                                 |                | V    |                                       |  |

| V <sub>CMR</sub> | Differential cross point voltage <sup>c</sup><br>CLK0<br>CLK1                         | V <sub>EE</sub> +1.0<br>V <sub>EE</sub> +0.1 | -0.4<br>-1.0   | V <sub>EE</sub> +1.0<br>V <sub>EE</sub> +0.1 | -0.4<br>-1.0   | V <sub>EE</sub> +1.0<br>V <sub>EE</sub> +0.1 | -0.4<br>-1.0   | V    |                                       |  |

| All inputs       | ECL single ended signals                                                              |                                              |                |                                              |                |                                              |                |      |                                       |  |

| $V_{IH}$         | Input high voltage                                                                    | -1.165                                       | -0.880         | -1.165                                       | -0.880         | -1.165                                       | -0.880         | V    |                                       |  |

| $V_{IL}$         | Input low voltage                                                                     | -1.810                                       | -1.480         | -1.810                                       | -1.480         | -1.810                                       | -1.480         | V    |                                       |  |

| I <sub>IH</sub>  | Input Current                                                                         |                                              | 150            |                                              | 150            |                                              | 150            | μА   | $V_{IN} = V_{EE}$ to $V_{CC}$         |  |

| LVPECL           | clock outputs (Q0-19, Q0-19)                                                          |                                              |                |                                              |                |                                              |                |      |                                       |  |

| V <sub>OH</sub>  | Output High Voltage                                                                   | -1.20                                        | -0.82          | -1.20                                        | -0.82          | -1.20                                        | -0.82          | V    | I <sub>OH</sub> = -30 mA <sup>d</sup> |  |

| V <sub>OL</sub>  | Output Low Voltage                                                                    | -1.90                                        | -1.40          | -1.90                                        | -1.40          | -1.90                                        | -1.40          | V    | I <sub>OL</sub> = -5 mA <sup>d</sup>  |  |

| Supply c         | urrent and V <sub>BB</sub>                                                            |                                              |                |                                              |                |                                              |                |      |                                       |  |

| I <sub>EE</sub>  | Max. Supply Current                                                                   |                                              | 190            |                                              | 190            |                                              | 190            | mA   | V <sub>EE</sub> pin                   |  |

| I <sub>CC</sub>  | Max. Supply Current <sup>e</sup>                                                      |                                              | 750            |                                              | 750            |                                              | 750            | mA   | V <sub>CC</sub> Pins                  |  |

| V <sub>BB</sub>  | Output reference voltagef  V <sub>EE</sub> =-3.3V  V <sub>EE</sub> =-2.5V             | -1.35<br>-1.35                               | -1.24<br>-1.24 | -1.35<br>-1.35                               | -1.24<br>-1.22 | -1.35<br>-1.35                               | -1.24<br>-1.22 | V    |                                       |  |

a. The input pairs CLK0, CLK1 are compatible to differential signaling standards such as ECL. The difference between CLK0 and CLK1 is the differential input threshold voltage (V<sub>CMR</sub>).

b. V<sub>PP</sub> is the minimum differential input voltage swing required to maintain device functionality.

c. V<sub>CMR</sub> (DC) is the crosspoint of the differential input signal. Functional operation is obtained when the crosspoint is within the V<sub>CMR</sub> (DC) range and the input swing lies within the V<sub>PP</sub> (DC) specification.

d. Equivalent to an output termination of  $50\Omega$  to  $V_{TT}$ .

e.  $I_{CC}$  includes current through the output resistors (all outputs terminated 50 $\Omega$  to  $V_{TT}$ ).

f. V<sub>BB</sub> output can be used to bias the complementary input when the device is used with single ended clock signals. V<sub>BB</sub> can sink max. 0.3 mA DC current.

Table 6: PECL/ECL/HSTL AC Characteristics<sup>a</sup> ( $V_{CC} = V_{CCO} = 2.375V$  to 3.8V,  $V_{EE} = GND$ ) or ( $V_{EE} = -3.8V$  to -2.375V,  $V_{CC} = V_{CCO} = GND$ )

| Symbol                          | Characteristics                                                                           | T <sub>A</sub> = -40°C                       |            |                                              | T <sub>A</sub> = 25°C                        |            |                                              | T <sub>A</sub> = 85°C                        |            |                                              | Unit           | Condition               |

|---------------------------------|-------------------------------------------------------------------------------------------|----------------------------------------------|------------|----------------------------------------------|----------------------------------------------|------------|----------------------------------------------|----------------------------------------------|------------|----------------------------------------------|----------------|-------------------------|

|                                 |                                                                                           | Min                                          | Тур        | Max                                          | Min                                          | Тур        | Max                                          | Min                                          | Тур        | Max                                          | 1              |                         |

| Clock in                        | put pair CLK0, CLK0, CLK1, CL                                                             | K1 <sup>b</sup> for PE                       | CL dif     | ferential s                                  | ignals                                       |            |                                              |                                              |            | •                                            |                |                         |

| V <sub>PP</sub>                 | Differential input voltage <sup>c</sup> (peak-to-peak)                                    | 0.5                                          |            | 1.0                                          | 0.5                                          |            | 1.0                                          | 0.5                                          |            | 1.0                                          | V              |                         |

| V <sub>CMR</sub>                | Differential cross point voltage <sup>d</sup> CLK0 CLK1                                   | 1.0<br>0.3                                   |            | V <sub>CC</sub> -0.4<br>V <sub>CC</sub> -1.3 | 1.0<br>0.3                                   |            | V <sub>CC</sub> -0.4<br>V <sub>CC</sub> -1.3 | 1.0<br>0.3                                   |            | V <sub>CC</sub> -0.4<br>V <sub>CC</sub> -1.3 | V<br>V         |                         |

| f <sub>CLK</sub>                | Input Frequency (PECL)                                                                    | 0                                            |            | 1.0                                          |                                              |            | 1.0                                          |                                              |            | 1.0                                          | GHz            |                         |

| Clock in                        | put pair CLK0, CLK0, CLK1, CL                                                             | K1 for ECI                                   | _ differ   | ential sigr                                  | nals                                         |            |                                              |                                              |            |                                              |                |                         |

| V <sub>PP</sub>                 | Differential input voltage (peak-to-peak)                                                 | 0.5                                          |            | 1.0                                          | 0.5                                          |            | 1.0                                          | 0.5                                          |            | 1.0                                          | V              |                         |

| V <sub>CMR</sub>                | Differential cross point voltage CLK0 CLK1                                                | V <sub>EE</sub> +1.0<br>V <sub>EE</sub> +0.3 |            | -0.4<br>-1.3                                 | V <sub>EE</sub> +1.0<br>V <sub>EE</sub> +0.3 |            | -0.4<br>-1.3                                 | V <sub>EE</sub> +1.0<br>V <sub>EE</sub> +0.3 |            | -0.4<br>-1.3                                 | V<br>V         |                         |

| f <sub>CLK</sub>                | Input Frequency (ECL)                                                                     | 0                                            |            | 1.0                                          |                                              |            | 1.0                                          |                                              |            | 1.0                                          | GHz            |                         |

| Clock in                        | put pair CLK1, CLK1 for HSTL                                                              | differential                                 | signal     | 6                                            |                                              |            |                                              |                                              |            |                                              |                |                         |

| $V_{DIF}$                       | Differential input voltage <sup>e</sup> (peak-to-peak) CLK1                               | 0.4                                          |            | 1.0                                          | 0.5                                          |            | 1.0                                          | 0.5                                          |            | 1.0                                          | V              |                         |

| V <sub>X</sub>                  | Differential cross point voltagef CLK1                                                    | 0.68                                         |            | 0.9                                          | 0.68                                         |            | 0.9                                          | 0.68                                         |            | 0.9                                          | ٧              |                         |

| f <sub>CLK</sub>                | Input Frequency (HSTL)                                                                    | 0                                            |            | 1.0                                          |                                              |            | 1.0                                          |                                              |            | 1.0                                          | GHz            |                         |

| PECL/E                          | CL clock outputs (Q0-19, Q0-19                                                            | <u>)</u> )                                   |            |                                              |                                              |            |                                              |                                              |            |                                              |                |                         |

| t <sub>PD</sub>                 | Propagation Delay  CLK <sub>0</sub> to Qx  CLK <sub>1</sub> to Qx                         | 350<br>370                                   | 460<br>500 | 600<br>640                                   | 390<br>440                                   | 520<br>570 | 660<br>710                                   | 480<br>530                                   | 630<br>680 | 750<br>800                                   | ps<br>ps       | Diff.<br>Diff.          |

| V <sub>O(P-P)</sub>             | Differential output voltage (peak-to-peak) $f_O < 50$ MHz $f_O < 0.8$ GHz $f_O < 1.0$ GHz | 450<br>400<br>375                            |            |                                              | 550<br>500<br>400                            |            |                                              | 550<br>500<br>400                            |            |                                              | mV<br>mV<br>mV |                         |

| t <sub>sk(O)</sub>              | Output-to-output skew (within device)                                                     |                                              | 30         | 50                                           |                                              | 30         | 50                                           |                                              | 30         | 50                                           | ps             | Diff.                   |

| t <sub>sk(PP)</sub>             | Output-to-output skew (part-to-part)                                                      |                                              |            | 270                                          |                                              |            | 270                                          |                                              |            | 270                                          | ps             | Diff.                   |

| t <sub>JIT(CC)</sub>            | Output cycle-to-cycle jitter (RMS)                                                        |                                              |            | TBD                                          |                                              |            | TBD                                          |                                              |            | TBD                                          | ps             |                         |

| DCO                             | Output duty cycle                                                                         | 49.5                                         | 50         | 50.5                                         | 49.5                                         | 50         | 50.5                                         | 49.5                                         | 50         | 50.5                                         | %              | DC <sub>fref</sub> = 50 |

| t <sub>r</sub> , t <sub>f</sub> | Output Rise/Fall Time                                                                     | 100                                          |            | 500                                          | 100                                          |            | 500                                          | 100                                          |            | 500                                          | ps             | 20% to 80               |

- a. AC characteristics apply for parallel output termination of  $50\Omega$  to  $V_{TT}$ .

- b. The input pairs CLK0, CLK1 are compatible to differential signaling standards such as ECL. The difference between CLK0 and CLK1 is the differential input threshold voltage (V<sub>CMR</sub>).

- c. V<sub>PP</sub> (AC) is the minimum differential input voltage swing required to maintain AC characteristics including tpd and device-to-device skew.

- d. V<sub>CMR</sub> (AC) is the crosspoint of the differential input signal. AC operation is obtained when the crosspoint is within the V<sub>CMR</sub> range and the input swing lies within the V<sub>PP</sub> (AC) specification. Violation of V<sub>CMR</sub> (AC) or V<sub>PP</sub> (AC) impacts the device propagation delay and part-to-part skew.

- e. V<sub>DIF</sub> (AC) is the minimum differential HSTL input voltage swing required to maintain AC characteristics. Only applicable to CLK1.

- f. V<sub>X</sub> (AC) is the crosspoint of the differential HSTL input signal. AC operation is obtained when the crosspoint is within the V<sub>X</sub> (AC) range and the input swing lies within the V<sub>DIF</sub> (AC) specification. Violation of V<sub>X</sub> (AC) or V<sub>DIF</sub> (AC) impacts the device propagation delay and part-to-part skew.

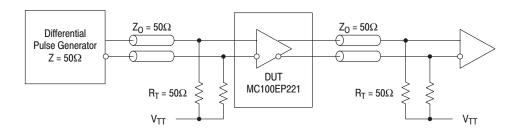

Figure 1. MC100EP221 AC test reference

Figure 2. MC100EP221 AC reference measurement waveform

#### **APPLICATIONS INFORMATION**

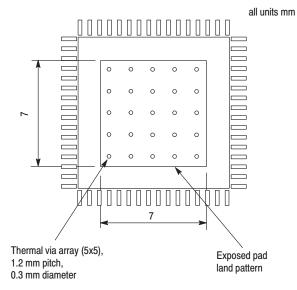

### Using the thermally enhanced package of the MC100EP221

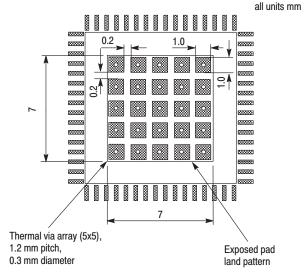

The MC100EP221 uses a thermally enhanced exposed pad (EP) 52 lead LQFP package. The package is molded so that the leadframe is exposed at the surface of the package bottom side. The exposed metal pad will provide the low thermal impedance that supports the power consumption of the MC100EP221 high-speed bipolar integrated circuit and eases the power management task for the system design. A thermal land pattern on the printed circuit board and thermal vias are recommended in order to take advantage of the enhanced thermal capabilities of the MC100EP221. Direct soldering of the exposed pad to the thermal land will provide an efficient thermal path. In multilayer board designs, thermal vias thermally connect the exposed pad to internal copper planes. Number of vias, spacing, via diameters and land pattern design depend on the application and the amount of heat to be removed from the package. A nine thermal via array, arranged in a 3 x 3 array and using a 1.2 mm pitch in the center of the thermal land is the absolute minimum requirement for MC100EP221 applications on multi-layer boards. The recommended thermal land design comprises a 5 x 5 thermal via array as shown in Figure 3 "Recommended thermal land pattern", providing an efficient heat removal path.

Figure 3. Recommended thermal land pattern

The via diameter is should be approx. 0.3 mm with 1 oz. copper via barrel plating. Solder wicking inside the via resulting in voids during the solder process must be avoided. If the copper plating does not plug the vias, stencil print solder paste onto the printed circuit pad. This will supply enough solder paste to fill those vias and not starve the solder joints. The attachment process for exposed pad package is equivalent to standard surface mount packages. Figure 4 "Recommended solder mask openings" shows a recommend solder mask opening with respect to the recommended 5 x 5 thermal via

array. Because a large solder mask opening may result in a poor release, the opening should be subdivided as shown in Figure 4 For the nominal package standoff 0.1 mm, a stencil thickness of 5 to 8 mils should be considered.

Figure 4. Recommended solder mask openings

For thermal system analysis and junction temperature calculation the thermal resistance parameters of the package is provided. For thermal system analysis and junction temperature calculation the thermal resistance parameters of the package is provided:

Table 7: Thermal Resistance<sup>a</sup>

| Convection-<br>LFPM | R <sub>THJA</sub> b<br>°C/W | R <sub>THJA</sub> ¢<br>°C/W | R <sub>THJC</sub> d<br>°C/W | R <sub>THJB</sub> e<br>°C/W |  |  |

|---------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|--|--|

| Natural             | 57.1                        | 24.9                        |                             |                             |  |  |

| 100                 | 50.0                        | 21.3                        |                             |                             |  |  |

| 200                 | 46.9                        | 20.0                        | 15.8                        | 9.7                         |  |  |

| 400                 | 43.4                        | 18.7                        |                             |                             |  |  |

| 800                 | 38.6                        | 16.9                        |                             |                             |  |  |

- a. Thermal data pattern with a 3 x 3 thermal via array on 2S2P boards (based on empirical results)

- b. Junction to ambient, single layer test board, per JESD51-6

- c. Junction to ambient, four conductor layer test board (2S2P), per JES51-6

- d. Junction to case, per MIL-SPEC 883E, method 1012.1

- e. Junction to board, four conductor layer test board (2S2P) per JESD 51-8

It is recommended that users employ thermal modeling analysis to assist in applying the general recommendations to their particular application. The exposed pad of the MC100EP221 package does not have an electrical low impedance path to the substrate of the integrated circuit and its terminals. The thermal land should be connected to GND through connection of internal board layers.