# 128K x 8 Static RAM

|                                      | Device Types |                   |                   |                   |                   |                   |                      |      |  |  |  |  |

|--------------------------------------|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|----------------------|------|--|--|--|--|

| Key Parameters<br>S128K8 and S128K8L | 25C          | 35M<br>35I<br>35C | 45M<br>45I<br>45C | 55M<br>55I<br>55C | 70M<br>70I<br>70C | 85M<br>85I<br>85C | 100M<br>100I<br>100C | Unit |  |  |  |  |

| Access Time                          | 25           | 35                | 45                | 55                | 70                | 85                | 100                  | nS   |  |  |  |  |

| Cycle Time                           | 25           | 35                | 45                | 55                | 70                | 85                | 100                  | nS   |  |  |  |  |

| Output Enable Access                 | 10           | 15                | 15                | 20                | 25                | 30                | 50                   | nS   |  |  |  |  |

#### **Features**

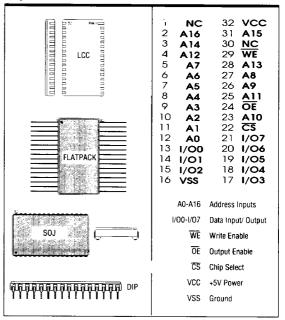

- 32 pin DIP, LCC, SOJ, Flatpack

- · Advanced 4-T CMOS technology

- S128K8 is compliant to DESC Standardized Military Drawing No. 5962-89598

# **General Description**

The Inova S128K8 is a high performance one megabit Static Random Access Memory (SRAM) organized as 128K eight -bit bytes.

The S128K8 is manufactured using a highly reliable, four transistor cell CMOS process. This provides a component which combines low active and standby power characteristics with high performance.

All inputs are fully TTL-compatible. Operation is fully static, without need for extra control logic to generate clock signals.

Every military grade device is fully compliant to MIL-STD-883C, paragraph 1.2.1. Industrial and commercial grade devices are fabricated in the same production line which assures that they are also of the highest quality.

- 300 mil DIP for 25, 35, 45 ns parts

- Military, industrial, and commercial temperature range

- Military grades compliant to MIL-STD-883C

# Package Options

# **Pinout**

# **Recommended Operating**

**Conditions**

| Parameter            | Symbol            | Min. | Мах.                 | Unit |

|----------------------|-------------------|------|----------------------|------|

| Supply Voltage(1)    | V <sub>cc</sub>   | 4.5  | 5.5                  | ٧    |

| Input HIGH Voltage   | V <sub>IH</sub>   | 2.2  | V <sub>cc</sub> +0.5 | V    |

| Input LOW Voltage    | V <sub>IL</sub>   | -0.5 | 0.8                  | V    |

| Operating Temp. Mil. | T <sub>c</sub>    | -55  | 125                  | °C   |

| Operating Temp. Ind. | T <sub>c</sub>    | -40  | 85                   | °C   |

| Operating Temp. Comr | n. T <sub>c</sub> | 0    | 70                   | °C   |

**Absolute Maximum Ratings** (2)

| , incolute indivini            |                                  |

|--------------------------------|----------------------------------|

| Temperature Under Bias         | -55 °C to 125 °C                 |

| Storage Temperature            | -65 °C to 150 °C                 |

| Supply Voltage(1)              | -0.5V to 7.0 V                   |

| Signal Voltage On Any Pin      | -0.5 V to V <sub>cc</sub> + 0.5V |

| Power Dissipation              | 1 Watt                           |

| D.C. Continuous Output Current | Per Output 20 mA                 |

| Lead Temperature (Soldering 10 | ) sec) 260 °C                    |

|                                |                                  |

#### Notes:

- 1. All voltages referenced to  $V_{ss}$  (GND).

- 2. Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **Truth Table**

| Mode              | <u>cs</u> | 0E | WE | I/O<br>Operation | Supply<br>Current                 |

|-------------------|-----------|----|----|------------------|-----------------------------------|

| Standby           | Н         | X  | X  | High Z           | I <sub>SB</sub> /I <sub>FSB</sub> |

| Read              | L         | L  | H  | Output           | I <sub>CC2</sub>                  |

| Write             | L         | Χ  | L  | Input            | I <sub>CC2</sub>                  |

| Output<br>Disable | L         | Н  | Н  | High Z           | l <sub>CC2</sub>                  |

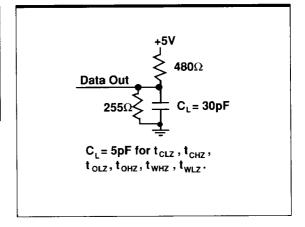

#### **Load Test Circuits**

# **Memory Scale**

| Access Time | 25 | 35 | 45 | 55 | 70 | 85 | 100 | Unit     |

|-------------|----|----|----|----|----|----|-----|----------|

| S128K8      | 40 | 29 | 22 | 18 | 14 | 11 | 10  | kbits/ns |

# **AC Test Conditions**

| Input Pulse Levels            | GND to 3.0V |

|-------------------------------|-------------|

| Input Rise and Fall Times     | 5ns         |

| Input Timing Reference Levels | 1.5V        |

| Output Reference Levels       | 1.5V        |

# **DC and Operating Characteristics** L=Low Power, S = Standard Power

| Symbol                |   | 2    | 5   | 3    | 5   | 4    | 5   | 5    | 5   | 7    | 0   | 8    | 5   | 10   | )0  | Units   |

|-----------------------|---|------|-----|------|-----|------|-----|------|-----|------|-----|------|-----|------|-----|---------|

|                       |   |      | S   | L    | S   | L    | s   | L    | S   | L    | S   | L    | S   | L    | S   |         |

|                       | С | 90   | 100 | 80   | 90  | 80   | 90  | 80   | 90  | 80   | 90  | 80   | 90  | 80   | 90  |         |

| I <sub>CC1</sub> (1)  |   |      |     | 85   | 95  | 85   | 95  | 85   | 95  | 85   | 95  | 85   | 95  | 85   | 95  | mA(max) |

|                       | М |      |     | 90   | 100 | 90   | 100 | 90   | 100 | 90   | 100 | 90   | 100 | 90   | 100 |         |

| I <sub>CC2</sub> (2)  |   | 140  | 150 | 125  | 140 | 125  | 125 | 125  | 125 | 125  | 125 | 125  | 125 | 125  | 125 | mA(max) |

|                       | С | 30   | 40  | 3    | 30  | 1.5  | 4   | 1.5  | 4   | 1.5  | 4   | 1.5  | 4   | 1.5  | 4   | mA(max) |

| I <sub>SB</sub> (3)   | 1 |      |     | 4    | 35  | 2.0  | 5   | 2.0  | 5   | 2.0  | 5   | 2.0  | 5   | 2.0  | 5   |         |

|                       | М |      |     | 10   | 40  | 10   | 10  | 10   | 10  | 10   | 10  | 10   | 10  | 10   | 10  |         |

|                       | С | 0.75 |     | 0.75 |     | 0.75 |     | 0.75 |     | 0.75 |     | 0.75 |     | 0.75 |     |         |

| I <sub>FSB</sub> (4)  | 1 |      |     | 1.25 |     | 1.25 |     | 1.25 |     | 1.25 |     | 1.25 |     | 1.25 |     | mA(max) |

|                       | М |      |     | 5    |     | 5    |     | 5    |     | 5    |     | 5    |     | 5    |     |         |

|                       | С | 0.10 |     | 0.10 |     | 0.10 |     | 0.10 |     | 0.10 |     | 0.10 |     | 0.10 |     | mA(max) |

| I <sub>CCDR</sub> (5) | ١ |      |     | 0.15 |     | 0.15 |     | 0.15 |     | 0.15 |     | 0.15 |     | 0.15 |     |         |

|                       | М |      |     | 2.0  |     | 2.0  |     | 2.0  |     | 2.0  |     | 2.0  |     | 2.0  |     |         |

| V <sub>DR</sub> (6)   |   | 2.0  | 2.0 | 2.0  | 2.0 | 2.0  | 2.0 | 2.0  | 2.0 | 2.0  | 2.0 | 2.0  | 2.0 | 2.0  | 2.0 | V(min)  |

Notes:

- (1) Static Supply Current:  $\overline{CS} = V_{ii}$ ,  $\overline{OE} = V_{iii}$  No address transitions

- (2) Dynamic Supply Current:  $\overline{CS} < V_{tt}$ ,  $\overline{OE} = V_{tt}$ , Address Change every  $t_{RG}$

- (3) Standby Supply Current With TTL Inputs:

CS > V<sub>H</sub>, Address change every t<sub>sc</sub>

- (4) Standby Supply Current With CMOS Inputs:  $\overline{CS} = V_{cc} + 0.2V$ . No address transitions

- (5) Data Retention Current:  $\overline{CS} = V_{DR} \min_{CC} = V_{DR} \min_{CC}$

- (6) Data Retention Voltage: V<sub>cc</sub> minimum supply voltage

# DC and Operating Characteristics L=Low Power, S = Standard Power

| <u> </u>              | <u> </u> | <i>&gt;</i> :             | <u>9</u> `      | <u> </u> |     | VI 10 | 1100 |      |          | 1 011 | ÇI, O      | - Olu | IIGUIG  | 1 1 011 | 101              |

|-----------------------|----------|---------------------------|-----------------|----------|-----|-------|------|------|----------|-------|------------|-------|---------|---------|------------------|

| Symbol 25             |          | 35                        |                 |          | 45  | İ     | 55   | 5    | 70       |       | 8          | 5     | 100     | )       | Units            |

|                       | L        | S                         | L               | S        | L   | S     | L    | S    | L        | S     | L          | S     | L       | S       |                  |

| I <sub>LI</sub>   (1) | 2        | 2                         | 2               | 2        | 2   | 2     | 2    | 2    | 2        | 2     | 2          | 2     | 2       | 2       | μ <b>A</b> (max) |

| I <sub>LO</sub>   (2) | 2        | 2                         | 2               | 2        | 2   | 2     | 2    | 2    | 2        | 2     | 2          | 2     | 2       | 2       | μ <b>A</b> (max) |

| V <sub>OL</sub> (3)   | 0.4      | 0.4                       | 0.4             | 0.4      | 0.4 | 0.4   | 0.4  | 0.4  | 0.4      | 0.4   | 0.4        | 0.4   | 0.4     | 0.4     | V (max)          |

| V <sub>OH</sub> (4)   | 2.4      | 2.4                       | 2.4             | 2.4      | 2.4 | 2.4   | 2.4  | 2.4  | 2.4      | 2.4   | 2.4        | 2.4   | 2.4     | 2.4     | V (min)          |

| Typical Tes           |          | Test                      | Test Conditions |          |     |       | Add  | Data | Data I/O |       | CS, WE, OE |       |         |         |                  |

| Pin Capacitance P     |          | Pin Voltage=0V, f=1.0 MHz |                 |          |     |       | 8 10 |      |          |       |            | 12    | pF(typ) |         |                  |

Notes:

- (1) Input Leakage Current:  $V_{CC} = max$ ,  $V_{IN} = GND$  to  $V_{CC}$

- (2) Output Leakage Current:  $V_{OUT} = GND$  to  $V_{CC}$ . Outputs in tri-state

- (3) Output Low Voltage: Io4 = 8 mA

- (4) Output High Voltage: I<sub>OH</sub> = -4 mA

#### AC Characteristics(1)

|     | S128K8 and S128K8L                 | Countral               | 25  | 5C  | 35C | , <i>I</i> ,M | 45C | ,I,M | 55C,I,M |     | 70 C,I,M |    | 85C,I,M |     |

|-----|------------------------------------|------------------------|-----|-----|-----|---------------|-----|------|---------|-----|----------|----|---------|-----|

| No. | Parameter                          | Symbol                 | Min | Max | Min | Max           | Min | Max  |         |     |          |    | Max     | Min |

| 1   | Read Cycle Time                    | t <sub>RC</sub>        | 25  |     | 35  |               | 45  |      | 55      |     | 70       |    | 85      |     |

| 2   | Address Access Time                | t <sub>AA</sub>        |     | 25  |     | 35            |     | 45   |         | 55_ |          | 70 |         | 85  |

| 3   | CS on to Output Valid              | t <sub>ACS</sub>       |     | 25  |     | 35            |     | 45   |         | 55  |          | 70 |         | 85  |

| 4   | OE on to Output Valid              | t <sub>oe</sub>        |     | 10  |     | 15            |     | 15   |         | 20  |          | 25 |         | 30  |

| 5   | CS on to Output in Low Z           | t <sub>CLZ</sub> (2,3) | 5   |     | 5   |               | 5   |      | 5       |     | 5        |    | 5       |     |

| 6   | OE on to Output in Low Z           | t <sub>OLZ</sub> (2,3) | 0   |     | 0   |               | 0   |      | 0       |     | 0        |    | 0       |     |

| 7   | CS off to Output in High Z         | t <sub>CHZ</sub> (2,3) | 0   | 10  | 0   | 15            | 0   | 20   | 0       | 35  | 0        | 35 | 0       | 35  |

| 8   | OE off to Output in High Z         | t <sub>OHZ</sub> (2,3) | 0   | 10  | 0   | 15            | 0   | 20   | 0       | 35  | 0        | 35 | 0       | 35  |

| 9   | Output Hold from Address Change    | t <sub>oн</sub>        | 3   |     | 5   |               | 5   |      | 5       |     | 5        |    | 5       |     |

| 10  | Write Cycle Time                   | t <sub>wc</sub>        | 25  |     | 35  |               | 45  |      | 55      |     | 70       |    | 85      |     |

| 11  | Chip Selection to End of Write     | t <sub>cw</sub>        | 20  |     | 25  |               | 35  |      | 45      |     | 60       |    | 75      |     |

| 12  | Address Set-up Time                | t <sub>AS</sub>        | 0   |     | 0   |               | 0   |      | 0       |     | 0        |    | 0       |     |

| 13  | Address Valid to End of Write      | t <sub>AW</sub>        | 20  |     | 25  |               | 35  |      | 45      |     | 60       |    | 75      |     |

| 14  | Write Pulse Width                  | t <sub>wP</sub>        | 20  |     | 25  |               | 30  |      | 35      |     | 35       |    | 40      |     |

| 15  | Write Recovery Time                | t <sub>wn</sub>        | 0   |     | 0   |               | 5   |      | 5       |     | 5        |    | 5       |     |

| 16  | Write Pulse on to Output in High Z | t <sub>WHZ(2,3)</sub>  | 0   | 10  | 0   | 15            | 0   | 20   | 0       | 35  | 0        | 35 | 0       | 35  |

| 17  | Write Pulse off to Output in Low Z | t <sub>WLZ(2,3)</sub>  | 5   |     | 5   |               | 5   |      | 5       |     | 5        |    | 5       |     |

| 18  | Data Valid Set-Up to End of Write  | t <sub>DW</sub>        | 15  |     | 20  |               | 25  |      | 25      |     | 30       |    | 35      |     |

| 19  | Data Hold from End of Write        | t <sub>DH</sub>        | 0   |     | 0   |               | 0   |      | 3       |     | 3        |    | 3       |     |

| 20  | Chip Deselect to Data Retention    | t <sub>CDR(2)</sub>    | 0   |     | 0   |               | 0   |      | 0       |     | 0        |    | 0       |     |

| 21  | Operation Recovery Time            | t <sub>R(2)</sub>      |     | 25  |     | 35            |     | 45   |         | 55  |          | 70 |         | 85  |

Notes: (1) At Recommended Operating Conditions. All Values in Nanoseconds. 100nS and 120nS parts are also available. (2) This Parameter is characterized initially and after any design or process change which could affect it. It is guaranteed to, but not tested to, the limits specified. (3) All Transitions are measured ± 500mV from steady state with loading as specified in "Load Test Circuits."

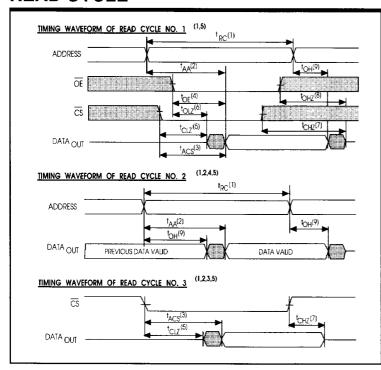

#### **READ CYCLE**

Reading the S128K8 device is accomplished by taking chipselect (CS) and output enable (OE) LOW, while write enable (WE) remains inactive or high. Under these conditions, the contents of the memory location specified on the address pins will appear on the appropriate data input/output pins.

#### Notes:

- 1. WE is high for READ CYCLES.

- Device is continuously selected,

CS= V<sub>n</sub> for all outputs active.

- 3. Address valid prior to or coincident with  $\overline{\text{CS}}$  transition low.

- 4. OE =V,

- 5. Data Output transitions measured ±500mV from steady state. This parameter is sampled and not 100% tested

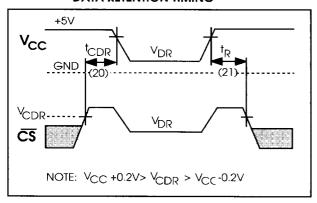

### **Data Retention**

S128K8 devices exhibit very low current drain when operated in Data Retention Mode. This Mode is entered by first driving Chip Select to  $V_{\rm CC}$  and subsequently driving both  $V_{\rm CC}$  and Chip Select to  $V_{\rm DR}$ . Chip Select must be set up before the  $V_{\rm CC}$  drops below its minimum level. When exiting from Data Retention Mode, the user must wait one full Read Cycle Time prior to asserting Chip Select.

#### DATA RETENTION TIMING

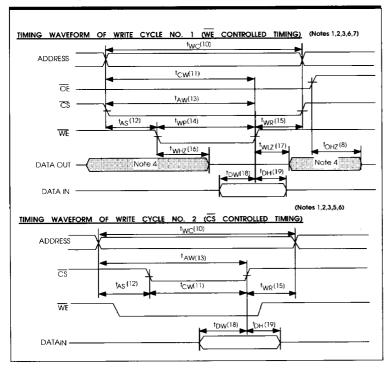

### **WRITE CYCLE**

Writing to the S128K8 is achieved when the chip select (CS) and write enable (WE) inputs are LOW. Data on the input/output pins is written into the memory location specified on the address pins (A0-A16).

The input/output pins remain in a high impedance state when chip select (CS) or output enable (OE) is HIGH, or write enable (WE) is LOW.

#### **Notes:**

- 1.  $\overline{\text{WE}}$  or  $\overline{\text{CS}}$  must be high during all address transitions.

- 2. A write occurs during the overlap (TWP) of a low  $\overline{\text{CS}}$  and a low  $\overline{\text{WE}}$ .

- 3. TWR is measured from the earlier of  $\overline{\text{CS}}$  or  $\overline{\text{WE}}$  going high to the end of the write cycle.

- 4. During this period, I/O pins are in the output state, and input signals must not be applied.

- 5. If the CS low transitions occurs simultaneously with or after the WE low transition, the outputs remain in a high impedance state.

- 6. Data output transitions are measured  $\pm$  500mV from steady state. This parameter is sampled and characterized but not 100% tested.

- 7. During a WE controlled write cycle, write pulse low is ≥TDW + TWHZ to allow the I/O drivers to turn off and data to be placed on the the bus for the required TDW. If OE is high during a WE controlled write cycle, this requirement does not apply and the write pulse can be as short as the specified TWP.

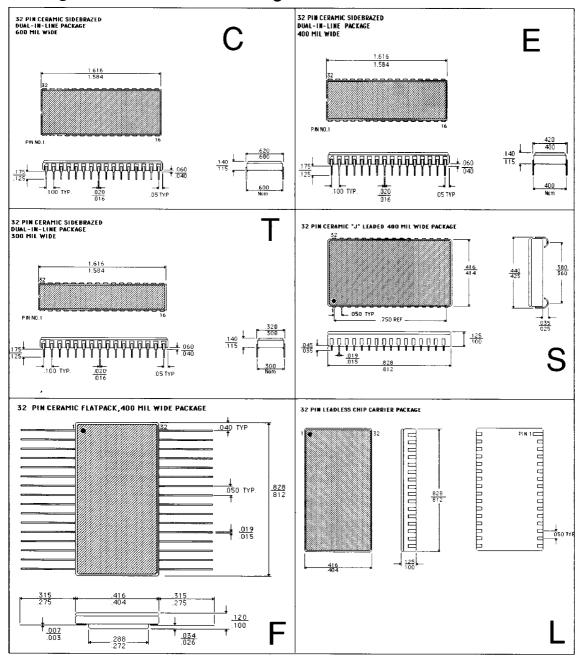

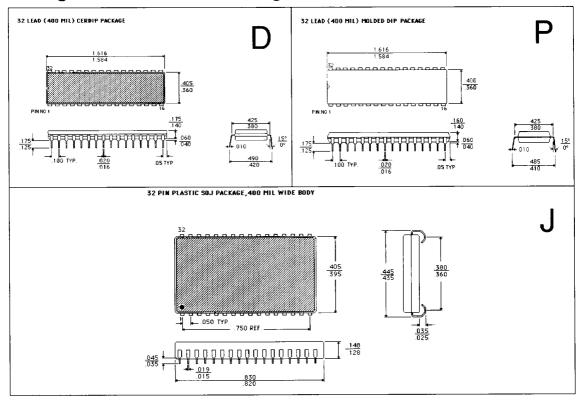

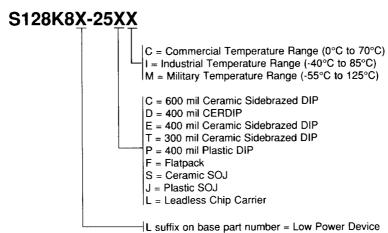

# **Package Dimension and Ordering Information**

# **Package Dimension and Ordering Information**

All Specifications are subject to change without notice.

Printed in U.S.A., AMN-790