# MOTHERBOARD CLOCK CHIP

#### **GENERAL DESCRIPTION**

The W83C17 Motherboard Clock Chip is a solid state dual phase-locked loop frequency synthesizer designed to offer jitter-free and low skew clocking for green PC motherboard applications. This frequency synthesizer generates three simultaneous clocks. One clock, REFCLK, is a fixed output frequency (14.318 MHz) which is the same as the input reference crystal (or clock). The second clock, PCLK, is a fixed output frequency which is 24 MHz when the input reference clock frequency is 14.318 MHz. The third clock, CPUCLK, is a programmable CPU clock, with up to eight selectable preprogrammed frequencies stored in an internal ROM. In addition to the industry standard frequency sets, Winbond also offers customized frequency sets (within the frequency range up to 135 MHz) to accommodate unique requirements. Contact Winbond's local sales representatives for further details.

The W83C17 has integrated advanced power management capabilities to support green PC applications. System power management can be achieved by switching the CPUCLK to slower speed (low power mode, 2/4/8 MHz optional), or by disabling the output buffers of CPUCLK and PCLK (stop mode). This clock generator also permits smooth and glitch-free transitions when frequency is changed or low power mode (or stop mode) is enabled.

The reference clock source is typically a series-resonant crystal connected across the XTAL1 and XTAL2 pins or an externally generated reference clock connected to the XTAL1 pin. In the latter case, the XTAL2 pin should be left open. For IBM® PC or compatible systems, the crystal frequency typically is 14.318 MHz.

#### **FEATURES**

- Clock generator for IBM PC/AT<sup>®</sup> system

- Mask programmable for CPU clock frequencies up to 135 MHz

- Generates three buffered clock outputs simultaneously (14.318 MHz, 24 MHz, and a CPU clock)

- · On-chip loop filters to provide glitch-free frequency transition

- · Advanced PLL for low phase jitter

- Provides advanced power management capabilities, including low power mode (2/4/8 MHz optional) and stop mode (0 Hz) for green PC applications

- Subsequent clock period changed under 0.1% while switching frequencies

- Advanced low power CMOS technology

- · 14-pin plastic DIP or SOP package

IBM and PC/AT are registered trademarks of International Business Machines Corporation.

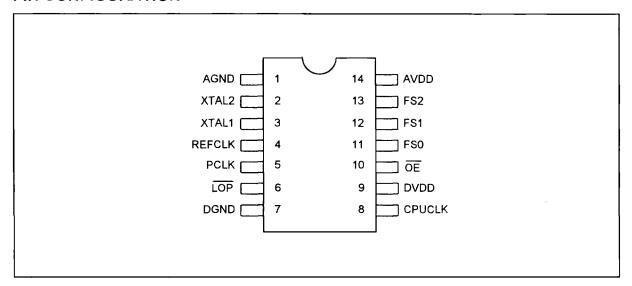

## **PIN CONFIGURATION**

# **PIN DESCRIPTION**

| NAME   | NUMBER | TYPE | DESCRIPTION                                                                                           |  |

|--------|--------|------|-------------------------------------------------------------------------------------------------------|--|

| AGND   | 1      |      | Analog ground.                                                                                        |  |

| XTAL2  | 2      | 0    | Crystal output (no connection when clock used).                                                       |  |

| XTAL1  | 3      | I    | Crystal input or input clock frequency. Typically 14.318 MHz system clock.                            |  |

| REFCLK | 4      | 0    | Crystal output which rebuffers the reference input clock or crystal frequency (typically 14.318 MHz). |  |

| PCLK   | 5      | 0    | Peripheral clock output. Typically 24 MHz.                                                            |  |

| LOP    | 6      | I    | Low power. When asserted low, the CPUCLK gradually transits to 2/4/8 MHz. Internal pull-up.           |  |

| DGND   | 7      |      | Digital ground.                                                                                       |  |

| CPUCLK | 8      | 0    | CPU clock output (see decoding table).                                                                |  |

| DVDD   | 9      |      | Digital power supply.                                                                                 |  |

| ŌĒ     | 10     | l    | Output enable. When asserted high, PCLK and CPUCLK stop to low. Internal pull-down.                   |  |

| FS0    | 11     | 1    | Frequency select 0 (see decoding table). Internal pull-up                                             |  |

| FS1    | 12     | 1    | Frequency select 1 (see decoding table). Internal pull-up                                             |  |

| FS2    | 13     |      | Frequency select 2 (see decoding table). Internal pull-up.                                            |  |

| AVDD   | 14     |      | Analog power supply.                                                                                  |  |

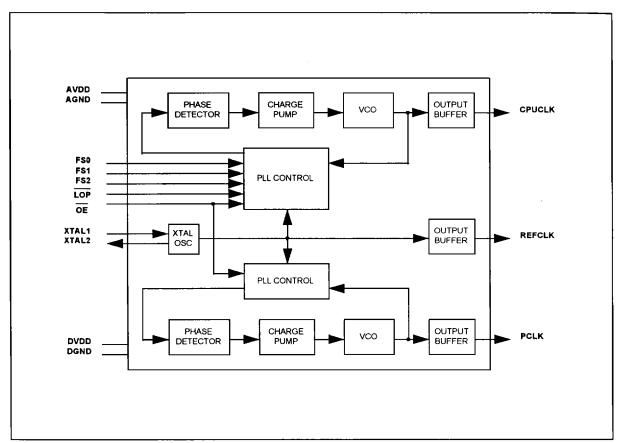

### **BLOCK DIAGRAM**

## **FUNCTIONAL DESCRIPTION**

The W83C17 Motherboard Clock Chip is a dual phase-locked loop frequency synthesizer capable of generating three clock outputs for a PC system. REFCLK (pin 4) provides the crystal oscillation frequency (14.318 MHz). PCLK (pin 5) provides the peripheral clock frequency (24 MHz). CPUCLK (pin 8) provides the CPU clock frequency, which is programmable through three selectable pins (FS0, FS1, and FS2) based on the decoding table. This device also has advanced power management features, including low power mode and stop mode.

#### **Low Power Mode**

The low power mode gradually transits the CPUCLK to 2/4/8 MHz to allow for system power saving.

#### Stop Mode

The stop mode feature stops the PCLK and CPUCLK to allow for CPU stop mode operation.

## Frequency Decoding Table

(Assumes a 14.318 MHz input. Unit: MHz)

| ΟE | LOP | FS2 | FS1 | FS0 | CPUCLK | PCLK | REFCLK |

|----|-----|-----|-----|-----|--------|------|--------|

| 1  | Х   | Х   | X   | Х   | 0      | 0    | 14.318 |

| 0  | 0   | Х   | X   | Х   | 8      | 24   | 14.318 |

| 0  | 1   | 0   | 0   | 0   | 33.3   | 24   | 14.318 |

| 0  | 1   | 0   | 0   | 1   | 80     | 24   | 14.318 |

| 0  | 1   | 0   | 1   | 0   | 66.6   | 24   | 14.318 |

| 0  | 1   | 0   | 1   | 1   | 50     | 24   | 14.318 |

| 0  | 1   | 1   | 0   | 0   | 40     | 24   | 14.318 |

| 0  | 1   | 1   | 0   | 1   | 60     | 24   | 14.318 |

| 0  | 1   | 1   | 1   | 0   | 25     | 24   | 14.318 |

| 0  | 1   | 1   | 1   | 1   | 20     | 24   | 14.318 |

### **ABSOLUTE MAXIMUM RATINGS**

| SYMBOL | PARAMETER             | MINIMUM | MAXIMUM  | UNIT |

|--------|-----------------------|---------|----------|------|

| VDD    | Supply voltage        | -0.5    | 7        | ٧    |

| VIN    | Input voltage         | -0.5    | Vpp +0.5 | ٧    |

| Vout   | Output voltage        | -0.5    | VDD +0.5 | ٧    |

| То     | Operating temperature | 0       | 70       | °C   |

| Тѕтс   | Storage temperature   | -65     | 150      | °C   |

| Pb     | Power dissipation     |         | 0.5      | W    |

Note: Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum conditions for extended periods may affect device reliability. For proper operation, it is recommended that VIN and VOUT be constrained to ≥ GND and ≤ VDD.

### DC CHARACTERISTICS

(VDD= 4.5 V to 5.5 V, Vss= 0 V, TA= 0° C to 70° C)

| SYMBOL | PARAMETER               | MINIMUM | MAXIMUM | UNIT |

|--------|-------------------------|---------|---------|------|

| VDD    | Operating voltage range | . 4.5   | 5.5     | ٧    |

| VIL    | Input low voltage       | Vss     | 0.8     | ٧    |

| ViH    | Input high voltage      | 2.0     | VDD     | ٧    |

| Vol    | Output low voltage      | •       | 0.4     | ٧    |

DC characteristics, continued

| SYMBOL | PARAMETER                     | мимим | MAXIMUM | UNIT |

|--------|-------------------------------|-------|---------|------|

| Vон    | Output high voltage           | 2.4   | -       | ٧    |

| lad    | Supply current (Note 1)       | -     | 35      | mA   |

| liL    | Input low leakage current     |       | 10      | μА   |

| liH    | Input high leakage current    | -     | -5      | μА   |

| Rup    | Internal pull-up resistance   | 50    | 200     | ΚΩ   |

| RDOWN  | Internal pull-down resistance | 50    | 200     | ΚΩ   |

| CIN    | Input pin capacitance         | -     | 8       | pF   |

| Соит   | Output pin capacitance        | -     | 8       | pF   |

Note: No load, 14.318 MHz crystal input, and CPUCLK running at 80 MHz.

# **AC CHARACTERISTICS**

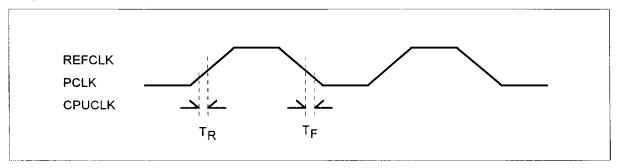

# **Output Clock Timing**

| SYMBOL | DESCRIPTION             | MIN. | TYP. | MAX. | UNIT | NOTES                |

|--------|-------------------------|------|------|------|------|----------------------|

| Tr     | Output clock rise time  | -    | 2.0  | -    | nS   | 25 pF load           |

| TF     | Output clock fall time  | -    | 2.0  | -    | nS   | 25 pF load           |

| Dτ     | Output clock duty cycle | T -  | 50   | -    | %    | 25 pF load           |

| FE     | Frequency error         | -    | -    | 0.5  | %    | All frequencies      |

| FMAX   | Maximum frequency       | -    | -    | 135  | MHz  | Per customer request |

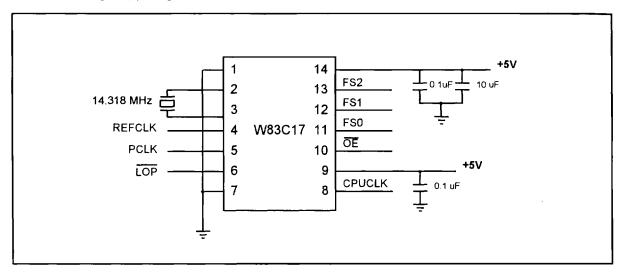

## **APPLICATION CIRCUIT**

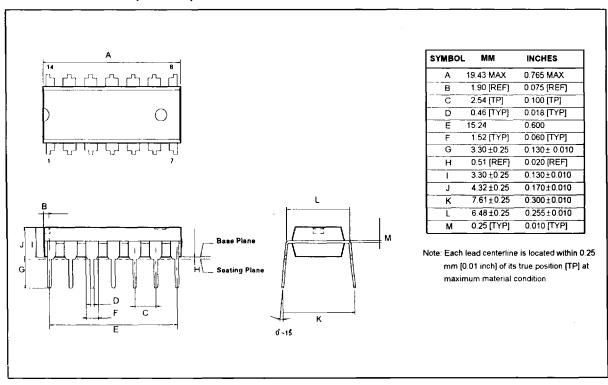

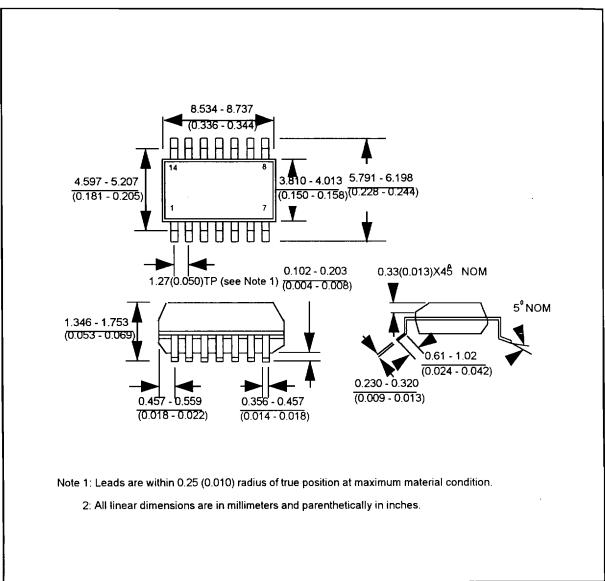

### **PACKAGE DIMENSIONS**

### 14-Pin Plastic DIP (300 mil)

# 14-Pin Plastic SOP (150 mil)

CORPORATE HEADQUARTERS:

No. 4, Creation Rd. III Science-Based Industrial Park Hsinchu, Taiwan, R.O.C. TEL: 886-35-770066 FAX: 886-35-789467

TAIPEI SALES OFFICE:

11Fl, No. 115, Sec. 3, Min Sheng E. Rd.

Taipei, Taiwan, R.O.C. TEL: 886-2-7190505 FAX: 886-2-7197502 TLX: 16485 WINTPE Winbond Electronics (H.K.) Ltd.

Rm. 803, World Trade Square, Tower II, 123 Hoi Bun Road, Kwun Tong, Kowloon, Hong Kong TEL: 852-7516023-7

TEL: 852-7516023-7 FAX: 852-7552064 Winbond Electronics (North America) Corp.

90 West Plumeria Drive San Jose, CA 95134 U.S.A. TEL: 1-408-943-6666 FAX: 1-408-943-6668