# mos integrated circuit $\mu PD29F008L$

# 8 M-BIT CMOS 3.0 V-ONLY FLASH MEMORY 1 M-WORD BY 8-BIT (BYTE MODE)

#### Description

The  $\mu$ PD29F008L is an electrically programmable/erasable high-speed 3.0 V-only flash memory with a 8,388,608-bit configuration. It possesses an automatic single Byte program function and an automatic block erase function that are effected by command register input.

This memory consists of 19 blocks: one protection block (16 K byte), two condition blocks (8 K byte by 2 blocks), and sixteen main blocks (32 K byte by 1 block, 64 K byte by 15 blocks).

The  $\mu$ PD29F008L comes in two types: the type T with the protection block located at the top address and the type B with the protection block located at the bottom address.

The  $\mu$ PD29F008L is packed in 40-pin TSOP (I) (10 × 20 mm).

#### **Features**

- · 1,048,576 words by 8 bit

- Two types of protection block locations

type T : protection block at the top address

type B : protection block at the bottom address

- Fast access time: 120, 150 ns (MAX.)

- Fast program/erase time.

Program: 9  $\mu$ s (TYP.)

· Block erase

Protection block: 1.0 s (TYP.)

Condition block: 1.0 s (TYP.)

Main block: 1.0 s (TYP.)

- Command register input

- · Automatic program function

- · Hardware reset

- Ready (/Busy) output (RY (/BY))

- · Data polling and toggle bit

- · Automatic erase function

- Functions for automatic erasure:

Erase suspend and resume functions

· Minimum number of repetitions for program/erase:

100,000 times

- · Directly drive TTL or CMOS

- · Low power dissipation

Reset mode :  $5.0 \mu A \text{ (MAX.)}$ Standby mode :  $5.0 \mu A \text{ (MAX.)}$ Operating mode : 35 mA (MAX.)

· Voltage range

Vcc: 3.0 V + 20 %/-10 % (Extend voltage)

The information in this document is subject to change without notice.

# **Ordering Information**

| Part number           | Access time<br>(MAX.) | Protection block   | Package                     |

|-----------------------|-----------------------|--------------------|-----------------------------|

| μPD29F008LGZ-B12T-LJH | 120 ns                | The top address    | 40-pin plastic TSOP (I)     |

| μPD29F008LGZ-B15T-LJH | 150 ns                |                    | (10 × 20 mm) (Normal bent)  |

| μPD29F008LGZ-B12B-LJH | 120 ns                | The bottom address |                             |

| μPD29F008LGZ-B15B-LJH | 150 ns                |                    |                             |

| μPD29F008LGZ-B12T-LKH | 120 ns                | The top address    | 40-pin plastic TSOP (I)     |

| μPD29F008LGZ-B15T-LKH | 150 ns                |                    | (10 × 20 mm) (Reverse bent) |

| μPD29F008LGZ-B12B-LKH | 120 ns                | The bottom address |                             |

| μPD29F008LGZ-B15B-LKH | 150 ns                |                    |                             |

**Remark** For the address locations of the blocks, see the memory maps in **Erase Block Layout**.

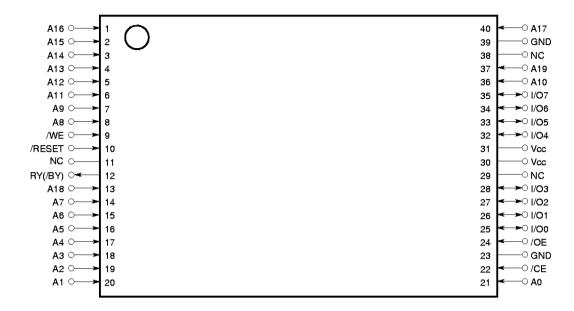

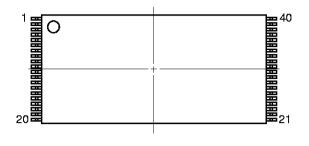

#### Pin Configuration (Marking Side)

40-pin plastic TSOP (I) (10  $\times$  20 mm) (Normal bent)  $\mu$ PD29F008LGZ-xxxT-LJH  $\mu$ PD29F008LGZ-xxxB-LJH

A0 to A19 : Address inputs I/O0 to I/O7 : Data inputs/outputs

/CE : Chip enable

/WE : Write enable

/OE : Output enable

/RESET : Hardware reset input RY (/BY) : Ready (/Busy) output

Vcc : Supply voltage

GND : Ground

NC : No connection

Note Some signals can be applied because this pin is not connected to the inside of the chip.

**Preliminary Data Sheet**

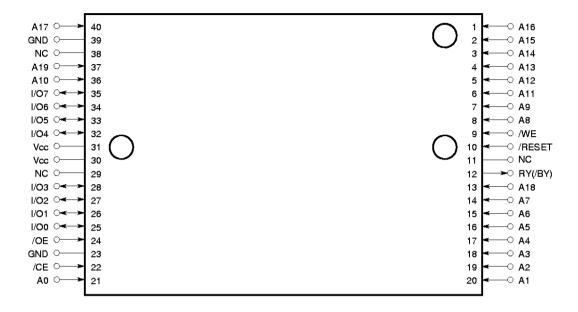

# 40-pin plastic TSOP (I) (10 $\times$ 20 mm) (Reverse bent) $\mu$ PD29F008LGZ-xxxT-LKH $\mu$ PD29F008LGZ-xxxB-LKH

A0 to A19 : Address inputs I/O0 to I/O7 : Data inputs/outputs

/CE : Chip enable

/WE : Write enable

/OE : Output enable

/RESET : Hardware reset input RY (/BY) : Ready (/Busy) output

Vcc : Supply voltage

GND : Ground NC No connection

Note Some signals can be applied because this pin is not connected to the inside of the chip.

**Preliminary Data Sheet**

# Input/Output Pin Functions

| Pin Name  | Inout/Output | Function                                                                                                                                                                                                                                                                                                                                                              |

|-----------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A0-A19    | Input        | Address inputs.                                                                                                                                                                                                                                                                                                                                                       |

| A9        | Input        | Address input. When A9 is at 11.5 V to 12.5 V, the signature mode is accessed.  During this mode A0 decodes between the manufacturer and device IDs.  A0 = "L": Manufacturer ID, A0 = "H": Device ID.                                                                                                                                                                 |

| 1/00-1/07 | Input/Output | Data inputs/outputs.                                                                                                                                                                                                                                                                                                                                                  |

| /CE       | Input        | Chip enable signal. High level input: Standby mode                                                                                                                                                                                                                                                                                                                    |

| /OE       | Input        | Output enable sinal.<br>High level input: Output disable mode                                                                                                                                                                                                                                                                                                         |

| /WE       | Input        | Write enable signal.  Low level input: Block Erase/Program and Command input                                                                                                                                                                                                                                                                                          |

| /RESET    | Input        | Hardware reset input.  Low level input: Reset mode                                                                                                                                                                                                                                                                                                                    |

| RY (/BY)  | Output       | The pin for indicating that automatic erase (or automatic program) operation is either in progress or have been completed. This pin is an open-drain output pin.  Low level output: The device is busy with automatic erase (or automatic program) operation.  High level output: The device is ready for new operations, in the erase suspend mode or in reset mode. |

| Vcc       |              | Supply voltage                                                                                                                                                                                                                                                                                                                                                        |

| GND       | _            | Ground                                                                                                                                                                                                                                                                                                                                                                |

| NC        | _            | No connecton: Not internally connected. (The signal can be connected.)                                                                                                                                                                                                                                                                                                |

# Erase Block Layout

| $\mu$ PD29F008Lxx-xxxT           | Address          |

|----------------------------------|------------------|

| Protection Block<br>(16 K bytes) | FFFFFH           |

| Condition Block                  | FC000H<br>FBFFFH |

| (8 K bytes)  Condition Block     | FA000H<br>F9FFFH |

| (8 K bytes)                      | F8000H<br>F7FFFH |

| Main Block<br>(32 K bytes)       | F0000H           |

| Main Block<br>(64 K bytes)       | EFFFFH<br>E0000H |

| Main Block<br>(64 K bytes)       | DFFFFH<br>D0000H |

| Main Block<br>(64 K bytes)       | CFFFFH           |

| Main Block<br>(64 K bytes)       | C0000H<br>BFFFFH |

| Main Block<br>(64 K bytes)       | B0000H<br>AFFFFH |

| Main Block                       | A0000H<br>9FFFFH |

| (64 K bytes)                     | 90000H<br>8FFFFH |

| Main Block<br>(64 K bytes)       | 80000H           |

| Main Block<br>(64 K bytes)       | 7FFFFH<br>70000H |

| Main Block<br>(64K bytes)        | 6FFFFH           |

| Main Block<br>(64 K bytes)       | 60000H<br>5FFFFH |

| Main Block                       | 50000H<br>4FFFFH |

| (64 K bytes)                     | 40000H<br>3FFFFH |

| Main Block<br>(64 K bytes)       | 30000H<br>2FFFFH |

| Main Block<br>(64 K bytes)       | 20000H<br>1FFFFH |

| Main Block<br>(64 K bytes)       | 16664<br>10000H  |

| Main Block<br>(64 K bytes)       | OFFFFH           |

|                                  | 00000H           |

| μPD29F008Lxx-xxxB                | Address          |

|----------------------------------|------------------|

| Main Block<br>(64 K bytes)       | FFFFFH           |

| Main Block                       | F0000H<br>EFFFFH |

| (64 K bytes)                     | E0000H<br>DFFFFH |

| Main Block<br>(64 K bytes)       | DOOOOH           |

| Main Block<br>(64 K bytes)       | CFFFFH           |

| Main Block                       | C0000H<br>BFFFFH |

| (64 K bytes)                     | B0000H<br>AFFFFH |

| Main Block<br>(64 K bytes)       | A0000H           |

| Main Block<br>(64 K bytes)       | 9FFFFH           |

| Main Block                       | 90000H<br>8FFFFH |

| (64 K bytes)                     | 80000H           |

| Main Block<br>(64 K bytes)       | 70000H           |

| Main Block<br>(64 K bytes)       | 6FFFFH           |

| Main Block                       | 60000H<br>5FFFFH |

| (64 K bytes)                     | 50000H<br>4FFFFH |

| Main Block<br>(64 K bytes)       | 40000H           |

| Main Block<br>(64 K bytes)       | 3FFFFH           |

| Main Block                       | 30000H<br>2FFFFH |

| (64 K bytes)                     | 20000H           |

| Main Block<br>(64 K bytes)       | 10000H           |

| Main Block<br>(32 K bytes)       | 0FFFFH<br>08000H |

| Condition Block<br>(8 K bytes)   | 07FFFH<br>06000H |

| Condition Block<br>(8 K bytes)   | 05FFFH<br>04000H |

| Protection Block<br>(16 K bytes) | 03FFFH<br>00000H |

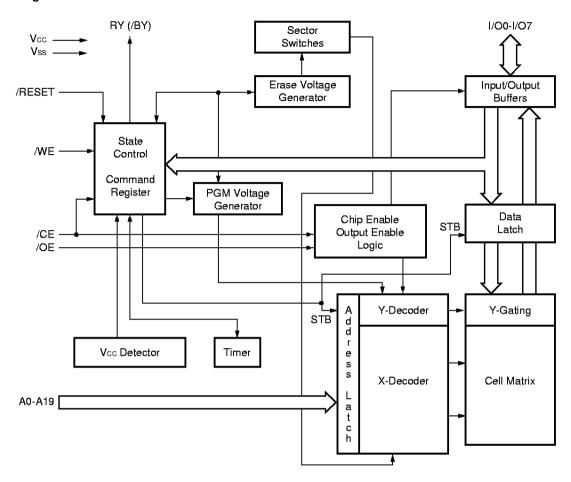

## **Block Diagram**

## **Operation Mode**

| Pin Name<br>Mode                                      | /RESET          | /CE | /OE | /WE      | <b>A</b> 9 | A6 | A1              | AO  | 1/00-1/07   |

|-------------------------------------------------------|-----------------|-----|-----|----------|------------|----|-----------------|-----|-------------|

| Product ID code,<br>Manufacturer code <sup>Note</sup> | V⊪              | V⊩  | V⊩  | V⊪       | <b>V</b> H | V⊩ | V⊩              | V∟  | ID          |

| Product ID code,<br>Device code                       | Vн              | V⊩  | V⊩  | VIH      | VH         | V⊩ | V⊩              | VIH | ID          |

| Read                                                  | Vн              | V⊩  | V⊩  | V⊪       | A9         | A6 | A1              | AO  | Data output |

| Standby                                               | V <sub>IH</sub> | VIH | ×   | ×        | ×          | ×  | ×               | ×   | Hi-Z        |

| Output disable                                        | <b>V</b> IH     | V⊩  | V⊪  | V⊪       | ×          | ×  | ×               | ×   | Hi-Z        |

| Write                                                 | V <sub>IH</sub> | V⊩  | Vн  | V⊩       | A9         | A6 | A1              | AO  | Data input  |

| Enable sector protect                                 | VIH             | V⊩  | Vн  | Pulse/V⊩ | Vн         | V⊩ | V <sub>IH</sub> | V⊾  | Code        |

| Verify sector protect                                 | VIH             | V⊩  | V⊩  | V⊪       | <b>V</b> H | V⊩ | V⊪              | V⊾  | Code        |

| Temporary sector unprotect                            | VH              | ×   | ×   | ×        | ×          | ×  | ×               | ×   | ×           |

| Reset                                                 | V⊩              | ×   | ×   | ×        | ×          | ×  | ×               | ×   | Hi-Z        |

**Note** Manufacturer and device codes may also be accessed via a command register write sequence. Please refer to Command Definition.

**Remark**  $V_H = 12.0 V \pm 0.5 V$

× : Don't care (ViH or ViL)

See DC characteristics for voltage levels.

ID = Data Read from Location address during Read product ID code.

10H: Manufacturer code

3EH: Device code for a Type T 37H: Device code for a Type B

## **Operation Mode (Command Mode)**

| Command Sequence     | Bus<br>Cycles | First Write | cycle | Second<br>write o | cycle | Third<br>write | cycle | Fourth<br>write o | cycle | Fifth<br>write o | ycle | Sixth<br>write o | cycle |

|----------------------|---------------|-------------|-------|-------------------|-------|----------------|-------|-------------------|-------|------------------|------|------------------|-------|

|                      |               | Address     | Data  | Address           | Data  | Address        | Data  | Address           | Data  | Address          | Data | Address          | Data  |

| Reset/Read           | 1             | xxxxH       | F0H   | -                 | _     | ı              | ı     | ı                 | ı     | ı                | -    | -                | _     |

| Read product ID code | 4             | 5555H       | ААН   | 2AAAH             | 55H   | 5555H          | 90H   | IA                | ID    | -                | -    | -                | _     |

| Program              | 4             | 5555H       | ААН   | 2AAAH             | 55H   | 5555H          | A0H   | PA                | PD    | -                | -    | -                | -     |

| Chip erase           | 6             | 5555H       | ААН   | 2AAAH             | 55H   | 5555H          | 80H   | 5555H             | ААН   | 2AAAH            | 55H  | 5555H            | 10H   |

| Sector erase         | 6             | 5555H       | ААН   | 2AAAH             | 55H   | 5555H          | 80H   | 5555H             | ААН   | 2AAAH            | 55H  | EA               | 30H   |

| Sector erase suspend | 1             | xxxxH       | вон   | -                 | -     | -              | -     | -                 | -     | -                | -    | -                | -     |

| Sector erase Resume  | 1             | xxxxH       | 30H   | -                 | _     | -              | -     | -                 | 1     | -                | -    | -                | _     |

Remark x: VIL or VIH

EA = Block Address of Memory Location to be erased.

PA = Address of Memory Location to be programmed.

PD = Data to be programmed at Location PA.

IA = Identifier Address (00000H: Address for Manufacturer ID, 00001H: Address for Device ID).

ID = Data Read from Location IA during Read product ID code.

10H: Manufacturer code

3EH: Device code for a Type T 37H: Device code for a Type B

**Preliminary Data Sheet**

#### Hardware Sequence Flags

|                      | Status           |                  | 1/07  | I/O6   | I/O5 | I/O3 | 1/02   | RY(/BY) |

|----------------------|------------------|------------------|-------|--------|------|------|--------|---------|

| In progress          | Programming      |                  | /I/O7 | Toggle | 0    | 0    | 1      | 0       |

|                      | Auto erase       |                  | 0     | Toggle | 0    | 1    | Toggle | 0       |

|                      | Erase suspend    | Erase sector     | 1     | 1      | 0    | 0    | Toggle | 1       |

|                      |                  | Non erase sector | DATA  | DATA   | DATA | DATA | DATA   | 1       |

|                      | Program in suspe | nd               | /1/07 | Toggle | 0    | 0    | 1      | 0       |

| Exceeded time limits | Programming      |                  | /1/07 | Toggle | 1    | 0    | 1      | 0       |

|                      | Auto erase       |                  | 0     | Toggle | 1    | 1    | N/A    | 0       |

|                      | Program in erase | suspend          | /1/07 | Toggle | 1    | 0    | N/A    | 0       |

#### /DATA Polling (I/O7)

/DATA Polling supports system software by indicating the precise end of write or erase cycles.

On this support, the next write or erase cycle can be started as soon as previous cycle has completed.

#### • How to use /DATA Polling

<Write Operation>

- After writing data by write operation, fix /WE = "H".

(See /DATA polling During Program or Erase Operation Timing Chart.)

- (2) Compare the read data from I/O7 with just before written data.

- (3) In coincidence with the both data,  $\mu$ PD29F008L will complete its write cycle. Then start the next cycle. In case of still in progress, the data on I/O7 is inverted just before written data.

#### <Erase Operation>

- After setting erase command by write operation, fix /WE = "H".

(See /DATA polling During Program or Erase Operation Timing Chart.)

- (2) If the read data on I/O7 is "1",  $\mu$ PD29F008L has completed its erase cycle, and the other means erase cycle is in progress.

#### Toggle Bit Function (I/O6)

Toggle bit function supports system software by indicating the precise end of write or erase cycles, too.

- · How to use Toggle bit function

- After writing data by command write operation, fix /WE = "H".

(See Toggle Bit During Program /Erase Algorithm Operation Timing Chart.)

- (2) Watch the read data on I/O6.

- (3) If the write or erase operation is in progress, the read data from I/O6 will toggle on every reading. And if the operation has completed, the read data will stop toggling.

#### Exceed Timing Limit (I/O5)

Exceed timing limit function supports system software by indicating the write or erase time has exceeded the specific limits.

- How to use Exceed Timing Limit function

- (1) After writing data by command write operation, fix /WE = "H".

- (2) Watch the read data on I/O5.

- (3) If the write or erase operation has not successfully completed, I/O5 will indicate "1".

#### Sector Erase Timer (I/O3)

Sector erase timer function supports system software by indicating the acceptance of sequential sector erase command write.

- How to use Sector Erase Timer function

- (1) After writing initial sector erase command sequence, watch the data on I/O3.

- (2) If the data on I/O3 is "1",  $\mu$ PD29F008L will not accept subsequent command until the erase operation is completed as indicated by Data Polling (I/O7) or Toggle Bit (I/O6).

- (3) And if the data on I/O3 is "0",  $\mu$ PD29F008L will be able to accept subsequent command.

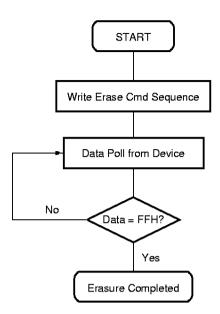

#### **Erase Flowchart**

# Erase Algorithm

| Bus operation | Command sequence | Comments                        |

|---------------|------------------|---------------------------------|

| Standby       |                  |                                 |

| Write         | Erase            |                                 |

| Read          |                  | /DATA polling to verify erasure |

| Standby       |                  | Compare output to FFH.          |

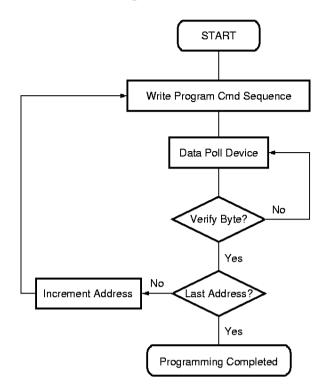

## **Program Flowchart**

# Program Algorithm

| Bus operation           | Command sequence | Comments                             |

|-------------------------|------------------|--------------------------------------|

| Standby <sup>Note</sup> |                  |                                      |

| Write                   | Program          | Valid address/data                   |

| Read                    |                  | /DATA polling to verify programming  |

| Standby <sup>Note</sup> |                  | Compare data output to data expected |

Note Device is either powered-down, erase inhibit, or program inhibit.

## **Electrical Characteristics (Preliminary)**

## **Absolute Maximum Ratings**

| Parameter                        | Symbol     | Test conditions                      | Ratings                       | Unit |

|----------------------------------|------------|--------------------------------------|-------------------------------|------|

| Supply voltage                   | Vcc        | with respect to GND                  | -0.5 to +5.5                  | ٧    |

| Input voltage                    | Vı         | with respect to GND                  | -0.5 <sup>Note</sup> to +5.5  | ٧    |

|                                  | Vı         | with respect to GND, A9, /RESET, /OE | -0.5 <sup>Note</sup> to +13.5 |      |

| Output voltage                   | <b>V</b> o | with respect to GND                  | -0.5 <sup>Note</sup> to +5.5  | ٧    |

| Operating ambient temperature    | Ta         |                                      | -20 to +70                    | ۰C   |

| Storage temperature              | Tstg       |                                      | -65 to +125                   | °C   |

| Storage temperature (under Bias) | Tbias      |                                      | -20 to +80                    | °C   |

**Note**  $V_1$ ,  $V_0 = -2.0 \text{ V (MIN.)}$  for pulse width  $\leq 20 \text{ ns.}$

Caution Exposing the device to stress above those listed in absolute maximum ratings could cause permanent damage. The device is not meant to be operated under conditions outside the limits described in the operational sections of this characteristics. Exposure to absoulte maximum rating conditions for extended periods may affect device reliability.

## Capacitance ( $T_A = 25$ °C, f = 1 MHz)

| Parameter          | Symbol | Test conditions | MIN. | TYP. | MAX. | Unit |

|--------------------|--------|-----------------|------|------|------|------|

| Input capacitance  | С      | VIN = 0 V       |      | 6.0  | 7.5  | pF   |

| Output capacitance | Co     | Vout = 0 V      |      | 8.5  | 12.0 | рF   |

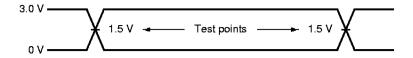

#### **AC Test Conditions**

Input Waveform (Rise/Fall time ≤ 10 ns)

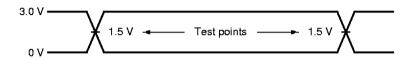

## **Output Waveform**

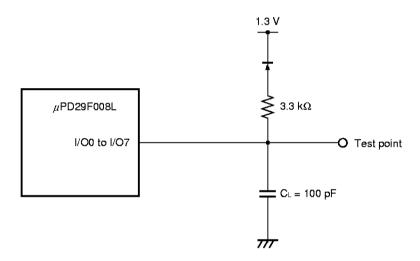

## **Output Load**

Remark CL includes capacitances of the probe and jig, and stray capacitances.

## Read Operation

# **Recommended Operating Conditions**

| Parameter                     | Symbol | MIN.                  | TYP. | MAX.                      | Unit |

|-------------------------------|--------|-----------------------|------|---------------------------|------|

| Supply voltage                | Vcc    | 2.7                   | 3.0  | 3.6                       | ٧    |

| High level input voltage      | VIH    | 2.0                   |      | Vcc +0.5 <sup>Note1</sup> | ٧    |

| Low level input voltage       | V⊩     | -0.5 <sup>Nate2</sup> |      | +0.8                      | ٧    |

| Operating ambient temperature | Ta     | -20                   |      | +70                       | °C   |

**Notes** 1.  $V_{IH} = V_{CC} + 1.0 \text{ V (MAX.)}$  for pulse width  $\leq 20 \text{ ns}$

2.  $V_{IL} = -1.0 \text{ V (MIN.)}$  for pulse width  $\leq 20 \text{ ns}$

# DC Characteristics (Recommended operating conditions unless otherwise noted)

| Parameter                 | Symbol            | Test conditions                                          | MIN.    | TYP. | MAX. | Unit |

|---------------------------|-------------------|----------------------------------------------------------|---------|------|------|------|

| High level output voltage | <b>V</b> он1      | lон = −2.0 mA, Vcc = Vcc (MIN.)                          | 2.4     |      |      | ٧    |

|                           | V <sub>OH2</sub>  | lон = −2.0 mA, Vcc = Vcc (MIN.)                          | 0.85 V∞ |      |      | ٧    |

|                           |                   | Іон = −100 μA, Vcc = Vcc (MIN.)                          | V∞-0.4  |      |      |      |

| Low level output voltage  | <b>V</b> ol1      | loL = 4.0 mA, Vcc = Vcc (MIN.)                           |         |      | 0.45 | ٧    |

|                           | <b>V</b> OL2      | loL = 5.8 mA, Vcc = Vcc (MIN.)                           |         |      | 0.45 |      |

| Output leakage current    | ILO               | Vout = 0 V to Vcc, /OE = VH                              | -1.0    |      | +1.0 | μΑ   |

| Input leakage current     | ILI               | VIN = 0 V to Vcc                                         | -1.0    |      | +1.0 | μΑ   |

| Vcc supply current        | Icca1             | V <sub>IN</sub> = V <sub>IH</sub> /V <sub>IL</sub> fixed |         |      | 35   | mA   |

|                           | ICCA2             | lout = 0 mA, /CE = VL, minimum cycle time                |         |      | 45   | mA   |

| Vcc standby current       | Iccs <sub>1</sub> | $/CE = /RESET = V_H, V_\infty = V_\infty (MAX.)$         |         |      | 250  | μΑ   |

|                           | Iccs <sub>2</sub> | /CE ≥ = Vcc -0.2 V                                       |         |      | 5    | μА   |

| Reset supply current      | Icoslp            | /RESET = GND ± 0.2 V                                     |         |      | 5    | μΑ   |

## AC Characteristics (Recommended operating conditions unless otherwise noted)

| D                             | 0 1 1       | T1                           | μPD29F0 | 008L-B12 | μPD29F0 | l lmit |      |

|-------------------------------|-------------|------------------------------|---------|----------|---------|--------|------|

| Parameter                     | Symbol      | Test condition               | MIN.    | MAX.     | MIN.    | MAX.   | Unit |

| Address to output delay       | tacc        | /CE = /OE = V <sub>I</sub> L |         | 120      |         | 150    | ns   |

| /CE to output delay           | tce         | /OE = V∟                     |         | 120      |         | 150    | ns   |

| /OE to output delay           | <b>t</b> oe | /CE = V ∟                    |         | 50       |         | 55     | ns   |

| /OE or /CE output float delay | <b>t</b> of | /CE = V                      |         | 30       |         | 40     | ns   |

| Address to output hold        | <b>t</b> oн | /CE = /OE = <b>V</b> ⊩       | 0       |          | 0       | ·      | ns   |

Remark toF is the time from inactivation of /CE or /OE to high-impedance state output.

#### Read Mode Timing Chart

Notes 1. For read operation, the definition of access time is as follows.

| Access time definition | /CE input condition        | /OE input conditon  |

|------------------------|----------------------------|---------------------|

| tacc                   | before stabilizing address | before (tacc – toe) |

| <b>t</b> oE            |                            | after (tacc - toe)  |

| tce                    | after stabilizing address  | before (tc= - to=)  |

| <b>t</b> oE            |                            | after (tc=- to=)    |

2. top is the time from inactivation of /CE or /OE to high-impedance state output.

# Program and Erase Operation

# **Recommended Operating Conditions**

| Parameter                     | Symbol | MIN.                  | TYP. | MAX.           | Unit |

|-------------------------------|--------|-----------------------|------|----------------|------|

| Supply voltage                | Vcc    | 2.7                   | 3.0  | 3.6            | ٧    |

| High level input voltage 1    | VH     | 2.0                   |      | Vcc +0.5 Note1 | ٧    |

| High level input voltage 2    | VH     | 11.5                  |      | 12.5           | ٧    |

| Low level input voltage       | V⊩     | -0.3 <sup>Note2</sup> |      | +0.8           | ٧    |

| Operating ambient temperature | Та     | -20                   |      | +70            | °C   |

**Notes** 1.  $V_{IH} = V_{CC} + 0.6 \text{ V (MAX.)}$  for pulse width  $\leq 20 \text{ ns}$

2.  $V_{IL} = -0.6 \text{ V (MIN.)}$  for pulse width  $\leq 20 \text{ ns}$

# DC Characteristics (Recommended operating conditions unless otherwise noted)

| Parame                    | Parameter S |                   | Test conditions                                                                  | MIN.    | TYP. | MAX.    | Unit |

|---------------------------|-------------|-------------------|----------------------------------------------------------------------------------|---------|------|---------|------|

| High level output voltage |             | <b>V</b> 0H1      | lон = −2.0 mA                                                                    | 2.4     |      |         | ٧    |

|                           |             | V <sub>OH2</sub>  | lон = −2.0 mA                                                                    | 0.85 V∞ |      |         | ٧    |

|                           |             |                   | Іон = –100 <b>µ</b> А                                                            | V∞-0.4  |      |         |      |

| Low level output vo       | Itage       | <b>V</b> OL1      | loL = 4.0 mA, Vcc = Vcc (MIN.)                                                   |         |      | 0.45    | ٧    |

|                           |             | V <sub>OL2</sub>  | loL = 5.8 mA, Vcc = Vcc (MIN.)                                                   |         |      | 0.45    |      |

| Output leakage curr       | ent         | ILO               | Vout = 0 V to Vcc, /OE = ViH                                                     | -1.0    |      | +1.0    | μΑ   |

| Input leakage curre       | nt          | lu                | VIN = 0 V to Vcc                                                                 | -1.0    |      | +1.0 μA |      |

| Vcc supply current        | Standby     | Iccs <sub>1</sub> | /CE = /RESET = V⊩                                                                |         |      | 250     | μА   |

|                           |             | Iccs <sub>2</sub> | /CE = /RESET = V∞ ± 0.2 V                                                        |         |      | 5       | μА   |

|                           | Reset       | Iccslp            | /RESET = GND ± 0.2 V                                                             |         |      | 5       | μΑ   |

|                           | Read        | IGGA1             | lout = 0 mA, /CE = $V_{\parallel}$ , $V_{N} = V_{\parallel}/V_{\parallel}$ fixed |         |      | 35      | mA   |

|                           |             | IGGA2             | lour = 0 mA, /CE = V <sub>L</sub> , minimum cycle time                           |         |      | 45      | mA   |

|                           | Program     | Iccp              |                                                                                  |         |      | 35      | mA   |

|                           | Erase       | ICCE              |                                                                                  |         |      | 35      | mA   |

| Low Vcc lock-out vc       | oltage      | <b>V</b> LKO      |                                                                                  | 2.3     |      | 2.5     | ٧    |

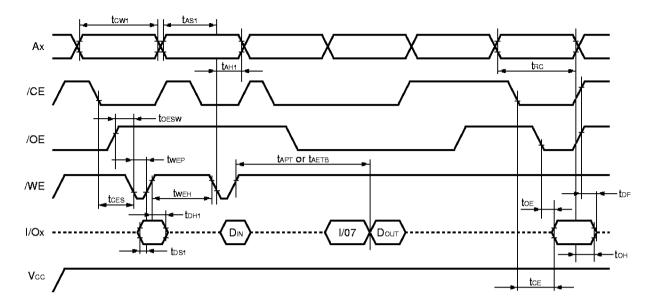

# AC Characteristics (1) (WE Control) (Recommended operating conditions unless otherwise noted)

|                                   | Parameter                | C                | μΡΕ  | )29F008L- | B12  | μΡΕ  | )29F008L- | B15  |      |

|-----------------------------------|--------------------------|------------------|------|-----------|------|------|-----------|------|------|

| raiametei                         |                          | Symbol           | MIN. | TYP.      | MAX. | MIN. | TYP.      | MAX. | Unit |

| Cycle time                        |                          | tow <sub>1</sub> | 120  |           |      | 150  |           |      | ns   |

| Address setup t                   | ime 1                    | tas1             | 0    |           |      | 0    |           |      | ns   |

| Address hold tir                  | ne 1                     | <b>t</b> ah1     | 50   |           |      | 65   |           |      | ns   |

| Data input setu                   | p time 1                 | <b>t</b> osı     | 50   |           |      | 65   |           |      | ns   |

| Data input hold                   | time 1                   | <b>t</b> oH1     | 0    |           |      | 0    |           |      | ns   |

| /OE setup time                    |                          | toes             | 0    |           |      | 0    |           |      | ns   |

| /OE hold time                     | Read                     | <b>t</b> oeh     | 0    |           |      | 0    |           |      | ns   |

|                                   | Toggle and /DATA polling |                  | 10   |           |      | 10   |           |      | ns   |

| Read recovery                     | time before write        | toehc            | 0    |           |      | 0    |           |      | ns   |

| /CE setup time                    |                          | tces             | 0    |           |      | 0    |           |      | ns   |

| /CE hold time (\                  | <b>/</b> ∟)              | tcel             | 0    |           |      | 0    |           |      | ns   |

| Write pulse widt                  | th                       | twep             | 50   |           |      | 65   |           |      | ns   |

| /WE hold time                     |                          | twен             | 30   |           |      | 35   |           |      | ns   |

| Total program ti                  | ime                      | <b>t</b> apt     |      | 9         |      |      | 9         |      | μs   |

| Total erase time                  | e                        | <b>t</b> aetb    |      | 1         |      |      | 1         |      | s    |

| Vcc setup time                    |                          | tvcs             | 50   |           |      | 50   |           |      | μs   |

| Write Recovery time from RY (/BY) |                          | <b>t</b> ra      | 0    |           |      | 0    |           |      | ns   |

| /RESET low time                   |                          | <b>t</b> RL      | 500  |           |      | 500  |           |      | ns   |

| /RESET high time before read      |                          | <b>t</b> prнн    | 50   |           |      | 50   |           |      | ns   |

| /RESET to slee                    | p time                   | tslp             | 20   |           |      | 20   |           |      | μs   |

| Program/Erase                     | valid to RY (/BY) delay  | teusy            | 90   |           |      | 90   |           |      | ns   |

**Remark** Duration of the program or erase operation is variable and is calculated in the internal algorthms.

# Write Operation Timing Chart

Remarks 1. DIN is DATA input to the device.

- 2. I/O7 is the output of the complement of the data written to the device.

- 3. Dout is the output of the data written to the device.

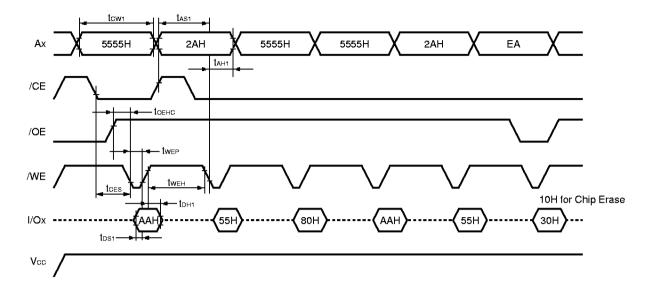

#### Chip/Sector Erase Operation Timing Chart

- **Remarks 1.** EA is the sector address for Sector Erase. Addresses = Don't care for Chip Erase.

- 2. These waveforms are for the word mode.

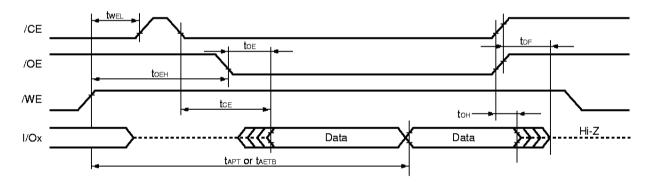

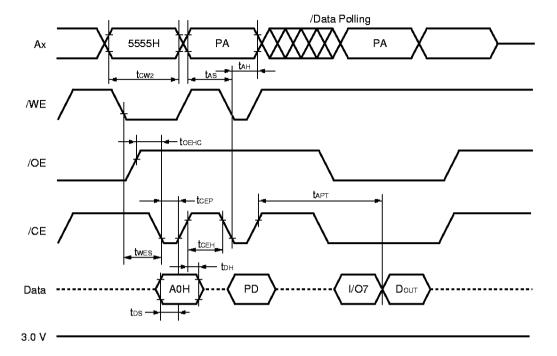

## /Data Polling During Program or Erase Operation Timing Chart

**Remark** I/O7 = Valid Data (The device has completed the Program or Erase operation).

# Toggle Bit During Program/Erase Algorithm Operation Timing Chart

**Remark** I/O6 stops toggling (The device has completed the Program or Erase operation).

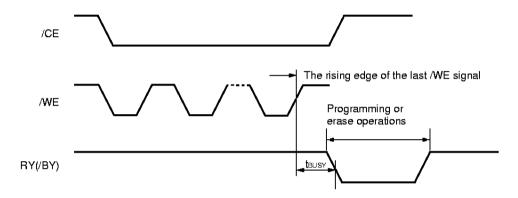

# RY (/BY) Timing Chart Program/Erase Operation

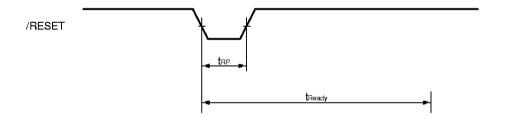

# /Reset Timing Chart

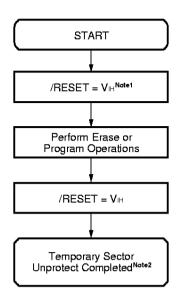

## **Temporary Sector Unprotect Flowchart**

Notes 1. All protected sectors unprotected.

2. All previously protected sectors are protected once again.

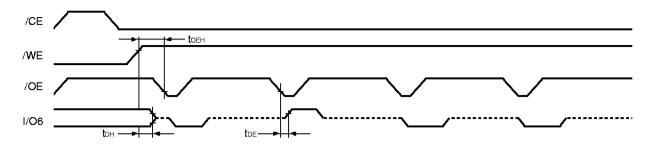

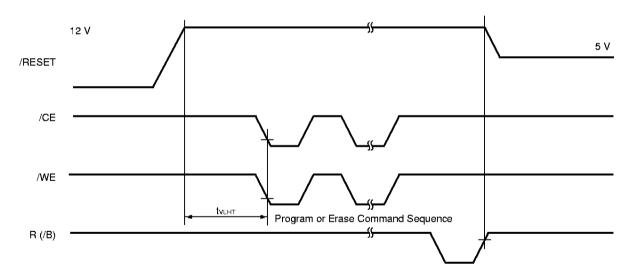

## **Temporary Sector Unprotect Timing Chart**

# AC Characteristics (2) (/CE Control) (Recommended operating conditions unless otherwise noted)

|                      | Parameter                |                  | μΡΕ  | )29F008L- | B12  | μΡΕ  | )29F008L- | B15  | - Unit |

|----------------------|--------------------------|------------------|------|-----------|------|------|-----------|------|--------|

| rarameter            |                          | Symbol           | MIN. | TYP.      | MAX. | MIN. | TYP.      | MAX. |        |

| Write cycle time     | •                        | tcw2             | 120  |           |      | 150  |           |      | ns     |

| Address setup t      | ime 2                    | tas2             | 0    |           |      | 0    |           |      | ns     |

| Address hold tir     | ne 2                     | t <sub>AH2</sub> | 50   |           |      | 50   |           |      | ns     |

| Data input setup     | time 2                   | t <sub>DS2</sub> | 50   |           |      | 50   |           |      | ns     |

| Data input hold      | time 2                   | <b>t</b> DH2     | 0    |           |      | 0    |           |      | ns     |

| /OE setup time       |                          | <b>t</b> oes     | 0    |           |      | 0    |           |      | ns     |

| /OE hold time        | Read                     | <b>t</b> 0EH     | 0    |           |      | 0    |           |      | ns     |

|                      | Toggle and /DATA polling |                  | 10   |           |      | 10   |           |      | ns     |

| Read recovery t      | time before write        | toenc            | 0    |           |      | 0    |           |      | ns     |

| /WE setup time       |                          | twes             | 0    |           |      | 0    |           |      | ns     |

| /WE hold time (      | VL)                      | <b>t</b> weL     | 0    |           |      | 0    |           |      | ns     |

| /CE pulse width      |                          | <b>t</b> cep     | 50   |           |      | 50   |           |      | ns     |

| /CE pulse width high |                          | <b>t</b> ceh     | 20   |           |      | 20   |           |      | ns     |

| Total program time   |                          | <b>t</b> apt     |      | 9         |      |      | 9         |      | μs     |

| Total erase time     | Nate -                   | <b>t</b> aetb    |      | 1         | 10   |      | 1         | 10   | s      |

Note This does not include the preprogramming time.

## Alternate /CE Controlled Write Operation Timing Chart

Remarks 1. PA is address of the memory location to be programmed.

- 2. PD is data to be programmed at byte address.

- 3. I/O7 is the output of the complement of the data written to the device.

- 4. DOUT is the output of the data written to the device.

- 5. Figure indicates last two bus cycles of four bus cycle sequence.

- 6. These waveforms are for the word mode.

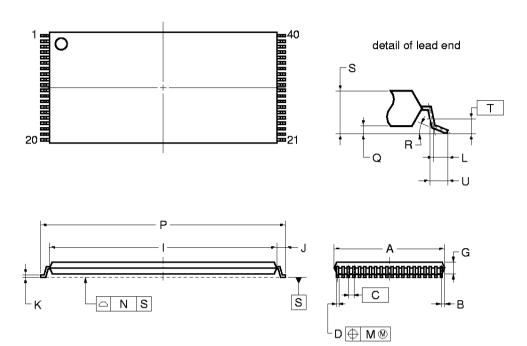

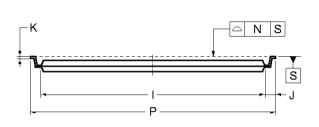

## Package Drawings

# ★ 40 PIN PLASTIC TSOP(I) (10x20)

#### NOTES

- 1. Controlling dimention millimeter.

- 2. Each lead centerline is located within 0.08 mm (0.003 inch) of its true position (T.P.) at maximum material condition.

- "A" excludes mold flash. (Includes mold flash: 10.4 mm MAX. <0.410 inch MAX.>)

| ITEM | MILLIMETERS  | INCHES                             |

|------|--------------|------------------------------------|

| Α    | 10.0±0.1     | $0.394^{+0.004}_{-0.005}$          |

| В    | 0.45 MAX.    | 0.018 MAX.                         |

| С    | 0.5 (T.P.)   | 0.020 (T.P.)                       |

| D    | 0.22±0.05    | $0.009^{+0.002}_{-0.003}$          |

| G    | 0.97±0.05    | $0.038\substack{+0.003 \\ -0.002}$ |

| I    | 18.4±0.1     | $0.724^{+0.005}_{-0.004}$          |

| J    | 0.8±0.1      | $0.031^{+0.005}_{-0.004}$          |

| K    | 0.145±0.05   | $0.006^{+0.004}_{-0.002}$          |

| L    | 0.5          | 0.020                              |

| М    | 0.10         | 0.004                              |

| N    | 0.10         | 0.004                              |

| Р    | 20.0±0.2     | $0.787^{+0.009}_{-0.008}$          |

| Q    | 0.1±0.05     | $0.004^{+0.002}_{-0.003}$          |

| R    | 3°+5°<br>-3° | 3°+5°                              |

| S    | 1.2 MAX.     | 0.047 MAX.                         |

| Т    | 0.25         | 0.010                              |

| U    | 0.6±0.15     | $0.024\substack{+0.006 \\ -0.007}$ |

|      | ·            | <u> </u>                           |

S40GZ-50-LJH1

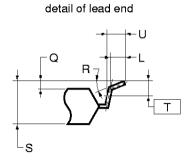

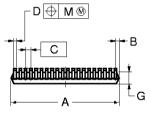

# ★ 40 PIN PLASTIC TSOP(I) (10x20)

#### NOTES

- 1. Controlling dimention millimeter.

- 2. Each lead centerline is located within 0.08 mm (0.003 inch) of its true position (T.P.) at maximum material condition.

- "A" excludes mold flash. (Includes mold flash: 10.4 mm MAX. <0.410 inch MAX.>)

| ITEM | MILLIMETERS  | INCHES                    |

|------|--------------|---------------------------|

| А    | 10.0±0.1     | $0.394^{+0.004}_{-0.005}$ |

| В    | 0.45 MAX.    | 0.018 MAX.                |

| С    | 0.5 (T.P.)   | 0.020 (T.P.)              |

| D    | 0.22±0.05    | $0.009^{+0.002}_{-0.003}$ |

| G    | 0.97±0.05    | $0.038^{+0.003}_{-0.002}$ |

| ı    | 18.4±0.1     | $0.724^{+0.005}_{-0.004}$ |

| J    | 0.8±0.1      | $0.031^{+0.005}_{-0.004}$ |

| K    | 0.145±0.05   | $0.006^{+0.002}_{-0.003}$ |

| L    | 0.5          | 0.020                     |

| М    | 0.10         | 0.004                     |

| N    | 0.10         | 0.004                     |

| Р    | 20.0±0.2     | $0.787^{+0.009}_{-0.008}$ |

| Q    | 0.1±0.05     | $0.004^{+0.002}_{-0.003}$ |

| R    | 3°+5°<br>-3° | 3°+5°                     |

| s    | 1.2 MAX.     | 0.047 MAX.                |

| Т    | 0.25         | 0.010                     |

| U    | 0.6±0.15     | $0.024^{+0.006}_{-0.007}$ |

S40GZ-50-LKH1

[MEMO]

[MEMO]

[MEMO]

NEC

# NOTES FOR CMOS DEVICES-

# (1) PRECAUTION AGAINST ESD FOR SEMICONDUCTORS

Note: Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it once, when it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor devices on it.

## (2) HANDLING OF UNUSED INPUT PINS FOR CMOS

Note: No connection for CMOS device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND with a resistor, if it is considered to have a possibility of being an output pin. All handling related to the unused pins must be judged device by device and related specifications governing the devices.

# **③ STATUS BEFORE INITIALIZATION OF MOS DEVICES**

Note: Power-on does not necessarily define initial status of MOS device. Production process of MOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the devices with reset function have not yet been initialized. Hence, power-on does not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the reset signal is received. Reset operation must be executed immediately after power-on for devices having reset function.

31

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.

NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from use of a device described herein or any other liability arising from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or others.

While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices, the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons or property arising from a defect in an NEC semiconductor device, customers must incorporate sufficient safety measures in its design, such as redundancy, fire-containment, and anti-failure features.

NEC devices are classified into the following three quality grades:

"Standard", "Special", and "Specific". The Specific quality grade applies only to devices developed based on a customer designated "quality assurance program" for a specific application. The recommended applications of a device depend on its quality grade, as indicated below. Customers must check the quality grade of each device before using it in a particular application.

Standard: Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

Special: Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

Specific: Aircrafts, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems or medical equipment for life support, etc.

The quality grade of NEC devices is "Standard" unless otherwise specified in NEC's Data Sheets or Data Books. If customers intend to use NEC devices for applications other than those specified for Standard quality grade, they should contact an NEC sales representative in advance.

Anti-radioactive design is not implemented in this product.

M4 96.5