# **Signetics**

### **Logic Products**

### **FEATURES**

- 8-bit transparent latch 8TS805

- 8-bit positive, edge-triggered register – 8TS806

- 3-State output buffers

- Common 3-State Output Enable

- Independent register and 3-State buffer operation

### DESCRIPTION

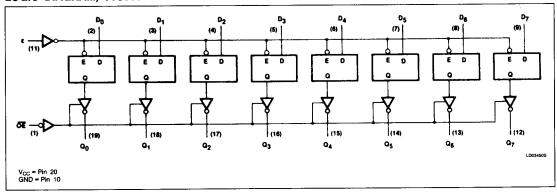

The 8TS805 is an octal, transparent latch coupled to eight 3-State output buffers. The two sections of the device are controlled independently by Latch Enable (E) and Output Enable  $(\overline{OE})$  control gates.

The data on the D inputs are transferred to the latch outputs when the Latch Enable (E) input is HIGH. The latch remains transparent to the data inputs while E is HIGH, and stores the data present one set-up time before the Highto-Low enable transition. The enable gate has about 400mV of hysteresis built

# 8TS805, 806 Latches/Flip-Flops

8TS805 Octal Transparent Latch With 3-State Outputs 8TS806 Octal D Flip-Flop With 3-State Outputs Product Specification

| TYPE   | TYPICAL PROPAGATION<br>DELAY | TYPICAL SUPPLY CURRENT (TOTAL) |

|--------|------------------------------|--------------------------------|

| 8TS805 | 10ns                         | 105mA                          |

| 8TS806 | 8ns                          | 116mA                          |

### ORDERING CODE

| PACKAGES    | COMMERCIAL RANGE<br>V <sub>CC</sub> = 5V ±5%; T <sub>A</sub> = 0°C to +70°C |

|-------------|-----------------------------------------------------------------------------|

| Plastic DIP | N8TS805N, N8TS806N                                                          |

#### NOTE:

For information regarding devices processed to Military Specifications, see the Signetics Military Products Data Manual.

# INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

| PINS | DESCRIPTION | 8TS   |

|------|-------------|-------|

| All  | Inputs      | 1Sul  |

| All  | Outputs     | 10Sul |

### NOTE:

An 8TS unit load (Sul) is  $50\mu A~I_{IH}$  and  $-2.0mA~I_{IL}$

in to help minimize problems that signal and ground noise can cause on the latching operation.

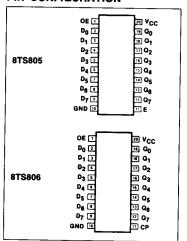

### PIN CONFIGURATION

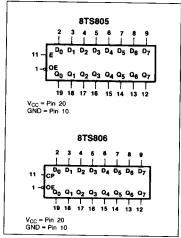

### LOGIC SYMBOL

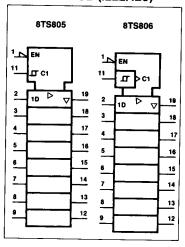

### LOGIC SYMBOL (IEEE/IEC)

8TS805, 806

The 3-State output buffers are designed to drive heavily loaded 3-State buses, MOS memories, or MOS microprocessors. The active LOW Output Enable ( $\overline{OE}$ ) controls all eight 3-State buffers independent of the latch operation. When  $\overline{OE}$  is LOW, the latched or transparent data appears at the outputs. When  $\overline{OE}$  is HIGH, the outputs are in the

HIGH impedance "off" state, which means they will neither drive nor load the bus.

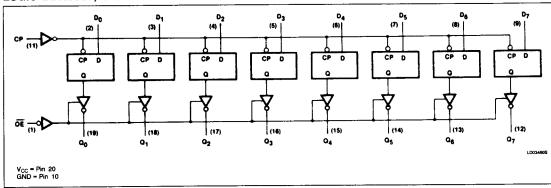

The 8TS806 is an 8-bit, edge-triggered register coupled to eight 3-State output buffers. The two sections of the device are controlled independently by the Clock (CP) and Output Enable  $(\overline{OE})$  control gates.

The register is fully edge triggered. The state of each D input, one set-up time before the LOW-to-HIGH clock transition, is transferred to the corresponding flip-flop's Q output. The clock buffer has about 400mV of hysteresis built in to help minimize problems that signal and ground noise can cause on the clocking operation.

### LOGIC DIAGRAM, 8TS805

### LOGIC DIAGRAM, 8TS806

### MODE SELECT - FUNCTION TABLE, 8TS805

|                          |        | INPUTS |        | INTERNAL DEGICTED | OUTPUTS                         |

|--------------------------|--------|--------|--------|-------------------|---------------------------------|

| OPERATING MODES          | ŌĒ     | E      | Dn     | INTERNAL REGISTER | Q <sub>0</sub> - Q <sub>7</sub> |

| Enable and read register | L      | н      | L<br>H | L<br>H            | L<br>H                          |

| Latch and read register  | L<br>L | L      | l<br>h | L<br>H            | L<br>H                          |

| Disable outputs          | Н      | Х      | х      | X                 | (Z)                             |

8TS805, 806

# MODE SELECT - FUNCTION TABLE, 8TS806

| OPERATING MODES                   | INPUTS |        |                |                   | OUTPUTS                         |

|-----------------------------------|--------|--------|----------------|-------------------|---------------------------------|

| OI ENATING MODES                  | ŌĒ     | СР     | D <sub>n</sub> | INTERNAL REGISTER | Q <sub>0</sub> - Q <sub>7</sub> |

| Load and read register            | L<br>L | †<br>† | l<br>h         | L<br>H            | L<br>H                          |

| Load register and disable outputs | Н      | х      | х              | Х                 | (Z)                             |

H = HIGH voltage level

# ABSOLUTE MAXIMUM RATINGS (Over operating free-air temperature range unless otherwise noted.)

|                  | PARAMETER                                      | S8TS                     | N8TS                     | UNIT |

|------------------|------------------------------------------------|--------------------------|--------------------------|------|

| V <sub>CC</sub>  | Supply voltage                                 | 7.0                      | 7.0                      |      |

| V <sub>IN</sub>  | Input voltage                                  | -0.5 to +5.5             | -0.5 to +5.5             |      |

| I <sub>IN</sub>  | Input current                                  | -30 to +5                | -30 to +5                | mA   |

| V <sub>OUT</sub> | Voltage applied to output in HIGH output state | -0.5 to +V <sub>CC</sub> | -0.5 to +V <sub>CC</sub> |      |

| TA               | Operating free-air temperature range           | -55 to +125              | 0 to 70                  | °C   |

# RECOMMENDED OPERATING CONDITIONS

|                 | PARAMETER                      |      | 8ТЅ |      |      |  |

|-----------------|--------------------------------|------|-----|------|------|--|

|                 | · Allows I set                 | Min  | Nom | Max  | UNIT |  |

| V <sub>CC</sub> | Supply voltage                 | 4.75 | 5.0 | 5.25 | V    |  |

| V <sub>IH</sub> | HIGH-level input voltage       | 2.0  |     |      | V    |  |

| V <sub>IL</sub> | LOW-level input voltage        |      |     | +0.8 | V    |  |

| lık             | Input clamp current            |      |     | -18  | mA   |  |

| Іон             | HIGH-level output current      |      |     | -6.5 | mA   |  |

| loL             | LOW-level output current       |      |     | 20   | mA   |  |

| TA              | Operating free-air temperature | 0    |     | 70   | °C   |  |

h = HIGH voltage level one set-up time prior to the LOW-to-HIGH clock transition or HIGH-to-LOW OE transition

L = LOW voltage level

t = LOW voltage level one set-up time prior to the LOW-to-HIGH clock transition or HIGH-to-LOW OE transition.

<sup>(</sup>Z) = HIGH impedance "off" state

<sup>1 =</sup> LOW-to-HIGH clock transition

X = Don't care

$V_{IL}$  = +0.7V MAX for S8TS at  $T_A$  = +125°C only.

8TS805, 806

### DC ELECTRICAL CHARACTERISTICS (Over recommended operating free-air temperature range unless otherwise noted.)

|                                                           |                                                                           |                                                                                               |                                                     |     | 8TS805, 80       | В     |      |

|-----------------------------------------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-----------------------------------------------------|-----|------------------|-------|------|

| PARAMETER                                                 | "                                                                         | TEST CONDITIONS                                                                               |                                                     |     | Typ <sup>2</sup> | Max   | UNIT |

| V <sub>OH</sub> HIGH-level output voltage                 | V <sub>CC</sub> = MIN, V<br>I <sub>OH</sub> = MAX                         | V <sub>CC</sub> = MIN, V <sub>IH</sub> = MIN, V <sub>IL</sub> = MAX,<br>I <sub>OH</sub> = MAX |                                                     | 2.4 | 3.1              |       | ٧    |

| V <sub>OL</sub> LOW-level output voltage                  | V <sub>CC</sub> = MIN,<br>V <sub>IH</sub> = MIN,<br>V <sub>IL</sub> = MAX |                                                                                               | i <sub>OL</sub> = MAX                               |     |                  | 0.5   | ٧    |

| V <sub>IK</sub> Input clamp voltage                       | V <sub>CC</sub> = MIN,                                                    | I <sub>I</sub> = I <sub>IK</sub>                                                              |                                                     |     |                  | -1.2  | ٧    |

| Off-state output current, IOZH HIGH-level voltage applied | V <sub>CC</sub> = MAX, V <sub>IH</sub> = MIN, V <sub>O</sub> = 2.4V       |                                                                                               |                                                     |     |                  | 50    | μΑ   |

| Off-state output current, IOZL LOW-level voltage applied  | V <sub>CC</sub> = MAX, V <sub>IH</sub> = MIN, V <sub>O</sub> = 0.5V       |                                                                                               |                                                     |     |                  | -50   | μΑ   |

| Input current at maximum input voltage                    | V <sub>CC</sub> = MAX, V <sub>I</sub> = 5.5V                              |                                                                                               |                                                     |     |                  | 1.0   | mA   |

| I <sub>IH</sub> HIGH-level input current                  | V <sub>CC</sub> = MAX,                                                    | V <sub>i</sub> = 2.7                                                                          | V                                                   |     |                  | 50    | μΑ   |

| IIL LOW-level input current                               | V <sub>CC</sub> = MAX,                                                    | V <sub>I</sub> = 0.5                                                                          | V                                                   |     |                  | -0.25 | mA   |

| I <sub>OS</sub> Short-circuit output current <sup>3</sup> | V <sub>CC</sub> = MAX                                                     |                                                                                               |                                                     | -40 |                  | -100  | mA   |

|                                                           |                                                                           | Iccl                                                                                          | 8TS805                                              |     | 105              | 160   | mA   |

| I <sub>CC</sub> Supply current (total)                    | V <sub>CC</sub> = MAX                                                     | ICCL                                                                                          | All inputs grounded,<br>8TS806                      |     | 102              | 140   | mA   |

|                                                           | lccz                                                                      |                                                                                               | CP, $\overline{\text{OE}}$ = 4.5V<br>D inputs = GND |     | 131              | 180   | mA   |

### NOTES:

- 1. For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions for the applicable type.

- 2. All typical values are at V<sub>CC</sub> = 5V, T<sub>A</sub> = 25°C.

- 3. I<sub>OS</sub> is tested with V<sub>OUT</sub> = +0.5V and V<sub>CC</sub> = V<sub>CC</sub> MAX + 0.5V. Not more than one output should be shorted at a time and duration of the short-circuit should not exceed one second.

- 4.  $V_{OL}$  = +0.45V MAX for S8TS at  $T_A$  = +125°C only.

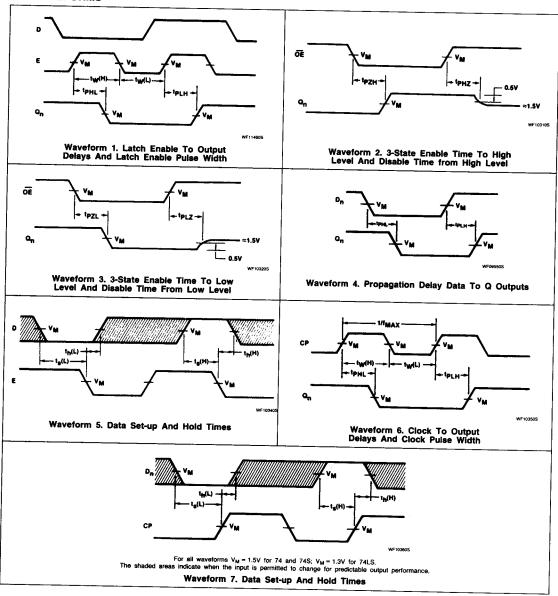

# AC ELECTRICAL CHARACTERISTICS $T_A = 25$ °C, $V_{CC} = 5.0$ V

| PARAMETER                            |                                             |                                  | . 8                   | UNIT     |     |

|--------------------------------------|---------------------------------------------|----------------------------------|-----------------------|----------|-----|

|                                      |                                             | TEST CONDITIONS                  | C <sub>L</sub> = 15pF |          |     |

|                                      |                                             |                                  | Min                   | Max      |     |

| f <sub>MAX</sub>                     | Maximum clock frequency                     | Waveform 6, 8TS806               | 75                    |          | MHz |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay<br>Latch enable to output | Waveform 1, 8TS805               |                       | 14<br>18 | ns  |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay<br>Data to output         | Waveform 4, 8TS805               |                       | 9<br>13  | ns  |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay<br>Clock to output        | Waveform 6, 8TS806               |                       | 15<br>17 | ns  |

| t <sub>PZH</sub>                     | Enable time to HIGH level                   | Waveform 2                       |                       | 15       | ns  |

| t <sub>PZL</sub>                     | Enable time to LOW level                    | Waveform 3 8TS805<br>8TS806      |                       | 18<br>18 | ns  |

| t <sub>PHZ</sub>                     | Disable time from HIGH level                | Waveform 2, C <sub>L</sub> = 5pF |                       | 9        | ns  |

| t <sub>PLZ</sub>                     | Disable time from LOW level                 | Waveform 3, C <sub>L</sub> = 5pF |                       | 12       | ns  |

NOTE:

Per industry convention, f<sub>MAX</sub> is the worst case value of the maximum device operating frequency with no constraints on t<sub>r</sub>, t<sub>f</sub>, pulse width or duty cycle.

8TS805, 806

### **AC WAVEFORMS**

# 8TS805, 806

### AC SET-UP REQUIREMENTS TA = 25°C, VCC = 5.0V

|                                          |                                   |                    | 8TS      |     |      |

|------------------------------------------|-----------------------------------|--------------------|----------|-----|------|

|                                          | PARAMETER                         | TEST CONDITIONS    | Min      | Max | UNIT |

| t <sub>W</sub> (H)<br>t <sub>W</sub> (L) | Latch enable pulse width          | Waveform 1, 8TS805 | 6<br>7.3 |     | ns   |

| ts                                       | Set-up time, data to latch enable | Waveform 5, 8TS805 | 5        |     | ns   |

| th                                       | Hold time, data to latch enable   | Waveform 5, 8TS805 | 10       |     | ns   |

| t <sub>W</sub> (H)<br>t <sub>W</sub> (L) | Clock pulse width                 | Waveform 6, 8TS806 | 6<br>7.3 |     | ns   |

| t <sub>s</sub>                           | Set-up time, data to clock        | Waveform 7, 8TS806 | 5        |     | ns   |

| th                                       | Hold time, data to clock          | Waveform 7, 8TS806 | 4        |     | ns   |

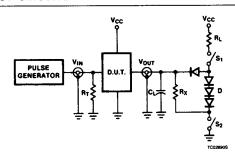

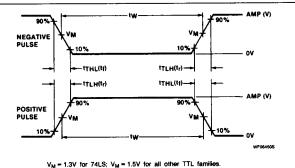

### TEST CIRCUITS AND WAVEFORMS

Test Circuit For 3-State Outputs

Input Pulse Definition

### SWITCH POSITION

| TEST             | SWITCH 1 | SWITCH 2 |

|------------------|----------|----------|

| t <sub>PZH</sub> | Open     | Closed   |

| tezu             | Closed   | Open     |

| t <sub>PHZ</sub> | Closed   | Closed   |

| terz             | Closed   | Closed   |

| = 4 4 4 1 V | INPUT PULSE REQUIREMENTS |           |             |                  |                  |  |  |

|-------------|--------------------------|-----------|-------------|------------------|------------------|--|--|

| FAMILY      | Amplitude                | Rep. Rate | Pulse Width | t <sub>TLH</sub> | t <sub>THL</sub> |  |  |

| 8T          | 3.0V                     | 1MHz      | 500ns       | 2.5ns            | 2.5ns            |  |  |

### DEFINITIONS

$R_L$  = Load resistor to  $V_{CC}$ ; see AC CHARACTERISTICS for value.

C<sub>L</sub> = Load capacitance includes jig and probe capacitance; see AC CHARACTERISTICS for value.

$R_T$  = Termination resistance should be equal to  $Z_{OUT}$  of Pulse Generators.

D = Diodes are 1N916, 1N3064, or equivalent.

$\mbox{R}_{\mbox{\scriptsize X}}=\mbox{1}k\Omega$  for 74, 74S,  $\mbox{R}_{\mbox{\scriptsize X}}=\mbox{5}k\Omega$  for 74LS.

$t_{\textrm{TLH.}} \ t_{\textrm{THL}}$  Values should be less than or equal to the table entries.