## SG124/224/324

6.7mW/9C

Continuous

\_550C to +1250C

-25°C to +85°C

65°C to +150°C

0°C ta +70°C

## **Quad Operational Amplifier**

The SG124 series integrated circuit contains four true-differential, independent operational amplifiers. Each amplifier has been designed to operate from either a single supply voltage or plus and minus voltages and features internal frequency compensation, high gain, and very low supply current requirements. An additional significant advantage of these amplifiers is that when using a single supply, the input and output can be operated down to ground potential. Thus, they can be powered by a standard +5V DC logic supply and still be compatible with all forms of logic inputs and putputs.

- · Four internally compensated op amps in a single package

- . Inputs and outputs can go to ground with a single supply

- . Input bias current is both low and constant with

- . Wide supply voltage compatibility with low current drain

- · Available in 14-pin plastic or cerdip package

## ABSOLUTE MAXIMUM RATINGS

Supply Voltage, V+ 32VDC or ±16VDC Differential Input Voltage 32VDC Input Voltage -0.3VDC to +32VDC Power Dissipation (Note 1) N Package (plastic) 600mW Derate above 25°C 6.0mW/°C J Package (cerdip) 1000mW

Output Short-Circuit to Gnd (Note 2) V+ ≤15V<sub>DC</sub> and T<sub>A</sub> = 25°C

Operating Temperature Range

Derate above 25°C

SG124 SG224 SG324

Storage Temperature Range

Lead Temperature (Soldering, 60 sec)

300°C COMMECTION DIACOAM

| CONNECTION DIAGRAM |          |    |                          |                  |  |  |  |  |

|--------------------|----------|----|--------------------------|------------------|--|--|--|--|

| DUTPUT 3           | 7        |    | $\overline{\mathcal{L}}$ | <u>о</u> штвит 2 |  |  |  |  |

| INPUT 3"           | 4        | 7  | 7                        | IMPUT 2"         |  |  |  |  |

| INPUT 31           |          |    | L                        | INPUT 2*         |  |  |  |  |

| G <u>NO</u>        |          | -N |                          | <u>v</u> .       |  |  |  |  |

| INPUT_41           |          |    |                          | INPUT 1          |  |  |  |  |

| 12<br>IMPUT 4-     |          |    |                          | INPUT 1          |  |  |  |  |

| DUTFUT 4           | $\nabla$ | 7  | V                        | OUTPUT           |  |  |  |  |

| 14                 | Ľ_       |    | Ь.                       | 1 OCTPUT         |  |  |  |  |

CHIP BONDING DIAGRAM

| Parameter                                   | Canditions                                                                                           | SG124 |      | SG224/SG324 |      | i    |                     |       |

|---------------------------------------------|------------------------------------------------------------------------------------------------------|-------|------|-------------|------|------|---------------------|-------|

|                                             |                                                                                                      | Min.  | Тур. | Max.        | Min. | Typ. | Max.                | Units |

| Input Offset Voltage                        | R <sub>S</sub> = 0Ω                                                                                  |       | 2    | 5           |      | 2    | 7                   | mVDC  |

| Input Bias Current (Note 3)                 |                                                                                                      |       | 45   | 150         |      | 45   | 250                 | nADC  |

| Input Offset Current                        | I <sub>IN</sub> (+) - I <sub>IN</sub> (-)                                                            |       | ±3   | ±30         |      | ±5   | ±50                 | nADC  |

| Input Common-Mode Voltage<br>Range (Note 4) |                                                                                                      | 0     |      | V+-1.5      | 0    |      | V <sup>+</sup> -1.5 | VDC   |

| Supply Current                              | R <sub>L</sub> ≃ ∞ On All Op Amps                                                                    |       | 0.8  | 1.2         |      | 0.B  | 1.2                 | mApo  |

| Large Signal Voltage Gain                   | R <sub>L</sub> ≥ 2kΩ                                                                                 | 50    | 100  |             | 25   | 100  |                     | V/mV  |

| Output Voltage Swing                        | R <sub>L</sub> = 2 kΩ                                                                                | 0     |      | V+-1.5      | 0    |      | V+-1.5              | VDC   |

| Common Mode Rejection<br>Ratio              | DC                                                                                                   | 70    | 85   |             | 65   | 85   |                     | dB    |

| Power Supply Rejection<br>Ratio             | DC                                                                                                   | 65    | 100  |             | 65   | 100  |                     | dB    |

| Amplifier-to-Amplifier<br>Coupling          | f = 1 kHz to 20 kHz<br>(Input Referred)                                                              |       | -120 |             |      | -120 |                     | dB    |

| Output Current Source                       | V <sub>IN</sub> <sup>+</sup> = +1V <sub>DC</sub> , V <sub>IN</sub> <sup>-</sup> = 0 V <sub>DC</sub>  | 20    | 40   |             | 20   | 40   |                     | mADO  |

| Output Current Sink                         | V <sub>IN</sub> <sup>-</sup> = +1 V <sub>DC</sub> , V <sub>IN</sub> <sup>+</sup> = 0 V <sub>DC</sub> | 10    | 20   |             | 10   | 20   |                     | mADO  |

Note 1: For operating at high temperatures, the SG324 must be derated based on a +125°C maximum junction temperature and a thermal resistance of 175°C/W which applies for the device soldered in a printed circuit board, operating in a still air ambient. The SG224 and SG124 can be derated based on a +150°C maximum junction temperature.

Note 2: Short circuits from the output to V<sup>+</sup> can cause excessive heating and eventual destruction. The maximum output current is approximately 40 mA independent of the magnitude of V<sup>+</sup>. At values of supply voltage in excess of +15V<sub>DC</sub>, con-

tinuous short-circuits can exceed the power dissipation ratings and cause eventual destruction.

Note 3: The direction of the input current is out of the IC due to the PNP input stage. This current is essentially constant, independent of the state of the output so no loading change exists on the input lines.

Note 4: The input common-mode voltage of either input signal voltage should not be allowed to go negative by more than 0.3V. The upper end of the common-mode voltage range is V\*1.5V, but either or both inputs can go to \*30Vpc without damage.

## APPLICATIONS INFORMATION

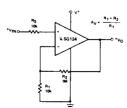

To reduce the power supply current drain, the amplifiers have a class A output stage for small signal levels which converts to class B in a large signal mode. This allows the amplifiers to both source and sink large output currents. Therefore both NPN and PNP external current boost transistors can be used to extend the power capability of the basic amplifiers. The output voltage needs to raise approximately 1 diode drop above ground to bias the on-chip vertical PNP transistor for output current sink-

For AC applications, where the load is capacitively coupled to the out-

put of the amplifier, a resistor should be used, from the output of the amplifier to ground to increase the class A bias current and prevent crossover distortion. Where the load is directly coupled, as in DC applications, there is no crossover distortion.

Capacitive loads which are applied directly to the output of the amplifier reduce the loop stability margin. Values of 50 pF can be accommodated using the worst-case non-inverting unity gain connection. Large closed loop gains or resistive isolation should be used if larger load capacitance must be driven by the amplifier.

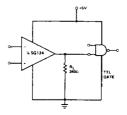

TTL INTERFACE

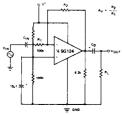

SINGLE SUPPLY NON-INVERTING DC AMPLIFIER 10V INPUT + DV DUTPUT