# 47F010 1024K Bit Flash EPROM

#### PRELIMINARY DATA SHEET

October 1989

#### Features

- 128K Byte Flash Erasable Non-Volatile Memory

- Input Latches for Writing and Erasing

- Low Power CMOS Process

- Flash EPROM Cell Technology

- Fast Byte Write: 225 µs max

- Ideal for Low-Cost Program Storage Applications

- · In-Circuit Alterable

- · 100 Program/Erase Cycles

- · Minimum 10 Year Data Retention

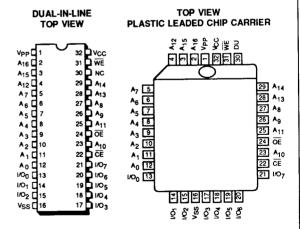

- Pinouts Upward Compatible Thru 2 Megabit Densities

- JEDEC Standard Byte Wide Pinout

- · 32 Pin PLCC

- · 32 Pin Dip

- Silicon Signature®

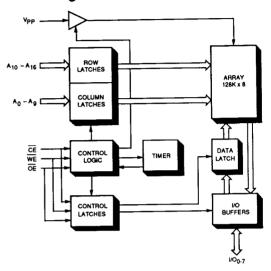

#### Block Diagram

#### Pin Names

| T (READ) |

|----------|

| _        |

| 3E       |

|          |

|          |

### Pin Configuration

Silicon Signature is a registered trademark of SEEQ Technology.

### Description

The 47F010 is a 1024K bit CMOS Flash EPROM organized as 128K x 8 bits. The 47F010 brings together the high density and cost effectiveness of UVEPROMs with the incircuit reprogrammability and package options of full featured EEPROMs. SEEQ's patented split gate Flash EPROM cell design reduces both the time and cost required to alter code in program and data storage applications.

The 47F010's fast electrical erase and 0.2 ms/byte programming is 20 times faster than reprogramming of UVEPROMs. Electrical erase and reprogramming make the 47F010 ideal for applications with high density requirements, but where ultraviolet erasure is either impractical or impossible.

On chip latches and timers permit simplified microprocessor interface, freeing the microprocessor to perform other tasks once write/erase cycles have been initiated. Endurance, the number of times each byte can be written and erased, is specified at 100 cycles. Electrical erase allows the 47F010 to be packaged in a wide range of windowless plastic, ceramic and surface mount packages.

#### Read

Reading is accomplished by presenting a valid address on Ao - As with chip enable (CE) and output enable (OE) at  $V_{_{\rm IL}}$  and write enable (WE) at  $V_{_{

m IH}}$ . The  $V_{_{

m PP}}$  pin can be at any TTL level or V, during read operations. See page 5 for additional information on A.C. parameters and read timing waveforms.

#### Erase and Write

Erasing and writing of the 47F010 can only be accomplished when V<sub>pp</sub> = V<sub>p</sub>. Latches on address, data and control inputs, permit erasing and writing using normal microprocessor bus timing. Address inputs are latched on the falling edge of write enable or chip enable, whichever is later. While data inputs are latched on the rising edge of write enable or chip enable, whichever is earlier. The write enable input is noise protected; a pulse of less than 20 ns will not initiate a write or erase. In addition, chip enable, output enable and write enable pins must be in the proper state to initiate a write or erase. Timing diagrams depict write enable controlled writes; the timing also applies to chip enable controlled writes.

#### **Byte Write**

A byte write is used to change any 1 in a byte to a 0. Individual bytes, multiple bytes or the entire memory can be written at one time. If a bit in a byte needs to be changed from a 0 to a 1, the 47F010 must first be erased via chip erase and then reprogrammed with the desired data. Any byte write operation requires that the V<sub>pp</sub> pin be at high voltage (Va).

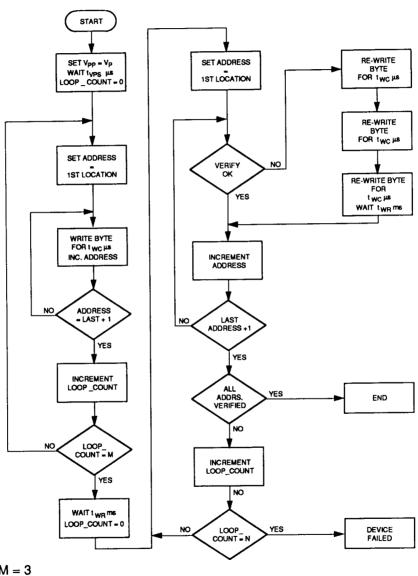

The 47F010 uses a software controlled looping algorithm (figure 1) to perform writes and verify successful byte programming. During a byte write operation, all non "FF"1 bytes are incrementally written using a 75 µs minimum two. Each byte write is automatically latched and timed on-chip, so that the microprocessor can perform other tasks once the write cycle has been initiated. Write cycle time duration can be controlled by the microprocessor, or the onchip timer will automatically terminate t<sub>wc</sub> after 150 μs. One write loop has been completed when all non "FF" data for all desired bytes have been written. After 3 programming loops, a read-verification cycle is performed. For any bytes which do not verify, a fill-in programming loop is performed.

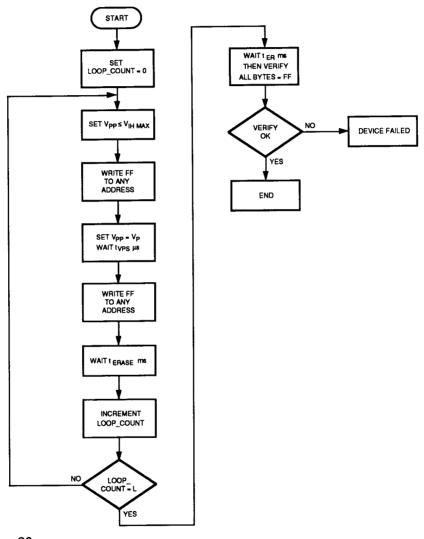

### Chip Erase

Chip Erase will change all bits in the memory to a logical 1. The 47F010 uses a two-step, software controlled looping algorithm to perform the chip erase operation. Each loop requires that a chip erase select be performed prior to the start of each chip erase cycle.

The chip erase select is activated by initiating a write cycle with the Vpp pin at Vin or lower. During the chip erase select, address and data lines can be at any TTL level. Following a chip erase select, the 47F010 will start chip erase if all data inputs are "FF",  $V_{pp} = V_p$  and a write cycle initiated. After 20 loops, a device erase verify is performed to insure all bytes = "FF". After erase, the V pp pin can be brought to any TTL level or left at high voltage.

Refer to page 8 for chip erase timing diagram and figure 2 for the erase algorithm.

### Power Up/Down Protection

This device contains a sense circuit which disables internal erase and write operations when  $V_{cc}$  is below 3.5 volts. In addition, erases and writes are prevented when any control input (CE, OE, WE) is in the wrong state for writing /erasing (see mode table).

# High Voltage Input Protection

The  $V_{pp}$  pin is at a high voltage for writing and erasing. There is an absolute maximum specification for the Vpp

1 Only non "FF" bytes can be written.

pin which must not be exceeded, even briefly, or permanent device damage may result. To minimize switching transients on this pin, we recommend using a minimum 0.1 uf decoupling capacitor with good high frequency response connected from V pp to ground at each device. In addition, sufficient bulk capacitance should be provided to minimize  $V_{pp}$  voltage sag when a device goes from standby to a write or erase cycle.

### Silicon Signature

A row of fixed ROM is present in the 47F010 which contains the device's Silicon Signature. Silicon Signature contains data which identifies SEEQ as the manufacturer and gives the product code. This allows device programmers to match the programming specification against the product which is to be programmed.

Silicon Signature is read by raising address A to 12 ± 0.5 volts and bringing all other address inputs, plus chip enable, and output enable to  $V_{\mu}$  with  $V_{cc}$  at 5 V. The two Silicon Signature bytes are selected by address input A,.

### Silicon Signature Bytes

|                     | A <sub>o</sub>  | Data (Hex) |

|---------------------|-----------------|------------|

| SEEQ Code           | V <sub>IL</sub> | 94         |

| Product Code 47F010 | V <sub>iH</sub> | 10         |

#### Mode Selection Table

| Mode              | CE              | ŌĒ              | WE              | V <sub>pp</sub> | A <sub>0-16</sub> | D <sub>0 .7</sub> |

|-------------------|-----------------|-----------------|-----------------|-----------------|-------------------|-------------------|

| Read              | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>iH</sub> | X               | Address           | D <sub>out</sub>  |

| Standby           | V <sub>IH</sub> | X               | Х               | Х               | Х                 | High Z            |

| Byte Write        | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IL</sub> | V <sub>P</sub>  | Address           | D <sub>IN</sub>   |

| Chip Erase Select | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IL</sub> | ΠL              | Х                 | Х                 |

| Chip Erase        | V,,             | V <sub>IH</sub> | V <sub>IL</sub> | V <sub>P</sub>  | Х                 | 'FF'              |

# Absolute Maximum Stress Range\*

| Storage                                                         | 65°C to +125°C |

|-----------------------------------------------------------------|----------------|

| Under Bias                                                      | 10°C to +85°C  |

| All Inputs except $V_{pp}$ and outputs with respect to $V_{ss}$ | +7 V to -0.5 V |

| V <sub>pp</sub> and A <sub>g</sub> with respect to V            | 'ss14 V        |

# E.S.D. Characteristics\*

|      | Parameter        |         | Test Condition |

|------|------------------|---------|----------------|

| V,AP | E.S.D. Tolerance | >2000 V | MIL-STD 883    |

| ZAP  |                  |         | Method 3015    |

<sup>\*</sup> Characterization data -- not tested.

\*COMMENT: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **Operating Conditions**

|                                 | 47F010      |

|---------------------------------|-------------|

| V <sub>cc</sub> Supply Voltage  | 5V ± 10%    |

| Temperature Range (Read)        | 0°C to 70°C |

| Temperature Range (Write/Erase) | 25°C ± 5°C  |

# Capacitance \* TA = 25°C, f =1 MHz

| Symbol          | Parameter          | Value | Test Condition         |

|-----------------|--------------------|-------|------------------------|

| C <sub>IN</sub> | Input Capacitance  | 6 pF  | V <sub>IN</sub> = 0 V  |

| Cout            | Output capacitance | 12 pF | V <sub>I/O</sub> = 0 V |

<sup>\*</sup> This parameter is measured only for initial qualifications and after process or design changes which may affect capacitance.

# $\textit{DC} \;\; \textit{Operating Characteristics} \;\; \text{Over specified V}_{\text{cc}} \; \text{and temperature range}$

|                  |                                                                     |                       | Limits                 |                      |                                                                                                                       |

|------------------|---------------------------------------------------------------------|-----------------------|------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------|

| Symbol           | Parameter                                                           | Min.                  | Max.                   | Unit                 | Test Condition                                                                                                        |

| l <sub>u</sub>   | Input Leakage                                                       |                       | 1                      | μА                   | V <sub>IN</sub> = 0.1V to V <sub>CC</sub>                                                                             |

| I <sub>LO</sub>  | Output Leakage                                                      |                       | 10                     | μА                   | V <sub>IN</sub> = 0.1 V to V <sub>CC</sub>                                                                            |

| V <sub>p</sub>   | Program/Erase Voltage                                               | 12.50                 | 13.00                  | V                    |                                                                                                                       |

| $V_{pR}$         | V <sub>pp</sub> Voltage During Read                                 | 0                     | V <sub>P</sub>         | ٧                    |                                                                                                                       |

| РР               | V <sub>P</sub> Current Standby Mode Read Mode Byte Write Chip Erase |                       | 200<br>200<br>30<br>60 | μΑ<br>μΑ<br>mA<br>mA | $\overline{CE} = V_{HI}, V_{pp} = V_{pR}$ $\overline{CE} = V_{IL}, V_{pp} = V_{pR}$ $V_{pp} = V_{p}$ $V_{pp} = V_{p}$ |

| CC1              | Standby V <sub>cc</sub> Current                                     |                       | 400                    | μА                   | CE = V <sub>cc</sub> -0.3V                                                                                            |

| CC2              | Standby V <sub>cc</sub> Current                                     |                       | 5                      | mA                   | CE = V <sub>IH</sub> min.                                                                                             |

| ССЗ              | Active V <sub>cc</sub> Current                                      |                       | 40                     | mA                   | CE = V <sub>IL</sub>                                                                                                  |

| V <sub>IL</sub>  | Input Low Voltage                                                   | -0.3                  | 0.8                    | ٧                    |                                                                                                                       |

| / <sub>IH</sub>  | Input High Voltage                                                  | 2.0                   | 7.0                    | V                    |                                                                                                                       |

| / <sub>oL</sub>  | Output Low Voltage                                                  |                       | 0.45                   | ٧                    | l <sub>ot</sub> = 2.1 ma                                                                                              |

| / <sub>OH1</sub> | Output Level (TTL)                                                  | 2.4                   |                        | ٧                    | I <sub>OH</sub> = -400 μA                                                                                             |

| V <sub>OH2</sub> | Output Level (CMOS)                                                 | V <sub>cc</sub> - 1.0 |                        | V                    | I <sub>OH</sub> = -100 μA                                                                                             |

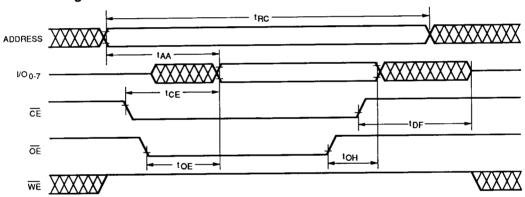

#### READ

#### AC Characteristics

(Over specified V<sub>cc</sub> and Temperature Range)

|                 |                     | 47F010<br>-200 |      | 47F010<br>-250 |      | 47F010<br>300 |      |      |

|-----------------|---------------------|----------------|------|----------------|------|---------------|------|------|

| Symbol Parar    | Parameter           | Min.           | Max. | Min.           | Max. | Min.          | Max. | Unit |

| t <sub>RC</sub> | Read Cycle Time     | 200            |      | 250            |      | 300           |      | ns   |

| AA              | Address to Data     |                | 200  |                | 250  |               | 300  | ns   |

| CE              | CE to Data          |                | 200  |                | 250  |               | 300  | ns   |

| OE .            | OE to Data          |                | 75   |                | 100  |               | 150  | ns   |

| DF              | OE/CE to Data Float |                | 50   |                | 60   |               | 100  | ns   |

| t <sub>on</sub> | Output Hold Time    | 0              |      | 0              |      | 0             |      | ns   |

### Read Timing

# A.C. Test Conditions

Output Load: 1 TTL gate and C(load) = 100 pF Input Rise and Fall Times: < 20 ns Input Pulse Levels: 0.45V to 2.4V Timing Measurement Reference Level: Inputs 1V and 2V Outputs 0.8V and 2V

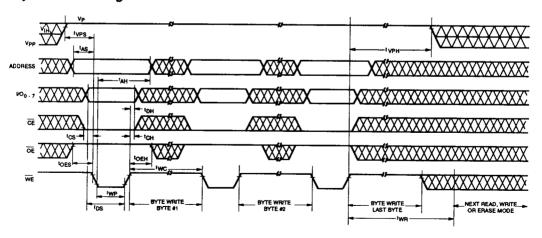

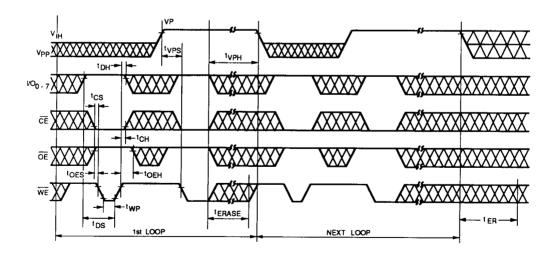

### Byte Write

#### AC Characteristics

(Over specified V<sub>cc</sub> and temperature range)

|                  |                            | 471  | -010 |      |

|------------------|----------------------------|------|------|------|

| Symbol           | Parameter                  | Min. | Max. | Unit |

| t <sub>vps</sub> | V <sub>pp</sub> Setup Time | 2    |      | μs   |

| t <sub>veh</sub> | V <sub>PP</sub> Hold Time  | 150  |      | μs   |

| t <sub>cs</sub>  | CE Setup Time              | 0    |      | ns   |

| t <sub>ch</sub>  | CE Hold Time               | 0    |      | ns   |

| toes             | OE Setup Time              | 10   |      | ns   |

| t <sub>oeh</sub> | OE Hold Time               | 10   |      | ns   |

| t <sub>as</sub>  | Address Setup Time         | 20   |      | ns   |

| t <sub>AH</sub>  | Address Hold Time          | 100  |      | ns   |

| t <sub>DŞ</sub>  | Data Setup Time            | 50   |      | ns   |

| t <sub>oh</sub>  | Data Hold Time             | 0    | 1    | ns   |

| t <sub>we</sub>  | WE Pulse Width             | 100  |      | ns   |

| t <sub>wc</sub>  | Write Cycle Time           | 75   |      | μs   |

| t <sub>wa</sub>  | Write Recovery Time        |      | 1.5  | ms   |

NOTE: In A.C. characteristics, all inputs to the device, e.g., setup time, hold time and cycle time, are tabulated as a minimum time; the user must provide a valid state on that input or wait for the state minimum time to assure proper operation. All outputs from the device, e.g. access time, erase time, recovery time, are tabulated as a maximum time, the device will perform the operation within the stated time.

# Byte Write Timing

Figure 1 47F010 Write Algorithm

M = 3

N = 5

### Chip Erase

### AC Characteristics

(Over specified V<sub>cc</sub> and temperature range)

|                    |                            | 47F  | 010  |      |

|--------------------|----------------------------|------|------|------|

| Symbol             | Parameter                  | Min. | Max. | Unit |

| t <sub>vps</sub>   | V <sub>pp</sub> Setup Time | 2    |      | μs   |

| t <sub>vph</sub>   | V <sub>PP</sub> Hold Time  | 500  |      | ms   |

| t <sub>cs</sub>    | CE Setup Time              | 0    |      | ns   |

| t <sub>oes</sub>   | OE Setup Time              | 0    |      | ns   |

| t <sub>DS</sub>    | Data Setup Time            | 50   |      | ns   |

| t <sub>DH</sub>    | Data Hold Time             | 0    |      | ns   |

| t <sub>we</sub>    | WE Pulse Width             | 100  |      | ns   |

| t <sub>ch</sub>    | CE Hold Time               | 0    |      | ns   |

| t <sub>oeh</sub>   | OE Hold Time               | 0    |      | ns   |

| t <sub>erase</sub> | Chip Erase Time            | 500  |      | ms   |

| t <sub>ER</sub>    | Erase Recovery Time        |      | 250  | ms   |

# Chip Erase Timing

Figure 2 47F010 Chip Erase Algorithm

## 47F010 PRELIMINARY DATA SHEET

# Ordering Information

| <u>D</u>                                                        | <u> </u>                    | 47F010                  | <u>- 200</u>                                 |

|-----------------------------------------------------------------|-----------------------------|-------------------------|----------------------------------------------|

| Package<br>Type                                                 | Temperature<br>Range (READ) | Device                  | Access<br>Time                               |

| D = Ceramic Dip P = Plastic Dip N = Plastic Leaded Chip Carrier | Q = 0 to 70° C              | 128K x 8 Flash<br>EPROM | 200 = 200 ns<br>250 = 250 ns<br>300 = 300 ns |