## **Programmable Timing Control Hub™ for P4™**

#### **Recommended Application:**

CK-408 clock with driven mode only for Brookdale and Brookdale-G chipset with P4 processor.

#### **Output Features:**

- 3 Pairs of differential CPU clocks (differential current mode)

- 3 3V66 @ 3.3V

- 10 PCI @ 3.3V

- 1 48MHz @ 3.3V fixed

- 2 REF @ 3.3V, 14.318MHz

- 1 48\_66MHz selectable @ 3.3V fixed

- 1 24\_48MHz selectable @ 3.3V

#### Features/Benefits:

- Programmable output frequency.

- Programmable output divider ratios.

- Programmable output rise/fall time.

- Programmable output skew.

- Programmable spread percentage for EMI control.

- Watchdog timer technology to reset system if system malfunctions.

- Programmable watch dog safe frequency.

- Support I<sup>2</sup>C Index read/write and block read/write operations.

- Uses external 14.318MHz crystal.

#### **Key Specifications:**

950218 Rev A 01/23/02

- CPU Output Jitter <150ps</li>

- 3V66 Output Jitter <250ps</li>

- CPU Output Skew <100ps</li>

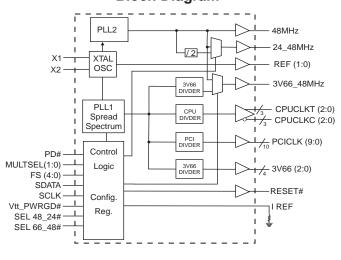

#### **Block Diagram**

- 40-Fill 300-Illii 33

- 1 This output has 2X drive

- \* Internal Pull-up resistor of 120K to VDD

- \*\* Internal Pull-down resistor of 120K to GND

#### Frequency Table

| Bit2 | Bit7 | Bit6 | Bit5 | Bit4 | CPUCLK | 3V66  | PCICLK |

|------|------|------|------|------|--------|-------|--------|

| FS4  | FS3  | FS2  | FS1  | FS0  | MHz    | MHz   | MHz    |

| 0    | 0    | 0    | 0    | 0    | 102.00 | 68.00 | 34.00  |

| 0    | 0    | 0    | 0    | 1    | 105.00 | 70.00 | 35.00  |

| 0    | 0    | 0    | 1    | 0    | 108.00 | 72.00 | 36.00  |

| 0    | 0    | 0    | 1    | 1    | 111.00 | 74.00 | 37.00  |

| 0    | 0    | 1    | 0    | 0    | 114.00 | 76.00 | 38.00  |

| 0    | 0    | 1    | 0    | 1    | 117.00 | 78.00 | 39.00  |

| 0    | 0    | 1    | 1    | 0    | 120.00 | 80.00 | 40.00  |

| 0    | 0    | 1    | 1    | 1    | 123.00 | 82.00 | 41.00  |

| 0    | 1    | 0    | 0    | 0    | 126.00 | 72.00 | 36.00  |

| 0    | 1    | 0    | 0    | 1    | 130.00 | 74.30 | 37.10  |

| 0    | 1    | 0    | 1    | 0    | 136.00 | 68.00 | 34.00  |

| 0    | 1    | 0    | 1    | 1    | 140.00 | 70.00 | 35.00  |

| 0    | 1    | 1    | 0    | 0    | 144.00 | 72.00 | 36.00  |

| 0    | 1    | 1    | 0    | 1    | 148.00 | 74.00 | 37.00  |

| 0    | 1    | 1    | 1    | 0    | 152.00 | 76.00 | 38.00  |

| 0    | 1    | 1    | 1    | 1    | 156.00 | 78.00 | 39.00  |

| 1    | 0    | 0    | 0    | 0    | 160.00 | 80.00 | 40.00  |

| 1    | 0    | 0    | 0    | 1    | 164.00 | 82.00 | 41.00  |

| 1    | 0    | 0    | 1    | 0    | 166.60 | 66.60 | 33.30  |

| 1    | 0    | 0    | 1    | 1    | 170.00 | 68.00 | 34.00  |

| 1    | 0    | 1    | 0    | 0    | 175.00 | 70.00 | 35.00  |

| 1    | 0    | 1    | 0    | 1    | 180.00 | 72.00 | 36.00  |

| 1    | 0    | 1    | 1    | 0    | 185.00 | 74.00 | 37.00  |

| 1    | 0    | 1    | 1    | 1    | 190.00 | 76.00 | 38.00  |

| 1    | 1    | 0    | 0    | 0    | 66.80  | 66.80 | 33.40  |

| 1    | 1    | 0    | 0    | 1    | 100.20 | 66.80 | 33.40  |

| 1    | 1    | 0    | 1    | 0    | 133.60 | 66.80 | 33.40  |

| 1    | 1    | 0    | 1    | 1    | 200.40 | 66.80 | 33.40  |

| 1    | 1    | 1    | 0    | 0    | 66.60  | 66.60 | 33.30  |

| 1    | 1    | 1    | 0    | 1    | 100.00 | 66.60 | 33.30  |

| 1    | 1    | 1    | 1    | 0    | 200.00 | 66.60 | 33.30  |

| 1    | 1    | 1    | 1    | 1    | 133.33 | 66.60 | 33.30  |

**General Description**

The ICS950218 is a single chip clock solution for desktop designs using the Intel Brookdale chipset with PC133 or DDR memory. It provides all necessary clock signals for such a system.

The ICS950218 is part of a whole new line of ICS clock generators and buffers called TCH™ (Timing Control Hub). ICS is the first to introduce a whole product line which offers full programmability and flexibility on a single clock device. This part incorporates ICS's newest clock technology which offers more robust features and functionality. Employing the use of a serially programmable I²C interface, this device can adjust the output clocks by configuring the frequency setting, the output divider ratios, selecting the ideal spread percentage, the output skew, the output strength, and enabling/disabling each individual output clock. TCH also incorporates ICS's Watchdog Timer technology and a reset feature to provide a safe setting under unstable system conditions. M/N control can configure output frequency with resolution up to 0.1MHz increment. With all these programmable features ICS's, TCH makes mother board testing, tuning and improvement very simple.

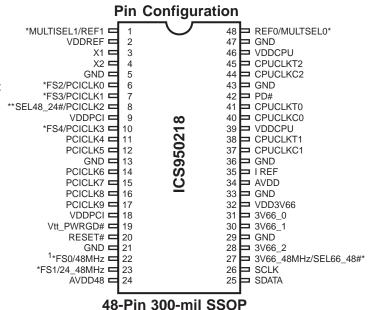

#### **Pin Description**

| PIN NUMBER PIN NAME          |                 | TYPE | DESCRIPTION                                                                                                                                                                 |  |

|------------------------------|-----------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ,                            | MULTSEL1        | IN   | 3.3V LVTTL input for selecting the current multiplier for CPU outputs.                                                                                                      |  |

| 1                            | REF1            | OUT  | 3.3V, 14.318MHz reference clock output.                                                                                                                                     |  |

| 2, 9, 18, 24,<br>32, 39, 46  | VDD             | PWR  | 3.3V power supply                                                                                                                                                           |  |

| 3                            | X1              | IN   | Crystal input, has internal load cap (33pF) and feedback resistor from X2                                                                                                   |  |

| 4                            | X2              | OUT  | Crystal output, nominally 14.318MHz. Has internal load cap (33pF)                                                                                                           |  |

| 5, 13, 21, 29,<br>36, 43, 47 | GND             | PWR  | Ground pins for 3.3V supply                                                                                                                                                 |  |

| 6                            | FS2             | IN   | Logic input frequency select bit. Input latched at power on.                                                                                                                |  |

| 0                            | PCICLK0         | OUT  | 3.3V PCI clock output                                                                                                                                                       |  |

| _                            | FS3             | IN   | Logic input frequency select bit. Input latched at power on.                                                                                                                |  |

| 7                            | PCICLK1         | OUT  | 3.3V PCI clock output                                                                                                                                                       |  |

| 8                            | SEL 48_24#      | IN   | This selects the frequency for the 24.48 MHz output. High = 48MHz, Low=24MHz                                                                                                |  |

|                              | PCICLK2         | OUT  | 3.3V PCI clock output                                                                                                                                                       |  |

| 10                           | FS4             | IN   | Logic input frequency select bit. Input latched at power on.                                                                                                                |  |

| 10                           | PCICLK3         | OUT  | 3.3V PCI clock output                                                                                                                                                       |  |

| 17, 16, 15, 14, 12, 11       | PCICLK (9:4, 2) | OUT  | 3.3V PCI clock outputs                                                                                                                                                      |  |

| 19                           | 19 Vtt_PWRGD#   |      | This 5V tolerant LVTTL input is a level sensitive strobe used to determine when FS (4:0) and MULTISEL inputs are valid and are ready to be sampled (active low)             |  |

| 20                           | RESET#          | OUT  | Real time system reset signal for frequency value or watchdog timmer timeout.  This signal is active low.                                                                   |  |

| 28, 30, 31                   | 3V66 (2:0)      | OUT  | 3.3V Fixed 66MHz clock outputs for HUB                                                                                                                                      |  |

| 22                           | FS0             | IN   | Logic input frequency select bit. Input latched at power on.                                                                                                                |  |

|                              | 48MHz           | OUT  | 3.3V Fixed 48MHz clock output.                                                                                                                                              |  |

| 23                           | FS1             | IN   | Logic input frequency select bit. Input latched at power on.                                                                                                                |  |

| 20                           | 24_48MHz        | OUT  | Selectable 24 or 48MHz output.                                                                                                                                              |  |

| 25                           | SDATA           | 1/0  | Data pin for I <sup>2</sup> C circuitry 5V tolerant                                                                                                                         |  |

| 26                           | SCLK            | IN   | Clock pin for I <sup>2</sup> C circuitry 5V tolerant                                                                                                                        |  |

|                              | SEL66_48#       | IN   | This selects the frequency for the 3V6_48 MHz output High = 66MHz, Low=48MHz                                                                                                |  |

| 27                           | 3V66_48MHz      | OUT  | Selectable 66 or 48MHz output                                                                                                                                               |  |

| 33                           | GND             | PWR  | Ground for CORE PLL                                                                                                                                                         |  |

| 34                           | AVDD            | PWR  | Power for CORE PLL 3.3V nominal                                                                                                                                             |  |

| 35 I REF OUT requires        |                 | OUT  | This pin establishes the reference current for the CPUCLK pairs. This pin requires a fixed precision resistor tied to ground in order to establish the appropriate current. |  |

| 42                           | PD#             | IN   | stopped. The latency of the power down will not be greater than 3ms.                                                                                                        |  |

| 44, 40, 37                   | CPUCLKC (2:0)   | OUT  | "Complementory" clocks of differential pair CPU outputs. These are current outputs and external resistors are required for voltage bias.                                    |  |

| 45, 41, 38                   | CPUCLKT (2:0)   | OUT  | "True" clocks of differential pair CPU outputs. These are current outputs and external resistors are required for voltage bias.                                             |  |

| 48                           | MULTSEL0        | IN   | 3.3V LVTTL input for selecting the current multiplier for CPU outputs.                                                                                                      |  |

|                              | REF0            | OUT  | 3.3V, 14.318MHz reference clock output.                                                                                                                                     |  |

#### **Maximum Allowed Current**

| Condition                       | Max 3.3V supply consumption Max discrete cap loads, Vdd = 3.465V All static inputs = Vdd or GND |

|---------------------------------|-------------------------------------------------------------------------------------------------|

| Powerdown Mode<br>(PWRDWN# = 0) | 40mA                                                                                            |

| Full Active                     | 360mA                                                                                           |

# **CPUCLK Swing Select Functions**

| MULTSEL0 | MULTSEL1 | Board Target<br>Trace/Term Z | Reference R,<br>Iref=<br>Vdd/(3*Rr) | Output<br>Current | Voh @ Z,<br>Iref=2.32mA |

|----------|----------|------------------------------|-------------------------------------|-------------------|-------------------------|

| 0        | 0        | 60 ohms                      | Rr = 475 1%<br>Iref = 2.32mA        | Ioh = 5*Iref      | 0.71V @ 60              |

| 0        | 0        | 50 ohms                      | Rr = 475 1%<br>Iref = 2.32mA        | Ioh = 5*Iref      | 0.59V @ 50              |

| 0        | 1        | 60 ohms                      | Rr = 475 1%<br>Iref = 2.32mA        | Ioh = 6*Iref      | 0.85V /2 60             |

| 0        | 1        | 50 ohms                      | Rr = 475 1%<br>Iref = 2.32mA        | Ioh = 6*Iref      | 0.71V @ 50              |

| 1        | 0        | 60 ohms                      | Rr = 475 1%<br>Iref = 2.32mA        | Ioh = 4*Iref      | 0.56V @ 60              |

| 1        | 0        | 50 ohms                      | Rr = 475 1%<br>Iref = 2.32mA        | Ioh = 4*Iref      | 0.47V @ 50              |

| 1        | 1        | 60 ohms                      | $Rr = 475 \ 1\%$<br>Iref = 2.32mA   | Ioh = 7*Iref      | 0.99V @ 60              |

| 1        | 1        | 50 ohms                      | $Rr = 475 \ 1\%$<br>Iref = 2.32mA   | Ioh = 7*Iref      | 0.82V @ 50              |

| 0        | 0        | 30 (DC equiv)                | Rr = 221 1%<br>Iref = 5mA           | Ioh = 5*Iref      | 0.75V @ 30              |

| 0        | 0        | 25 (DC equiv)                | Rr = 221 1%<br>Iref = 5mA           | Ioh = 5*Iref      | 0.62V @ 20              |

| 0        | 1        | 30 (DC equiv)                | Rr = 221 1% $Iref = 5mA$            | Ioh = 6*Iref      | 0.90V @ 30              |

| 0        | 1        | 25 (DC equiv)                | Rr = 221 1% $Iref = 5mA$            | Ioh = 6*Iref      | 0.75V @ 20              |

| 1        | 0        | 30 (DC equiv)                | Rr = 221 1%<br>Iref = 5mA           | Ioh = 4*Iref      | 0.60 @ 20               |

| 1        | 0        | 25 (DC equiv)                | Rr = 221 1% $Iref = 5mA$            | Ioh = 4*Iref      | 0.5V @ 20               |

| 1        | 1        | 30 (DC equiv)                | Rr = 221 1% $Iref = 5mA$            | Ioh = 7*Iref      | 1.05V @ 30              |

| 1        | 1        | 25 (DC equiv)                | Rr = 221 1%<br>Iref = 5mA           | Ioh = 7*Iref      | 0.84V @ 20              |

### General I<sup>2</sup>C serial interface information

#### **How to Write:**

- · Controller (host) sends a start bit.

- Controller (host) sends the write address D2 (H)

- ICS clock will acknowledge

- Controller (host) sends the begining byte location = N

- ICS clock will acknowledge

- Controller (host) sends the data byte count = X

- ICS clock will acknowledge

- Controller (host) starts sending Byte N through Byte N + X -1 (see Note 2)

- ICS clock will acknowledge each byte one at a time

- Controller (host) sends a Stop bit

| In    | Index Block Write Operation |                      |     |  |  |  |  |

|-------|-----------------------------|----------------------|-----|--|--|--|--|

| Col   | ntroller (Host)             | ICS (Slave/Receiver) |     |  |  |  |  |

| Т     | starT bit                   |                      |     |  |  |  |  |

| Slav  | e Address D2 <sub>(H)</sub> |                      |     |  |  |  |  |

| WR    | WRite                       |                      |     |  |  |  |  |

|       |                             |                      | ACK |  |  |  |  |

| Beg   | inning Byte = N             |                      |     |  |  |  |  |

|       |                             |                      | ACK |  |  |  |  |

| Data  | Byte Count = X              |                      |     |  |  |  |  |

|       |                             |                      | ACK |  |  |  |  |

| Begir | nning Byte N                |                      |     |  |  |  |  |

|       |                             |                      | ACK |  |  |  |  |

|       | 0                           | ţe                   |     |  |  |  |  |

|       | 0                           | X Byte               | 0   |  |  |  |  |

|       | 0                           | 0                    |     |  |  |  |  |

|       |                             | 0                    |     |  |  |  |  |

| Byte  | e N + X - 1                 |                      |     |  |  |  |  |

|       |                             | ACK                  |     |  |  |  |  |

| Р     | stoP bit                    | P stoP bit           |     |  |  |  |  |

Indox Diods Write Onorotic

#### How to Read:

- Controller (host) will send start bit.

- Controller (host) sends the write address D2<sub>(H)</sub>

- ICS clock will acknowledge

- Controller (host) sends the begining byte location = N

- ICS clock will acknowledge

- Controller (host) will send a separate start bit.

- Controller (host) sends the read address D3 (H)

- ICS clock will acknowledge

- ICS clock will send the data byte count = X

- ICS clock sends Byte N + X -1

- ICS clock sends Byte 0 through byte X (if X<sub>(H)</sub> was written to byte 8).

- Controller (host) will need to acknowledge each byte

- · Controllor (host) will send a not acknowledge bit

- · Controller (host) will send a stop bit

| In    | Index Block Read Operation  |                     |                    |  |  |  |

|-------|-----------------------------|---------------------|--------------------|--|--|--|

| Cor   | troller (Host)              | IC                  | S (Slave/Receiver) |  |  |  |

| Т     | starT bit                   |                     |                    |  |  |  |

| Slave | e Address D2 <sub>(H)</sub> |                     |                    |  |  |  |

| WR    | WRite                       |                     |                    |  |  |  |

|       |                             |                     | ACK                |  |  |  |

| Begi  | nning Byte = N              |                     |                    |  |  |  |

|       |                             |                     | ACK                |  |  |  |

| RT    | Repeat starT                |                     |                    |  |  |  |

| Slave | e Address D3 <sub>(H)</sub> |                     |                    |  |  |  |

| RD    | ReaD                        |                     |                    |  |  |  |

|       |                             | ACK                 |                    |  |  |  |

|       |                             |                     |                    |  |  |  |

|       |                             | Data Byte Count = X |                    |  |  |  |

|       | ACK                         |                     |                    |  |  |  |

|       |                             |                     | Beginning Byte N   |  |  |  |

|       | ACK                         |                     |                    |  |  |  |

|       |                             | ţe                  | 0                  |  |  |  |

|       | 0                           | X Byte              | 0                  |  |  |  |

|       | 0                           | ×                   | 0                  |  |  |  |

|       | 0                           |                     |                    |  |  |  |

|       |                             |                     | Byte N + X - 1     |  |  |  |

| N     | Not acknowledge             |                     |                    |  |  |  |

| Р     | stoP bit                    |                     |                    |  |  |  |

<sup>\*</sup>See notes on the following page.

Byte 0: Functionality and frequency select register (Default=0)

| Bit     |                                                                                                     |                                       |             |             |             |                                     | Description                       |               |                        | PWD    |

|---------|-----------------------------------------------------------------------------------------------------|---------------------------------------|-------------|-------------|-------------|-------------------------------------|-----------------------------------|---------------|------------------------|--------|

|         | Bit2<br>FS4                                                                                         | Bit7<br>FS3                           | Bit6<br>FS2 | Bit5<br>FS1 | Bit4<br>FS0 | CPUCLK<br>MHz                       | 3V66<br>MHz                       | PCICLK<br>MHz | Spread %               |        |

|         | 0                                                                                                   | 0                                     | 0           | 0           | 0           | 102.00                              | 68.00                             | 34.00         | +/-0.25% Center spread |        |

|         | 0                                                                                                   | 0                                     | 0           | 0           | 1           | 105.00                              | 70.00                             | 35.00         | +/-0.25% Center spread |        |

|         | 0                                                                                                   | 0                                     | 0           | 1           | 0           | 108.00                              | 72.00                             | 36.00         | +/-0.25% Center spread |        |

|         | 0                                                                                                   | 0                                     | 0           | 1           | 1           | 111.00                              | 74.00                             | 37.00         | +/-0.25% Center spread |        |

|         | 0                                                                                                   | 0                                     | 1           | 0           | 0           | 114.00                              | 76.00                             | 38.00         | +/-0.25% Center spread |        |

|         | 0                                                                                                   | 0                                     | 1           | 0           | 1           | 117.00                              | 78.00                             | 39.00         | +/-0.25% Center spread |        |

|         | 0                                                                                                   | 0                                     | 1           | 1           | 0           | 120.00                              | 80.00                             | 40.00         | +/-0.25% Center spread |        |

|         | 0                                                                                                   | 0                                     | 1           | 1           | 1           | 123.00                              | 82.00                             | 41.00         | +/-0.25% Center spread |        |

|         | 0                                                                                                   | 1                                     | 0           | 0           | 0           | 126.00                              | 72.00                             | 36.00         | +/-0.25% Center spread |        |

|         | 0                                                                                                   | 1                                     | 0           | 0           | 1           | 130.00                              | 74.30                             | 37.10         | +/-0.25% Center spread |        |

|         | 0                                                                                                   | 1                                     | 0           | 1           | 0           | 136.00                              | 68.00                             | 34.00         | +/-0.25% Center spread |        |

|         | 0                                                                                                   | 1                                     | 0           | 1           | 1           | 140.00                              | 70.00                             | 35.00         | +/-0.25% Center spread |        |

|         | 0                                                                                                   | 1                                     | 1           | 0           | 0           | 144.00                              | 72.00                             | 36.00         | +/-0.25% Center spread |        |

|         | 0                                                                                                   | 1                                     | 1           | 0           | 1           | 148.00                              | 74.00                             | 37.00         | +/-0.25% Center spread |        |

| Bit     | 0                                                                                                   | 1                                     | 1           | 1           | 0           | 152.00                              | 76.00                             | 38.00         | +/-0.25% Center spread | Note 1 |

| (2,7:4) | 0                                                                                                   | 1                                     | 1           | 1           | 1           | 156.00                              | 78.00                             | 39.00         | +/-0.25% Center spread | 110101 |

|         | 1                                                                                                   | 0                                     | 0           | 0           | 0           | 160.00                              | 80.00                             | 40.00         | +/-0.25% Center spread |        |

|         | 1                                                                                                   | 0                                     | 0           | 0           | 1           | 164.00                              | 82.00                             | 41.00         | +/-0.25% Center spread |        |

|         | 1                                                                                                   | 0                                     | 0           | 1           | 0           | 166.60                              | 66.60                             | 33.30         | +/-0.25% Center spread |        |

|         | 1                                                                                                   | 0                                     | 0           | 1           | 1           | 170.00                              | 68.00                             | 34.00         | +/-0.25% Center spread |        |

|         | 1                                                                                                   | 0                                     | 1           | 0           | 0           | 175.00                              | 70.00                             | 35.00         | +/-0.25% Center spread |        |

|         | 1                                                                                                   | 0                                     | 1           | 0           | 1           | 180.00                              | 72.00                             | 36.00         | +/-0.25% Center spread |        |

|         | 1                                                                                                   | 0                                     | 1           | 1           | 0           | 185.00                              | 74.00                             | 37.00         | +/-0.25% Center spread |        |

|         | 1                                                                                                   | 0                                     | 1           | 1           | 1           | 190.00                              | 76.00                             | 38.00         | +/-0.25% Center spread |        |

|         | 1                                                                                                   | 1                                     | 0           | 0           | 0           | 66.80                               | 66.80                             | 33.40         | +/-0.25% Center spread |        |

|         | 1                                                                                                   | 1                                     | 0           | 0           | 1           | 100.20                              | 66.80                             | 33.40         | +/-0.25% Center spread |        |

|         | 1                                                                                                   | 1                                     | 0           | 1           | 0           | 133.60                              | 66.80                             | 33.40         | +/-0.25% Center spread |        |

|         | 1                                                                                                   | 1                                     | 0           | 1           | 1           | 200.40                              | 66.80                             | 33.40         | +/-0.25% Center spread |        |

|         | 1                                                                                                   | 1                                     | 1           | 0           | 0           | 66.60                               | 66.60                             | 33.30         | 0 to -0.5% Down spread |        |

|         | 1                                                                                                   | 1                                     | 1           | 0           | 1           | 100.00                              | 66.60                             | 33.30         | 0 to -0.5% Down spread |        |

|         | 1                                                                                                   | 1                                     | 1           | 1           | 0           | 200.00                              | 66.60                             | 33.30         | 0 to -0.5% Down spread |        |

|         | 1                                                                                                   | 1                                     | 1           | 1           | 1           | 133.33                              | 66.60                             | 33.30         | 0 to -0.5% Down spread |        |

| Bit 3   | 0 - Frequency is selected by hardware select, latched inputs 1 - Frequency is selected by Bit 2,7:4 |                                       |             |             |             |                                     |                                   | 0             |                        |        |

| Bit 1   | 1 -                                                                                                 | 0 - Normal 1 - Spread spectrum enable |             |             |             |                                     |                                   |               | 0                      |        |

| Bit 0   |                                                                                                     |                                       |             |             |             | vill be selected<br>vill be program | by latch inputs<br>med by Byte 10 | bit (4:0)     |                        | 0      |

#### Notes:

1. Default at power-up will be for latched logic inputs to define frequency, as displayed by Bit 3.

Byte 1: Output Control Register (1 = enable, 0 = disable)

| Bit  | Pin#  | PWD | Description   |

|------|-------|-----|---------------|

| Bit7 | 45,44 | 1   | CPUT/C2       |

| Bit6 | 38,37 | 1   | CPUT/C1       |

| Bit5 | 41,40 | 1   | CPUT/C0       |

| Bit4 | -     | Х   | FS4 Read back |

| Bit3 | -     | Х   | FS3 Read back |

| Bit2 | -     | Х   | FS2 Read back |

| Bit1 | -     | Х   | FS1 Read back |

| Bit0 | -     | Х   | FS0 Read back |

# Byte 2: Output Control Register (1 = enable, 0 = disable)

| Bit  | Pin# | PWD | Description |

|------|------|-----|-------------|

| Bit7 | -    | 1   | Reserved    |

| Bit6 | 17   | 1   | PCICLK_9    |

| Bit5 | 16   | 1   | PCICLK_8    |

| Bit4 | 15   | 1   | PCICLK_7    |

| Bit3 | 14   | 1   | PCICLK_6    |

| Bit2 | 12   | 1   | PCICLK_5    |

| Bit1 | 11   | 1   | PCICLK_4    |

| Bit0 | 10   | 1   | PCICLK_3    |

# Byte 3: Output Control Register (1 = enable, 0 = disable)

| Bit  | Pin# | PWD | Description                                     |

|------|------|-----|-------------------------------------------------|

| Bit7 | 23   | 1   | 48MHz_1                                         |

| Bit6 | 22   | 1   | 48MHz_0                                         |

| Bit5 | -    | 1   | Reset gear shift detect 1 = Enable, 0 = Disable |

| Bit4 | -    | 0   | 0 = Sel 48_24# by hardware;1 = I <sup>2</sup> C |

| Bit3 | -    | 0   | Sel 48_24#, 0 = 24MHz, 1 = 48MHz                |

| Bit2 | 8    | 1   | PCICLK_2                                        |

| Bit1 | 7    | 1   | PCICLK_1                                        |

| Bit0 | 6    | 1   | PCICLK_0                                        |

# Byte 4: Output Control Register (1 = enable, 0 = disable)

| Bit   | Pin# | PWD | Description           |

|-------|------|-----|-----------------------|

| Bit 7 | -    | Х   | MultiSEL0 (read back) |

| Bit 6 | -    | Х   | MultiSEL1 (Read back) |

| Bit 5 | 31   | 1   | 3V66-0                |

| Bit 4 | 30   | 1   | 3V66-1                |

| Bit 3 | 48   | 1   | REF0                  |

| Bit 2 | 1    | 1   | REF1                  |

| Bit 1 | 27   | 1   | 3V66_3                |

| Bit 0 | 28   | 1   | 3V66_2                |

#### Notes:

- 1. PWD = Power on Default

- 2. For disabled clocks, they stop low for single ended clocks. Differential CPU clocks stop with CPUCLKT at high, CPUCLKC off, and external resistor termination will bring CPUCLKC low.

Byte 5: Programming Edge Rate (1 = enable, 0 = disable)

| Bit   | Pin# | PWD | Description                                                                                                                  |

|-------|------|-----|------------------------------------------------------------------------------------------------------------------------------|

| Bit 7 | Χ    | Х   | Sel 48_24# (Read back)                                                                                                       |

| Bit 6 | Χ    | Х   | Sel 66_48# (Read back)                                                                                                       |

| Bit 5 | Χ    | 1   | (Reserved)                                                                                                                   |

| Bit 4 | Χ    | 1   | (Reserved)                                                                                                                   |

| Bit 3 | Χ    | 0   | 0 = Sel 66_48# by hardware; 1 = by I <sup>2</sup> C                                                                          |

| Bit 2 | Χ    | 1   | Sel 66_48#, 0 = 48MHz, 1 = 66MHz                                                                                             |

| Bit 1 | Х    | 1   | Async. 3V66 control bit 0 : 3V66 / PCI = 64/32 MHz asynchronous with CPU 1 : 3V66 / PCI = 66.6/33.3 MHz synchronous with CPU |

| Bit 0 | Х    | 0   | (Reserved)                                                                                                                   |

Byte 6: Vendor ID Register (1 = enable, 0 = disable)

| Bit   | Name             | PWD | Description                                                      |

|-------|------------------|-----|------------------------------------------------------------------|

| Bit 7 | Revision ID Bit3 | Х   |                                                                  |

| Bit 6 | Revision ID Bit2 | Х   | Revision ID values will be based on individual device's revision |

| Bit 5 | Revision ID Bit1 | Х   | Revision iD values will be based on individual device's revision |

| Bit 4 | Revision ID Bit0 | Х   |                                                                  |

| Bit 3 | Vendor ID Bit3   | 0   | (Reserved)                                                       |

| Bit 2 | Vendor ID Bit2   | 0   | (Reserved)                                                       |

| Bit 1 | Vendor ID Bit1   | 0   | (Reserved)                                                       |

| Bit 0 | Vendor ID Bit0   | 1   | (Reserved)                                                       |

#### Byte 7: Revision ID and Device ID Register

| Bit   | Name       | PWD | Description                                                             |

|-------|------------|-----|-------------------------------------------------------------------------|

| Bit 7 | Device ID7 | 0   |                                                                         |

| Bit 6 | Device ID6 | 0   |                                                                         |

| Bit 5 | Device ID5 | 1   |                                                                         |

| Bit 4 | Device ID4 | 0   | Device ID values will be based on individual device "28H" in this case. |

| Bit 3 | Device ID3 | 1   | Zon III tills case.                                                     |

| Bit 2 | Device ID2 | 0   |                                                                         |

| Bit 1 | Device ID1 | 0   |                                                                         |

| Bit 0 | Device ID0 | 0   |                                                                         |

#### Byte 8: Byte Count Read Back Register

| Bit   | Name  | PWD | Description                                                      |

|-------|-------|-----|------------------------------------------------------------------|

| Bit 7 | Byte7 | 0   |                                                                  |

| Bit 6 | Byte6 | 0   |                                                                  |

| Bit 5 | Byte5 | 0   | NI-4 \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \                         |

| Bit 4 | Byte4 | 0   | Note: Writing to this register will configure byte count and how |

| Bit 3 | Byte3 | 1   | many bytes will be read back, default is $0F_H = 15$ bytes.      |

| Bit 2 | Byte2 | 1   |                                                                  |

| Bit 1 | Byte1 | 1   |                                                                  |

| Bit 0 | Byte0 | 1   |                                                                  |

**Byte 9: Watchdog Timer Count Register**

| Bit   | Name | PWD | Description                                                         |

|-------|------|-----|---------------------------------------------------------------------|

| Bit 7 | WD7  | 0   |                                                                     |

| Bit 6 | WD6  | 0   |                                                                     |

| Bit 5 | WD5  | 0   | The decimal representation of these 8 bits correspond to X •        |

| Bit 4 | WD4  | 0   | 290ms the watchdog timer will wait before it goes to alarm mode     |

| Bit 3 | WD3  | 1   | and reset the frequency to the safe setting. Default at power up it |

| Bit 2 | WD2  | 0   | 8 • 290ms = 2.3 seconds.                                            |

| Bit 1 | WD1  | 0   |                                                                     |

| Bit 0 | WD0  | 0   |                                                                     |

Byte 10: Programming Enable bit 8 Watchdog Control Register

| Bit   | Name              | PWD | Description                                                                                                                    |

|-------|-------------------|-----|--------------------------------------------------------------------------------------------------------------------------------|

| Bit 7 | Program<br>Enable | 0   | Programming Enable bit<br>0 = no programming. Frequencies are selected by HW latches or Byte0 1<br>= enable all PC programing. |

| Bit 6 | WD Enable         | 0   | Watchdog Enable bit. This bit will over write WDEN latched value. 0 = disable, 1 = Enable.                                     |

| Bit 5 | WD Alarm          | 0   | Watchdog Alarm Status 0 = normal 1= alarm status                                                                               |

| Bit 4 | SF4               | 0   |                                                                                                                                |

| Bit 3 | SF3               | 1   | Wetchdon acts from any hits Writing to those hits will configure the acts                                                      |

| Bit 2 | SF2               | 0   | Watchdog safe frequency bits. Writing to these bits will configure the safe                                                    |

| Bit 1 | SF1               | 0   | frequency corrsponding to Byte 0 Bit 2, 7:4 table                                                                              |

| Bit 0 | SF0               | 0   |                                                                                                                                |

Byte 11: VCO Frequency M Divider (Reference divider) Control Register

| Bit   | Name   | PWD | Description                                                  |

|-------|--------|-----|--------------------------------------------------------------|

| Bit 7 | Ndiv 8 | Х   | N divider bit 8                                              |

| Bit 6 | Mdiv 6 | Х   |                                                              |

| Bit 5 | Mdiv 5 | Х   |                                                              |

| Bit 4 | Mdiv 4 | Х   | The decimal respresentation of Mdiv (6:0) corresposd to the  |

| Bit 3 | Mdiv 3 | Х   | reference divider value. Default at power up is equal to the |

| Bit 2 | Mdiv 2 | Х   | latched inputs selection.                                    |

| Bit 1 | Mdiv 1 | Х   |                                                              |

| Bit 0 | Mdiv 0 | Х   |                                                              |

Byte 12: VCO Frequency N Divider (VCO divider) Control Register

| Bit   | Name   | PWD | Description                                                   |

|-------|--------|-----|---------------------------------------------------------------|

| Bit 7 | Ndiv 7 | Χ   |                                                               |

| Bit 6 | Ndiv 6 | Χ   |                                                               |

| Bit 5 | Ndiv 5 | Х   | The decimal representation of Ndiv (8:0) correspond to the    |

| Bit 4 | Ndiv 4 | Х   | VCO divider value. Default at power up is equal to the        |

| Bit 3 | Ndiv 3 | Χ   | latched inputs selecton. Notice Ndiv 8 is located in Byte 11. |

| Bit 2 | Ndiv 2 | Х   |                                                               |

| Bit 1 | Ndiv 1 | Χ   |                                                               |

| Bit 0 | Ndiv 0 | Х   |                                                               |

#### Byte 13: Spread Spectrum Control Register

| Bit   | Name | PWD | Description                                                                                                               |

|-------|------|-----|---------------------------------------------------------------------------------------------------------------------------|

| Bit 7 | SS 7 | Χ   |                                                                                                                           |

| Bit 6 | SS 6 | Χ   | TI 0 10 (400) I (1 II II II                                                                                               |

| Bit 5 | SS 5 | Χ   | The Spread Spectrum (12:0) bit will program the spread                                                                    |

| Bit 4 | SS 4 | Χ   | precentage. Spread precent needs to be calculated based on the                                                            |

| Bit 3 | SS 3 | Χ   | VCO frequency, spreading profile, spreading amount and spread frequency. It is recommended to use ICS software for spread |

| Bit 2 | SS 2 | Χ   | programming. Default power on is latched FS divider.                                                                      |

| Bit 1 | SS 1 | Χ   | programming. Doladic power on 13 laterica i o arvider.                                                                    |

| Bit 0 | SS 0 | Х   |                                                                                                                           |

Byte 14: Spread Spectrum Control Register

| Bit   | Name     | PWD | Description            |

|-------|----------|-----|------------------------|

| Bit 7 | Reserved | Х   | Reserved               |

| Bit 6 | Reserved | Х   | Reserved               |

| Bit 5 | Reserved | Х   | Reserved               |

| Bit 4 | SS 12    | X   | Spread Spectrum Bit 12 |

| Bit 3 | SS 11    | X   | Spread Spectrum Bit 11 |

| Bit 2 | SS 10    | Х   | Spread Spectrum Bit 10 |

| Bit 1 | SS 9     | Х   | Spread Spectrum Bit 9  |

| Bit 0 | SS 8     | Х   | Spread Spectrum Bit 8  |

Byte 15: Output Divider Control Register

| Bit   | Name      | PWD | Description                                                                                                     |

|-------|-----------|-----|-----------------------------------------------------------------------------------------------------------------|

| Bit 7 | CPUDIV3   | Х   | OPHO short if the self-result and formal factors A                                                              |

| Bit 6 | CPUDIV2   | Χ   | CPU2 clock divider ratio can be configured via these 4 bits individually. For divider selection table refer to  |

| Bit 5 | CPUDIV1   | Χ   | Table 1. Default at power up is latched FS divider.                                                             |

| Bit 4 | CPUDIV0   | Χ   | Table 1. Belaut at power up to laterica 1 e divider.                                                            |

| Bit 3 | CPU Div 3 | Х   |                                                                                                                 |

| Bit 2 | CPU Div 2 | Х   | CPU(1:0) clock divider ratio can be configured via these 4 bits individually. For divider selection table refer |

| Bit 1 | CPU Div 1 | Χ   | to Table 1. Default at power up is latched FS divider.                                                          |

| Bit 0 | CPU Div 0 | Χ   | to table 1. Delault at power up is lateried 1 6 divider.                                                        |

Byte 16: Output Divider Control Register

| Bit   | Name       | PWD | Description                                                                                                      |

|-------|------------|-----|------------------------------------------------------------------------------------------------------------------|

| Bit 7 | 3V66 Div 3 | Х   | 2)/(50/(2:0) aloaly divides notice on the configuration                                                          |

| Bit 6 | 3V66 Div 2 | Χ   | 3V66(3:2) clock divider ratio can be configured via these 4 bits individually. For divider selection table refer |

| Bit 5 | 3V66 Div 1 | X   | to Table 1. Default at power up is latched FS divider.                                                           |

| Bit 4 | 3V66 Div 0 | X   | to Table 1. Belault at power up is lateried 1.6 divider.                                                         |

| Bit 3 | 3V66 Div 3 | Χ   |                                                                                                                  |

| Bit 2 | 3V66 Div 2 | Χ   | 3V66(1:0) clock divider ratio can be configured via these 4 bits individually. For divider selection table refer |

| Bit 1 | 3V66 Div 1 | X   | to Table 1. Default at power up is latched FS divider.                                                           |

| Bit 0 | 3V66 Div 0 | X   | to table 1. Deladit at power up is lateried 1 o divider.                                                         |

#### **Byte 17: Output Divider Control Register**

| Bit   | Name          | PWD | Description                                                                                                            |

|-------|---------------|-----|------------------------------------------------------------------------------------------------------------------------|

| Bit 7 | 3V66(3:2)_INV | Χ   | 3V66(3:2) Phase Inversion bit                                                                                          |

| Bit 6 | 3V66(1:0)_INV | Χ   | 3V66(1:0) Phase Inversion bit                                                                                          |

| Bit 5 | CPU_INV       | Χ   | CPUCLK_2 Phase Inversion bit                                                                                           |

| Bit 4 | CPU_INV       | Χ   | CPUCLK Phase Inversion bit                                                                                             |

| Bit 3 | PCI Div 3     | X   |                                                                                                                        |

| Bit 2 | PCI Div 2     | Х   | PCI clock divider ratio can be configured via these 4 bits individually. For divider selection table refer to Table 2. |

| Bit 1 | PCI Div 1     | Х   | Default at power up is latched FS divider.                                                                             |

| Bit 0 | PCI Div 0     | Х   | Dollar at portor up to tatoriou i o dividor.                                                                           |

Table 1 Table 2

| Div (3:2) | 00 | 01  | 10  | 11  | Div (3:2) | 00 | 01  | 10  | 11  |

|-----------|----|-----|-----|-----|-----------|----|-----|-----|-----|

| Div (1:0) | 00 | 01  | 10  | ''  | Div (1:0) | 00 | 01  | 10  | ''  |

| 00        | /2 | /4  | /8  | /16 | 00        | /4 | /8  | /16 | /32 |

| 01        | /3 | /6  | /12 | /24 | 01        | /3 | /6  | /12 | /24 |

| 10        | /5 | /10 | /20 | /40 | 10        | /5 | /10 | /20 | /40 |

| 11        | /7 | /14 | /28 | /56 | 11        | /9 | /18 | /36 | /72 |

#### Byte 18: Group Skew Control Register

| Bit   | Name       | PWD | Description                                                             |

|-------|------------|-----|-------------------------------------------------------------------------|

| Bit 7 | CPU_Skew 1 | 0   | These 2 bits delay the CPUCLKC/T2 with respect to                       |

| Bit 6 | CPU_Skew 0 | 1   | CPUCLKC/T (1:0)<br>00 = 0ps 01 = 250ps 10 = 500ps 11 =750ps             |

| Bit 5 | Reserved   | 0   | Reserved                                                                |

| Bit 4 | Reserved   | 0   | Reserved                                                                |

| Bit 3 | CPU_Skew 1 | 0   | These 2 bits delay the CPUCLKC/T (1:0) clock with respect to CPUCLKC/T2 |

| Bit 2 | CPU_Skew 0 | 1   | 00 = 0ps 01 = 250ps 10 = 500ps 11 = 750ps                               |

| Bit 1 | Reserved   | 0   | Reserved                                                                |

| Bit 0 | Reserved   | 0   | Reserved                                                                |

#### Byte 19: Group Skew Control Register

| Bit   | Name                 | PWD | Programming Sequence |     |      |    |   |       |          |

|-------|----------------------|-----|----------------------|-----|------|----|---|-------|----------|

| Bit 7 |                      | 0   |                      | 0   | 0    | 0  | 0 | 0ps   | Reserved |

| Bit 6 | These 4bits control  | 1   |                      | 0   | 1    | 0  | 0 | 150ps | Reserved |

| Bit 5 | CPU-3V66(3:2)        | 0   |                      | 1   | 0    | 0  | 0 | 300ps | Reserved |

| Bit 4 |                      | 0   |                      | 1   | 1    | 0  | 0 | 450ps | Reserved |

| Bit 3 |                      | 0   |                      | 1   | 1    | 0  | 1 | 600ps | Reserved |

| Bit 2 | These 4 bits control | 1   |                      | 1   | 1    | 1  | 0 | 750ps | Reserved |

| Bit 1 | CPU-3V66(1:0)        | 0   |                      | 1   | 1    | 1  | 1 | 900ps | Reserved |

| Bit 0 |                      | 0   |                      | Res | erve | ed |   |       | Reserved |

#### Byte 20: Group Skew Control Register

| Bit   | Name                | PWD | Programming Sequence |   |   |   |   |       |          |

|-------|---------------------|-----|----------------------|---|---|---|---|-------|----------|

| Bit 7 |                     | 1   |                      | 0 | 0 | 0 | 0 | 0ps   | Reserved |

| Bit 6 | These 4bits control | 0   |                      | 0 | 1 | 0 | 0 | 150ps | Reserved |

| Bit 5 | CPU-PCI(9:0)        | 0   |                      | 1 | 0 | 0 | 0 | 300ps | Reserved |

| Bit 4 |                     | 0   |                      | 1 | 1 | 0 | 0 | 450ps | Reserved |

| Bit 3 |                     | 1   |                      | 1 | 1 | 0 | 1 | 600ps | Reserved |

| Bit 2 | Resreved            | 0   |                      | 1 | 1 | 1 | 0 | 750ps | Reserved |

| Bit 1 | Resieved            | 0   |                      | 1 | 1 | 1 | 1 | 900ps | Reserved |

| Bit 0 |                     | 0   | Reserved             |   |   |   |   |       | Reserved |

#### Byte 21: Slew Rate Control Register

| Bit   | Name                | PWD | Description                               |

|-------|---------------------|-----|-------------------------------------------|

| Bit 7 | PCICLK_2_Slew 1     | 1   | PCICLK2 clock slew rate control bits.     |

| Bit 6 | PCICLK_2_Slew 1     | 0   | 01 = strong:11 = normal; 10 = weak        |

| Bit 5 | PCICLK (1:0)_Slew 0 | 1   | PCICLK(1:0) clock slew rate control bits. |

| Bit 4 | PCICLK (1:0)_Slew 0 | 0   | 01 = strong: 11 = normal; 10 = weak       |

| Bit 3 | 3V66 (3:2)_Slew 1   | 1   | 3V66 (2:1) clock slew rate control bits.  |

| Bit 2 | 3V66 (3:2)_Slew 1   | 0   | 01 = strong: 11 = normal; 10 = weak       |

| Bit 1 | 3V66 (1:0)_Slew 1   | 1   | 3V66 (1:0) clock slew rate control bits.  |

| Bit 0 | 3V66 (1:0)_Slew 0   | 0   | 01 = strong: 11 = normal; 10 = weak       |

Byte 22: Slew Rate Control Register

| Bit   | Name             | PWD | Description                              |

|-------|------------------|-----|------------------------------------------|

| Bit 7 | REF Slew 1       | 1   | REF clock slew rate control bits.        |

| Bit 6 | REF Slew 0       | 0   | 01 = strong: 11 = normal; 10 = weak      |

| Bit 5 | PCI (9:7) Slew 1 | 1   | PCI (9:7)) clock slew rate control bits. |

| Bit 4 | PCI (9:7) Slew 0 | 0   | 01 = strong: 11 = normal; 10 = weak      |

| Bit 3 | PCI (6:5) Slew 1 | 1   | PCI (6:5) clock slew rate control bits.  |

| Bit 2 | PCI (6:5) Slew 0 | 0   | 01 = strong: 11 = normal; 10 = weak      |

| Bit 1 | PCI (4:3) Slew 1 | 1   | PCI (4:3) clock slew rate control bits.  |

| Bit 0 | PCI (4:3) Slew 0 | 0   | 01 = strong: 11 = normal; 10 = weak      |

Byte 23: Slew Rate Control Register

| Bit   | Name            | PWD | Description                            |

|-------|-----------------|-----|----------------------------------------|

| Bit 7 | Reserved        | Х   |                                        |

| Bit 6 | Reserved        | Х   | Reserved                               |

| Bit 5 | Reserved        | 1   | Reserved                               |

| Bit 4 | Reserved        | 0   |                                        |

| Bit 3 | 48MHz Slew 1    | 1   | 48MHz clock slew rate control bits.    |

| Bit 2 | 48MHz Slew 0    | 0   | 01 = strong: 11 = normal; 10 = weakk   |

| Bit 1 | 24_48MHz Slew 1 | 1   | 24_48MHz clock slew rate control bits. |

| Bit 0 | 24_48MHz Slew 0 | 0   | 01 = strong: 11 = normal; 10 = weak    |

**Absolute Maximum Ratings**

Logic Inputs . . . . . . . . . . . . . GND –0.5 V to  $V_{DD}$  +0.5 V

Ambient Operating Temperature  $\ \dots \ 0^{\circ}C$  to  $+70^{\circ}C$

Stresses above those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These ratings are stress specifications only and functional operation of the device at these or any other conditions above those listed in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect product reliability.

#### Electrical Characteristics - Input/Supply/Common Output Parameters

$T_A = 0 - 70C$ ; Supply Voltage  $V_{DD} = 3.3 \text{ V} + 5\%$

| PARAMETER                      | SYMBOL                             | CONDITIONS                                              | MIN           | TYP    | MAX            | UNITS |

|--------------------------------|------------------------------------|---------------------------------------------------------|---------------|--------|----------------|-------|

| Input High Voltage             | $V_{IH}$                           | $\wedge$ $\langle \rightleftharpoons \rangle$           | 2             |        | $V_{DD} + 0.3$ | V     |

| Input Low Voltage              | $V_{IL}$                           |                                                         | $V_{SS}$ -0.3 | フト     | 0.8            | V     |

| Input High Current             | I <sub>IH</sub>                    | $V_{IN} = V_{DD}$                                       | -5            |        | 5              | m A   |

| Input Low Current              | I <sub>IL1</sub>                   | V <sub>IN</sub> = 0 V; Inputs with no pull-up resistors | -5            |        |                | m A   |

| Input Low Current              | I <sub>IL2</sub>                   | V <sub>IN</sub> = 0 V; Inputs with pull-up resistors    | -200          |        |                | m A   |

| Operating                      | . ((                               | C <sub>L</sub> = 0 pF; Select @ 66M                     | >             |        | 100            | m A   |

| Supply Current                 | I <sub>DD3.3OP</sub>               | C <sub>L</sub> = Full load                              |               |        | 360            | m A   |

| Power Down                     | 405                                | IREF=2.32                                               |               |        | 25             | m A   |

| Supply Current                 | IDD3.3PD                           | IREF= 5mA                                               |               |        | 45             | m A   |

| Input frequency                | Ej                                 | $V_{DD} = 3.3 \text{ V};$                               |               | 14.318 |                | MHz   |

| Pin Inductance                 | L <sub>pin</sub>                   |                                                         |               |        | 7              | nΗ    |

|                                | C <sub>IN</sub>                    | Logic Inputs                                            |               |        | 5              | pF    |

| Input Capacitance <sup>1</sup> | Cout                               | Out put pin capacitance                                 |               |        | 6              | pF    |

|                                | CINX                               | X1 & X2 pins                                            | 27            | 36     | 45             | pF    |

| Transition Time <sup>1</sup>   | $T_{trans}$                        | To 1st crossing of target Freq.                         |               |        | 3              | mS    |

| Settling Time <sup>1</sup>     | // T <sub>s</sub>                  | From 1st crossing to 1% target Freq.                    |               |        | 3              | m S   |

| Clk Stabilization <sup>1</sup> | T <sub>STAB</sub>                  | From V <sub>DD</sub> = 3.3 V to 1% target Freq.         |               |        | 3              | mS    |

| Delay                          | t <sub>PZH</sub> ,t <sub>PZH</sub> | output enable delay (all outputs)                       | / 1           |        | 10             | nS    |

| Dolay                          | t <sub>PLZ</sub> ,t <sub>PZH</sub> | output disable delay (all outputs)                      | 1             |        | 10             | nS    |

<sup>1</sup>Guarenteed by design, not 100% tested in production.

#### **Electrical Characteristics - CPUCLK**

$T_A = 0 - 70^{\circ} \text{ C}$ ;  $V_{DD} = 3.3 \text{ V} + /-5\%$ ; (unless otherwise stated)

| PARAMETER                           | SYMBOL                | CONDITIONS                                                               | MIN / | TYP                         | MAX | UNITS |

|-------------------------------------|-----------------------|--------------------------------------------------------------------------|-------|-----------------------------|-----|-------|

| Current Source                      | Z <sub>O</sub>        | $V_O = V_X$                                                              | 3000  | $\langle \langle / \rangle$ |     | 0     |

| Output Impedance                    | 20                    | $v_0 = v_X$                                                              | 3000  | \\'/                        |     | Ω     |

| Output High Voltage                 | $V_{OH}$              | V <sub>R</sub> = 475W +1%; IREF = 2.32m A; I <sub>OH</sub> = 6*IREF      |       | 0.71                        | 1.2 | V     |

| Output High Current                 | I <sub>OH</sub>       | $V_{R} = 47.0 V_{\frac{1}{2}} 170$ , INCLI = 2.32H/A, $I_{OH} = 0$ INCLI |       | -13.92                      |     | m A   |

| Rise Time <sup>1</sup>              | t <sub>r</sub>        | $V_{OL} = 20\%, V_{OH} = 80\%$                                           | 175   |                             | 700 | ps    |

| Differential Crossover              | V                     | Note 3                                                                   | 45    | 50                          | 55  | %     |

| Voltage <sup>1</sup>                | $V_X$                 | Note 3                                                                   | V 45  | 30                          | 55  | /0    |

| Duty Cycle <sup>1</sup>             | d <sub>t</sub>        | $V_T = 50\%$                                                             | 45    | 51                          | 55  | %     |

| Skew <sup>1</sup> , CPU to CPU      | t <sub>sk</sub>       | V <sub>T</sub> = 50%                                                     |       |                             | 100 | ps    |

| Jitter, Cycle-to-cycle <sup>1</sup> | t <sub>jcyc-cyc</sub> | $V_T = V_X$                                                              |       |                             | 150 | ps    |

#### Notes:

1 - Guaranteed by design, not 100% tested in production.

#### **Electrical Characteristics - PCICLK**

$T_A = 0 - 70C$ ;  $V_{DD} = 3.3 \text{ V} + /-5\%$ ;  $C_L = 10-30 \text{ pF}$  (unless otherwise stated)

| PARAMETER           | SYMBOL                         | CONDITIONS                                       | MIN | TYP   | MAX  | UNITS |

|---------------------|--------------------------------|--------------------------------------------------|-----|-------|------|-------|

| Output Frequency    | F0 <sup>1</sup>                |                                                  |     | 33.33 |      | MHz   |

| Output Impedance    | R <sub>DSN1</sub> <sup>1</sup> | $V_{O} = V_{DD}^{*}(0.5)$                        | 12  |       | 55   | Ω     |

| Output High Voltage | V <sub>OH1</sub>               | l <sub>OH</sub> = -1 m A                         | 2.4 |       |      | V     |

| Output Low Voltage  | V <sub>OL1</sub>               | I <sub>OL</sub> = 1 mA                           |     |       | 0.55 | V     |

| Output High Current | OH1                            | VOH @ MIN = 1.0 V, VOH @ MAX = 3.135 V           | -33 |       | -33  | m A   |

| Output Low Current  | I <sub>OL1</sub>               | VOL@ MIN = 1.95 V, VOL@ MAX= 0.4                 | 30  |       | 38   | m A   |

| Rise Time           | t <sub>r1</sub> 1              | $V_{OL} = 0.4 \text{ V}, V_{OH} = 2.4 \text{ V}$ | 0.5 |       | 2    | ns    |

| Fall Time           | ) t <sub>f1</sub> 1            | $V_{OH} = 2.4 \text{ V}, V_{OL} = 0.4 \text{ V}$ | 0.5 |       | 2    | ns    |

| Duty Cycle          | d <sub>t1</sub> <sup>1</sup>   | V <sub>T</sub> = 1.5 V                           | 45  |       | 55   | %     |

| Skew                | t <sub>sk1</sub> 1             | $V_{T} = 1.5 \text{ V}$                          |     |       | 500  | ps    |

| Jitter              | t <sub>jcyc-cyc</sub> 1        | $V_{T} = 1.5 \text{ V}$                          |     |       | 250  | ps    |

<sup>&</sup>lt;sup>1</sup>Guarenteed by design, not 100% tested in production.

#### Electrical Characteristics - 3V66

$T_A = 0 - 70C$ ;  $V_{DD} = 3.3 \text{ V +/-5\%}$ ;  $C_L = 10-30 \text{ pF}$  (unless otherwise stated)

|                     |                                | • •                                              |      | / /     |     |       |

|---------------------|--------------------------------|--------------------------------------------------|------|---------|-----|-------|

| PARAMETER           | SYMBOL                         | CONDITIONS                                       | MIN  | TŶP     | MAX | UNITS |

| Output Frequency    | F <sub>O1</sub>                |                                                  |      | 66.66   |     | MHz   |

| Output Impedance    | R <sub>DSP1</sub> <sup>1</sup> | $V_O = V_{DD}^*(0.5)$                            | (12/ |         | 55  | Ω     |

| Output High Voltage | V <sub>OH1</sub>               | $I_{OH} = -1 \text{ mA}$                         | 2.4  | <i></i> |     | V     |

| Output Low Voltage  | V <sub>OL1</sub>               | I <sub>OL</sub> = 1 mA                           | 1/2  |         | 0.4 | V     |

| Output High Current | I <sub>OH1</sub>               | VOH @ MIN = 1.0 V, VOH @ MAX = 3.135 V           | -33  |         | -33 | m A   |

| Output Low Current  | I <sub>OL1</sub>               | VOL@ MIN = 1.95 V, VOL@ MAX= 0.4                 | > 30 |         | 38  | m A   |

| Rise Time           | t <sub>r1</sub> ( ( <          | $V_{OL} = 0.4 \text{ V}, V_{OH} = 2.4 \text{ V}$ | 0.5  |         | 2   | ns    |

| Fall Time           | t <sub>11</sub>                | $V_{OH} = 2.4 \text{ V}, V_{OL} = 0.4 \text{ V}$ | 0.5  |         | 2   | ns    |

| Duty Cycle          | d <sub>11</sub> 1              | V <sub>T</sub> = 1.5 V                           | 45   |         | 55  | %     |

| Skew                | t <sub>sk1</sub> 1             | $V_T = 1.5 \text{ V}$                            |      |         | 500 | ps    |

| Jitter              | tjcyc-cyc <sup>1</sup>         | $V_T = 1.5 \text{ V}$                            |      |         | 250 | ps    |

<sup>&</sup>lt;sup>1</sup>Guarenteed by design, not 100% tested in production.

#### Electrical Characteristics - 48MHz

$T_A = 0 - 70C$ ;  $V_{DD} = 3.3 \text{ V +/-5\%}$ ;  $C_L = 10-30 \text{ pF (unless otherwise stated)}$

| PARAMETER                | SYMBOL                         | CONDITIONS                                       | MIN | TYP | MAX  | UNITS |

|--------------------------|--------------------------------|--------------------------------------------------|-----|-----|------|-------|

| Output Frequency         | Fo <sup>1</sup>                | $V_0 = V_{DD}^*(0.5)$                            |     | 48  |      | MHz   |

| Output Impedance         | R <sub>DSN1</sub> <sup>1</sup> | $V_{\rm O} = V_{\rm DD}^*(0.5)$                  | 12  |     | 55   | Ω     |

| Output High Voltage      | V <sub>OĤ1</sub>               | I <sub>OH</sub> = -1 m A                         | 2.4 |     |      | V     |

| Output Low Voltage       | V <sub>OL1</sub>               | I <sub>OL</sub> = 1 mA                           |     |     | 0.55 | V     |

| Output High Current      | I <sub>OH1</sub>               | VOH @ MIN = 1.0 V, VOH @ MAX = 3.135 V           | -29 |     | -23  | m A   |

| Output Low Current       | I <sub>OL1</sub>               | VOL@ MIN = 1.95 V, VOL@ MAX= 0.4                 | 29  |     | 27   | m A   |

| 48DOT Rise Time          | t <sub>r1</sub> 1              | $V_{OL} = 0.4 \text{ V}, V_{OH} = 2.4 \text{ V}$ | 0.5 |     | 1    | ns    |

| 48DOT Fall Time          | t <sub>f1</sub> 1              | $V_{OH} = 2.4 \text{ V}, V_{OL} = 0.4 \text{ V}$ | 0.5 |     | 1    | ns    |

| VCH 48 USB<br>Rise Time  | t <sub>r</sub> <sup>1</sup>    | V <sub>OL</sub> = 0.4 V, V <sub>OH</sub> = 2.4 V | 1   |     | 2    | ns    |

| VCH 48 USB<br>Fall Time  | tf <sup>1</sup>                | $V_{OH} = 2.4 \text{ V}, V_{OL} = 0.4 \text{ V}$ | 1   |     | 2    | ns    |

| 48 DOT to 48 USB<br>Skew | tskew <sup>1</sup>             | VT=1.5V                                          |     |     | 1    | ns    |

| Duty Cycle               | d <sub>t1</sub> <sup>1</sup>   | $V_T = 1.5 \text{ V}$                            | 45  |     | 55   | %     |

| Jitter                   | t <sub>jcyc-cyc</sub> 1        | $V_T = 1.5 \text{ V}$                            |     |     | 350  | ps    |

<sup>&</sup>lt;sup>1</sup>Guarenteed by design, not 100% tested in production.

#### Electrical Characteristics - REF

$T_A = 0 - 70C$ ;  $V_{DD} = 3.3 \text{ V +/-5\%}$ ;  $C_L = 10-20 \text{ pF}$  (unless otherwise stated)

| PARAMETER           | SYMBOL                         | CONDITIONS                                       | MIN     | TYP               | MAX | UNITS |

|---------------------|--------------------------------|--------------------------------------------------|---------|-------------------|-----|-------|

| Output Frequency    | F <sub>O1</sub>                |                                                  | _ ( ( < | $\langle \rangle$ |     | MHz   |

| Output Impedance    | R <sub>DSP1</sub> <sup>1</sup> | $V_{O} = V_{DD}^{*}(0.5)$                        | 20      |                   | 60  | Ω     |

| Output High Voltage | V <sub>OH1</sub>               | I <sub>OH</sub> = -1 mA                          | 2.4     |                   |     | V     |

| Output Low Voltage  | V <sub>OL1</sub>               | $I_{OL} = 1 \text{ mA}$                          |         |                   | 0.4 | V     |

| Output High Current | I <sub>OH1</sub>               | VOH@ MIN = 1.0 V, VOH@ MAX = 3.135 V             | -29     |                   | -23 | mA    |

| Output Low Current  | I <sub>OL1</sub>               | VOL@ MIN = 1.95 V, VOL@ MAX= 0.4                 | 29      |                   | 27  | mA    |

| Rise Time           | t <sub>11</sub>                | $V_{OL} = 0.4 \text{ V}, V_{OH} = 2.4 \text{ V}$ | 1       |                   | 4   | ns    |

| Fall Time           | t <sub>f1</sub>                | $V_{OH} = 2.4 \text{ V}, V_{OL} = 0.4 \text{ V}$ | 1       |                   | 4   | ns    |

| Duty Cycle          | d <sub>t1</sub>                | $V_T = 1.5 \text{ V}$                            | 45      |                   | 55  | %     |

| Jitter              | t <sub>jcyc-cyc</sub>          | $V_T = 1.5 \text{ V}$                            |         |                   | 500 | ps    |

<sup>1</sup>Guarenteed by design, not 100% tested in production.

# **Shared Pin Operation - Input/Output Pins**

The I/O pins designated by (input/output) serve as dual signal functions to the device. During initial power-up, they act as input pins. The logic level (voltage) that is present on these pins at this time is read and stored into a 5-bit internal data latch. At the end of Power-On reset, (see AC characteristics for timing values), the device changes the mode of operations for these pins to an output function. In this mode the pins produce the specified buffered clocks to external loads.

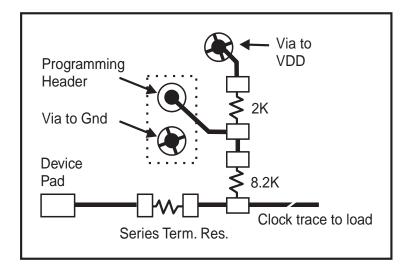

To program (load) the internal configuration register for these pins, a resistor is connected to either the VDD (logic 1) power supply or the GND (logic 0) voltage potential. A 10 Kilohm (10K) resistor is used to provide both the solid CMOS programming voltage needed during the power-programming period and to provide an insignificant load on the output clock during the subsequent operating period. Figure 1 shows a means of implementing this function when

a switch or 2 pin header is used. With no jumper is installed the pin will be pulled high. With the jumper in place the pin will be pulled low. If programmability is not necessary, than only a single resistor is necessary. The programming resistors should be located close to the series termination resistor to minimize the current loop area. It is more important to locate the series termination resistor close to the driver than the programming resistor.

Fig. 1

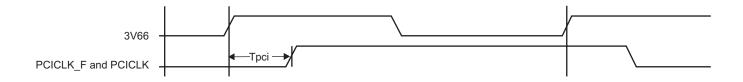

#### Un-Buffered Mode 3V66 & PCI Phase Relationship

All 3V66 clocks are to be in pphase with each other. In the case where 3V66\_1 is configured as 48MHz VCH clock, there is no defined phase relationship between 3V66\_1/VCH and other 3V66 clocks. The PCI group should lag 3V66 by the standard skew described below as Tpci.

# Group Skews at Common Transition Edges: (Un-Buffered Mode)

| GROUP       | SYMBOL                | CONDITIONS                    | MIN | TYP | MAX | UNITS |

|-------------|-----------------------|-------------------------------|-----|-----|-----|-------|

| 3V66        | 3V66                  | 3V66 pin to pin skew          | 0   |     | 500 | ps    |

| PCI         | PCI                   | PCI_F and PCI pin to pin skew | 0   |     | 500 | ps    |

| 3V66 to PCI | S <sub>3V66-PCI</sub> | 3V66 leads 33MHz PCI          | 1.5 |     | 3.5 | ns    |

<sup>&</sup>lt;sup>1</sup>Guarenteed by design, not 100% tested in production.

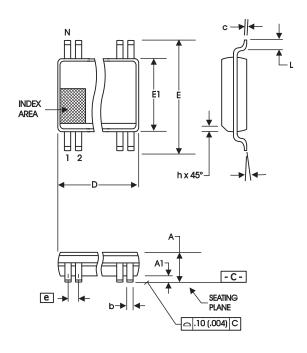

|        | In Millimeters    |       | In Inches         |       |  |

|--------|-------------------|-------|-------------------|-------|--|