# P29FCT52A/B/C (P29PCT52A/B/C) P29FCT53A/B/C (P29PCT53A/B/C) OCTAL REGISTERED TRANSCEIVER

# **FEATURES**

- Function, Pinout, and Drive Compatible with the FCT, F Logic, and Am2952/53

- FCT-C speed at 6.3ns max. (Com'l) FCT-A speed at 7.5ns max. (Com'l)

- CMOS for Low Power Consumption

- Edge-rate Control Circuitry for Significantly Improved Noise Characteristics

- **■** ESD protection exceeds 2000V

- Inputs and Outputs Interface Directly with TTL, NMOS, and CMOS Devices

- Outputs Meet Levels Required for CMOS Static RAM Low Power Standby Mode

- # 64 mA Sink Current (Com'l), 48 mA (Mil) 24 mA Source Current (Com'l), 15 mA (Mil)

- Manufactured in 0.8 micron PACE Technology™

# DESCRIPTION

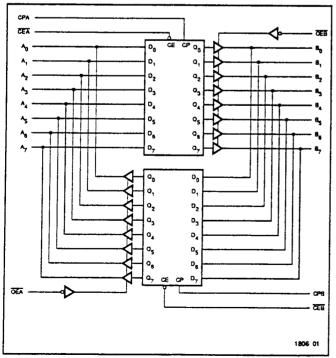

The '29FCT53 AND '29FCT53 have two 8-bit back-to-back registers that store data flowing in both directions between two bidirectional buses. Separate clock, clock enable and 3-state output enable signals are provided for each register. Both A outputs and B outputs are guaranteed to sink 64mA.

The '29FCT52 is an inverting option of the '29FCT53.

The '29FCT52 and '29FCT53 are manufactured using PACE Technology™ which is Performance Advanced

CMOS Engineered to use 0.8 micron effective channel lengths resulting in 500 picoseconds loaded\* internal gate delays. PACE Technology includes two-level metal and epitaxial substrates. In addition to very high performance and very high density, the technology features latch-up protection and single event upset protection, and is supported by a Class 1 environment volume production facility.

For a fan-in/fan-out of 4 at 85°C junction temperature and 5.0 V supply.

For a fan-in/fan-out of 1, the internal gate delay is 200 picosecond at room temperature.

#### 24

#### **FUNCTIONAL BLOCK DIAGRAM**

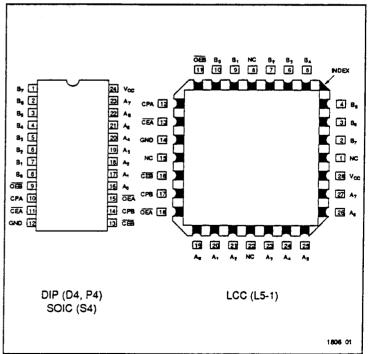

#### PIN CONFIGURATIONS

Means Quality, Service and Speed

# REGISTERED FUNCTION TABLE

|   | Inputs |    | Internal | Function  |

|---|--------|----|----------|-----------|

| D | СР     | CE | Q        | Function  |

| X | X      | Н  | NC       | Hold Data |

| L | 7      | L  | L        | Load Data |

| Н |        | L  | Н        |           |

# **OUTPUT CONTROL**

| ŌĒ     | internal | Y-Ou     | tputs    | _               |

|--------|----------|----------|----------|-----------------|

| j<br>S | Q        | '29FCT52 | '29FCT53 | Function        |

| Ι      | Х        | Z        | Z        | Disable Outputs |

| L      | L        | L        | Н        | Enable Outputs  |

| L      | Н        | Н        | L        |                 |

1806 Tbl 01

1806 Tbl 02

# PIN DESCRIPTION

| Name             | 1/0 | Description                                                                                                                                                                                                                                                |

|------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A <sub>0-7</sub> | 1/0 | Eight bidirectional lines carrying the A Register inputs or B Register outputs.                                                                                                                                                                            |

| B <sub>0-7</sub> | 1/0 | Eight bidirectional lines carrying the B Register inputs or A Register outputs.                                                                                                                                                                            |

| СРА              | ı   | Clock for the A Register. When CEA is LOW, data is entered into the A Register on the LOW-to-HIGH transition of the CPA signal.                                                                                                                            |

| CEA              | 1   | Clock Enable for the A Register. When $\overline{CEA}$ is LOW, data is entered into the A Register on the LOW-to-HIGH transition of the CPA signal. When $\overline{CEA}$ is HIGH, the A Register holds its contents regardless of CPA signal transitions. |

| OEB              | ı   | Output Enable for the A Register. When $\overline{OEB}$ is LOW, the A Register outputs are enabled onto the $B_{0-7}$ lines. When $\overline{OEB}$ is HIGH, the $B_{0-7}$ outputs are in the high impedence state.                                         |

| СРВ              | I   | Clock for the B Register. When $\overline{\text{CEB}}$ is LOW, data is entered into the B Register on the LOW-to-HIGH transition of the CPB signal.                                                                                                        |

| CEB              | l   | Clock Enable for the B Register. When $\overline{CEB}$ is LOW, data is entered into the B Register on the LOW-to-HIGH transition of the CPB signal. When $\overline{CEB}$ is HIGH, the B Register holds its contents regardless of CPB signal transitions. |

| ŌĒĀ              | l   | Output Enable for the B Register. When $\overline{OEA}$ is LOW, the B Register outputs are enabled onto the $A_{0-7}$ lines. When $\overline{OEA}$ is HIGH, the $A_{0-7}$ outputs are in the high impedence state.                                         |

1806 Tbi 03

### **ABSOLUTE MAXIMUM RATINGS12**

| Symbol           | Parameter                           | Value        | Unit |

|------------------|-------------------------------------|--------------|------|

| T <sub>stG</sub> | Storage Temperature                 | -65 to +150  | °C   |

| T <sub>A</sub>   | Ambient Temperature<br>Under Bias   | -65 to +135  | °C   |

| V <sub>cc</sub>  | V <sub>cc</sub> Potential to Ground | -0.5 to +7.0 | V    |

| l <sub>IN</sub>  | Input Current                       | -30 to +5.0  | mA   |

| lotes: | 1806 Tbl |

|--------|----------|

|        |          |

Operation beyond the limits set forth in the above table may impair the useful life of the device. Unless otherwise noted, these limits are over the operating free-air temperature range.

| Symbol           | Parameter                 | Value                    | Unit |

|------------------|---------------------------|--------------------------|------|

| OUTPUT           | Current Applied to Output | 120                      | mA   |

| V <sub>IN</sub>  | Input Voltage             | $-0.5$ to $V_{cc} + 0.5$ | ٧    |

| V <sub>out</sub> | Voltage Applied to Output | $-0.5$ to $V_{cc} + 0.5$ | ٧    |

1806 Tbl 05

#### RECOMMENDED OPERATING CONDITIONS

| Free Air Ambient Temperature | Min   | Max    |

|------------------------------|-------|--------|

| Military                     | -55°C | +125°C |

| Commercial                   | 0°C   | +70°C  |

| Supply Voltage (V <sub>cc</sub> ) | Min    | Max    |

|-----------------------------------|--------|--------|

| Military                          | +4.5V  | +5.5V  |

| Commercial                        | +4.75V | +5.25V |

1806 Tbl 07

## DC ELECTRICAL CHARACTERISTICS (Over recommended operating conditions)

1806 Tbl 06

| Symbol           |                                                | Parameter                                                        | Min                                 | Typ¹                          | Max                 | Units       | V <sub>cc</sub>   | Conditions                        |

|------------------|------------------------------------------------|------------------------------------------------------------------|-------------------------------------|-------------------------------|---------------------|-------------|-------------------|-----------------------------------|

| V <sub>IH</sub>  | Input HIC                                      | GH Voltage                                                       | 2.0                                 |                               |                     | V           |                   |                                   |

| V <sub>IL</sub>  | Input LO                                       | Input LOW Voltage                                                |                                     |                               | 0.8                 | V           |                   |                                   |

| V <sub>H</sub>   | Hysteres                                       | is                                                               |                                     | 0.35                          |                     | ٧           |                   | All inputs                        |

| V <sub>CD</sub>  | Input Cla                                      | ımp Diode Voltage                                                |                                     | -0.7                          | -1.2                | V           | MIN               | I <sub>IN</sub> = -18mA           |

|                  |                                                | $V_{cc} = 3V, V_{IN} = 0.2V, \text{ or } V_{cc} - 0.2V$          | $V_{cc} - 0.2$                      | V <sub>cc</sub>               |                     | ٧           |                   | I <sub>OH</sub> = -32μΑ           |

| V <sub>OH</sub>  | Output<br>HIGH<br>Voltage                      | Military/Commercial (CMOS)<br>Military (TTL)<br>Commercial (TTL) | V <sub>cc</sub> - 0.2<br>2.4<br>2.7 | V <sub>cc</sub><br>4.3<br>4.3 |                     | >>>         | MIN<br>MIN<br>MIN | I <sub>OH</sub> = -15mA           |

|                  |                                                | $V_{CC} = 3V$ , $V_{IN} = 0.2V$ , or $V_{CC} - 0.2V$             |                                     | ·                             | 0.2                 | ٧           |                   | I <sub>OL</sub> = 300μA           |

| V <sub>OL</sub>  | Output<br>LOW<br>Voltage                       | Military/Commercial (CMOS)<br>Military (TTL)<br>Commercial (TTL) | ·                                   | GND<br>0.3<br>0.3             | 0.2<br>0.55<br>0.55 | V<br>V<br>V | MIN<br>MIN<br>MIN | $I_{OL} = 48 \text{mA}$           |

| I <sub>IH</sub>  | Input HIC                                      | GH Current (Except I/O Pins)                                     |                                     |                               | 5                   | μА          | MAX               | V <sub>IN</sub> = V <sub>CC</sub> |

| 1,               | Input LO                                       | W Current (Except I/O Pins)                                      |                                     |                               | <del></del> 5       | μА          |                   | V <sub>IN</sub> = GND             |

| I <sub>IH</sub>  | input Hi                                       | GH Current <sup>3</sup> (Except I/O Pins)                        |                                     |                               | 5                   | μА          | MAX               | $V_{1N} = 2.7V$                   |

| I <sub>IL</sub>  | Input LO                                       | W Current <sup>3</sup> (Except I/O Pins)                         |                                     |                               | <b>-</b> 5          | μΑ          | MAX               | $V_{1N} = 0.5V$                   |

| I <sub>IH</sub>  | Input HIG                                      | 6H Current (I/O Pins only)                                       |                                     |                               | 15                  | μА          | MAX               | $V_{IN} = V_{CC}$                 |

| 1,_              | Input LO                                       | W Current (I/O Pins only)                                        |                                     |                               | <b>–15</b>          | μΑ          | MAX               | V <sub>IN</sub> = GND             |

| 1,,,             | Input HIG                                      | GH Current <sup>3</sup> (I/O Pins only)                          |                                     |                               | 15                  | μΑ          | MAX               | $V_{1N} = 2.7V$                   |

| 1,               | Input LOW Current <sup>3</sup> (I/O Pins only) |                                                                  |                                     |                               | <b>–</b> 15         | μΑ          | MAX               | $V_{1N} = 0.5V$                   |

| los              | Output Short Circuit Current <sup>2</sup>      |                                                                  | -60                                 |                               |                     | mA          | MAX               | $V_{OUT} = 0.0V$                  |

| C <sub>IN</sub>  | Input Cap                                      | pacitance <sup>3</sup>                                           |                                     | 5                             | 10                  | pF          |                   | All inputs                        |

| C <sub>out</sub> | Output C                                       | apacitance <sup>3</sup>                                          |                                     | 9                             | 12                  | рF          |                   | All outputs                       |

#### Notes:

- 1. Typical limits are at  $V_{cc} = 5.0V$ ,  $T_A = +25$ °C ambient.

- 2. Not more than one output should be shorted at a time. Duration of short should not exceed one second. The use of high speed test apparatus and/or sample and hold techniques are preferable in order to minimize internal chip heating and more accurately reflect

- operational values. Otherwise prolonged shorting of a high output may raise the chip temperature well above normal and thereby cause invalid readings in other parameter tests. In any sequence of parameter tests, I os tests should be performed last.

- 3. This parameter is guaranteed but not tested.

1**80**6Tbl 08

<sup>2.</sup> Unused inputs must always be connected to an appropriate logic voltage level, preferably either  $V_{\infty}$  or ground.

# DC CHARACTERISTICS (Over recommended operating conditions unless otherwise specified.)

| Symbol           | Parameter                                       | Typ¹ | Max   | Units      | Conditions                                                                                                                                                                                                                   |

|------------------|-------------------------------------------------|------|-------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Icc              | Quiescent Power Supply<br>Current (CMOS inputs) | 0.5  | 1.5   | mA         | $V_{CC} = MAX$ , $f_1 = 0$ ,<br>Outputs Open,<br>$V_{IN} \le 0.2V$ or $V_{IN} \ge V_{CC} - 0.2V$                                                                                                                             |

| ΔΙ <sub>cc</sub> | Quiescent Power Supply Current (TTL inputs)     | 0.5  | 2.0   | mA         | $V_{CC} = MAX$ , $V_{IN} = 3.4V^2$ , $f_1 = 0$ , Outputs Open                                                                                                                                                                |

| I <sub>CCD</sub> | Dynamic Power Supply Current <sup>3</sup>       | 0.15 | 0.25  | mA/<br>mHz | $V_{CC}$ = MAX, One Input Toggling,<br>50% Duty Cycle, $\overline{OEA}$ or $\overline{OEB}$ = GND<br>Outputs Open,<br>$V_{IN} \le 0.2V$ or $V_{IN} \ge V_{CC} - 0.2V$                                                        |

|                  |                                                 | 2.0  | 4.0   | mA         | $V_{CC}$ = MAX, $f_0$ = 10 MHz,<br>50% Duty Cycle, Outputs Open,<br>One Bit Toggling at $f_1$ = 5MHz,<br>OEA or OEB = GND,<br>$V_{IN} \le 0.2V$ or $V_{IN} \ge V_{CC} - 0.2V$                                                |

| I <sub>c</sub>   | Total Power Supply Current⁵                     | 2.5  | 6.0   | mA         | $V_{CC}$ = MAX, $f_0$ = 10 MHz,<br>50% Duty Cycle, Outputs Open,<br>One Bit Toggling at $f_1$ = 5MHz,<br>OEA or OEB = GND,<br>$V_{IN}$ = 3.4V or $V_{IN}$ = GND                                                              |

|                  |                                                 | 4.3  | 7.8⁴  | mA         | $V_{\rm CC}$ = MAX, $f_{\rm 0}$ = 10 MHz,<br>50% Duty Cycle, Outputs Open,<br>Eight Bits Toggling at $f_{\rm 1}$ = 2.5MHz,<br>OEA or OEB = GND,<br>$V_{\rm IN} \le 0.2 {\rm V}$ or $V_{\rm IN} \ge V_{\rm CC} - 0.2 {\rm V}$ |

|                  |                                                 | 6.5  | 16.84 | mA         | $V_{CC} = MAX$ , $f_0 = 10 MHz$ ,<br>50% Duty Cycle, Outputs Open,<br>Eight Bits Toggling at $f_1 = 2.5MHz$ ,<br>$\overline{OEA}$ or $\overline{OEB} = GND$ ,<br>$V_{IN} = 3.4V$ or $V_{IN} = GND$                           |

Notes

Typical values are at V<sub>ce</sub> = 5.0V, +25°C ambient and maximum loading. I<sub>ccor</sub>= Power Supply Current for a TTL High Input

$(V_N = 3.4V)$

D<sub>H</sub> = Duty Cycle for TTL Inputs High

N, = Number of TTL Inputs at D,

I<sub>cco</sub> = Dynamic Current Caused by an Input Transition Pair (HLH or LHL)

1806 Tbl 09

f<sub>e</sub> = Clock Frequency for Register Devices (Zero for Non-Register Devices)

f. = Input Frequency

N, = Number of Inputs at f,

All currents are in milliamps and all frequencies are in megahertz.

<sup>2.</sup> Per TTL driven input ( $V_N = 3.4V$ ); all other inputs at  $V_{\rm oc}$  or GND.

<sup>3.</sup> This parameter is not directly testable, but is derived for use in Total Power Supply calculations.

Values for these conditions are examples of the I<sub>cc</sub> formula. These limits are guaranteed but not tested.

<sup>5.</sup>  $l_{\text{CC}} = l_{\text{OUIESCENT}} + l_{\text{INPUTS}} + l_{\text{DYNAMC}}$   $l_{\text{CC}} = l_{\text{CCOC}} + l_{\text{CCOT}} D_{\text{H}} N_{\text{T}} + l_{\text{CCO}} (f_{\text{d}}/2 + f_{\text{1}} N_{\text{1}})$   $l_{\text{CCOC}} = \text{Quiescent Current with CMOS input levels}$

## **AC CHARACTERISTICS**

|                                      |                                                                  | Р     | P29FCT52A/53A |      |       | P29FCT52B/53B |      |         |          | P    | 29FC7       |          |      |       |            |

|--------------------------------------|------------------------------------------------------------------|-------|---------------|------|-------|---------------|------|---------|----------|------|-------------|----------|------|-------|------------|

| Symbol                               | Parameter                                                        | MIL C |               | CC   | COM'L |               | MIL  |         | COM'L    |      | <b>/</b> IL | IL COM'L |      | Units | Fig.       |

|                                      |                                                                  | Min.  | Max.          | Min. | Max.  | Min.          | Max. | Min.    | Max.     | Min. | Max.        | Min.     | Max. |       | No.        |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay<br>CPA, CPB to B <sub>n</sub> , A <sub>n</sub> | 2.0   | 11.0          | 2.0  | 10.0  | 2.0           | 8.0  | 2.0     | 7.5      | 2.0  | 7.3         | 2.0      | 6.3  | ns    | 1,5        |

| t <sub>PZH</sub><br>t <sub>PZL</sub> | Output Enable Time<br>OEA or OEB to A, or B,                     | 1.5   | 13.0          | 1.5  | 10.5  | 1.5           | 8.5  | 1.5     | 8.0      | 1.5  | 8.0         | 1.5      | 7.0  | ns    | 1,7,8      |

| t <sub>PHZ</sub><br>t <sub>PLZ</sub> | Output Enable Time<br>OEA or OEB to A, or B,                     | 1.5   | 10.0          | 1.5  | 10.0  | 1.5           | 8.0  | 1.5     | 7.5      | 1.5  | 7.5         | 1.5      | 6.5  | ns    | 1,7,8      |

| lotes:                               |                                                                  |       |               |      |       |               |      | <u></u> | <u> </u> | L    | <u></u>     |          |      | 1     | 806 Tbl 10 |

#### Notes:

- 1. Minimum limits are guaranteed but not tested on Propagation Delays.

- 2. AC Characteristics guaranteed with C<sub>L</sub> = 50pF as shown in Figure 1.

### **AC OPERATING REQUIREMENTS**

|                                          |                                                                         | P2   | P29FCT52A/53A |      |       | P29FCT52B/53B |      |      |       | P29FCT52C/53C |      |       |      |       |      |

|------------------------------------------|-------------------------------------------------------------------------|------|---------------|------|-------|---------------|------|------|-------|---------------|------|-------|------|-------|------|

| Symbol                                   | Parameter                                                               | N    | MIL           |      | COM'L |               | MIL  |      | COM'L |               | IL   | COM'L |      | Units | Fig. |

|                                          |                                                                         | Min. | Max.          | Min. | Max.  | Min.          | Max. | Min. | Max.  | Min.          | Max. | Min.  | Max. |       | INC. |

| t <sub>s</sub> (H)<br>t <sub>s</sub> (L) | Setup Time, HIGH or LOW, A <sub>n</sub> ,B <sub>n</sub> to CPA, CPB     | 2.5  | _             | 2.5  | _     | 2.5           | _    | 2.5  | _     | 2.5           | _    | 2.5   | _    | ns    | 4    |

| t <sub>h</sub> (H)<br>t <sub>h</sub> (L) | Hold Time, HIGH<br>or LOW, A <sub>n</sub> B <sub>n</sub> to<br>CPA, CPB | 2.0  | _             | 2.0  | _     | 1.5           | _    | 1.5  | _     | 1.5           | _    | 1.5   | _    | ns    | 4    |

| t <sub>s</sub> (H)<br>t <sub>s</sub> (L) | Set-up Time, HIGH or LOW, CEA, CEB to CPA, CPB                          | 3.0  |               | 3.0  | _     | 3.0           | _    | 3.0  | _     | 3.0           | _    | 3.0   | _    | ns    | 4    |

| t <sub>h</sub> (H)<br>t <sub>h</sub> (L) | Hold Time, HIGH or LOW, CEA, CEB to CPA, CPB                            | 2.0  | _             | 2.0  | ı     | 2.0           | _    | 2.0  | 1     | 2.0           | -    | 2.0   | _    | ns    | 4    |

| t,,(H)<br>t,,(L)                         | Pulse Width, HIGH<br>or LOW, CPA or<br>CPB                              | 3.0  | _             | 3.0  | _     | 3.0           | -    | 3.0  | _     | 3.0           | _    | 3.0   | _    | ns    | 5    |

1. Minimum limits are guaranteed but not tested on Propagation Delays.

### 1806 Tbl 11

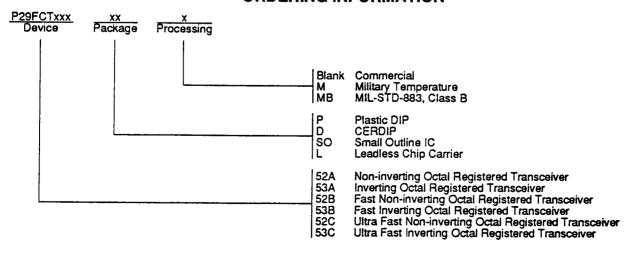

### ORDERING INFORMATION

1806 03