# 3.3 Volt Asynchronous x9 First-In/First-Out Queue

| Memory Configuration | Device |

|----------------------|--------|

| 8,192 x 9            | FQV05  |

| 4,096 x 9            | FQV04  |

| 2,048 x 9            | FQV03  |

| 1,024 x 9            | FQV02  |

| 512 x 9              | FQV01  |

# **Key Features:**

- Industry leading First-In/First-Out Queues (up to 50MHz)

- Independent Write and Read cycle time

- Asynchronous and simultaneous read and write

- 3.3V power supply

- Fully expandable in both word depth and width

- Retransmit capability

- Full, Empty, and Half Full flag indicators

- Available packages: 32-pin Plastic Lead Chip Carrier (PLCC)

- (0°C to 70°C) Commercial operating temperature available for access time of 15ns and above

- (-40°C to 85°C) Industrial operating temperature available for access time of 15ns and above

- Pin-to-pin compatible with IDT (72V01, 72V02, 72V03, 72V04, 72V05)

# **Product Description:**

HBA's FlexQ<sup>™</sup> Async FIFO offers industry leading 0.25um process technology and memory densities from 512 x 9 to 8,192 x 9. System designer has full flexibility of implementing deeper and wider queues using the depth and width expansion features. Full and Empty indicators allow easy handshaking between transmitters and receivers.

Independent Write and Read controls provide rate-matching capability. System designer can re-read data from the starting position by using Retransmit ( $\overline{\text{RET}}$ ). Retransmit allows reset of the read pointer to its initial position. Half Full flag ( $\overline{\text{HALF}}$ ) is available in the single device mode and width expansion mode, but not in depth expansion mode.

These FlexQ<sup>TM</sup> Async devices have low power consumption, hence minimizing system power requirements. In addition, industry standard 32 - pin PLCC are offered to save system board space.

These queues are ideal for applications such as data communication, telecommunication, graphics, multiprocessing, test equipment, medical systems, network switching, etc.

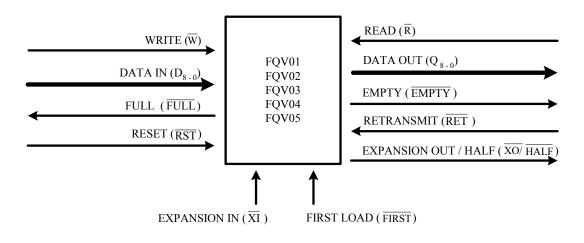

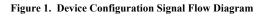

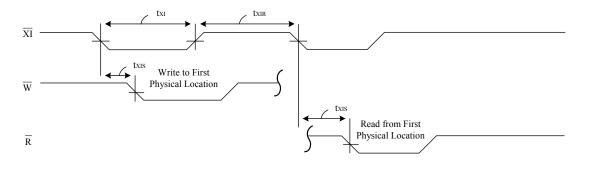

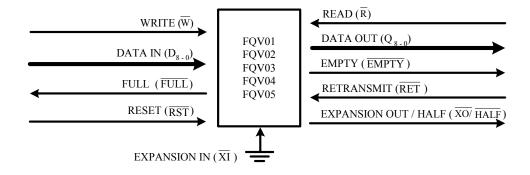

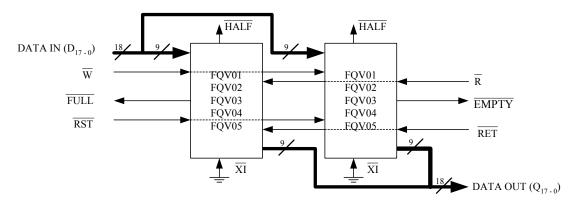

Block Diagram of Single Aynchronous Queue 8,192 x 9 / 4,096 x 9 / 2,048 x 9 / 1,024 x 9 / 512 x 9

Figure 2. Device Architecture

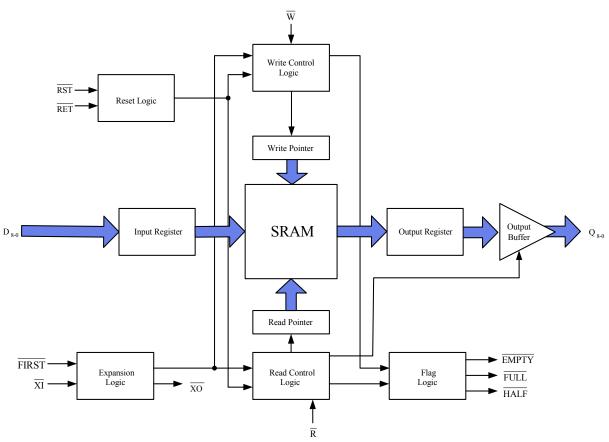

PLCC - 32 (Drw No: J-01A; Order code: J)

Top View

Figure 3. Device Pin-Out

| Pin #                                    | Symbol           | Name                              | Input/<br>Output | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------------------------------|------------------|-----------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 25                                       | RST              | Reset                             | Input            | Reset is required to initialize Write and Read pointers to the first position of the queue by setting $\overline{RST}$ low. $\overline{FULL}$ will go high; $\overline{EMPTY}$ will go low.                                                                                                                                                                                                                                                                       |

| 2                                        | W                | Write                             | Input            | Writes data into queue during low to high transitions of $\overline{W}$ if queue is not full yet.                                                                                                                                                                                                                                                                                                                                                                 |

| 3, 4, 5, 6,<br>7, 28, 29,<br>30, 31      | D <sub>8-0</sub> | Data Inputs                       | Input            | 9 - bit wide input data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 18                                       | R                | Read                              | Input            | Reads data from queue during high to low transitions of $\overline{R}$ if queue is not empty.                                                                                                                                                                                                                                                                                                                                                                     |

| 10, 11, 13,<br>14, 15, 19,<br>20, 21, 22 | Q <sub>8-0</sub> | Data Output                       | Output           | 9 - bit wide output data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 26                                       | FIRST /<br>RET   | First Load/<br>Retransmit         | Input            | $\overline{\text{FIRST}}$ / $\overline{\text{RET}}$ is used differently depending on mode. In<br>Depth Expansion Mode, the pin is grounded to indicate first<br>load. In Single Device Mode, the pin acts as retransmit.                                                                                                                                                                                                                                          |

| 8                                        | XI               | Expansion In                      | Input            | $\overline{XI}$ is used to indicate operations in different modes. When the pin is grounded, it indicates an operation in the Single Device Mode. When it is tied to Vcc, it indicates an operation in Depth Expansion Mode.                                                                                                                                                                                                                                      |

| 9                                        | FULL             | Full Flag                         | Output           | Queue is full when $\overline{\text{FULL}}$ goes low. This prohibits further writes into the queue. The assertion of $\overline{\text{FULL}}$ is synchronous to the falling edge of $\overline{\text{W}}$ and the deassertion is synchronous to the rising edge of $\overline{\text{R}}$ .                                                                                                                                                                        |

| 24                                       | EMPTY            | Empty Flag                        | Output           | Queue is empty when $\overline{\text{EMPTY}}$ goes low. This prohibits further reads from the queue. The assertion of $\overline{\text{EMPTY}}$ is synchronous to the falling edge of $\overline{\text{R}}$ and the deassertion is synchronous to the rising edge of $\overline{\text{W}}$ .                                                                                                                                                                      |

| 23                                       | XO /<br>HALF     | Expansion Out /<br>Half Full Flag | Output           | $\overline{\text{XO}} / \overline{\text{HALF}}$ is used differently depending on mode. In Depth<br>Expansion Mode, $\overline{\text{XI}}$ is connected to the previous device's $\overline{\text{XO}}$<br>pin. When the previous device has reached the last location of<br>memory, this pin will send pulses to the next device in the<br>Daisy Chain. In Single Device Mode, when $\overline{\text{XI}}$ is grounded,<br>this pin indicates queue is half-full. |

| 32                                       | Vcc              | Power                             | N/A              | 3.3V power supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 16                                       | GND              | Ground                            | N/A              | 0V Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1, 12, 17,<br>27                         | NC               | No Connection                     | N/A              | No connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

Table 1. Pin Descriptions

| Symbol | Rating                                  | Com'l & Ind'l | Unit |

|--------|-----------------------------------------|---------------|------|

| Vterm  | Terminal Voltage with<br>respect to GND | -0.5 to +7    | V    |

| Tstg   | Storage Temperature                     | -55 to +125   | °C   |

| Iout   | DC Output Current                       | -50 to +50    | mA   |

NOTES:

Absolute Max Ratings are for reference only. Permanent damage to the device may occur if extended period of operation is outside this range. Standard operation should fall within the Recommended Operating Conditions.

#### **Table 2. Absolute Maximum Ratings**

|                               |                                        |           | FQV05, F                               | QV04, FQ | V03, FQV | 02, FQV01                  | 1    |      |

|-------------------------------|----------------------------------------|-----------|----------------------------------------|----------|----------|----------------------------|------|------|

|                               |                                        | Commer    | cial t <sub>A</sub> = 15<br>35ns, 50ns |          | Industr  | ial tA = 15r<br>35ns, 50ns |      |      |

| Symbol                        | Parameter                              | Min.      | Тур.                                   | Max.     | Min.     | Тур.                       | Max. | Unit |

| Recommended O                 | perating Conditions                    |           |                                        | 1        |          | 1                          |      |      |

| Vcc                           | Supply Voltage Com'l/Ind'l             | 3.0       | 3.3                                    | 3.6      | 3.0      | 3.3                        | 3.6  | V    |

| GND                           | Supply Voltage                         | 0         | 0                                      | 0        | 0        | 0                          | 0    | V    |

| VIH                           | Input High Voltage<br>Com'l/Ind'l      | 2.0       | -                                      | -        | 2.0      | -                          | -    | V    |

| VIL                           | Input Low Voltage<br>Com'l/Ind'l       | -         | -                                      | 0.8      | -        | -                          | 0.8  | V    |

| Та                            | Operating Temperature<br>Commercial    | 0         | -                                      | 70       | 0        | -                          | 70   | °C   |

| Та                            | Operating Temperature<br>Industrial    | -40       | -                                      | 85       | -40      | -                          | 85   | °C   |

| DC Electrical Cha             | aracteristics                          |           |                                        |          |          |                            |      |      |

| ILI <sup>(1)</sup>            | Input Leakage Current (any input)      | -10       | -                                      | 10       | -10      | -                          | 10   | μΑ   |

| Ilo                           | Output Leakage Current                 | -10       | -                                      | 10       | -10      | -                          | 10   | μΑ   |

| Voh                           | Output Logic "1" Voltage,<br>IOH=-2mA  | 2.4       | -                                      | -        | 2.4      | -                          | -    | V    |

| Vol                           | Output Logic "0" Voltage,<br>IOL = 8mA | -         | -                                      | 0.4      | -        | -                          | 0.4  | V    |

| Power Consumpti               | ion                                    |           |                                        |          |          |                            |      |      |

| Icc1 <sup>(2,3,4)</sup>       | Active Power Supply<br>Current         | -         | -                                      | 50       | -        | -                          | 50   | mA   |

| $\operatorname{Icc2}^{(2,5)}$ | Standby Current                        | -         | -                                      | 5        | -        | -                          | 5    | mA   |

| Capacitance at 1.             | OMHz Ambient Temperature               | (25°C)    |                                        |          |          |                            |      |      |

| Symbol                        | Parameter                              |           | Con                                    | ditions  |          | Ν                          | lax. | Unit |

| CIN <sup>(6)</sup>            | Input Capacitance                      | VIN= 0V 8 |                                        | 8        | pF       |                            |      |      |

| Cout <sup>(6)</sup>           | Output Capacitance                     |           | Vot                                    | JT=0V    |          |                            | 8    | pF   |

#### NOTES:

1. Measurement with 0.4<=VIN<=Vcc

2. Tested with outputs open (IOUT=0)

3. Tested at f=20MHz

5. All inputs = Vcc-0.2V or GND+0.2V and ( $\overline{R}=\overline{W}=\overline{RST}=\overline{FIRST}/\overline{RET}=VIH$ )

6. Design simulated, not tested.

#### **Table 3. DC Specifications**

<sup>4.</sup> Typical Icc1=15+2\*fs+0.02\*CL\*fc (in mA) with Vcc=3.3V, tA=25°C, fs=WCLK frequency=RCLK frequency (in MHz, using TTL levels), data switching at fs/2, CL=Capacitive load (in PF)

|                 | Commercial & Industrial                          |                   |                                           |                   |                                           |                   |                                           |                   |                                           |      |

|-----------------|--------------------------------------------------|-------------------|-------------------------------------------|-------------------|-------------------------------------------|-------------------|-------------------------------------------|-------------------|-------------------------------------------|------|

|                 |                                                  | FQV<br>FQV<br>FQV | 04-15<br>03-15<br>02-15<br>01-15<br>05-15 | FQV<br>FQV<br>FQV | 05-25<br>04-25<br>03-25<br>02-25<br>01-25 | FQV<br>FQV<br>FQV | 05-35<br>04-35<br>03-35<br>02-35<br>01-35 | FQV<br>FQV<br>FQV | 05-50<br>04-50<br>03-50<br>02-50<br>01-50 |      |

| Symbol          | Parameter                                        | Min.              | Max                                       | Min.              | Max                                       | Min.              | Max                                       | Min.              | Max                                       | Unit |

| fs              | Shift Frequency                                  | -                 | 40                                        | -                 | 28.5                                      | -                 | 22.2                                      | -                 | 15                                        | MHz  |

| trc             | Read Cycle Time                                  | 25                | -                                         | 35                | -                                         | 45                | -                                         | 65                | -                                         | ns   |

| tA              | Access Time                                      | -                 | 15                                        | -                 | 25                                        | -                 | 35                                        | -                 | 50                                        | ns   |

| trr             | Read Recovery Time                               | 10                | -                                         | 10                | -                                         | 10                | -                                         | 15                | -                                         | ns   |

| trpw            | Read Pulse Width                                 | 15                | -                                         | 25                | -                                         | 35                | -                                         | 50                | -                                         | ns   |

| <b>t</b> rlz    | Read Pulse Low to Data Bus at Low Z $^{(1)}$     | 3                 | -                                         | 3                 | -                                         | 3                 | -                                         | 3                 | -                                         | ns   |

| twlz            | Write Pulse High to Data Bus at Low Z $^{(1,2)}$ | 5                 | -                                         | 5                 | -                                         | 5                 | -                                         | 5                 | -                                         | ns   |

| tov             | Data Valid from Read Pulse High                  | 5                 | -                                         | 5                 | -                                         | 5                 | -                                         | 5                 | -                                         | ns   |

| <b>t</b> rhz    | Read Pulse High to Data Bus at High Z $^{(1)}$   | -                 | 15                                        | -                 | 18                                        | -                 | 20                                        | -                 | 30                                        | ns   |

| twc             | Write Cycle Time                                 | 25                | -                                         | 35                | -                                         | 45                | -                                         | 65                | -                                         | ns   |

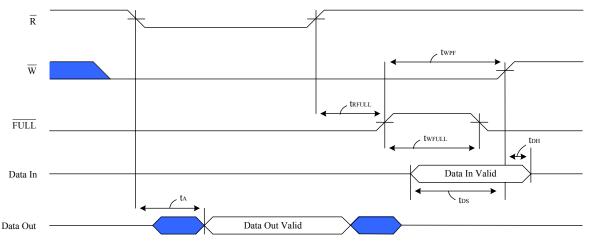

| twpw            | Write Pulse Width                                | 15                | -                                         | 25                | -                                         | 35                | -                                         | 50                | -                                         | ns   |

| twr             | Write Recovery Time                              | 10                | -                                         | 10                | -                                         | 10                | -                                         | 15                | -                                         | ns   |

| tos             | Data Set-up Time                                 | 11                | -                                         | 15                | -                                         | 18                | -                                         | 30                | -                                         | ns   |

| tdн             | Data Hold Time                                   | 0                 | -                                         | 0                 | -                                         | 0                 | -                                         | 5                 | -                                         | ns   |

| <b>t</b> rstc   | Reset Cycle Time                                 | 25                | -                                         | 35                | -                                         | 45                | -                                         | 65                | -                                         | ns   |

| trst            | Reset Pulse Width                                | 15                | -                                         | 25                | -                                         | 35                | -                                         | 50                | -                                         | ns   |

| trsts           | Reset Set-up Time <sup>(1)</sup>                 | 15                | -                                         | 25                | -                                         | 35                | -                                         | 50                | -                                         | ns   |

| trstr           | Reset Recovery Time                              | 10                | -                                         | 10                | -                                         | 10                | -                                         | 15                | -                                         | ns   |

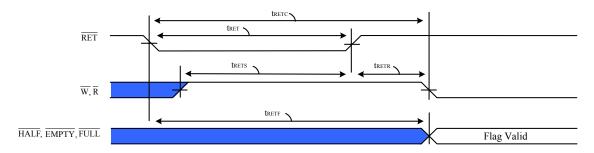

| <b>t</b> retc   | Retransmit Cycle Time                            | 25                | -                                         | 35                | -                                         | 45                | -                                         | 65                | -                                         | ns   |

| <b>t</b> ret    | Retransmit Pulse Width                           | 15                | -                                         | 25                | -                                         | 35                | -                                         | 50                | -                                         | ns   |

| <b>t</b> rets   | Retransmit Set-up Time <sup>(1)</sup>            | 15                | -                                         | 25                | -                                         | 35                | -                                         | 50                | -                                         | ns   |

| <b>t</b> retr   | Retransmit Recovery Time                         | 10                | -                                         | 10                | -                                         | 10                | -                                         | 15                | -                                         | ns   |

| tefl            | Reset to Empty Flag Low                          | -                 | 25                                        | -                 | 35                                        | -                 | 45                                        | -                 | 65                                        | ns   |

| thfh, tffh      | Reset to Half-Full and Full Flag High            | -                 | 25                                        | -                 | 35                                        | -                 | 45                                        | -                 | 65                                        | ns   |

| <b>t</b> retf   | Retransmit Low to Flags Valid                    | -                 | 25                                        | -                 | 35                                        | -                 | 45                                        | -                 | 65                                        | ns   |

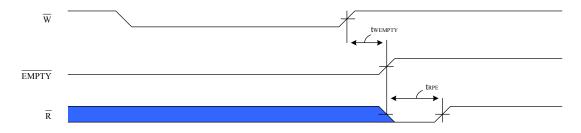

| <b>t</b> rempty | Read Low to Empty Flag Low                       | -                 | 15                                        | -                 | 25                                        | -                 | 30                                        | -                 | 45                                        | ns   |

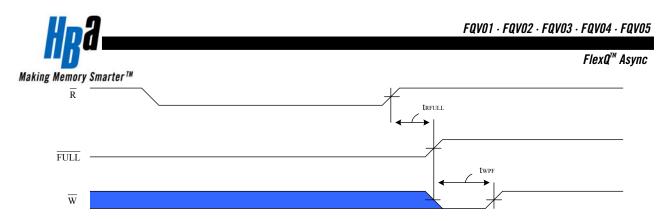

| <b>t</b> rfull  | Read High to Full Flag High                      | -                 | 15                                        | -                 | 25                                        | -                 | 30                                        | -                 | 45                                        | ns   |

| <b>t</b> rpe    | Read Pulse Width after Empty Flag High           | 15                | -                                         | 25                | -                                         | 35                | -                                         | 50                | -                                         | ns   |

| twempty         | Write High to Empty Flag High                    | -                 | 15                                        | -                 | 25                                        | -                 | 30                                        | -                 | 45                                        | ns   |

| twfull          | Write Low to Full Flag Low                       | -                 | 15                                        | -                 | 25                                        | -                 | 30                                        | -                 | 45                                        | ns   |

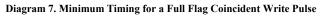

| twhalf          | Write Low to Half-Full Flag Low                  | -                 | 25                                        | -                 | 35                                        | -                 | 45                                        | -                 | 65                                        | ns   |

| trhalf          | Read High to Half-Full Flag High                 | -                 | 25                                        | -                 | 35                                        | -                 | 45                                        | -                 | 65                                        | ns   |

| twpf            | Write Pulse Width after Full Flag High           | 15                | -                                         | 25                | -                                         | 35                | -                                         | 50                | -                                         | ns   |

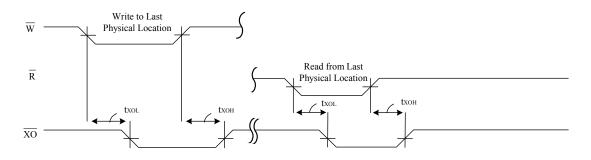

| txol            | Read/Write to XO Low                             | -                 | 15                                        | -                 | 25                                        | -                 | 35                                        | -                 | 50                                        | ns   |

| tхон            | Read/Write to XO High                            | -                 | 15                                        | -                 | 25                                        | -                 | 35                                        | -                 | 50                                        | ns   |

| txı             | XI Pulse Width                                   | 15                | -                                         | 25                | -                                         | 35                | -                                         | 50                | -                                         | ns   |

| txir            | XI Recovery Time                                 | 10                | -                                         | 10                | -                                         | 10                | -                                         | 10                | -                                         | ns   |

| txis            | XT Set-up Time                                   | 10                | -                                         | 10                | -                                         | 10                | -                                         | 15                | -                                         | ns   |

|                 | AT bet-up Time                                   | -                 |                                           | -                 | 1                                         | -                 | 1                                         | -                 | 1                                         |      |

NOTES:

Design simulated, not tested. Only applies to read data flow-through mode. 1. 2.

#### **Table 4. AC Electrical Characteristics**

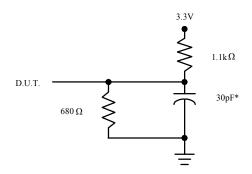

NOTES: 3FA09B

| Input Pulse Levels            | GND to 3.0V       |

|-------------------------------|-------------------|

| Input Rise/Fall Times         | 5ns               |

| Input Timing Reference Levels | 1.5V              |

| Output Reference Levels       | 1.5V              |

| Output Load                   | Refer to Figure 4 |

| Table | 5. | AC | Test | Con | dition |

|-------|----|----|------|-----|--------|

|-------|----|----|------|-----|--------|

**Figure 4. Output Load** \*Includes jig and scope capacitances.

# **Timing Diagrams**

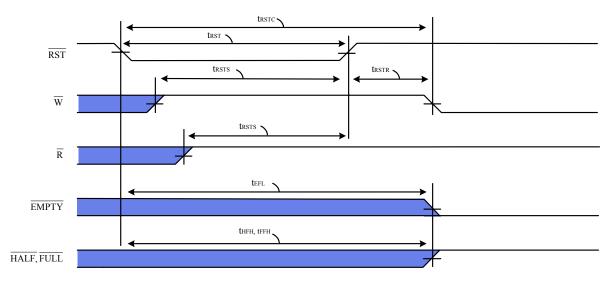

#### NOTES:

- 1. EMPTY, FULL, and HALF may change status during Reset, but are valid at tRSTC.

- 2.  $\overline{W}$  and  $\overline{R} = VIH$  near rising edge of  $\overline{RST}$ .

Diagram 1. Reset Timing

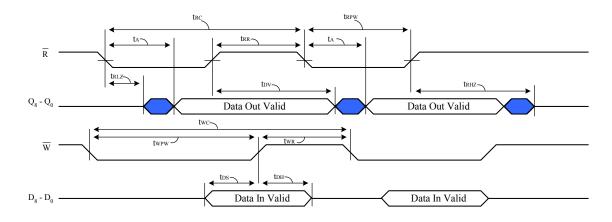

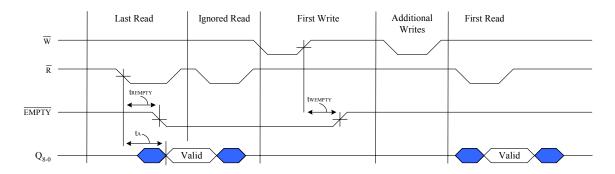

Diagram 2. Asynchronous Write and Read Operation

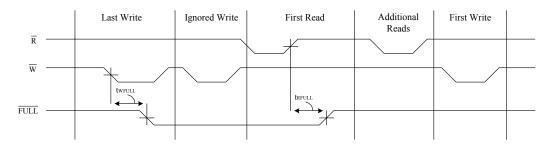

Diagram 3. Full Flag From Last Write to First Read

Diagram 4. Empty Flag From Last Read to First Write

#### Diagram 5. Retransmit

Diagram 9. Expansion Out

Diagram 10. Expansion In

**Operating Modes**

# **Single Device Mode:** When application requirements are for 256/512/1,024/2,048/4,096/8,192 words or less, a single device may be used. These devices are in Single Device Mode when Expansion In ( $\overline{XI}$ ) is grounded.

Figure 5. Single Device Mode

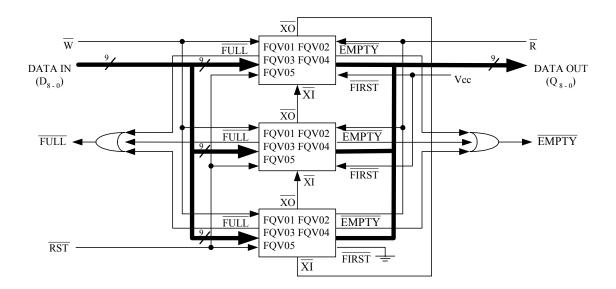

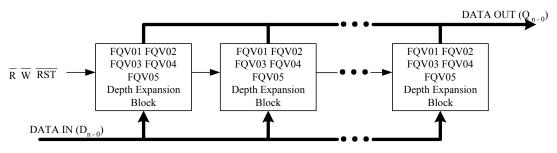

**Depth Expansion Mode:** When application requirements are greater than 256/512/1,024/2,048/4,096/8,192 words, multiple devices may be used for Depth Expansion. These devices are in Depth Expansion Mode when the following conditions are met:

- 1. The first device's First Load (FIRST) pin must be grounded.

- 2. All other devices' First Load (FIRST) pin must be tied to HIGH

- 3. All devices' Expansion Out  $(\overline{XO})$  pin must be tied to the next devices' Expansion In  $(\overline{XI})$  pin.

- 4. Retransmit (RET) and Half-Full Flag (HALF) are non-functional in Depth Expansion Mode.

- 5. An external logic is required to generate a composite Full Flag (FULL) and Empty Flag (EMPTY). This requires the ORing of all Empty and Full Flags.

Figure 6. Depth Expansion Mode

# **Usage Modes**

**Width Expansion Mode:** When applications require increased word width, multiple devices may be used for Width Expansion Mode. These devices are in Width Expansion Mode when the same signals from multiple devices are connected. Any word width may be achieved by connecting additional devices. Status flags are functional for any one device.

Figure 7. Width Expansion Mode

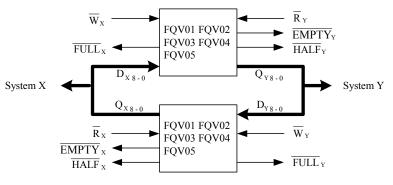

**Bidirectional Mode:** When applications require data buffering between two systems that are capable of Read and Write operations, a pair of devices may be used for Bidirectional Mode. Both Depth Expansion and Width Expansion may be used in this mode.

Figure 8. Bidirectional Mode

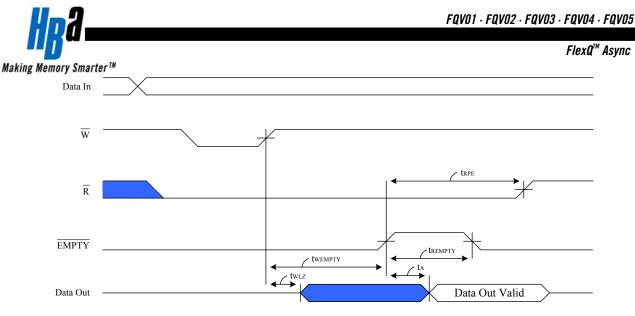

**Data Flow-Through Mode:** There are two types of flow-through modes, read flow-through and write flow-through. In the read flow-through mode, the device allows a single word to be read after one word of data has been written into an empty FIFO. The data is enabled on the bus after the rising edge of  $\overline{W}$ , and remains on the bus until  $\overline{R}$  goes from Low to High. Then the bus goes into a three-state mode. EMPTY will have a pulse showing temporary deassertion and then would be asserted. In the write flow-through mode, the device allows a single word to be written after one word of data has been read from a full FIFO.  $\overline{R}$  causes FULL to be deasserted but a Low  $\overline{W}$  causes it to be asserted again for the new data word. The new word goes into the FIFO on the rising edge of  $\overline{W}$ .  $\overline{W}$  must be toggled when FULL is not asserted to write new data into the FIFO and to increment the write pointer.

**Compound Expansion Mode:** Compound Expansion Mode is a combination of Depth and Width Expansion Modes to achieve large FIFO arrays.

Figure 9. Compound Expansion Mode

# **Order Information:**

| HBA<br>Device Family | Device Type           | Power    | Speed (ns)*        | Package** | Temperature Range                                    |

|----------------------|-----------------------|----------|--------------------|-----------|------------------------------------------------------|

| <u>XX</u>            | <u>XX</u>             | <u>X</u> | <u>XX</u>          | <u>X</u>  | <u>X</u>                                             |

| FQV                  | <b>05</b> (8,192 x 9) | Low      | 15 – 40 MHz        | J         | Blank – Commercial ( $0^{\circ}C$ to $70^{\circ}C$ ) |

|                      | <b>04</b> (4,096 x 9) |          | <b>25</b> – 29 MHz |           | I - Industrial (-40° to 85°C)                        |

|                      | <b>03</b> (2,048 x 9) |          | <b>35</b> – 22 MHz |           |                                                      |

|                      | <b>02</b> (1,024 x 9) |          | <b>50</b> – 15 MHz |           |                                                      |

|                      | <b>01</b> (512 x 9)   |          |                    |           |                                                      |

\*Speed – Slower speeds available upon request. \*\*Package – 32 - pin Plastic Lead Chip Carrier (PLCC)

#### **Example:**

| FQV05L15J   | (8k x 9, 15ns, PLCC, Commercial temp)  |

|-------------|----------------------------------------|

| FQV01L25PFI | (512 x 9, 25ns, PLCC, Industrial temp) |

#### USA

2107 North First Street, Suite 415 San Jose, CA 95131, USA www.hba.com

Tel: 408.453.8885 Fax: 408.453.8886

### Taiwan

No. 81, Suite 8F-9, Shui-Lee Rd. Hsinchu, Taiwan, R.O.C. www.hba.com

Tel: 886.3.516.9118 Fax: 886.3.516.9181

MAY 2003