### **Rochester Electronics Manufactured Components**

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All recreations are done with the approval of the OCM.

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceed the OCM data sheet.

## **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-35835

- Class Q Military

- Class V Space Level

- Qualified Suppliers List of Distributors (QSLD)

• Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OEM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

74F646 Octal Transceiver/Register with 3-STATE Outputs

# 74F646 Octal Transceiver/Register with 3-STATE Outputs

#### **General Description**

FAIRCHILD

SEMICONDUCTOR

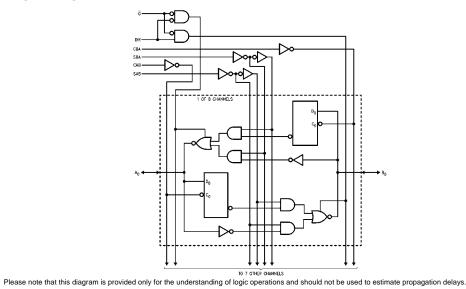

These devices consist of bus transceiver circuits with 3-STATE, D-type flip-flops, and control circuitry arranged for multiplexed transmission of data directly from the input bus or from the internal registers. Data on the A or B bus will be clocked into the registers as the appropriate clock pin goes to a high logic level. Control  $\overline{G}$  and direction pins are provided to control the transceiver function. In the transceiver mode, data present at the high impedance port may be stored in either the A or the B register or in both. The select controls can multiplex stored and real-time (transparent mode) data. The direction control determines which bus will receive data when the enable control  $\overline{G}$  is Active LOW. In the isolation mode (control  $\overline{G}$  HIGH), A data may be stored in the B register and/or B data may be stored in the A register.

#### Features

- Independent registers for A and B buses

- Multiplexed real-time and stored data

- 74F646 has non-inverting data paths

- 3-STATE outputs

- 300 mil slim DIP

#### **Ordering Code:**

| Order Number                                                                                              | Package Number | Package Description                                                        |  |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------|----------------|----------------------------------------------------------------------------|--|--|--|--|--|--|

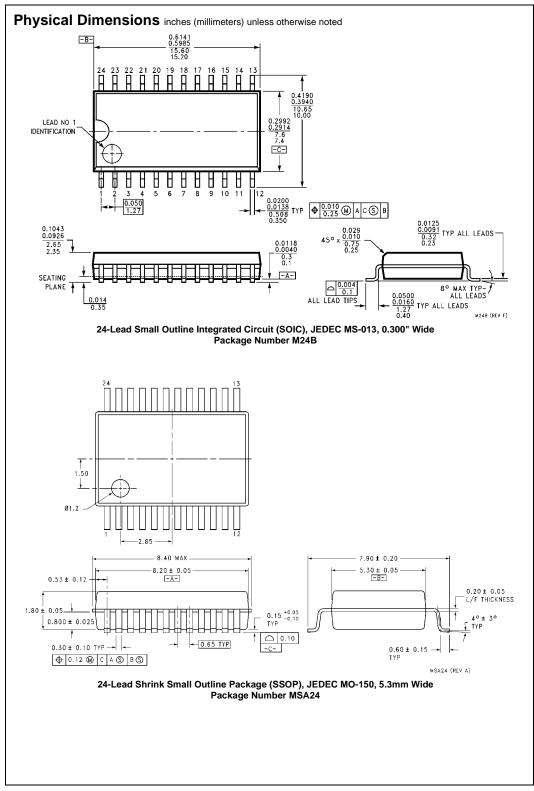

| 74F646SC                                                                                                  | M24B           | 24-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300" Wide |  |  |  |  |  |  |

| 74F646MSA                                                                                                 | MSA24          | 24-Lead Shrink Small Outline Package (SSOP), JEDEC MO-150, 5.3mm Wide      |  |  |  |  |  |  |

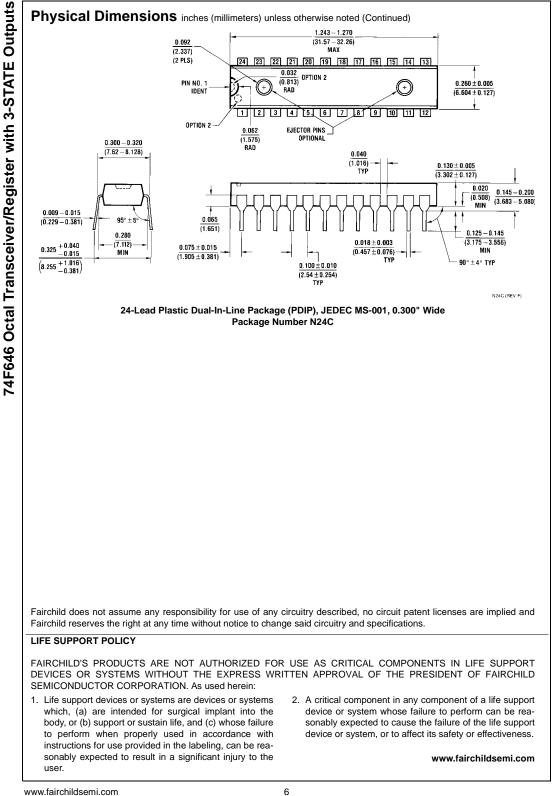

| 74F646SPC N24C 24-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide                     |                |                                                                            |  |  |  |  |  |  |

| Devices also available in Tape and Reel. Specify by appending the suffix letter "X" to the ordering code. |                |                                                                            |  |  |  |  |  |  |

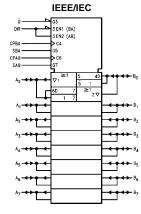

#### Logic Symbols

#### **Connection Diagram**

© 2004 Fairchild Semiconductor Corporation DS009580

www.fairchildsemi.com

# 74F646

#### Unit Loading/Fan Out

| Din Namas                      | Decemination            | U.L.           | Input I <sub>IH</sub> /I <sub>IL</sub>  |

|--------------------------------|-------------------------|----------------|-----------------------------------------|

| Pin Names                      | Description             | HIGH/LOW       | Output I <sub>OH</sub> /I <sub>OL</sub> |

| A <sub>0</sub> –A <sub>7</sub> | Data Register A Inputs/ | 3.5/1.083      | 70 μA/–650 μA                           |

|                                | 3-STATE Outputs         | 600/106.6 (80) | –12 mA/64 mA (48 mA)                    |

| B <sub>0</sub> –B <sub>7</sub> | Data Register B Inputs/ | 3.5/1.083      | 70 μA/–650 μA                           |

|                                | 3-STATE Outputs         | 600/106.6 (80) | –12 mA/64 mA (48 mA)                    |

| СРАВ, СРВА                     | Clock Pulse Inputs      | 1.0/1.0        | 20 µA/–0.6 mA                           |

| SAB, SBA                       | Select Inputs           | 1.0/1.0        | 20 µA/–0.6 mA                           |

| G                              | Output Enable Input     | 1.0/1.0        | 20 µA/–0.6 mA                           |

| DIR                            | Direction Control Input | 1.0/1.0        | 20 µA/–0.6 mA                           |

#### **Function Table**

|       |                                                                                        | Inp    | uts    |     |     | Data I/O                       | (Note 1)                       | Function                                                       |  |

|-------|----------------------------------------------------------------------------------------|--------|--------|-----|-----|--------------------------------|--------------------------------|----------------------------------------------------------------|--|

| G     | DIR                                                                                    | CPAB   | СРВА   | SAB | SBA | A <sub>0</sub> -A <sub>7</sub> | B <sub>0</sub> –B <sub>7</sub> | Function                                                       |  |

| Н     | Х                                                                                      | H or L | H or L | Х   | Х   |                                |                                | Isolation                                                      |  |

| н     | Х                                                                                      | ~      | Х      | Х   | Х   | Input                          | Input                          | Clock A <sub>n</sub> Data into A Register                      |  |

| Н     | Х                                                                                      | Х      | ~      | Х   | Х   |                                |                                | Clock B <sub>n</sub> Data into B Register                      |  |

| L     | Н                                                                                      | Х      | Х      | L   | Х   |                                |                                | A <sub>n</sub> to B <sub>n</sub> —Real Time (Transparent Mode) |  |

| L     | н                                                                                      | ~      | Х      | L   | Х   | Input                          | Output                         | Clock A <sub>n</sub> Data into A Register                      |  |

| L     | н                                                                                      | H or L | х      | н   | Х   |                                |                                | A Register to B <sub>n</sub> (Stored Mode)                     |  |

| L     | н                                                                                      | ~      | х      | н   | Х   |                                |                                | Clock An Data into A Register and Output to Bn                 |  |

| L     | L                                                                                      | Х      | Х      | Х   | L   |                                |                                | B <sub>n</sub> to A <sub>n</sub> —Real Time (Transparent Mode) |  |

| L     | L                                                                                      | Х      | ~      | Х   | L   | Output                         | Input                          | Clock B <sub>n</sub> Data into B Register                      |  |

| L     | L                                                                                      | Х      | H or L | Х   | н   |                                |                                | B Register to A <sub>n</sub> (Stored Mode)                     |  |

| L     | L                                                                                      | Х      | ~      | Х   | н   |                                |                                | Clock $B_n$ Data into B Register and Output to $A_n$           |  |

| H = H | H = HIGH Voltage Level L = LOW Voltage Level X = Irrelevant ~ = LOW-to-HIGH Transition |        |        |     |     |                                |                                |                                                                |  |

H = HIGH Voltage LevelL = LOW Voltage LevelX = Irrelevant $\sim$  = LOW-to-HIGH TransitionNote 1: The data output functions may be enabled or disabled by various signals at the  $\overline{G}$  and DIR Inputs. Data input functions are always enabled;<br/>i.e., data at the bus pins will be stored on every LOW-to-HIGH transition of the clock inputs.

#### Logic Diagram

www.fairchildsemi.com

#### Absolute Maximum Ratings(Note 2)

| Storage Temperature                         | $-65^{\circ}C$ to $+150^{\circ}C$    |

|---------------------------------------------|--------------------------------------|

| Ambient Temperature under Bias              | $-55^{\circ}C$ to $+125^{\circ}C$    |

| Junction Temperature under Bias             | -55°C to +150°C                      |

| V <sub>CC</sub> Pin Potential to Ground Pin | -0.5V to +7.0V                       |

| Input Voltage (Note 3)                      | -0.5V to +7.0V                       |

| Input Current (Note 3)                      | -30 mA to +5.0 mA                    |

| Voltage Applied to Output                   |                                      |

| in HIGH State (with $V_{CC} = 0V$ )         |                                      |

| Standard Output                             | –0.5V to V <sub>CC</sub>             |

| 3-STATE Output                              | -0.5V to +5.5V                       |

| Current Applied to Output                   |                                      |

| in LOW State (Max)                          | twice the rated I <sub>OL</sub> (mA) |

| ESD Last Passing Voltage (Min)              | 4000V                                |

|                                             |                                      |

# Recommended Operating Conditions

Free Air Ambient Temperature Supply Voltage 74F646

0°C to +70°C +4.5V to +5.5V

Note 2: Absolute maximum ratings are values beyond which the device may be damaged or have its useful life impaired. Functional operation under these conditions is not implied.

Note 3: Either voltage limit or current limit is sufficient to protect inputs.

#### **DC Electrical Characteristics**

| Symbol                             | Parameter                                  | Min  | Тур | Max  | Units | V <sub>cc</sub> | Conditions                                                  |

|------------------------------------|--------------------------------------------|------|-----|------|-------|-----------------|-------------------------------------------------------------|

| VIH                                | Input HIGH Voltage                         | 2.0  |     |      | V     |                 | Recognized as a HIGH Signal                                 |

| V <sub>IL</sub>                    | Input LOW Voltage                          |      |     | 0.8  | V     |                 | Recognized as a LOW Signal                                  |

| V <sub>CD</sub>                    | Input Clamp Diode Voltage                  |      |     | -1.2 | V     | Min             | I <sub>IN</sub> = -18 mA (Non I/O Pins)                     |

| V <sub>OH</sub>                    | Output HIGH 10% V <sub>CC</sub><br>Voltage | 2.0  |     |      | V     | Min             | I <sub>OH</sub> = -15 mA (A <sub>n</sub> , B <sub>n</sub> ) |

| V <sub>OL</sub>                    | Output LOW 10% V <sub>CC</sub><br>Voltage  |      |     | 0.55 | V     | Min             | $I_{OL} = 64 \text{ mA} (A_n, B_n)$                         |

| IIH                                | Input HIGH<br>Current                      |      |     | 5.0  | μΑ    | Max             | V <sub>IN</sub> = 2.7V (Non I/O Pins)                       |

| I <sub>BVI</sub>                   | Input HIGH Current<br>Breakdown Test       |      |     | 7.0  | μΑ    | Max             | V <sub>IN</sub> = 7.0V (Non I/O Pins)                       |

| I <sub>BVIT</sub>                  | Input HIGH Current<br>Breakdown (I/O)      |      |     | 0.5  | mA    | Max             | V <sub>IN</sub> = 5.5V (A <sub>n</sub> , B <sub>n</sub> )   |

| I <sub>CEX</sub>                   | Output HIGH<br>Leakage Current             |      |     | 50   | μA    | Max             | $V_{OUT} = V_{CC}$                                          |

| V <sub>ID</sub>                    | Input Leakage<br>Test                      | 4.75 |     |      | V     | 0.0             | I <sub>ID</sub> = 1.9 μA<br>All Other Pins Grounded         |

| I <sub>OD</sub>                    | Output Leakage<br>Circuit Current          |      |     | 3.75 | μΑ    | 0.0             | V <sub>IOD</sub> = 150 mV<br>All Other Pins Grounded        |

| IIL                                | Input LOW Current                          |      |     | -0.6 | mA    | Max             | V <sub>IN</sub> = 0.5V (Non I/O Pins)                       |

| I <sub>IH</sub> + I <sub>OZH</sub> | Output Leakage Current                     |      |     | 70   | μΑ    | Max             | $V_{OUT} = 2.7V (A_n, B_n)$                                 |

| $I_{IL} + I_{OZL}$                 | Output Leakage Current                     |      |     | -650 | μΑ    | Max             | $V_{OUT} = 0.5V (A_n, B_n)$                                 |

| I <sub>OS</sub>                    | Output Short-Circuit Current               | -100 |     | -225 | mA    | Max             | $V_{OUT} = 0V$                                              |

| I <sub>ZZ</sub>                    | Bus Drainage Test                          |      |     | 500  | μΑ    | 0.0V            | $V_{OUT} = 5.25V$                                           |

| ICCH                               | Power Supply Current                       |      |     | 135  | mA    | Max             | V <sub>O</sub> = HIGH                                       |

| I <sub>CCL</sub>                   | Power Supply Current                       |      |     | 150  | mA    | Max             | V <sub>O</sub> = LOW                                        |

| I <sub>CCZ</sub>                   | Power Supply Current                       |      |     | 150  | mA    | Max             | V <sub>O</sub> = HIGH Z                                     |

74F646

#### **AC Electrical Characteristics**

| Symbol           |                         |                         | +25°C         | $T_A = -55^{\circ}C \text{ to } +125^{\circ}C$ |       | $T_A = 0^{\circ}C$ to $+70^{\circ}C$ |       |     |  |

|------------------|-------------------------|-------------------------|---------------|------------------------------------------------|-------|--------------------------------------|-------|-----|--|

|                  | Parameter               | V <sub>CC</sub> =       | + <b>5.0V</b> | V <sub>CC</sub> =                              | +5.0V | V <sub>CC</sub> =                    | Units |     |  |

|                  | i arameter              | <b>C</b> <sub>L</sub> = | 50 pF         | <b>C</b> <sub>L</sub> =                        | 50 pF | $C_L = 50 \ pF$                      |       |     |  |

|                  |                         | Min                     | Max           | Min                                            | Max   | Min                                  | Max   |     |  |

| f <sub>MAX</sub> | Maximum Clock Frequency | 90                      |               | 75                                             |       | 90                                   |       | MHz |  |

| t <sub>PLH</sub> | Propagation Delay       | 2.0                     | 7.0           | 2.0                                            | 8.5   | 2.0                                  | 8.0   |     |  |

| t <sub>PHL</sub> | Clock to Bus            | 2.0                     | 8.0           | 2.0                                            | 9.5   | 2.0                                  | 9.0   | ns  |  |

| t <sub>PLH</sub> | Propagation Delay       | 1.0                     | 7.0           | 1.0                                            | 8.0   | 1.0                                  | 7.5   | ns  |  |

| t <sub>PHL</sub> | Bus to Bus              | 1.0                     | 6.5           | 1.0                                            | 8.0   | 1.0                                  | 7.0   | 115 |  |

| t <sub>PLH</sub> | Propagation Delay       | 2.0                     | 8.5           | 2.0                                            | 11.0  | 2.0                                  | 9.5   | 200 |  |

| t <sub>PHL</sub> | SBA or SAB to A or B    | 2.0                     | 8.0           | 2.0                                            | 10.0  | 2.0                                  | 9.0   | ns  |  |

| t <sub>PZH</sub> | Enable Time             | 2.0                     | 8.5           | 2.0                                            | 10.0  | 2.0                                  | 9.0   | ns  |  |

| t <sub>PZL</sub> | OE to A or B            | 2.0                     | 12.0          | 2.0                                            | 13.5  | 2.0                                  | 12.5  | 115 |  |

| t <sub>PHZ</sub> | Disable Time            | 1.0                     | 7.5           | 1.0                                            | 9.0   | 1.0                                  | 8.5   | ns  |  |

| t <sub>PLZ</sub> | OE to A or B            | 2.0                     | 9.0           | 2.0                                            | 11.0  | 2.0                                  | 9.5   | 115 |  |

| t <sub>PZH</sub> | Enable Time             | 2.0                     | 14.0          | 2.0                                            | 16.0  | 2.0                                  | 15.0  | ns  |  |

| t <sub>PZL</sub> | DIR to A or B           | 2.0                     | 13.0          | 2.0                                            | 15.0  | 2.0                                  | 14.0  | 115 |  |

| t <sub>PHZ</sub> | Disable Time            | 1.0                     | 9.0           | 1.0                                            | 10.0  | 1.0                                  | 9.5   | ns  |  |

| t <sub>PLZ</sub> | DIR to A or B           | 2.0                     | 11.0          | 2.0                                            | 12.0  | 2.0                                  | 11.5  | ns  |  |

# AC Operating Requirements

|                    |                         | $T_{A} = +25^{\circ}C$<br>$V_{CC} = +5.0V$ |     | $T_A = -55^{\circ}C$ | c to +125°C | $T_A = 0^{\circ}C$ to $+70^{\circ}C$ |     |       |  |

|--------------------|-------------------------|--------------------------------------------|-----|----------------------|-------------|--------------------------------------|-----|-------|--|

| Symbol             | Parameter               |                                            |     | $V_{CC} = +5.0V$     |             | $V_{CC} = +5.0V$                     |     | Units |  |

|                    |                         | Min                                        | Max | Min                  | Max         | Min                                  | Max |       |  |

| t <sub>S</sub> (H) | Setup Time, HIGH or LOW | 5.0                                        |     | 5.0                  |             | 5.0                                  |     |       |  |

| t <sub>S</sub> (L) | Bus to Clock            | 5.0                                        |     | 5.0                  |             | 5.0                                  |     | ns    |  |

| t <sub>H</sub> (H) | Hold Time, HIGH or LOW  | 2.0                                        |     | 2.5                  |             | 2.0                                  |     | ns    |  |

| t <sub>H</sub> (L) | Bus to Clock            | 2.0                                        |     | 2.5                  |             | 2.0                                  |     | 115   |  |

| t <sub>W</sub> (H) | Clock Pulse Width       | 5.0                                        |     | 5.0                  |             | 5.0                                  |     | ns    |  |

| t <sub>W</sub> (L) | HIGH or LOW             | 5.0                                        |     | 5.0                  |             | 5.0                                  |     | 115   |  |

www.fairchildsemi.com

74F646