Burr-Brown Products from Texas Instruments

SBAS001A - OCTOBER 1989 - REVISED FEBRUARY 2004

ADS7800

# **12-Bit 3μs Sampling ANALOG-TO-DIGITAL CONVERTER**

### **FEATURES**

- 333k SAMPLES PER SECOND

- STANDARD ±10V AND ±5V INPUT RANGES

- DC PERFORMANCE OVER TEMP: No Missing Codes 1/2LSB Integral Linearity Error 3/4LSB Differential Linearity Error

- AC PERFORMANCE OVER TEMP: 72dB Signal-to-Noise Ratio 80dB Spurious-Free Dynamic Range –80dB Total Harmonic Distortion

- INTERNAL SAMPLE/HOLD, REFERENCE, CLOCK, AND THREE-STATE OUTPUTS

- POWER DISSIPATION: 215mW max

- PACKAGE: 24-Pin Single-Wide DIP 24-Lead SOIC

## DESCRIPTION

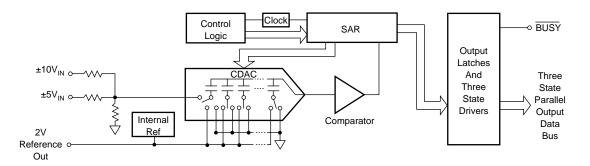

The ADS7800 is a complete 12-bit sampling analog-todigital (A/D) converter using state-of-the-art CMOS structures. It contains a complete 12-bit successive approximation A/D converter with internal sample/hold, reference, clock, digital interface for microprocessor control, and three-state output drivers.

The ADS7800 is specified at a 333kHz sampling rate. Conversion time is factory set for 2.70 $\mu$ s max over temperature, and the high-speed sampling input stage insures a total acquisition and conversion time of 3 $\mu$ s max over temperature. Precision, laser-trimmed scaling resistors provide industry-standard input ranges of  $\pm$ 5V or  $\pm$ 10V.

AC and DC performance are completely specified. Two grades based on linearity and dynamic performance are available to provide the optimum price/performance fit in a wide range of applications.

The 24-pin ADS7800 is available in plastic and sidebraze hermetic 0.3" wide DIPs, and in an SOIC package. It operates from a +5V supply and either a -12V or -15Vsupply. The ADS7800 is available in grades specified over 0°C to +70°C and -40°C to +85°C temperature ranges.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

All trademarks are the property of their respective owners.

# SPECIFICATIONS

### ELECTRICAL

At T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, Sampling Frequency, f<sub>S</sub> = 333kHz, -V<sub>S</sub> = -15V, V<sub>S</sub> = +5V, unless otherwise specified.

|                                                                                                                                                                                                                                           |                                                                                                                                                                                                 | ADS                      | 67800JP/JU/A            | н                               | ADS         | 7800KP/KU/B       | H                           |                                                           |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-------------------------|---------------------------------|-------------|-------------------|-----------------------------|-----------------------------------------------------------|--|

| PARAMETER                                                                                                                                                                                                                                 | CONDITIONS                                                                                                                                                                                      | MIN                      | TYP                     | МАХ                             | MIN         | TYP               | МАХ                         | UNITS                                                     |  |

| RESOLUTION                                                                                                                                                                                                                                |                                                                                                                                                                                                 |                          |                         | 12                              |             |                   | *                           | Bits                                                      |  |

| ANALOG INPUT<br>Voltage Ranges<br>Impedance                                                                                                                                                                                               | ±10V Range<br>±5V Range                                                                                                                                                                         | 4.4<br>2.9               | ±10V/±5V<br>6.3<br>4.2  | 8.1<br>5.4                      | *           | *<br>*<br>*       | *                           | V<br>kΩ<br>kΩ                                             |  |

| THROUGHPUT SPEED<br>Conversion Time<br>Complete Cycle<br>Throughput Rate                                                                                                                                                                  | Conversion Alone<br>Acquisition + Conversion                                                                                                                                                    | 333                      | 2.5<br>2.6<br>380       | 2.7<br>3.0                      | *           | * *               | *                           | μs<br>μs<br>kHz                                           |  |

| DC ACCURACY<br>Full Scale Error <sup>(1)</sup><br>Full Scale Error Drift<br>Integral Linearity Error<br>Differential Linearity Error<br>No Missing Codes<br>Bipolar Zero <sup>(1)</sup><br>Bipolar Zero Drift<br>Power Supply Sensitivity |                                                                                                                                                                                                 |                          | 6<br>Ensured<br>1       | ±0.50<br>±1<br>±1<br>±4         |             | *<br>Ensured<br>* | ±0.35<br>±1/2<br>±3/4<br>±2 | %<br>ppm/°C<br>LSB <sup>(2)</sup><br>LSB<br>LSB<br>ppm/°C |  |

| Transition Noise <sup>(3)</sup>                                                                                                                                                                                                           | $\begin{array}{l} -16.5 \mathrm{V} < -\mathrm{V_S} < -13.5 \mathrm{V} \\ -12.6 \mathrm{V} < -\mathrm{V_S} < -11.4 \mathrm{V} \\ +4.75 \mathrm{V} < \mathrm{V_S} < +5.25 \mathrm{V} \end{array}$ |                          | 0.1                     | ±1/2<br>±1/2<br>±1              |             | *                 | *<br>*<br>±1/2              | LSB<br>LSB<br>LSB<br>LSB                                  |  |

| AC ACCURACY<br>Spurious-Free Dynamic Range<br>Total Harmonic Distortion<br>Two-tone Intermodulation Distortion                                                                                                                            | $\begin{array}{l} f_{IN} = 47 kHz \\ f_{IN} = 47 kHz \\ f_{IN1} = 24.4 kHz \ (-6 dB) \\ f_{IN2} = 28.5 kHz \ (-6 dB) \end{array}$                                                               | 74                       | 77<br>-77<br>-77        | 74<br>74                        | 77          | 80<br>80<br>80    | -77<br>-77                  | dB <sup>(4)</sup><br>dB<br>dB                             |  |

| Signal-to-(Noise + Distortion) Ratio<br>Signal-to-Noise Ratio (SNR)                                                                                                                                                                       | $f_{IN2} = 200 \text{ M/L}^2 (0000)$<br>$f_{IN} = 47 \text{ kHz}$<br>$f_{IN} = 47 \text{ kHz}$                                                                                                  | 67<br>68                 | 70<br>71                |                                 | 69<br>70    | 72<br>73          |                             | dB<br>dB                                                  |  |

| SAMPLING DYNAMICS<br>Aperture Delay<br>Aperture Jitter<br>Transient Response <sup>(5)</sup><br>Overvoltage Recovery <sup>(6)</sup>                                                                                                        |                                                                                                                                                                                                 |                          | 13<br>150<br>130<br>150 |                                 |             | *<br>*<br>*       |                             | ns<br>ps, rms<br>ns<br>ns                                 |  |

| INTERNAL REFERENCE VOLTAGE<br>Voltage<br>Source Current Available<br>for External Loads                                                                                                                                                   |                                                                                                                                                                                                 | 1.9                      | 2.0<br>10               | 2.1                             | *           | *                 | *                           | ν<br>μΑ                                                   |  |

| DIGITAL INPUTS<br>Logic Levels<br>V <sub>IL</sub><br>V <sub>IH</sub><br>I <sub>IL</sub><br>I <sub>IL</sub>                                                                                                                                |                                                                                                                                                                                                 | -0.3<br>+2.4<br>-5<br>+5 |                         | +0.8<br>+5.3                    | *<br>*<br>* |                   | *                           | V<br>V<br>μΑ<br>μΑ                                        |  |

| DIGITAL OUTPUTS<br>Data Format<br>Data Coding                                                                                                                                                                                             |                                                                                                                                                                                                 |                          | F                       | Parallel, 12-bit<br>Binary Offs |             | t                 |                             |                                                           |  |

| V <sub>OL</sub><br>V <sub>OH</sub><br>I <sub>LEAKAGE</sub> (High-Z State)                                                                                                                                                                 | I <sub>SINK</sub> = 1.6mA<br>I <sub>SOURCE</sub> = 500μA                                                                                                                                        | 0.0<br>+2.4              | ±0.1                    | +0.4<br>+5.0<br>±5              | *           | *                 | *<br>*                      | V<br>V<br>μA                                              |  |

| POWER SUPPLIES<br>Rated Voltage<br>$-V_S$<br>$V_S (V_{SA} and V_{SD})$<br>Current                                                                                                                                                         |                                                                                                                                                                                                 | -11.4<br>+4.75           | -15<br>+5.0             | -16.5<br>+5.25                  | *           | *                 | *                           | V<br>V                                                    |  |

| -I <sub>S</sub><br>I <sub>S</sub><br>Power Consumption                                                                                                                                                                                    |                                                                                                                                                                                                 |                          | 3.5<br>18<br>135        | 6<br>25<br>215                  |             | * * *             | *<br>*<br>*                 | mA<br>mA<br>mW                                            |  |

# **SPECIFICATIONS** (CONT)

#### ELECTRICAL

At  $T_A = T_{MIN}$  to  $T_{MAX}$ , Sampling Frequency,  $f_S$ , = 333kHz,  $-V_S = -15V$ ,  $V_S = +5V$ , unless otherwise specified.

|                   |             | ADS | 7800JP/JU/A | Н    | ADS |     |     |       |

|-------------------|-------------|-----|-------------|------|-----|-----|-----|-------|

| PARAMETER         | CONDITIONS  | MIN | ТҮР         | MAX  | MIN | ТҮР | MAX | UNITS |

| TEMPERATURE RANGE |             |     |             |      |     |     |     |       |

| Specification     | JP/JU/KP/KU | 0   |             | +70  | *   |     | *   | °C    |

|                   | AH/BH       | -40 |             | +85  | *   |     | *   | °C    |

| Operating         | JP/KP/JU/KU | -40 |             | +85  | *   |     | *   | °C    |

| Storage           |             | -65 |             | +150 | *   |     | *   | °C    |

\* Same as specification for ADS7800JP/JU/AH.

NOTES: (1) Adjustable to zero with external potentiometer. (2) LSB means Least Significant Bit. For ADS7800, 1LSB = 2.44mV for the  $\pm 5V$  range, 1LSB = 4.88mV for the  $\pm 10V$  range. (3) Noise was characterized over temperature near full scale, 0V, and negative full scale. 0.1LSB represents a typical rms level of noise at the worst case, which was near full scale input at +125°C. (4) All specifications in dB are referred to a full-scale input, either  $\pm 10V$  or  $\pm 5V$ . (5) For full scale step input, 12-bit accuracy attained in specified time. (6) Recovers to specified performance in specified time after 2 x F<sub>S</sub> input overvoltage.

#### **ABSOLUTE MAXIMUM RATINGS**

| $eq:started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_st$ | $\begin{array}{c} +7V\\ \pm 0.3V\\ \pm 1V\\ \dots -0.3 \text{ to } V_{\text{S}} + 0.3V\\ \dots \pm 20V\\ 160^{\circ}\text{C}\\ \dots \\ 750\text{mW}\\ +300^{\circ}\text{C}\\ \dots \\ 100^{\circ}\text{C/W}\\ \end{array}$ |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                             |

| Ceramic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 50°C/W                                                                                                                                                                                                                      |

#### PACKAGE/ORDERING INFORMATION

For the most current package and ordering information, see the Package Option Addendum located at the end of this data sheet.

## ELECTROSTATIC DISCHARGE SENSITIVITY

The ADS7800 is an ESD (electrostatic discharge) sensitive device. The digital control inputs have a special FET structure, which turns on when the input exceeds the supply by 18V, to minimize ESD damage. However, permanent damage may occur on unconnected devices subject to high energy electrostatic fields. When not in use, devices must be stored in conductive foam or shunts. The protective foam should be discharged to the destination socket before devices are removed.

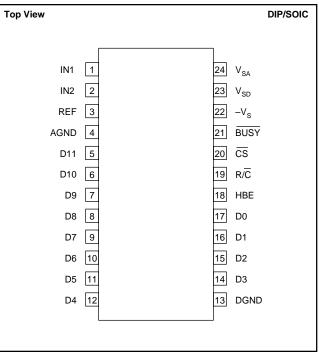

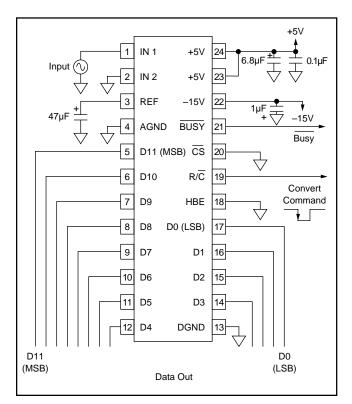

#### **PIN ASSIGNMENTS**

| PIN # | NAME     | DESCRIPTION                                                                                                                                                                                 |

|-------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | IN1      | $\pm 10V$ Analog Input. Connected to GND for $\pm 5V$ range.                                                                                                                                |

| 2     | IN2      | $\pm 5 \text{V}$ Analog Input. Connected to GND for $\pm 10 \text{V}$ range.                                                                                                                |

| 3     | REF      | +2V Reference Output. Bypass to GND with 22 $\mu$ F to 47 $\mu$ F Tantalum. Buffer for external loads.                                                                                      |

| 4     | AGND     | Analog Ground. Connect to pin 13.                                                                                                                                                           |

| 5     | D11      | Data Bit 11. Most Significant Bit (MSB).                                                                                                                                                    |

| 6     | D10      | Data Bit 10.                                                                                                                                                                                |

| 7     | D9       | Data Bit 9.                                                                                                                                                                                 |

| 8     | D8       | Data Bit 8.                                                                                                                                                                                 |

| 9     | D7       | Data Bit 7 if HBE is LOW; LOW if HBE is HIGH.                                                                                                                                               |

| 10    | D6       | Data Bit 6 if HBE is LOW; LOW if HBE is HIGH.                                                                                                                                               |

| 11    | D5       | Data Bit 5 if HBE is LOW; LOW if HBE is HIGH.                                                                                                                                               |

| 12    | D4       | Data Bit 4 if HBE is LOW; LOW if HBE is HIGH.                                                                                                                                               |

| 13    | DGND     | Digital Ground. Connect to pin 4.                                                                                                                                                           |

| 14    | D3       | Data Bit 3 if HBE is LOW; Data Bit 11 if HBE is HIGH.                                                                                                                                       |

| 15    | D2       | Data Bit 2 if HBE is LOW; Data Bit 10 if HBE is HIGH.                                                                                                                                       |

| 16    | D1       | Data Bit 1 if HBE is LOW; Data Bit 9 if HBE is HIGH.                                                                                                                                        |

| 17    | D0       | Data Bit 0 if HBE is LOW. Least Significant Bit (LSB);<br>Data Bit 8 if HBE is HIGH.                                                                                                        |

| 18    | HBE      | High Byte Enable. When held LOW, data output as 12<br>bits in parallel. When held HIGH, four MSBs presented on<br>pins 14-17, pins 9-12 output LOWs. Must be LOW to<br>initiate conversion. |

| 19    | R/C      | Read/Convert. Falling edge initiates conversion when $\overline{\text{CS}}$ is LOW, HBE is LOW, and $\overline{\text{BUSY}}$ is HIGH.                                                       |

| 20    | ĊS       | Chip Select. Outputs in Hi-Z state when HIGH. Must be LOW to initiate conversion or read data.                                                                                              |

| 21    | BUSY     | Busy. Output LOW during conversion. Data valid on rising<br>edge in Convert Mode.                                                                                                           |

| 22    | -Vs      | Negative Power Supply. –12V or –15V. Bypass to GND.                                                                                                                                         |

| 23    | $V_{SD}$ | Positive Digital Power Supply. +5V. Connect to pin 24, and bypass to GND.                                                                                                                   |

| 24    | $V_{SA}$ | Positive Analog Power Supply. +5V. Connect to pin 23, and bypass to GND.                                                                                                                    |

### **PIN CONFIGURATION**

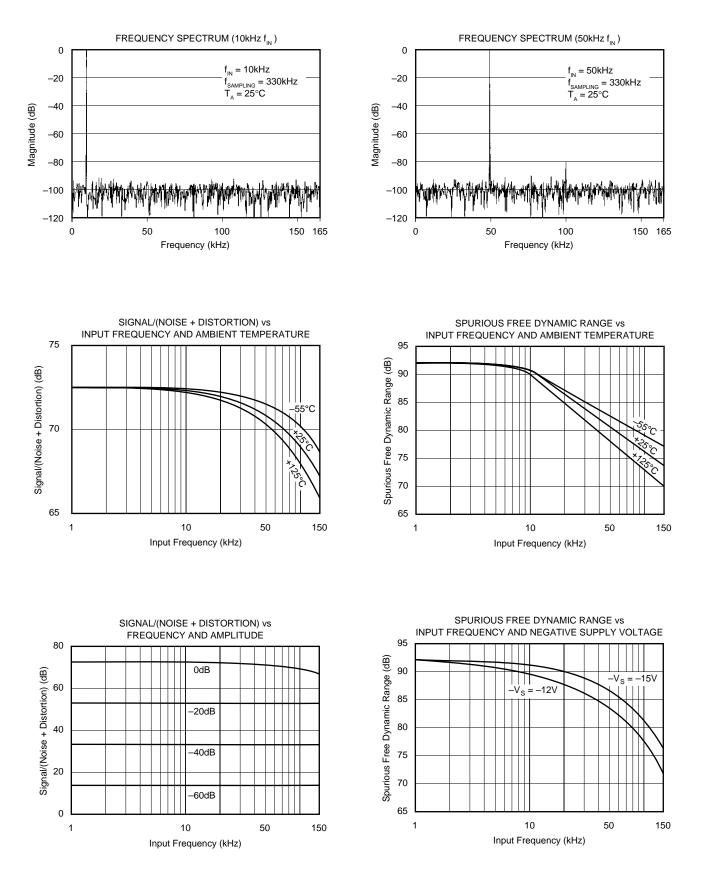

## **TYPICAL PERFORMANCE CURVES**

At +V<sub>S</sub> = +5V, -V<sub>S</sub> = -15V, and T<sub>A</sub> = +25°C, unless otherwise noted. All plots use 1024 point FFTs.

# THEORY OF OPERATION

The ADS7800 combines the advantages of advanced CMOS technology (logic density, stable capacitors, and good analog switches) with Burr-Brown's proven skills in laser-trimmed thin-film resistors to provide a complete sampling A/D converter.

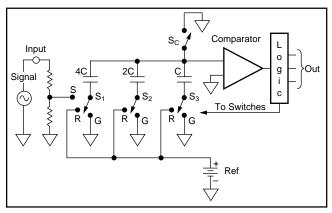

A basic charge-redistribution successive approximation architecture converts analog input voltages into digital words. Figure 1 shows the operation of a simplified 3-bit charge redistribution A/D. Precision laser-trimmed scaling resistors at the input divide standard input ranges ( $\pm 10V$  or  $\pm 5V$  for the ADS7800) into levels compatible with the CMOS characteristics of the internal capacitor array.

While in the sampling mode, the capacitor array switch for the MSB capacitor (S<sub>1</sub>) is in position "S", so that the charge on the MSB capacitor is proportional to the voltage level of the analog input signal, and the remaining array switches (S<sub>2</sub> and S<sub>3</sub>) are set to position "R" to provide an accurate bipolar offset from the reference source REF. At the same time, switch S<sub>C</sub> is also in the closed position to auto-zero any offset errors in the CMOS comparator.

When a convert command is received, switch  $S_1$  is opened to trap a charge on the MSB capacitor proportional to the input level at the time of the sampling command, switches  $S_2$  and  $S_3$  are opened to trap an offset charge, and switch  $S_C$  is opened to float the comparator input. The charge trapped on the capacitor array can now be moved between the three capacitors in the array by connecting switches  $S_1$ ,  $S_2$  and  $S_3$  to positions "R" (to connect to REF) or "G" (to connect to GND) successively, changing the voltage generated at the comparator input node.

The first approximation connects the MSB capacitor via switch  $S_1$  to REF, while switches  $S_2$  and  $S_3$  are connected to GND. Depending on whether the comparator output is HIGH or LOW, the logic will then latch  $S_1$  in position "R" or "G", and moves on to make the next approximation by connecting  $S_2$  to REF and  $S_3$  to GND. When the three successive approximation steps are made for this simple converter, the voltage level at the comparator will be within 1/2LSB of GND, and the data output word will be based on reading the positions of  $S_1$ ,  $S_2$  and  $S_3$ .

FIGURE 1. 3-Bit Charge Redistribution A/D.

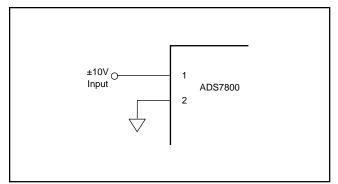

FIGURE 2. Basic ±10V Operation.

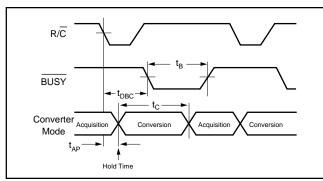

### OPERATION BASIC OPERATION

Figure 2 shows the simple hookup circuit required to operate the ADS7800 in a  $\pm 10V$  range in the Convert Mode. A convert command arriving on pin 19, R/ $\overline{C}$ , (a pulse taking pin 19 LOW for a minimum of 40ns) puts the ADS7800 in the hold mode, and a conversion is started. Pin 21, BUSY, will be held LOW during the conversion, and rises only after the conversion is completed and the data has been transferred to the output latches. Thus, the rising edge of the signal on pin 21 can be used to read the data from the conversion. Also, during conversion, the BUSY signal puts the output data lines in Hi-Z states and inhibits input lines. This means that pulses on pin 19 are ignored, so that new conversions cannot be initiated during a conversion, either as a result of spurious signals or to short-cycle the ADS7800.

In the Read Mode, the input to pin 19 is kept normally LOW, and a HIGH pulse is used to read data and initiate a conversion. In this mode, the rising edge of  $R/\overline{C}$  on pin 19 will enable the output data pins, and the data from the previous conversion becomes valid. The falling edge then puts the ADS7800 in a hold mode, and initiates a new conversion.

The ADS7800 will begin acquiring a new sample as soon as the conversion is completed, even before the BUSY output rises on pin 21, and will track the input signal until the next conversion is started, whether in the Convert Mode or the Read Mode.

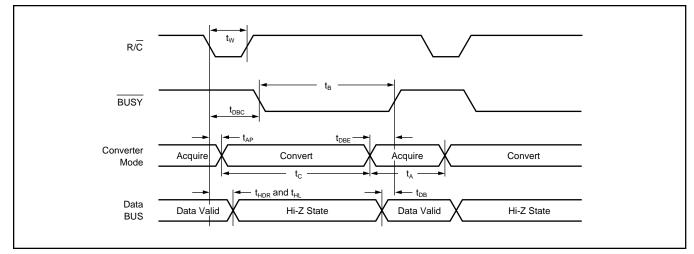

FIGURE 3. Acquisition and Conversion Timing.

| SYMBOL           | PARAMETER           | MIN | TYP  | MAX  | UNITS   |

|------------------|---------------------|-----|------|------|---------|

| t <sub>DBC</sub> | BUSY delay from R/C |     | 80   | 150  | ns      |

| t <sub>B</sub>   | BUSY Low            |     | 2.5  | 2.7  | μs      |

| t <sub>AP</sub>  | Aperture Delay      |     | 13   |      | ns      |

| $\Delta t_{AP}$  | Aperture Jitter     |     | 150  |      | ps, rms |

| t <sub>C</sub>   | Conversion Time     |     | 2.47 | 2.70 | μs      |

TABLE I. Acquisition and Conversion Timing.

For use with an 8-bit bus, the data can be read out in two bytes under the control of pin 18, HBE. With a LOW input on pin 18, at the end of a conversion, the 8 LSBs of data are loaded into the latches on pins 9 through 12 and 14 through 17. Taking pin 18 HIGH then loads the 4 MSBs on pins 14 through 17, with pins 9 through 12 being forced LOW.

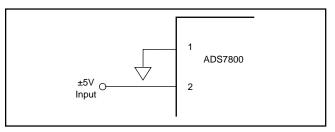

### **ANALOG INPUT RANGES**

The ADS7800 offers two standard bipolar input ranges:  $\pm 10V$  and  $\pm 5V$ . If a  $\pm 10V$  range is required, the analog input signal should be connected to pin 1. A signal requiring a  $\pm 5V$  range should be connected to pin 2. In either case, the other pin of the two must be grounded or connected to the adjustment circuits described in the section on calibration. (See Figures 4 and 5, or 10 and 11.)

### **CONTROLLING THE ADS7800**

The ADS7800 can be easily interfaced to most microprocessor-based and other digital systems. The microprocessor may take full control of each conversion, or the ADS7800 may operate in a stand-alone mode, controlled only by the  $R/\overline{C}$  input. Full control consists of initiating the conversion and reading the output data at user command, transmitting data either all 12-bits in one parallel word, or in two 8-bit bytes. The three control inputs ( $\overline{CS}$ ,  $R/\overline{C}$  and HBE) are all TTL/CMOS compatible. The functions of the control lines are shown in Table II.

| cs | R/C | HBE | BUSY | OPERATION                               |  |  |  |  |  |

|----|-----|-----|------|-----------------------------------------|--|--|--|--|--|

| 1  | Х   | Х   | 1    | None - Outputs in Hi-Z State.           |  |  |  |  |  |

| 0  | 1↓0 | 0   | 1    | Holds Signal and Initiates Conversion.  |  |  |  |  |  |

| 0  | 1   | 0   | 1    | Output Three-State Buffers Enabled once |  |  |  |  |  |

|    |     |     |      | Conversion has Finished.                |  |  |  |  |  |

| 0  | 1   | 1   | 1    | Enable Hi-Byte in 8-bit Bus Mode.       |  |  |  |  |  |

| 0  | 1↓0 | 1   | 1    | Inhibit Start of Conversion.            |  |  |  |  |  |

| 0  | 0   | 1   | 1    | None - Outputs in Hi-Z State.           |  |  |  |  |  |

| Х  | Х   | Х   | 0    | Conversion in Progress. Outputs Hi-Z    |  |  |  |  |  |

|    |     |     |      | State. New Conversion Inhibited until   |  |  |  |  |  |

|    |     |     |      | Present Conversion has Finished.        |  |  |  |  |  |

TABLE II. Control Line Functions.

For stand-alone operation, control of the ADS7800 is accomplished by a single control line connected to  $R/\overline{C}$ . In this mode,  $\overline{CS}$  and HBE are connected to GND. The output data are presented as 12-bit words. The stand-alone mode is used in systems containing dedicated input ports which do not require full bus interface capability.

Conversion is initiated by a HIGH-to-LOW transition on  $R/\overline{C}$ . The three-state data output buffers are enabled when  $R/\overline{C}$  is HIGH and  $\overline{BUSY}$  is HIGH. Thus, there are two possible modes of operation: conversion can be initiated with either positive or negative pulses. In either case, the  $R/\overline{C}$  pulse must remain LOW a minimum of 40ns.

Figure 6 illustrates timing when conversion is initiated by an  $R/\overline{C}$  pulse which goes LOW and returns HIGH during the conversion. In this case (Convert Mode), the three-state outputs go into the Hi-Z state in response to the falling edge of  $R/\overline{C}$ , and are enabled for external access of the data after completion of the conversion.

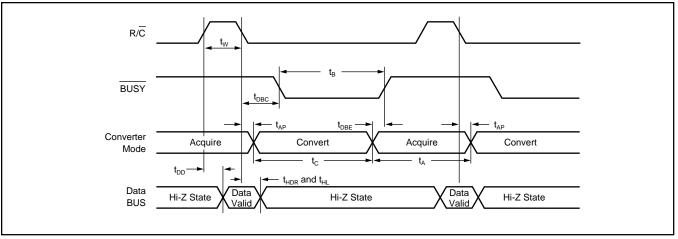

Figure 7 illustrates the timing when conversion is initiated by a positive  $R/\overline{C}$  pulse. In this mode (Read Mode), the output data from the previous conversion is enabled during the HIGH portion of  $R/\overline{C}$ . A new conversion starts on the falling edge of  $R/\overline{C}$ , and the three-state outputs return to the Hi-Z state until the next occurrence of a HIGH on  $R/\overline{C}$ .

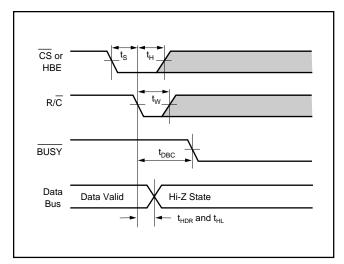

## **CONVERSION START**

A conversion is initiated on the ADS7800 only by a negative transition occurring on  $R/\overline{C}$ , as shown in Table I. No other combination of states or transitions will initiate a conversion. Conversion is inhibited if either  $\overline{CS}$  or HBE are HIGH, or if  $\overline{BUSY}$  is LOW.  $\overline{CS}$  and HBE should be stable a minimum of 25ns prior to the transition on  $R/\overline{C}$ . Timing relationships for start of conversion are illustrated in Figure 8.

The  $\overline{\text{BUSY}}$  output indicates the current state of the converter by being LOW only during conversion. During this time the three-state output buffers remain in a Hi-Z state, and therefore data cannot be read during conversion. During this period, additional transitions on the three digital inputs ( $\overline{\text{CS}}$ ,  $R/\overline{\text{C}}$  and HBE) will be ignored, so that conversion cannot be prematurely terminated or restarted.

### INTERNAL CLOCK

The ADS7800 has an internal clock that is factory trimmed to achieve a typical conversion time of 2.47 $\mu$ s, and a maximum conversion time over the full operating temperature range of 2.7 $\mu$ s. No external adjustments are required, and with the guaranteed maximum acquisition time of 300ns, throughput performance is assured with convert pulses as close as 3 $\mu$ s.

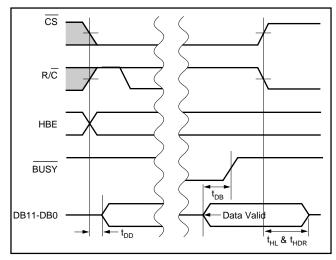

### **READING DATA**

After conversion is initiated, the output buffers remain in a Hi-Z state until the following three logic conditions are simultaneously met:  $R/\overline{C}$  is HIGH,  $\overline{BUSY}$  is HIGH and  $\overline{CS}$  is LOW. Upon satisfaction of these conditions, the data lines are enabled according to the state of HBE. See Figure 9 and Table III for timing relationships and specifications.

## CALIBRATION

#### OPTIONAL EXTERNAL GAIN AND OFFSET TRIM

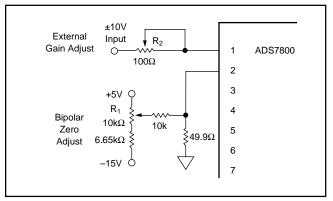

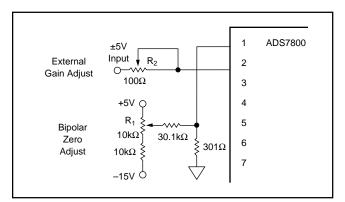

Offset and full-scale errors may be trimmed to zero using external offset and full-scale trim potentiometers connected to the ADS7800 as shown in Figures 10 and 11.

If adjustment of offset and full scale is not required, connections as shown in Figures 4 and 5 should be used.

FIGURE 4. ±10V Range Without Trims.

FIGURE 5. ±5V Range Without Trims.

### CALIBRATION PROCEDURE

First, trim offset, by applying at the input (pin 1 or 2) the mid-point transition voltage (-2.44mV for the  $\pm 10$ V range, -1.22mV for the  $\pm 5$ V range.) With the ADS7800 converting continually, adjust potentiometer R<sub>1</sub> until the MSB (D11 on pin 5) is toggling alternately HIGH and LOW.

Next adjust full scale, by applying at the input a DC input signal that is 3/2LSB below the nominal full scale voltage (+9.9927V for the  $\pm 10V$  range, +4.9963V for the  $\pm 5V$  range.) With the ADS7800 converting continually, adjust R<sub>2</sub> until the LSB (D0 on pin 17) is toggling HIGH and LOW with all of the other bits HIGH.

# LAYOUT CONSIDERATIONS

Because of the high resolution and linearity of the ADS7800, system design problems such as ground path resistance and contact resistance become very important.

### ANALOG SIGNAL SOURCE IMPEDANCE

The input resistance of the ADS7800 is  $6.3k\Omega$  or  $4.2k\Omega$  (for the ±10V and ±5V ranges respectively.) To avoid introducing distortion, the source resistance must be very low, or constant with signal level. The output impedance provided by most op amps is ideal.

Pins 23 ( $V_{SD}$ ) and 24 ( $V_{SA}$ ) are not connected internally on the ADS7800, to maximize accuracy on the chip. They should be connected together as close as possible to the unit.

FIGURE 6. Convert Mode:  $R/\overline{C}$  Pulse LOW — Outputs Enabled After Conversion.

FIGURE 7. Read Mode:  $R/\overline{C}$  Pulse HIGH— Outputs Enabled Only When  $R/\overline{C}$  is High.

| SYMBOL                         | PARAMETER                                                                                                   | MIN | ТҮР  | MAX  | UNITS   |

|--------------------------------|-------------------------------------------------------------------------------------------------------------|-----|------|------|---------|

| t <sub>w</sub>                 | R/C Pulse Width                                                                                             | 40  | 10   |      | ns      |

| t <sub>DBC</sub>               | BUSY delay from R/C                                                                                         |     | 80   | 150  | ns      |

| t <sub>B</sub>                 | BUSY LOW                                                                                                    |     | 2.5  | 2.7  | μs      |

| t <sub>AP</sub>                | Aperture Delay                                                                                              |     | 13   |      | ns      |

| $\Delta t_{AP}$                | Aperture Jitter                                                                                             |     | 150  |      | ps, rms |

| t <sub>C</sub>                 | Conversion Time                                                                                             |     | 2.47 | 2.70 | μs      |

| t <sub>DBE</sub>               | BUSY from End of Conversion                                                                                 |     | 100  |      | ns      |

| t <sub>DB</sub>                | BUSY Delay after Data Valid                                                                                 | 25  | 75   | 200  | ns      |

| t <sub>A</sub>                 | Acquisition Time                                                                                            |     | 130  | 300  | ns      |

| t <sub>A</sub> +t <sub>C</sub> | Throughput Time                                                                                             |     | 2.6  | 3.0  | μs      |

| t <sub>HDR</sub>               | Valid Data Held After R/C LOW                                                                               | 20  | 50   |      | ns      |

| ts                             | $\overline{\text{CS}}$ or HBE LOW before R/ $\overline{\text{C}}$ Falls                                     | 25  | 5    |      | ns      |

| t <sub>H</sub>                 | CS or HBE LOW after R/C Falls                                                                               | 25  | 0    |      | ns      |

| t <sub>DD</sub>                | Data Valid from $\overline{CS}$ LOW, R/ $\overline{C}$ HIGH, and HBE in Desired State (Load = 100pF)        |     | 65   | 150  | ns      |

| t <sub>HDR</sub>               | Valid Data Held After R/C Low                                                                               | 20  | 50   |      | ns      |

| t <sub>HL</sub>                | Delay to Hi-Z State after R/ $\overline{C}$ Falls or $\overline{CS}$ Rises (3k $\Omega$ Pullup or Pulldown) |     | 50   | 150  | ns      |

TABLE III. Timing Specifications ( $T_{MIN}$  to  $T_{MAX}$ ).

FIGURE 8. Conversion Start Timing.

Pin 24 may be slightly more sensitive than pin 23 to supply variations, but to maintain maximum system accuracy, both should be well isolated from digital supplies with wide load variations.

To limit the effects of digital switching elsewhere in a system on the analog performance of the system, it often makes sense to run a separate +5V supply conductor from the supply regulator to any analog components requiring +5V, including the ADS7800.

The V<sub>S</sub> pins (23 and 24) should be connected together and bypassed with a parallel combination of a 6.8µF tantalum capacitor and a 0.1µF ceramic capacitor located close to the converter to obtain noise-free operation. (See Figure 2.) The  $-V_S$  pin 22 should be bypassed with a 1µF tantalum capacitor, again as close as possible to the ADS7800.

Noise on the power supply lines can degrade converter performance, especially noise and spikes from a switching power supply. Appropriate supplies or filters must be used.

The GND pins (4 and 13) are also separated internally, and should be directly connected to a ground plane under the

converter if at all possible. A ground plane is usually the best solution for preserving dynamic performance and reducing noise coupling into sensitive converter circuits. Where any compromises must be made, the common return of the analog input signal should be referenced to pin 4, AGND, on the ADS7800, which prevents any voltage drops that might occur in the power supply common returns from appearing in series with the input signal.

Coupling between analog input and digital lines should be minimized by careful layout. For instance, if the lines must cross, they should do so at right angles. Parallel analog and digital lines should be separated from each other by a pattern connected to common.

If external full scale and offset potentiometers are used, the potentiometers and related resistors should be located as close to the ADS7800 as possible.

FIGURE 9. Read Cycle Timing.

#### **REFERENCE BYPASS**

Pin 3 (REF) should be bypassed with a  $22\mu$ F to  $47\mu$ F tantalum capacitor. A rated working voltage of 2V or more is acceptable here. This pin is used to enhance the system accuracy of the internal reference circuit, and is not recommended for driving external signals. If there are important system reasons for using the ADS7800 reference externally, the output of pin 3 must be appropriately buffered.

#### **"HOT SOCKET" PRECAUTION**

Two separate  $+5V V_S$  pins, 23 and 24, are used to minimize noise caused by digital transients. If one pin is powered and the other is not, the ADS7800 may "Latch Up" and draw excessive current. In normal operation, this is not a problem because both pins will be soldered together. However, during evaluation, incoming inspection, repair, etc., where the potential of a "Hot Socket" exists, care should be taken to power the ADS7800 only after it has been socketed.

FIGURE 10. ±10V Range With External Trims.

#### **MINIMIZING "GLITCHES"**

Coupling of external transients into an A/D converter can cause errors which are difficult to debug. In addition to the discussions earlier on layout considerations for supplies, bypassing and grounding, there are several other useful steps that can be taken to get the best analog performance out of a system using the ADS7800. These potential system problem sources are particularly important to consider when developing a new system, and looking for the causes of errors in breadboards.

First, care should be taken to avoid glitches during critical times in the sampling and conversion process. Since the ADS7800 has an internal sample/hold function, the signal that puts it into the hold state ( $R/\overline{C}$  going LOW) is critical, as it would be on any sample/hold amplifier. The  $R/\overline{C}$  falling edge should be sharp and have minimal ringing, especially during the 20ns after it falls.

Although not normally required, it is also good practice to avoid glitching the ADS7800 while bit decisions are being made. Since the above discussion calls for a fast, clean rise and fall on  $R/\overline{C}$ , it makes sense to keep the rising edge of the convert pulse outside the time when bit decisions are being made. In other words, the convert pulse should either be short (under 100ns so that it transitions before the MSB decision), or relatively long (over 2.75µs to transition after the LSB decision).

FIGURE 11. ±5V Range With External Trims.

Next, although the data outputs are forced into a Hi-Z state during conversion, fast bus transients can still be capacitively coupled into the ADS7800. If the data bus experiences fast transients during conversion, these transients can be attenuated by adding a logic buffer to the data outputs. The  $\overline{\text{BUSY}}$  output can be used to enable the buffer.

Naturally, transients on the analog input signal are to be avoided, especially at times within  $\pm 20$ ns of R/ $\overline{C}$  going LOW, when they may be trapped as part of the charge on the capacitor array. This requires careful layout of the circuit in front of the ADS7800.

Finally, in multiplexed systems, the timing on when the multiplexer is switched may affect the analog performance of the system. In most applications, the multiplexer can be switched as soon as  $R/\overline{C}$  goes LOW (with appropriate delays), but this may affect the conversion if the switched signal shows glitches or significant ringing at the ADS7800 input. Whenever possible, it is safer to wait until the conversion is completed before switching the multiplexer. The extremely fast acquisition time and conversion time of the ADS7800 make this practical in many applications.

| Input Voltage Range Defined As:      |                     | ±10V                | ±5V                 |

|--------------------------------------|---------------------|---------------------|---------------------|

| Analog Input Connected to Pin        |                     | 1                   | 2                   |

| Pin Connected to GND                 |                     | 2                   | 1                   |

| One Least Significant Bit (LSB)      | FSR/2 <sup>12</sup> | 20V/2 <sup>12</sup> | 10V/2 <sup>12</sup> |

|                                      |                     | 4.88mV              | 2.44mV              |

| OUTPUT TRANSITION VALUES             |                     |                     | •                   |

| FFE <sub>H</sub> to FFF <sub>H</sub> | +Full Scale         | +10V-3/2LSB         | +5V-3/2LSB          |

|                                      |                     | +9.9927V            | +4.9963V            |

| 7FF <sub>H</sub> to 800 <sub>H</sub> | Mid Scale           | 0V-1/2LSB           | 0V-1/2LSB           |

|                                      | (Bipolar Zero)      | -2.44mV             | -1.22mV             |

| 000 <sub>H</sub> to 001 <sub>H</sub> | -Full Scale         | -10V+1/2LSB         | -5V+1/2LSB          |

|                                      |                     | -9.9976V            | -4.9988V            |

TABLE IV. Input Voltages, Transition Values, and LSB Values.

### PACKAGING INFORMATION

| Orderable Device | Status  | Package Type | -       | Pins | -    | Eco Plan     | Lead finish/  | MSL Peak Temp       | Op Temp (°C) | Device Marking | Samples |

|------------------|---------|--------------|---------|------|------|--------------|---------------|---------------------|--------------|----------------|---------|

|                  | (1)     |              | Drawing |      | Qty  | (2)          | Ball material | (3)                 |              | (4/5)          |         |

|                  |         |              |         |      |      |              | (6)           |                     |              |                |         |

| ADS7800AH        | LIFEBUY | CDIP SB      | JDN     | 24   | 1    | RoHS & Green | Call TI       | N / A for Pkg Type  |              | ADS7800AH      |         |

| ADS7800BH        | LIFEBUY | CDIP SB      | JDN     | 24   | 1    | RoHS & Green | Call TI       | N / A for Pkg Type  |              | ADS7800BH      |         |

| ADS7800JU        | LIFEBUY | SOIC         | DW      | 24   | 25   | RoHS & Green | Call TI       | Level-3-260C-168 HR | -40 to 85    | ADS7800JU      |         |

| ADS7800JU/1K     | LIFEBUY | SOIC         | DW      | 24   | 1000 | RoHS & Green | Call TI       | Level-3-260C-168 HR | -40 to 85    | ADS7800JU      |         |

| ADS7800JU/1KE4   | LIFEBUY | SOIC         | DW      | 24   | 1000 | RoHS & Green | Call TI       | Level-3-260C-168 HR | -40 to 85    | ADS7800JU      |         |

| ADS7800KU        | LIFEBUY | SOIC         | DW      | 24   | 25   | RoHS & Green | Call TI       | Level-3-260C-168 HR | -40 to 85    | ADS7800KU      |         |

| ADS7800KUE4      | LIFEBUY | SOIC         | DW      | 24   | 25   | RoHS & Green | Call TI       | Level-3-260C-168 HR | -40 to 85    | ADS7800KU      |         |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

(5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and

www.ti.com

continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

### PACKAGE MATERIALS INFORMATION

Texas Instruments

www.ti.com

### TAPE AND REEL INFORMATION

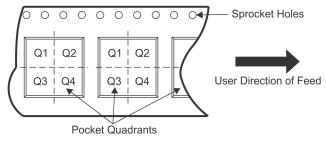

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

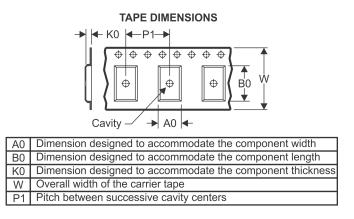

| Device       | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| ADS7800JU/1K | SOIC            | DW                 | 24 | 1000 | 330.0                    | 24.4                     | 10.75      | 15.7       | 2.7        | 12.0       | 24.0      | Q1               |

www.ti.com

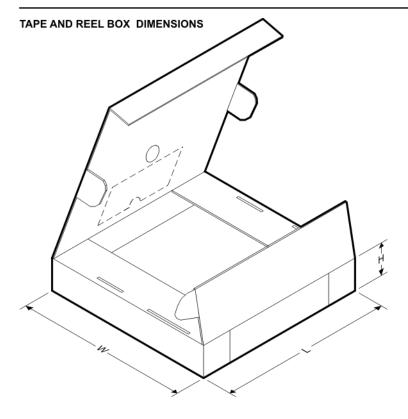

### PACKAGE MATERIALS INFORMATION

5-Jan-2022

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| ADS7800JU/1K | SOIC         | DW              | 24   | 1000 | 367.0       | 367.0      | 45.0        |

www.ti.com

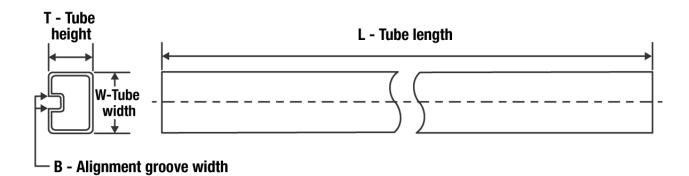

### TUBE

| *All | dimensions | are | nominal |

|------|------------|-----|---------|

| Device      | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | Τ (μm) | B (mm) |

|-------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| ADS7800AH   | JDN          | CDIP SB      | 24   | 1   | 506.98 | 15.24  | 12290  | NA     |

| ADS7800BH   | JDN          | CDIP SB      | 24   | 1   | 506.98 | 15.24  | 12290  | NA     |

| ADS7800JU   | DW           | SOIC         | 24   | 25  | 507    | 12.83  | 5080   | 6.6    |

| ADS7800KU   | DW           | SOIC         | 24   | 25  | 507    | 12.83  | 5080   | 6.6    |

| ADS7800KUE4 | DW           | SOIC         | 24   | 25  | 507    | 12.83  | 5080   | 6.6    |

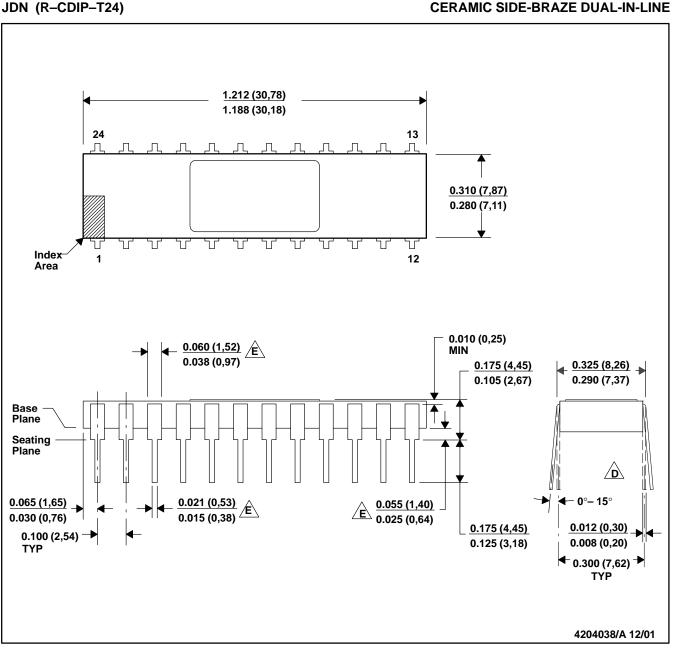

### **MECHANICAL DATA**

MCDI046 – JANUARY 2002

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Leads within 0.005 (0.13) radius of true position (TP) at gage plane with maximum material condition and unit installed.

- D The Package thermal performance may be enhanced by bonding the thermal die pad to an external thermal plane.

- This pad is electrically and thermally connected to the backside of the die and possibly selected ground leads. Outlines on which the seating plane is coincident with the plane (standoff = 0), terminal lead standoffs are not required, and lead

- shoulder may equal lead width along any part of the lead above the seating/base plane.

- F. A visual index feature must be located within the cross-hatched area.

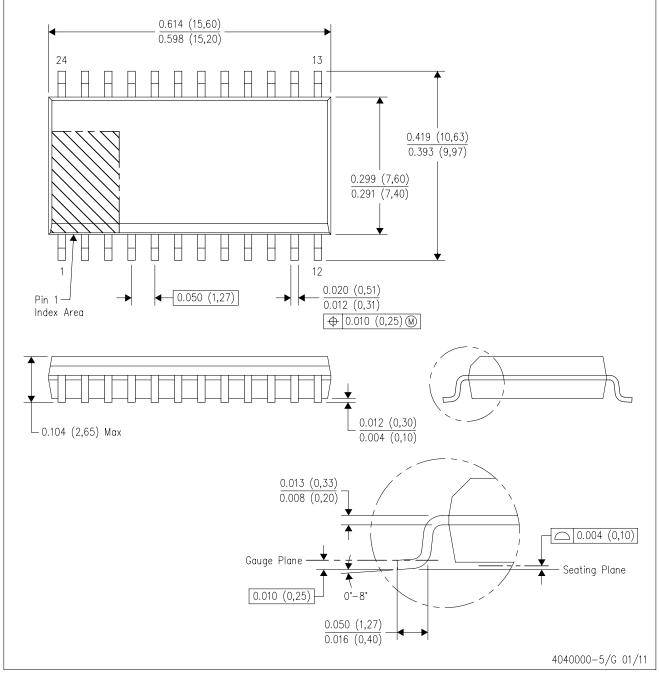

DW (R-PDSO-G24)

PLASTIC SMALL OUTLINE

NOTES: A. All linear dimensions are in inches (millimeters). Dimensioning and tolerancing per ASME Y14.5M-1994.

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusion not to exceed 0.006 (0,15).

D. Falls within JEDEC MS-013 variation AD.

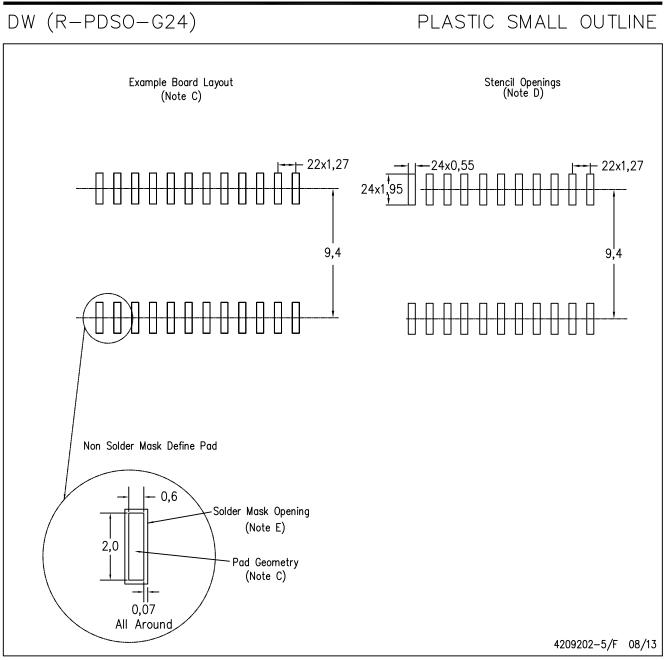

### LAND PATTERN DATA

NOTES:

A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Refer to IPC7351 for alternate board design.

- D. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC-7525

- E. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated