## **TPS2592BA, TPS2592BL**

SLVSCU2 - DECEMBER 2014

# TPS2592Bx 5-V eFuse with Over Voltage Protection and Blocking FET Control

Not Recommended for New Designs

#### Features

- 5-V eFuse, V<sub>ABSMAX</sub> = 20 V

- Integrated 28-mΩ Pass MOSFET

- Fixed 6.1-V Over Voltage Clamp

- 2-A to 5-A Adjustable I<sub>LIMIT</sub> (±15% Accuracy)

- Reverse Current Blocking Support

- Programmable OUT Slew Rate, UVLO

- Built-in Thermal Shutdown

- UL 2367 Recognized File No. 169910\*

- \*R<sub>ILIM</sub> ≤ 100 kΩ (4 A max)

- Safe During Single Point Failure Test (UL60950)

- Small Foot Print 10L (3 mm x 3 mm) VSON

## **Applications**

- Adapter Powered Devices

- HDD and SSD Drives

- Set Top Boxes

- Servers / AUX Supplies

- Fan Control

- PCI/PCIe Cards

# 3 Description

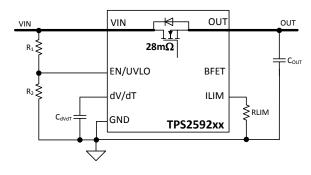

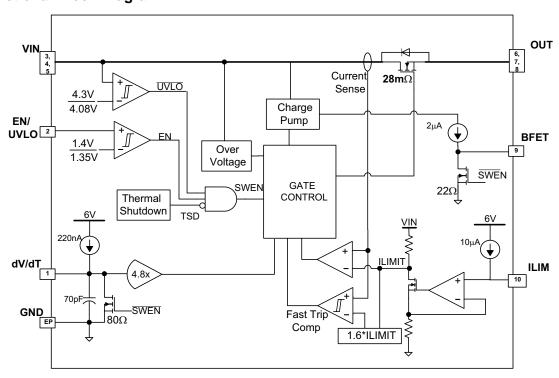

The TPS2592Bx family of eFuses is a highly integrated circuit protection and power management solution in a tiny package. The devices use few external components and provide multiple protection modes. They are a robust defense against overloads, shorts circuits, voltage surges, excessive inrush current, and reverse current.

Current limit level can be set with a single external resistor. Over voltage events are limited by internal clamping circuits to a safe fixed maximum, with no external components required. Applications with particular voltage ramp requirements can set dV/dT with a single capacitor to ensure proper output ramp

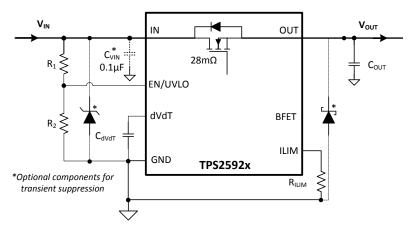

Many systems, such as SSDs, must not allow holdup capacitance energy to dump back through the FET body diode onto a drooping or shorted input bus. The BFET pin is for such systems. An external NFET can be connected "Back to Back (B2B)" with the TPS2592 output and the gate driven by BFET to prevent current flow from load to source (see Figure 42).

## Device Information<sup>(1)</sup>

| PART NUMBER          | PACKAGE    | BODY SIZE (NOM)   |

|----------------------|------------|-------------------|

| TPS2592BA            | \(CON (40) | 2.00 mm 2.00 mm   |

| PS2592BA<br>PS2592BL | VSON (10)  | 3.00 mm × 3.00 mm |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

# Application Schematic

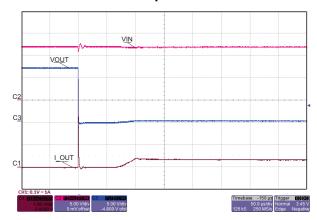

#### **Transient: Output Short Circuit**

## **TPS2592BA, TPS2592BL**

SLVSCU2 – DECEMBER 2014 www.ti.com

## **Table of Contents**

| 1 | Features 1                             |    | 9.4 Device Functional Modes            | 16 |

|---|----------------------------------------|----|----------------------------------------|----|

| 2 | Applications 1                         | 10 | Application and Implementation         | 17 |

| 3 | Description 1                          |    | 10.1 Application Information           | 17 |

| 4 | Application Schematic 1                |    | 10.2 Typical Applications              | 17 |

| 5 | Revision History2                      |    | 10.3 Maximum Device Power Dissipation  | 01 |

| 6 | Device Comparison Table3               |    | Considerations                         |    |

| 7 |                                        | 11 | Power Supply Recommendations           | 24 |

| ′ | Pin Configuration and Functions 3      |    | 11.1 Transient Protection              | 24 |

| 8 | Specifications4                        |    | 11.2 Output Short-Circuit Measurements | 24 |

|   | 8.1 Absolute Maximum Ratings 4         | 12 | Layout                                 | 25 |

|   | 8.2 ESD Ratings 4                      |    | 12.1 Layout Guidelines                 | 25 |

|   | 8.3 Recommended Operating Conditions 4 |    | 12.2 Layout Example                    |    |

|   | 8.4 Thermal Information 5              | 13 | Device and Documentation Support       |    |

|   | 8.5 Electrical Characteristics 5       |    | 13.1 Device Support                    |    |

|   | 8.6 Timing Requirements 6              |    |                                        |    |

|   | 8.7 Typical Characteristics            |    | 13.2 Related Links                     |    |

| _ |                                        |    | 13.3 Trademarks                        | 26 |

| 9 | Detailed Description 13                |    | 13.4 Electrostatic Discharge Caution   | 26 |

|   | 9.1 Overview                           |    | 13.5 Glossary                          |    |

|   | 9.2 Functional Block Diagram 13        | 14 | Mechanical, Packaging, and Orderable   |    |

|   | 9.3 Feature Description                |    | Information                            | 26 |

|   |                                        |    |                                        |    |

# 5 Revision History

| DATE          | REVISION | NOTES           |

|---------------|----------|-----------------|

| December 2014 | *        | Initial release |

Product Folder Links: TPS2592BA TPS2592BL

Submit Documentation Feedback

## **TPS2592BA, TPS2592BL**

SLVSCU2-DECEMBER 2014

## 6 Device Comparison Table

| PART NUMBER | UV    | OV CLAMP | FAULT RESPONSE | STATUS |

|-------------|-------|----------|----------------|--------|

| TPS2592BA   | 4.3 V | 6.1 V    | Auto Retry     | Active |

| TPS2592BL   | 4.3 V | 6.1 V    | Latched        | Active |

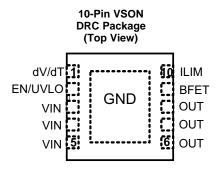

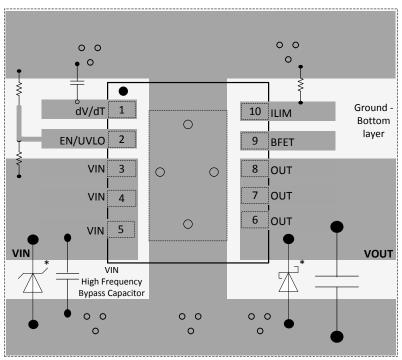

## 7 Pin Configuration and Functions

**Pin Functions**

|             | PIN       | DESCRIPTION                                                                                                                                                                                                                                                                                        |

|-------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME NUMBER |           | DESCRIPTION                                                                                                                                                                                                                                                                                        |

| BFET        | 9         | Connect this pin to the gate of a blocking NFET. See the Feature Description.                                                                                                                                                                                                                      |

| dV/dT 1     |           | Tie a capacitor from this pin to GND to control the ramp rate of OUT at device turn-on.                                                                                                                                                                                                            |

| EN/UVLO     | 2         | This is a dual function control pin. When used as an ENABLE pin and pulled down, it shuts off the internal pass MOSFET and pulls BFET to GND. When pulled high, it enables the device and BFET. As an UVLO pin, it can be used to program different UVLO trip point via external resistor divider. |

| GND         | PowerPAD™ | GND                                                                                                                                                                                                                                                                                                |

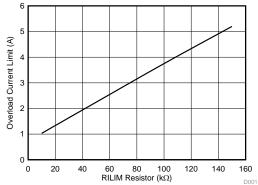

| ILIM        | 10        | A resistor from this pin to GND will set the overload and short circuit limit.                                                                                                                                                                                                                     |

| OUT         | 6-8       | Output of the device                                                                                                                                                                                                                                                                               |

| VIN         | 3-5       | Input supply voltage                                                                                                                                                                                                                                                                               |

Product Folder Links: TPS2592BA TPS2592BL

SLVSCU2 – DECEMBER 2014 www.ti.com

## 8 Specifications

## 8.1 Absolute Maximum Ratings

over operating temperature range (unless otherwise noted) (1) (2)

|                                             |                                                       | MIN                                                                                                                                                                                                  | MAX                                                                                      | UNIT    |  |

|---------------------------------------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|---------|--|

| Supply voltogo range (1)                    | VIN                                                   | -0.3                                                                                                                                                                                                 | 20                                                                                       | V       |  |

| Supply voltage range 7                      | VIN (10 ms Transient)                                 |                                                                                                                                                                                                      | 22                                                                                       | V       |  |

| Output voltage                              | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | V                                                                                                                                                                                                    |                                                                                          |         |  |

| Output voltage                              | OUT (Transient < 1 µs)                                |                                                                                                                                                                                                      | 0.3 20 22 0.3 VIN + 0.3 -1.2 0.3 7 0.3 7 0.3 7 0.3 7 0.3 30 See the Thermal Inform 40 50 | V       |  |

|                                             | ILIM                                                  | -0.3                                                                                                                                                                                                 | 7                                                                                        |         |  |

| Voltage                                     | EN/UVLO                                               | -0.3                                                                                                                                                                                                 | 7                                                                                        | V       |  |

| Supply voltage range (1)                    | dV/dT                                                 | -0.3                                                                                                                                                                                                 | 7                                                                                        | V       |  |

|                                             | -0.3                                                  | 30                                                                                                                                                                                                   |                                                                                          |         |  |

| Continuous power dissipation                |                                                       | See th                                                                                                                                                                                               | ne Thermal Info                                                                          | rmation |  |

| Maximum power dissipation (3),              | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$   |                                                                                                                                                                                                      | 40                                                                                       | 10/     |  |

|                                             | $T_A = 0$ °C to +85°C                                 | T   -0.3   VIN + 0.3   V     T (Transient < 1 μs)   -1.2   V     1   -0.3   7     UVLO   -0.3   7     HT   -0.3   7     ET   -0.3   30     See the Thermal Information     = -40°C to +85°C   40   W | ۷V                                                                                       |         |  |

| Storage temperature range, T <sub>stg</sub> |                                                       | -65                                                                                                                                                                                                  | 150                                                                                      | °C      |  |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 8.2 ESD Ratings

|                        |                         |                                                                                | VALUE | UNIT |

|------------------------|-------------------------|--------------------------------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> Ele | Clastrootatia diaabaraa | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)                         | ±2000 | \/   |

|                        | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±500  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

## 8.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                                                                                                                               |                       | MIN       | TYP | MAX   | UNIT |

|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------|-----|-------|------|

|                                                                                                                                               | VIN                   | 4.5       | 5   | 5.5   |      |

| Input voltage range  Continuous output current Resistance  External capacitance  Operating junction temperature Operating Ambient temperature | BFET                  | 0         |     | VIN+6 | \/   |

| input voitage range                                                                                                                           | dV/dT, EN/UVLO        | 4.5 5 5.5 | V   |       |      |

|                                                                                                                                               | ILIM                  | 0         |     |       |      |

| Continuous output current                                                                                                                     | lout                  | 0         |     | 5     | Α    |

| Resistance                                                                                                                                    | ILIM                  | 10        | 100 | 162   | kΩ   |

| External conscitance                                                                                                                          | OUT                   | 0.1       | 1   | 1000  | μF   |

| External capacitance                                                                                                                          | dV/dT                 |           | 1   | 1000  | nF   |

| Operating junction temperature                                                                                                                | range, T <sub>J</sub> | -40       | 25  | 125   | °C   |

| Operating Ambient temperature                                                                                                                 | range, T <sub>A</sub> | -40       | 25  | 85    | °C   |

Submit Documentation Feedback

<sup>(2)</sup> All voltage values, except differential voltages, are with respect to network ground terminal.

<sup>(3)</sup> Refer to detailed explanation in the application section Maximum Device Power Dissipation Considerations.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

TPS2592BA, TPS2592BL

# 8.4 Thermal Information<sup>(1)</sup>

over operating free-air temperature range (unless otherwise noted)

|                    | THEDMAL METRIC                               | TPS2592Bx     | LINUT  |

|--------------------|----------------------------------------------|---------------|--------|

|                    | Junction-to-case (top) thermal resistance    | DRC (10) PINS | UNIT   |

| $R_{\theta JA}$    | Junction-to-ambient thermal resistance       | 45.9          |        |

| $R_{\theta JCtop}$ | Junction-to-case (top) thermal resistance    | 53            |        |

| $R_{\theta JB}$    | Junction-to-board thermal resistance         | 21.2          | °C /// |

| $\Psi_{JT}$        | Junction-to-top characterization parameter   | 1.2           | °C/W   |

| ΨЈВ                | Junction-to-board characterization parameter | 21.4          |        |

| $R_{\theta JCbot}$ | Junction-to-case (bottom) thermal resistance | 5.9           |        |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

## 8.5 Electrical Characteristics

-40 °C  $\leq$  T $_{J}$   $\leq$  125 °C, VIN = 5 V, V $_{EN/UVLO}$  = 2 V, R $_{ILIM}$  = 100 k $\Omega$ , C $_{dVdT}$  = OPEN. All voltages referenced to GND (unless otherwise noted)

|                          | PARAMETER                                                               | TEST CONDITIONS                                                                                           | MIN  | TYP  | MAX                                                                     | UNIT |

|--------------------------|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|------|------|-------------------------------------------------------------------------|------|

| VIN (INPUT SU            | IPPLY)                                                                  | '                                                                                                         | 1    |      | •                                                                       |      |

| V <sub>UVR</sub>         | UVLO threshold, rising                                                  |                                                                                                           | 4.15 | 4.3  | 4.45                                                                    | V    |

| V <sub>UVhyst</sub>      | UVLO hysteresis <sup>(1)</sup>                                          |                                                                                                           |      | 5.4% |                                                                         |      |

| IQ <sub>ON</sub>         |                                                                         | Enabled: EN/UVLO = 2 V                                                                                    | 0.4  | 0.62 | 0.80                                                                    | mA   |

| IQ <sub>OFF</sub>        | Supply current                                                          | EN/UVLO = 0 V                                                                                             |      | 0.1  | 0.25                                                                    | mA   |

|                          |                                                                         | $VIN > 6.75 \text{ V}, I_{OUT} = 10 \text{ mA},$<br>-40°C \(\text{S} \text{T}_{J} \leq 85°C               | 5.5  | 6.1  | 6.75                                                                    |      |

| V <sub>ovc</sub>         | Over-voltage clamp                                                      | $VIN > 6.75 \text{ V}, I_{OUT} = 10 \text{ mA},$<br>-40°C \(\text{S} \text{T}_{J} \leq 125°C              | 5.25 | 6.1  | 6.75                                                                    | V    |

| EN/UVLO (ENA             | ABLE/UVLO INPUT)                                                        |                                                                                                           |      |      |                                                                         |      |

| V <sub>ENR</sub>         | EN Threshold voltage, rising                                            |                                                                                                           | 1.37 | 1.4  | 1.44                                                                    | V    |

| V <sub>ENF</sub>         | EN Threshold voltage, falling                                           |                                                                                                           | 1.32 | 1.35 | 1.39                                                                    | V    |

| I <sub>EN</sub>          | EN Input leakage current                                                | 0 V ≤ V <sub>EN</sub> ≤ 5 V                                                                               | -100 | 0    | 100                                                                     | nA   |

| dV/dT (OUTPU             | IT RAMP CONTROL)                                                        |                                                                                                           |      |      | ,                                                                       |      |

| I <sub>dVdT</sub>        | dV/dT Charging current <sup>(1)</sup>                                   | $V_{dVdT} = 0 V$                                                                                          |      | 220  |                                                                         | nA   |

| R <sub>dVdT_disch</sub>  | dV/dT Discharging resistance                                            | EN/UVLO = 0 V, I <sub>dVdT</sub> = 10 mA sinking                                                          | 50   | 73   | 100                                                                     | Ω    |

| $V_{dVdTmax}$            | dV/dT Max capacitor voltage <sup>(1)</sup>                              |                                                                                                           |      | 5.5  |                                                                         | V    |

| GAIN <sub>dVdT</sub>     | dV/dT to OUT gain <sup>(1)</sup>                                        | $\Delta V_{dVdT}$                                                                                         |      | 4.85 |                                                                         | V/V  |

| ILIM (CURREN             | IT LIMIT PROGRAMMING)                                                   | ,                                                                                                         | '    |      | '                                                                       |      |

| I <sub>ILIM</sub>        | ILIM Bias current <sup>(1)</sup>                                        |                                                                                                           |      | 10   |                                                                         | μA   |

|                          |                                                                         | $R_{ILIM} = 45.3 \text{ k}\Omega, V_{VIN-OUT} = 1 \text{ V}$                                              | 1.79 | 2.10 | 2.42                                                                    |      |

| I <sub>OL</sub>          |                                                                         | $R_{ILIM} = 100 \text{ k}\Omega, V_{VIN-OUT} = 1 \text{ V}$                                               | 3.46 | 3.75 | 4.03                                                                    | Α    |

|                          |                                                                         | $R_{ILIM} = 150 \text{ k}\Omega, V_{VIN-OUT} = 1 \text{ V}$                                               | 4.4  | 5.2  | 1.44<br>1.39<br>100<br>100<br>2.42<br>4.03<br>6<br>2.38<br>3.98<br>5.60 |      |

| I <sub>OL-R-Short</sub>  | Overload current limit <sup>(2)</sup>                                   | $R_{\rm ILIM}$ = 0 $\Omega,$ Shorted Resistor Current Limit (Single Point Failure Test: UL60950) $^{(1)}$ |      | 0.7  |                                                                         | А    |

| I <sub>OL-R-Open</sub>   |                                                                         | $R_{\rm ILIM}$ = OPEN, Open Resistor Current Limit (Single Point Failure Test: UL60950) $^{(1)}$          |      | 0.55 |                                                                         | А    |

|                          |                                                                         | $R_{ILIM} = 45.3 \text{ k}\Omega, V_{VIN-OUT} = 5 \text{ V}$                                              | 1.72 | 2.05 | 2.38                                                                    |      |

| I <sub>SCL</sub>         | Short-circuit current limit (2)                                         | $R_{ILIM} = 100 \text{ k}\Omega, V_{VIN-OUT} = 5 \text{ V}$                                               | 3.14 | 3.56 | 3.98                                                                    | Α    |

|                          |                                                                         | $R_{ILIM} = 150 \text{ k}\Omega, V_{VIN-OUT} = 5 \text{ V}$                                               | 4.12 | 4.86 | 1.44<br>1.39<br>100<br>100<br>2.42<br>4.03<br>6<br>2.38<br>3.98<br>5.60 |      |

| RATIO <sub>FASTRIP</sub> | Fast-Trip comparator level w.r.t. overload current limit <sup>(1)</sup> | I <sub>FASTRIP</sub> : I <sub>OL</sub>                                                                    |      | 160% |                                                                         |      |

| V <sub>OpenILIM</sub>    | ILIM Open resistor detect threshold <sup>(1)</sup>                      | V <sub>ILIM</sub> Rising, R <sub>ILIM</sub> = OPEN                                                        |      | 3.1  |                                                                         | V    |

<sup>(1)</sup> These parameters are provided for reference only and do not constitute part of TI's published device specifications for purposes of TI's product warranty.

Product Folder Links: TPS2592BA TPS2592BL

SLVSCU2-DECEMBER 2014

<sup>(2)</sup> Pulsed testing techniques used during this test maintain junction temperature approximately equal to ambient temperature.

## **Electrical Characteristics (continued)**

-40°C  $\leq$  T<sub>J</sub>  $\leq$  125°C, VIN = 5 V, V<sub>EN /UVLO</sub> = 2 V, R<sub>ILIM</sub> = 100 k $\Omega$ , C<sub>dVdT</sub> = OPEN. All voltages referenced to GND (unless otherwise noted)

|                           | PARAMETER                            | TEST CONDITIONS                                                | MIN             | TYP                    | MAX | UNIT |

|---------------------------|--------------------------------------|----------------------------------------------------------------|-----------------|------------------------|-----|------|

| OUT (PASS F               | ET OUTPUT)                           |                                                                | ,               |                        |     |      |

| D                         | FET ON resistance                    | T <sub>J</sub> = 25°C                                          | 21              | 28                     | 33  | mΩ   |

| R <sub>DS(on)</sub>       | FET ON resistance                    | T <sub>J</sub> = 125°C                                         |                 | 39                     | 46  | mt7  |

| I <sub>OUT-OFF-LKG</sub>  | OUT Bias current in off state        | V <sub>EN/UVLO</sub> = 0 V, V <sub>OUT</sub> = 0 V (Sourcing)  | -5              | 0                      | 1   |      |

| I <sub>OUT-OFF-SINK</sub> | OUT Bias current in oil state        | V <sub>EN/UVLO</sub> = 0V, V <sub>OUT</sub> = 300 mV (Sinking) | 10              | 15                     | 20  | μA   |

| BFET (BLOCK               | (ING FET GATE DRIVER)                |                                                                | <u>.</u>        |                        |     |      |

| I <sub>BFET</sub>         | BFET Charging current <sup>(1)</sup> | V <sub>BFET</sub> = V <sub>OUT</sub>                           |                 | 2                      |     | μΑ   |

| $V_{BFETmax}$             | BFET Clamp voltage <sup>(1)</sup>    |                                                                |                 | V <sub>VIN</sub> + 6.4 |     | V    |

| R <sub>BFETdisch</sub>    | BFET Discharging resistance to GND   | V <sub>EN/UVLO</sub> = 0 V, I <sub>BFET</sub> = 100 mA         | 15              | 26                     | 36  | Ω    |

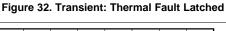

| TSD (THERMA               | AL SHUT DOWN)                        |                                                                |                 |                        | ,   |      |

| T <sub>SHDN</sub>         | TSD Threshold, rising <sup>(1)</sup> |                                                                |                 | 160                    |     | °C   |

| T <sub>SHDNhyst</sub>     | TSD Hysteresis <sup>(1)</sup>        |                                                                |                 | 10                     |     | °C   |

|                           | Thermal fault, latebad or autoratm   | TPS2592BL                                                      | L               | ATCHED                 |     |      |

|                           | Thermal fault: latched or autoretry  | TPS2592BA                                                      | AU <sup>-</sup> | TO-RETR                | Υ   |      |

8.6 Timing Requirements

|                                                                                      | PARAMETER                                 | TEST CONDITIONS                                                                       | MIN  | TYP | MAX                        | UNIT |

|--------------------------------------------------------------------------------------|-------------------------------------------|---------------------------------------------------------------------------------------|------|-----|----------------------------|------|

| T <sub>ON</sub>                                                                      | Turn-on delay <sup>(1)</sup>              | $EN/UVLO \rightarrow H$ to $I_{VIN}$ = 100 mA, 1-A resistive load at OUT              |      | 220 |                            | μs   |

| t <sub>OFFdly</sub>                                                                  | Turn Off delay <sup>(2)</sup>             | $EN\downarrow$ to BFET $\downarrow$ , $C_{BFET} = 0$                                  |      | 0.4 |                            | μs   |

| dV/dT (OU                                                                            | TPUT RAMP CONTROL)                        |                                                                                       |      |     |                            |      |

|                                                                                      |                                           | EN/UVLO $\rightarrow$ H to OUT = 4.9 V, $C_{dVdT} = 0$                                | 0.28 | 0.4 | 0.52                       |      |

| $t_{\text{dVdT}}$                                                                    | Output ramp time                          | EN/UVLO $\rightarrow$ H to OUT = 4.9 V,<br>$C_{dVdT} = 1 \text{ nF}^{(2)}$            |      | 5   |                            | ms   |

| ILIM (CUR                                                                            | RENT LIMIT PROGRAMMING)                   |                                                                                       |      |     |                            |      |

| t <sub>FastOffDly</sub>                                                              | Fast-Trip comparator delay <sup>(2)</sup> | I <sub>OUT</sub> > I <sub>FASTRIP</sub> to I <sub>OUT</sub> = 0 (Switch Off)          |      | 3   |                            | μs   |

| BFET (BL                                                                             | OCKING FET GATE DRIVER)                   |                                                                                       |      |     |                            |      |

|                                                                                      | BFET Turn-On duration (2)                 | $EN/UVLO \rightarrow H \text{ to } V_{BFET} = 12 \text{ V}, C_{BFET} = 1 \text{ nF}$  |      | 4.2 |                            |      |

| <sup>I</sup> BFET-ON                                                                 | BFET Turn-On duration (=)                 | $EN/UVLO \rightarrow H \text{ to } VB_{FET} = 12 \text{ V}, C_{BFET} = 10 \text{ nF}$ |      | 42  | 0.4 0.52<br>5 3 4.2 42 0.4 | ms   |

|                                                                                      | BFET Turn-Off duration (2)                | EN/UVLO → L to <sub>VBFET</sub> = 1 V, C <sub>BFET</sub> = 1 nF                       |      | 0.4 |                            |      |

| t <sub>OFFdly</sub> dV/dT (OUT  t <sub>dVdT</sub> ILIM (CURR t <sub>FastOffDly</sub> | BFE I Turn-Off duration (=)               | $EN/UVLO \rightarrow L$ to $V_{BFET} = 1 \text{ V}$ , $C_{BFET} = 10 \text{ nF}$      |      | 1.4 |                            | μs   |

<sup>(1)</sup> These parameters are provided for reference only and do not constitute part of TI's published device specifications for purposes of TI's product warranty.

Product Folder Links: TPS2592BA TPS2592BL

These parameters are provided for reference only and do not constitute part of Tl's published device specifications for purposes of Tl's product warranty.

SLVSCU2-DECEMBER 2014

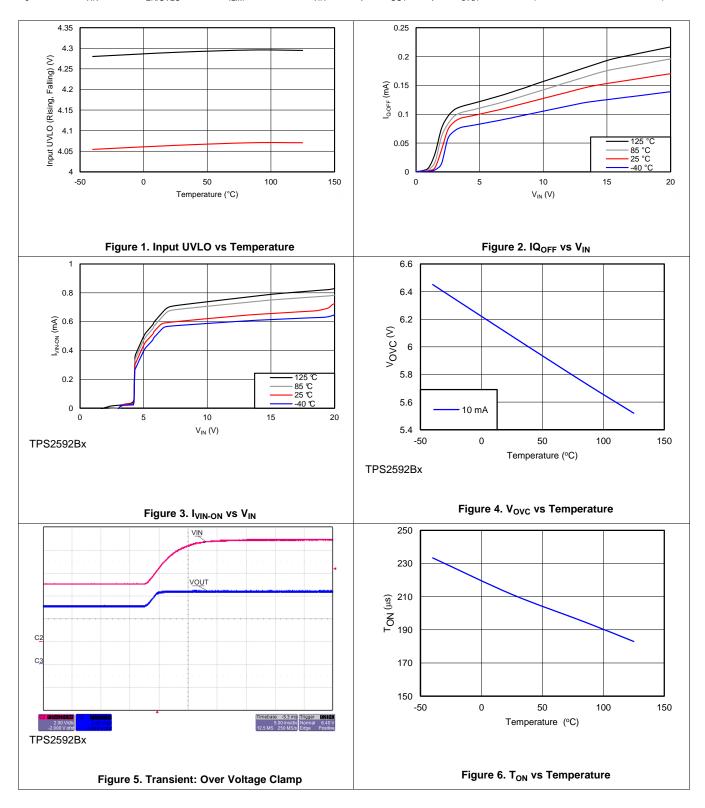

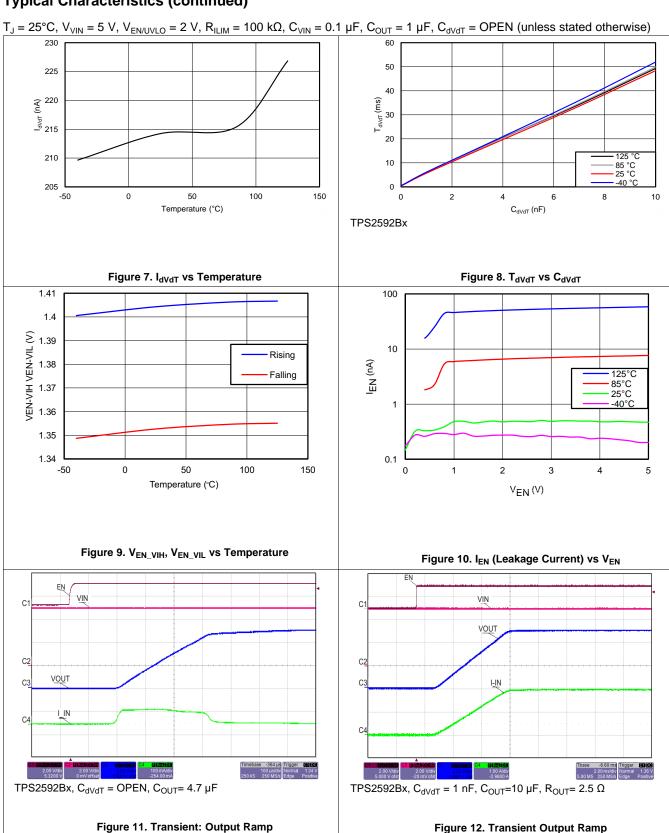

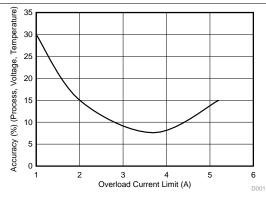

## 8.7 Typical Characteristics

$T_{J} = 25^{\circ}C,\ V_{VIN} = 5\ V,\ V_{EN/UVLO} = 2\ V,\ R_{ILIM} = 100\ k\Omega,\ C_{VIN} = 0.1\ \mu\text{F},\ C_{OUT} = 1\ \mu\text{F},\ C_{dVdT} = OPEN\ (unless stated otherwise)$

SLVSCU2-DECEMBER 2014 www.ti.com

# **NSTRUMENTS**

## **Typical Characteristics (continued)**

Submit Documentation Feedback

SLVSCU2-DECEMBER 2014

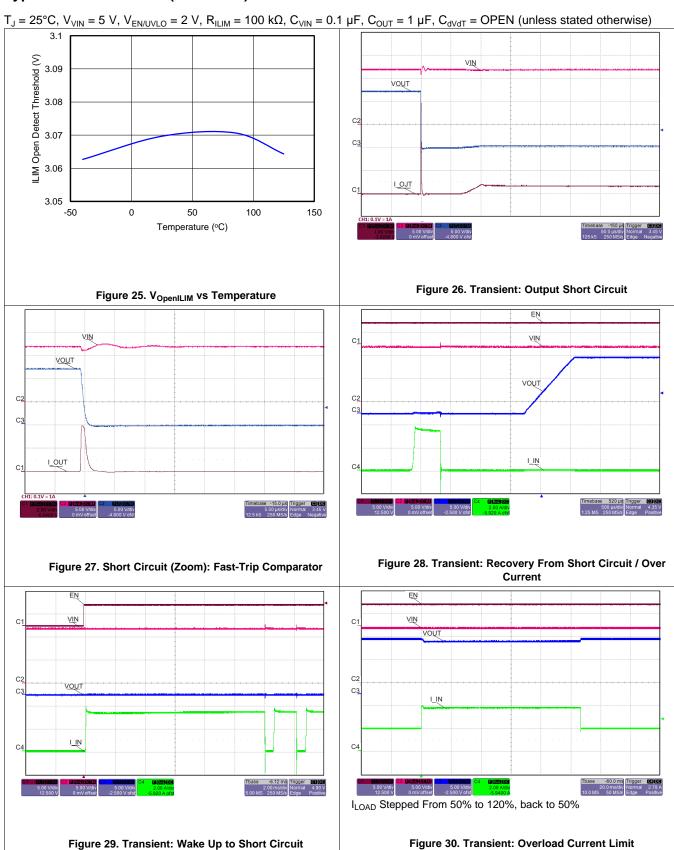

## **Typical Characteristics (continued)**

$T_{J} = 25^{\circ}\text{C}, \ V_{VIN} = 5 \ \text{V}, \ V_{EN/UVLO} = 2 \ \text{V}, \ R_{ILIM} = 100 \ \text{k}\Omega, \ C_{VIN} = 0.1 \ \mu\text{F}, \ C_{OUT} = 1 \ \mu\text{F}, \ C_{dVdT} = OPEN \ (unless stated otherwise)$ C: V<u>ou</u>t VOUT BFET I\_OUT EN↓ EN↓ Figure 14. Turn Off Delay to BFET Figure 13. Transient: Turn Off Delay 45 VIŅ 40 VOUT R<sub>DSON</sub> (mΩ) 30 32 BFET 25 20 0 50 100 150 Temperature (°C) VIN↓ Figure 16. R<sub>DSON</sub> vs Temperature Figure 15. Turn Off Delay to BFET 6  $R_{ILIM}$  = 150  $k\Omega$ 3.5 5 3  $R_{ILIM}$  = 100  $k\Omega$ (A) TUOV (A) TUOV<sup>3</sup> 2 125°C 85°C 25°C 2 1.5 25°C -40°C -40°C 0.5 1.5 0 0.5 1.5 V<sub>VIN-OUT</sub> (V) V<sub>VIN-OUT</sub> (V) 150 kΩ 100 kΩ Figure 17. I<sub>OUT</sub> vs V<sub>VIN-OUT</sub> Figure 18. I<sub>OUT</sub> vs V<sub>VIN-OUT</sub>

SLVSCU2 – DECEMBER 2014 www.ti.com

# TEXAS INSTRUMENTS

## **Typical Characteristics (continued)**

$T_{J} = 25^{\circ}C,\ V_{VIN} = 5\ V,\ V_{EN/UVLO} = 2\ V,\ R_{ILIM} = 100\ k\Omega,\ C_{VIN} = 0.1\ \mu\text{F},\ C_{OUT} = \underline{1}\ \mu\text{F},\ C_{dVdT} = OPEN\ (unless stated otherwise)$ 0 2 -, I<sub>SC</sub> (% Nomalized) -2 1.8  $R_{ILIM}$  = 45.3 k $\Omega$ (A) TUOVI IOL-150k ISC-150K-92B\_ 1.4 ISC-150K-92A\_ ِ 12- ك<u>\_</u> 1.2 85°C 25°C -14 -40°C -16 1.5 0 0.5 -50 0 50 100 150 Temperature (°C) V<sub>VIN-OUT</sub> (V) 150 kΩ 45.3 kΩ Figure 20. I<sub>OL</sub>, I<sub>SC</sub> vs Temperature Figure 19. I<sub>OUT</sub> vs V<sub>VIN-OUT</sub> 2 1 0 0 <sup>1</sup>OL, <sup>1</sup>SC (% Normalized) I<sub>SC</sub> (% Normalized) -2 -1 -2 -4 IOL-45.3k ISC-45.3K-92B\_ IOL-100K -3 -6 ISC-45.3K-92A ISC-100K-92B\_ 4-اح اح -8 ISC-100K-92A -10 -5 -12 -6 -50 0 50 100 150 -50 0 50 100 150 Temperature (°C) Temperature (°C) 100 kΩ 45.3 kΩ Figure 21. I<sub>OL</sub>, I<sub>SC</sub> vs Temperature Figure 22. I<sub>OL</sub>, I<sub>SC</sub> vs Temperature 0.9 0.58 0.85 0.57 0.8 0.56 OL-R-SHORT (A) O.55 0.54 0.53 0.53 0.6 0.52 0.55 0.51 0.5 0.5 -50 0 150 -50 0 50 100 150 50 100 Temperature (°C) Temperature (°C)  $R_{ILIM} = OPEN$  $R_{ILIM} = 0$ Figure 24.  $I_{OL-R-Open}$  vs Temperature Figure 23. I<sub>OL-R-Short</sub> vs Temperature

Submit Documentation Feedback

SLVSCU2-DECEMBER 2014

## **Typical Characteristics (continued)**

TEXAS INSTRUMENTS

SLVSCU2 – DECEMBER 2014 www.ti.com

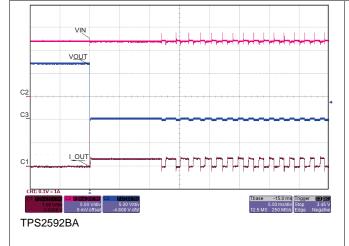

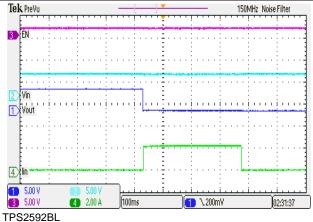

## **Typical Characteristics (continued)**

Figure 31. Transient: Thermal Fault Auto-Retry

Figure 34. Overload Current Limit vs R<sub>ILIM</sub>

Submit Documentation Feedback

SLVSCU2-DECEMBER 2014

## 9 Detailed Description

#### 9.1 Overview

The TPS2592xx is an e-fuse with integrated power switch that is used to manage current/voltage/start-up voltage ramp to a connected load. The device starts its operation by monitoring the VIN bus. When VIN exceeds the undervoltage-lockout threshold (VUVR), the device samples the EN/UVLO pin. A high level on this pin enables the internal MOSFET. As VIN rises, the internal MOSFET of the device will start conducting and allow current to flow from VIN to OUT. When EN/UVLO is held low (below VENF), internal MOSFET is turned off. User also has the ability to modify the output voltage ramp time by connecting a capacitor between dV/dT pin and GND.

After a successful start-up sequence, the device now actively monitors its load current and input voltage, ensuring that the adjustable overload current limit  $I_{OL}$  is not exceeded and input voltage spikes are safely clamped to  $V_{OVC}$  level at the output. This keeps the output device safe from harmful voltage and current transients. The device also has built-in thermal sensor. In the event device temperature ( $T_{J}$ ) exceeds  $T_{SHDN}$ , typically 160°C, the thermal shutdown circuitry will shut down the internal MOSFET thereby disconnecting the load from the supply. In TPS2592xL, the output will remain disconnected (MOSFET open) until power to device is recycled or EN/UVLO is toggled (pulled low and then high). The TPS2592xA device will remain off during a cooling period until device temperature falls below  $T_{SHDN}$  – 10°C, after which it will attempt to restart. This ON and OFF cycle will continue until fault is cleared.

## 9.2 Functional Block Diagram

## 9.3 Feature Description

#### 9.3.1 GND

This is the most negative voltage in the circuit and is used as a reference for all voltage measurements unless otherwise specified.

# TEXAS INSTRUMENTS

#### **Feature Description (continued)**

#### 9.3.2 VIN

Input voltage to the TPS2592Bx. A ceramic bypass capacitor close to the device from VIN to GND is recommended to alleviate bus transients. The recommended operating voltage range is 4.5 V to 5.5 V for TPS2592Bx. The device can continuously sustain a voltage of 20 V on VIN pin. However, above the recommended maximum bus voltage, the device will be in over-voltage protection (OVP) mode, limiting the output voltage to  $V_{OVC}$ . The power dissipation in OVP mode is  $P_{D_OVP} = (V_{VIN} - V_{OVC}) \times I_{OUT}$ , which can potentially heat up the device and cause thermal shutdown.

#### 9.3.3 dV/dT

Connect a capacitor from this pin to GND to control the slew rate of the output voltage at power-on. This pin can be left floating to obtain a predetermined slew rate (minimum  $T_{dVdT}$ ) on the output. Equation governing slew rate at start-up is shown below:

$$\frac{dV_{OUT}}{dt} = \frac{I_{dVdT} \times GAIN_{dVdT}}{C_{dVdT} + C_{INT}}$$

(1)

Where:

$$\begin{split} &I_{dVdT} = 220 \text{ nA (TYP)} \\ &C_{INT} = 70 \text{ pF (TYP)} \\ &GAIN_{dVdT} = 4.85 \\ &\frac{dV_{OUT}}{dT} = \text{ Desired output slew rate} \end{split}$$

The total ramp time (T<sub>dVdT</sub>) for 0 to VIN can be calculated using the following equation:

$$T_{dVdT} = 10^6 \times V_{IN} \times (C_{dVdT} + 70 \text{ pF})$$

(2)

For details on how to select an appropriate charging time/rate, refer to the applications section: Setting Output Voltage Ramp Time  $(T_{dVdT})$

## 9.3.4 BFET

Connect this pin to an external NFET that can be used to disconnect input supply from rest of the system in the event of power failure at VIN. The BFET pin is controlled by either UVLO event or EN/UVLO (see Table 1). BFET can source charging current of 2  $\mu$ A (TYP) and sink (discharge) current from the gate of the external FET via a 26- $\Omega$  internal discharge resistor to initiate fast turn-off, typically <1  $\mu$ s. Due to 2  $\mu$ A charging current, it is recommended to use >10 M $\Omega$  impedance when probing the BFET node.

Table 1.

| EN/UVLO > V <sub>ENR</sub> | VIN>V <sub>UVR</sub> | BFET MODE |

|----------------------------|----------------------|-----------|

| Н                          | Н                    | Charge    |

| X                          | L                    | Discharge |

| L                          | X                    | Discharge |

#### 9.3.5 EN/UVLO

As an input pin, it controls both the ON/OFF state of the internal MOSFET and that of the external blocking FET. In its high state, the internal MOSFET is enabled and charging begins for the gate of external FET. A low on this pin will turn off the internal MOSFET and pull the gate of the external FET to GND via the built-in discharge resistor. High and Low levels are specified in the parametric table of the datasheet. The EN/UVLO pin is also used to clear a thermal shutdown latch in the TPS2592xL by toggling this pin  $(H\rightarrow L)$ .

The internal de-glitch delay on EN/UVLO falling edge is intentionally kept low (1 us typical) for quick detection of power failure. When used with a resistor divider from supply to EN/UVLO to GND, power-fail detection on EN/UVLO helps in quick turn-off of the BFET driver, thereby stopping the flow of reverse current (see typical application diagram, Figure 42). For applications where a higher de-glitch delay on EN/UVLO is desired, or when the supply is particularly noisy, it is recommended to use an external bypass capacitor from EN/UVLO to GND.

4 Submit Documentation Feedback

SLVSCU2-DECEMBER 2014

#### 9.3.6 ILIM

The device continuously monitors the load current and keeps it limited to the value programmed by  $R_{ILIM}$ . After start-up event and during normal operation, current limit is set to  $I_{OI}$  (over-load current limit).

$$I_{OL} = (0.7 + 3 \times 10^{-5} \times R_{ILIM})$$

(3)

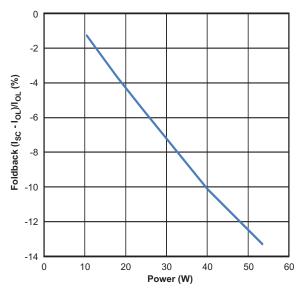

When power dissipation in the internal MOSFET [ $P_D = (V_{VIN} - V_{OUT}) \times I_{OUT}$ ] exceeds 10 W, there is a 2% – 12% thermal foldback in the current limit value so that  $I_{OL}$  drops to  $I_{SC}$ . In each of the two modes, MOSFET gate voltage is regulated to throttle short-circuit and overload current flowing to the load. Eventually, the device shuts down due to over temperature.

Figure 35. Thermal Foldback in Current Limit

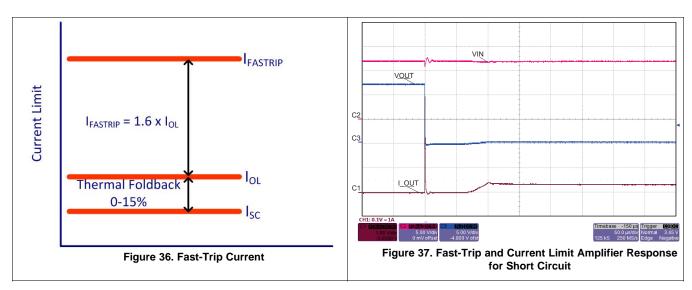

During a transient short circuit event, the current through the device increases very rapidly. The current-limit amplifier cannot respond very quickly to this event due to its limited bandwidth. Therefore, the TPS2592 incorporates a fast-trip comparator, which shuts down the pass device very quickly when  $I_{OUT} > I_{FASTRIP}$ , and terminates the rapid short-circuit peak current. The trip threshold is set to 60% higher than the programmed overload current limit ( $I_{FASTRIP} = 1.6 \times I_{OL}$ ). After the transient short-circuit peak current has been terminated by the fast-trip comparator, the current limit amplifier smoothly regulates the output current to  $I_{OL}$  (see figure below).

#### TPS2592BA, TPS2592BL

SLVSCU2-DECEMBER 2014 www.ti.com

#### 9.4 Device Functional Modes

The TPS2592xx is a hot-swap controller with integrated power switch that is used to manage current/voltage/start-up voltage ramp to a connected load. The device starts its operation by monitoring the VIN bus. When  $V_{VIN}$  exceeds the undervoltage-lockout threshold ( $V_{UVR}$ ), the device samples the EN/UVLO pin. A high level on this pin enables the internal MOSFET and also start charging the gate of external blocking FET (if connected) via the BFET pin. As VIN rises, the internal MOSFET of the device and external FET (if connected) will start conducting and allow current to flow from VIN to OUT. When EN/UVLO is held low (that is, below V<sub>ENF</sub>), the internal MOSFET is turned off and BFET pin is discharged, thereby, blocking the flow of current from VIN to OUT. User also has the ability to modify the output voltage ramp time by connecting a capacitor between dV/dT pin and GND.

Having successfully completed its start-up sequence, the device now actively monitors its load current and input voltage, ensuring that the adjustable overload current limit I<sub>OL</sub> is not exceeded and input voltage spikes are safely clamped to V<sub>OVC</sub> level at the output. This keeps the output device safe from harmful voltage and current transients. The device also has built-in thermal sensor. In the event device temperature (T<sub>J</sub>) exceeds T<sub>SHDN</sub>, typically 160°C, the thermal shutdown circuitry will shut down the internal MOSFET thereby disconnecting the load from the supply. In the TPS2592xL, the output will remain disconnected (MOSFET open) until power to device is recycled or EN/UVLO is toggled (pulled low and then high). The TPS2592xA device will remain off during a cooling period until device temperature falls below T<sub>SHDN</sub> - 10°C, after which it will attempt to restart. This ON and OFF cycle will continue until fault is cleared.

Submit Documentation Feedback

www ti com

SLVSCU2-DECEMBER 2014

## 10 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

## 10.1 Application Information

The TPA2592xx is a smart eFuse. It is typically used for Hot-Swap and Power rail protection applications. It operates from 4.5 V to 18 V with programmable current limit and undervoltage protection. The device aids in controlling the in-rush current and provides precise current limiting during overload conditions for systems such as Set-Top-Box, DTVs, Gaming Consoles, SSDs/HDDs and Smart Meters. The device also provides robust protection for multiple faults on the sub-system rail.

The following design procedure can be used to select component values for the device. Alternatively, the WEBENCH® software may be used to generate a complete design. The WEBENCH® software uses an iterative design procedure and accesses a comprehensive database of components when generating a design. Additionally, a spreadsheet design tool TPS2592 Design Calculator (SLUC571) is available on web folder. This section presents a simplified discussion of the design process.

## 10.2 Typical Applications

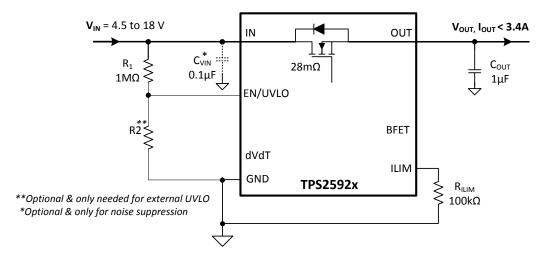

## 10.2.1 Simple 3.7-A eFuse Protection for Set Top Boxes

Figure 38. Typical Application Schematic: Simple 3.7-A e-Fuse for STBs

## 10.2.1.1 Design Requirements

**Table 2. Design Parameters**

| DESIGN PARAMETER                                   | EXAMPLE VALUE                     |

|----------------------------------------------------|-----------------------------------|

| Input voltage range, V <sub>IN</sub>               | 5 V                               |

| Undervoltage lockout set point, V <sub>(UV)</sub>  | Default: V <sub>UVR</sub> = 4.3 V |

| Overvoltage protection set point , $V_{(OV)}$      | Default: V <sub>OVC</sub> = 6.1 V |

| Load at Start-Up , R <sub>L(SU)</sub>              | 2 Ω                               |

| Current limit, I <sub>OL</sub> = I <sub>ILIM</sub> | 3.7 A                             |

| Load capacitance , C <sub>OUT</sub>                | 1 μF                              |

| Maximum ambient temperatures , T <sub>A</sub>      | 85°C                              |

Product Folder Links: TPS2592BA TPS2592BL

## TEXAS INSTRUMENTS

#### 10.2.1.2 Detailed Design Procedure

The following design procedure can be used to select component values for the TPS2592xx.

#### 10.2.1.2.1 Step by Step Design Procedure

This design procedure below seeks to control the junction temperature of device under both static and transient conditions by proper selection of output ramp-up time and associated support components. The designer can adjust this procedure to fit the application and design criteria.

#### 10.2.1.2.2 Programming the Current-Limit Threshold: R<sub>ILIM</sub> Selection

The R<sub>ILIM</sub> resistor at the ILIM pin sets the over load current limit, this can be set using Equation 4.

$$R_{\rm ILIM} = \frac{I_{\rm ILIM} - 0.7}{3 \times 10^{-5}} \tag{4}$$

For  $I_{OL} = I_{ILIM} = 3.7$  A, from equation 4,  $R_{ILIM} = 100$  k $\Omega$ . Choose closest standard value resistor with 1% tolerance.

#### 10.2.1.2.3 Undervoltage Lockout Set Point

The undervoltage lockout (UVLO) trip point is adjusted using the external voltage divider network of  $R_1$  and  $R_2$  as connected between IN, EN/UVLO and GND pins of the device. The values required for setting the undervoltage are calculated solving Equation 5.

$$V_{(UV)} = \frac{R_1 + R_2}{R_2} \times V_{ENR}$$

(5)

Where  $V_{ENR} = 1.4 \text{ V}$ , is enable voltage rising threshold.

Since  $R_1$  and  $R_2$  will leak the current from input supply (VIN), these resistors should be selected based on the acceptable leakage current from input power supply (VIN). The current drawnby  $R_1$  and  $R_2$  from the power supply { $I_{R12} = V_{IN}/(R_1 + R_2)$ }.

However, leakage currents due to external active components connected to the resistor string can add error to these calculations. So, the resistor string current, I<sub>R12</sub> must be chosen to be 20x greater than the leakage current expected.

For default UVLO of  $V_{UVR}$  = 4.3 V, select  $R_2$  = OPEN, and  $R_1$  = 1 M $\Omega$ . Since EN/UVLO pin is rated only to 7 V, it cannot be connected directly to  $V_{IN}$  > 7 V. It has to be connected through  $R_1$  = 1 M $\Omega$  only, so that the pull-up current for EN/UVLO pin is limited to < 20  $\mu$ A.

The power failure threshold is detected on the falling edge of supply. This threshold voltage is 4% lower than the rising threshold,  $V_{INR}$ . This is calculated using Equation 6.

$$V_{(PFAIL)} = 0.96 \times V_{UVR}$$

(6)

Where  $V_{UVR}$  is 4.3V, Power fail threshold set is:  $V_{(PFAIL)} = 4.1 \text{ V}$

## 10.2.1.2.4 Setting Output Voltage Ramp Time (T<sub>dVdT</sub>)

For a successful design, the junction temperature of device should be kept below the absolute-maximum rating during both dynamic (start-up) and steady state conditions. Dynamic power stresses often are an order of magnitude greater than the static stresses, so it is important to determine the right start-up time and in-rush current limit required with system capacitance to avoid thermal shutdown during start-up with and without load.

The ramp-up capacitor  $C_{dVdT}$  needed is calculated considering the two possible cases:

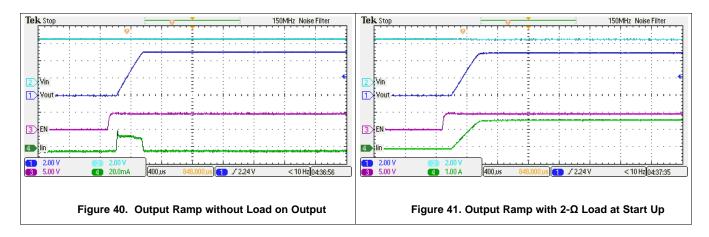

## 10.2.1.2.4.1 Case 1: Start-up without Load: Only Output Capacitance C<sub>OUT</sub> Draws Current During Start-up

During start-up, as the output capacitor charges, the voltage difference as well as the power dissipated across the internal FET decreases. The average power dissipated in the device during start-up is calculated using Equation 8.

For TPS2592xx, the inrush current is determined as,

$$I_{(INRUSH)} = C_{(OUT)} \times \frac{V_{(IN)}}{T_{dVdT}}$$

(7)

8 Submit Documentation Feedback

SLVSCU2-DECEMBER 2014

Power dissipation during start-up is:

$$P_{D(INRUSH)} = 0.5 \times V_{(IN)} \times I_{(INRUSH)}$$

(8)

Equation 8 assumes that load does not draw any current until the output voltage has reached its final value.

#### 10.2.1.2.4.2 Case 2: Start-up with Load: Output Capacitance C<sub>OUT</sub> and Load Draws Current During Start-up

When load draws current during the turn-on sequence, there will be additional power dissipated. Considering a resistive load during start-up ( $R_{L(SU)}$ ), load current ramps up proportionally with increase in output voltage during  $T_{dVdT}$  time. The average power dissipation in the internal FET during charging time due to resistive load is given by:

$$P_{D(LOAD)} = \left(\frac{1}{6}\right) \times \frac{V^2(IN)}{R_{L(SU)}}$$

(9)

Total power dissipated in the device during startup is:

$$P_D(STARTUP) = P_D(INRUSH) + P_D(LOAD)$$

(10)

Total current during startup is given by:

$$I(STARTUP) = I(INRUSH) + I_L(t)$$

(11)

If I<sub>(STARTUP)</sub> > I<sub>OL</sub>, the device limits the current to I<sub>OL</sub> and the current limited charging time is determined by:

$$T_{\text{dVdT}(\text{Current-Limited})} = C_{\text{OUT}} \times R_{\text{L}(\text{SU})} \times \left[ \frac{I_{\text{OL}}}{I_{\text{(INRUSH)}}} - 1 + LN \left( \frac{I_{\text{(INRUSH)}}}{I_{\text{OL}} - \frac{V_{\text{(IN)}}}{R_{\text{L}(\text{SU})}}} \right) \right]$$

$$(12)$$

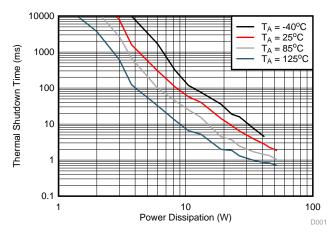

The power dissipation, with and without load, for selected start-up time should not exceed the shutdown limits as shown in Figure 39.

Figure 39. Thermal Shutdown Limit Plot

For the design example under discussion, select ramp-up capacitor  $C_{dVdT}$  = OPEN. Then, using Equation 2.

$$T_{dVdT} = 10^6 \times 5 \times (0 + 70 \text{ pF}) = 350 \text{ }\mu\text{s}$$

(13)

The inrush current drawn by the load capacitance (C<sub>OUT</sub>) during ramp-up using Equation 7.

$$I_{\text{(INRUSH)}} = 1 \,\mu\text{F} \times \frac{5}{350 \,\mu\text{s}} = 14.3 \,\text{mA}$$

(14)

The inrush Power dissipation is calculated, using Equation 8.

$$P_{D(INRUSH)} = 0.5 \times 5 \times 14.3 \text{ m} = 36 \text{ mW}$$

(15)

SLVSCU2 – DECEMBER 2014 www.ti.com

For 36 mW of power loss, the thermal shut down time of the device should not be less than the ramp-up time  $T_{dVdT}$  to avoid the false trip at maximum operating temperature. From thermal shutdown limit graph Figure 39 at  $T_A = 85$ °C, for 36 mW of power, the shutdown time is infinite. So it is safe to use 350 µs as start-up time without any load on output.

Considering the start-up with load 2  $\Omega$ , the additional power dissipation, when load is present during start up is calculated, using Equation 9.

$$P_{D(LOAD)} = \frac{5 \times 5}{6 \times 2} = 2.08 \text{ W}$$

(16)

The total device power dissipation during start up, using Equation 10 is:

$$P_{D(STARTUP)} = 2.08 + 36 \text{ m} = 2.44 \text{ W}$$

(17)

From thermal shutdown limit graph at  $T_A = 85^{\circ}C$ , the thermal shutdown time for 2.44 W is more than 100 ms. So it is well within acceptable limits to use no external capacitor ( $C_{dV/dT}$ ) with start-up load of 2  $\Omega$ .

If, due to large  $C_{OUT}$ , there is a need to decrease the power loss during start-up, it can be done with increase of  $C_{dVdT}$  capacitor.

## 10.2.1.3 Support Component Selection - C<sub>VIN</sub>

$C_{VIN}$  is a bypass capacitor to help control transient voltages, unit emissions, and local supply noise. Where acceptable, a value in the range of 0.001  $\mu F$  to 0.1  $\mu F$  is recommended for  $C_{VIN}$ .

#### 10.2.1.4 Application Curves

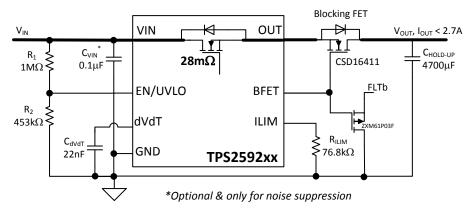

## 10.2.2 Inrush and Reverse Current Protection for Hold-Up Capacitor Application (e.g., SSD)

Figure 42. Inrush and Reverse Current Protection for Hold-Up Capacitor Application (e.g., SSD) (TPS2592 UVLO is used as power fail comparator)

20

SLVSCU2-DECEMBER 2014

#### 10.2.2.1 Design Requirements

#### **Table 3. Design Parameters**

| DESIGN PARAMETER                                   | EXAMPLE VALUE                     |

|----------------------------------------------------|-----------------------------------|

| Input voltage range, V <sub>IN</sub>               | 5 V                               |

| Undervoltage lockout set point, V <sub>(UV)</sub>  | 4.5 V                             |

| Overvoltage protection set point , $V_{(OV)}$      | Default: V <sub>OVC</sub> = 6.1 V |

| Load at Start-Up , R <sub>L(SU)</sub>              | 1000 Ω                            |

| Current limit, I <sub>OL</sub> = I <sub>ILIM</sub> | 3 A                               |

| Load capacitance , C <sub>OUT</sub>                | 4700 μF                           |

| Maximum ambient temperatures , T <sub>A</sub>      | 85°C                              |

#### 10.2.2.2 Detailed Design Procedure

#### 10.2.2.2.1 Programming the Current-Limit Threshold: R<sub>ILIM</sub> Selection

The R<sub>ILIM</sub> resistor at the ILIM pin sets the over load current limit, this can be set using Equation 4.

For  $I_{OL} = I_{ILIM} = 3$  A, from equation 4,  $R_{ILIM} = 76.8$  k $\Omega$ , choose closest standard value resistor with 1% tolerance.

#### 10.2.2.2.2 Undervoltage Lockout Set Point

The undervoltage lockout (UVLO) trip point is adjusted using the external voltage divider network of R<sub>1</sub> and R<sub>2</sub> as connected between IN, EN/UVLO and GND pins of the device. The values required for setting the undervoltage are calculated solving Equation 5.

For UVLO of  $V_{(UV)} = 4.5 \text{ V}$ , select  $R_2 = 453 \text{ k}\Omega$ , and  $R_1 = 1 \text{ M}\Omega$ .

The power failure threshold is detected on the falling edge of supply. This threshold voltage is 4% lower than the rising threshold,  $V_{(UV)}$ . This is calculated using Equation 6.

Where  $V_{(UV)} = 4.5 \text{ V}$ , Power fail threshold set is :  $V_{(PFAIL)} = 4.33 \text{ V}$

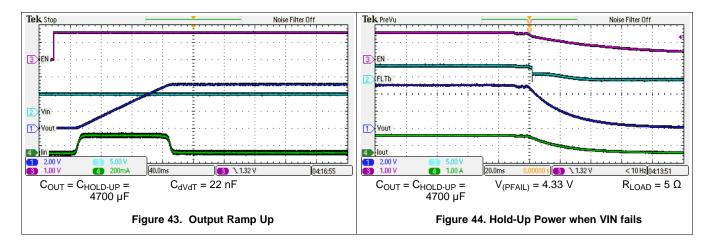

#### 10.2.2.2.3 Setting Output Voltage Ramp Time (T<sub>dVdT</sub>)

For a successful design, the junction temperature of device should be kept below the absolute-maximum rating during both dynamic (start-up) and steady state conditions. Dynamic power stresses often are an order of magnitude greater than the static stresses, so it is important to determine the right start-up time and in-rush current limit required with system capacitance to avoid thermal shutdown during start-up with and without load.

For the design example under discussion, select ramp-up capacitor  $C_{dVdT} = 22$  nF. Then, using Equation 2.

$$T_{dVdT} = 10^6 \text{ x 5 x } (22 \text{ nF} + 70 \text{ pF}) = 110 \text{ ms}$$

(18)

The inrush current drawn by the load capacitance (C<sub>OUT</sub>) during ramp-up using Equation 7.

$$I_{\text{(INRUSH)}} = 4700 \,\mu\text{F} \times \frac{5}{110 \,\text{ms}} = 213 \,\text{mA}$$

(19)

The inrush Power dissipation is calculated, using Equation 8.

$$P_{D(INRUSH)} = 0.5 \times 5 \times 213 \text{ m} = 533 \text{ mW}$$

(20)

Considering the start-up with load 1000  $\Omega$ , the additional power dissipation, when load is present during start up is calculated, using Equation 9.

$$P_{D(LOAD)} = \frac{5 \times 5}{6 \times 1000} = 4.2 \text{ mW}$$

(21)

The total device power dissipation during start up is:

$$P_{D(STARTUP)} = 533 + 4.2 = 537 \text{ mW}$$

(22)

From thermal shutdown limit graph at  $T_A = 85$ °C, the thermal shutdown time for 537 mW is more than 300 ms. So the device will start safely.

SLVSCU2 – DECEMBER 2014 www.ti.com

## 10.2.2.3 Support Component Selection - CVIN

$C_{VIN}$  is a bypass capacitor to help control transient voltages, unit emissions, and local supply noise. Where acceptable, a value in the range of 0.001  $\mu F$  to 0.1  $\mu F$  is recommended for  $C_{VIN}$ .

## 10.2.2.4 Application Curves

2 Submit Documentation Feedback

TPS2592BA, TPS2592BL

SLVSCU2 - DECEMBER 2014

## 10.3 Maximum Device Power Dissipation Considerations

To prevent damage to the TPS2592x, it is necessary to keep internal power dissipation ( $P_D$ ) below the levels specified in below Table. The power dissipation is defined as ( $P_D = (V_{IN} - V_{OUT}) \times I_{OUT}$ ).

|                                |                                | MIN | MAX | UNIT        |

|--------------------------------|--------------------------------|-----|-----|-------------|

| Marriago de Darros Dispiration | -40°C ≤ T <sub>A</sub> ≤ +85°C |     | 40  | <b>10</b> / |

| Maximum Power Dissipation      | 0°C ≤ T <sub>A</sub> ≤ +85°C   |     | 50  | W           |

During normal operation  $P_D$  is low ( typically <  $\frac{1}{2}$  Watt) because the FET is fully on with low ( $V_{IN}-V_{OUT}$ ). However, during short circuit and surge protection the FET may be only partially on and ( $V_{IN}-V_{OUT}$ ) can be high.

## Example 1: Short Circuit on Output $\rightarrow$ V<sub>IN</sub> = 5 V, I<sub>LIMIT</sub> = 5 A. T<sub>J</sub> = -40°C

- P<sub>D</sub> = 5 V x 5 A = 25 W

- OK  $\rightarrow$  (P<sub>D</sub> = 25 W) < (P<sub>D\_MAX</sub> = 40 W)

Example 2: Surge Clamp  $\rightarrow$  V<sub>IN</sub> = 5 V, I<sub>LIMIT</sub> = 3.7 A. T<sub>J</sub> = 0°C, V<sub>SURGE</sub> = 19 V, V<sub>CLAMP</sub> = 6.1 V

- $P_D = (19 6.1) \times 3 A = 47.7 \text{ Watt}$

- OK at  $T_J = 0$ °C  $\rightarrow$  ( $P_D = 47.7$  W) < ( $P_{D\_MAX}$  at 0°C = 50 W)

- NOT OK at  $-40^{\circ}\text{C} \rightarrow (P_D = 47.7 \text{ W}) > (P_{D \text{ MAX}} \text{ at } -40^{\circ}\text{C} = 40 \text{ W})$

# TEXAS INSTRUMENTS

## 11 Power Supply Recommendations

The device is designed for supply voltage range of 4.5 V  $\leq$  V<sub>IN</sub>  $\leq$  18 V. If the input supply is located more than a few inches from the device an input ceramic bypass capacitor higher than 0.1  $\mu$ F is recommended. Power supply should be rated higher than the current limit set to avoid voltage droops during over current and short-circuit conditions.

#### 11.1 Transient Protection

In case of short circuit and over load current limit, when the device interrupts current flow, input inductance generates a positive voltage spike on the input and output inductance generates a negative voltage spike on the output. The peak amplitude of voltage spikes (transients) is dependent on value of inductance in series to the input or output of the device. Such transients can exceed the *Absolute Maximum Ratings* of the device if steps are not taken to address the issue.

Typical methods for addressing transients include

- Minimizing lead length and inductance into and out of the device

- Using large PCB GND plane

- Schottky diode across the output to absorb negative spikes

- A low value ceramic capacitor ( $C_{(IN)} = 0.001 \, \mu\text{F}$  to 0.1  $\mu\text{F}$ ) to absorb the energy and dampen the transients. The approximate value of input capacitance can be estimated with Equation 23.

$$V_{SPIKE(Absolute)} = V_{(IN)} + I_{(LOAD)} \times \sqrt{\frac{L_{(IN)}}{C_{(IN)}}}$$

(23)

#### Where:

- V<sub>(IN)</sub> is the nominal supply voltage

- I<sub>(LOAD)</sub> is the load current,

- L<sub>(IN)</sub> equals the effective inductance seen looking into the source

- C<sub>(IN)</sub> is the capacitance present at the input

Some applications may require the addition of a Transient Voltage Suppressor (TVS) to prevent transients from exceeding the *Absolute Maximum Ratings* of the device.

The circuit implementation with optional protection components (a ceramic capacitor, TVS and schottky diode) is shown in Figure 45.

Figure 45. Circuit Implementation with Optional Protection Components

## 11.2 Output Short-Circuit Measurements

It is difficult to obtain repeatable and similar short-circuit testing results. Source bypassing, input leads, circuit layout and component selection, output shorting method, relative location of the short, and instrumentation all contribute to variation in results. The actual short itself exhibits a certain degree of randomness as it microscopically bounces and arcs. Care in configuration and methods must be used to obtain realistic results. Do not expect to see waveforms exactly like those in the data sheet; every setup differs.

24

SLVSCU2-DECEMBER 2014

## 12 Layout

## 12.1 Layout Guidelines

- For all applications, a 0.01-uF or greater ceramic decoupling capacitor is recommended between IN terminal and GND. For hot-plug applications, where input power path inductance is negligible, this capacitor can be eliminated/minimized.

- The optimum placement of decoupling capacitor is closest to the IN and GND terminals of the device. Care

must be taken to minimize the loop area formed by the bypass-capacitor connection, the IN terminal, and the

GND terminal of the IC. See Figure 46 for a PCB layout example.

- High current carrying power path connections should be as short as possible and should be sized to carry at least twice the full-load current.

- The GND terminal must be tied to the PCB ground plane at the terminal of the IC. The PCB ground should be a copper plane or island on the board.

- Locate all support components: R<sub>ILIM</sub>, C<sub>dVdT</sub> and resistors for EN/UVLO, close to their connection pin. Connect

the other end of the component to the GND pin of the device with shortest trace length. The trace routing for

the R<sub>ILIM</sub> and C<sub>dVdT</sub> components to the device should be as short as possible to reduce parasitic effects on

the current limit and soft start timing. These traces should not have any coupling to switching signals on the

board.

- Protection devices such as TVS, snubbers, capacitors, or diodes should be placed physically close to the

device they are intended to protect, and routed with short traces to reduce inductance. For example, a

protection Schottky diode is recommended to address negative transients due to switching of inductive loads,

and it should be physically close to the OUT pins.

- Obtaining acceptable performance with alternate layout schemes is possible; however this layout has been shown to produce good results and is intended as a guideline.

## 12.2 Layout Example

Top layer

Bottom layer signal ground plane

O Via to signal ground plane

\* Optional: Needed only to suppress the transients caused by inductive load switching

Figure 46. Layout Example

Submit Documentation Feedback

SLVSCU2 – DECEMBER 2014 www.ti.com

## 13 Device and Documentation Support

## 13.1 Device Support

## 13.1.1 Third-Party Products Disclaimer

TI'S PUBLICATION OF INFORMATION REGARDING THIRD-PARTY PRODUCTS OR SERVICES DOES NOT CONSTITUTE AN ENDORSEMENT REGARDING THE SUITABILITY OF SUCH PRODUCTS OR SERVICES OR A WARRANTY, REPRESENTATION OR ENDORSEMENT OF SUCH PRODUCTS OR SERVICES, EITHER ALONE OR IN COMBINATION WITH ANY TI PRODUCT OR SERVICE.

#### 13.2 Related Links

The table below lists quick access links. Categories include technical documents, support and community resources, tools and software, and quick access to sample or buy.

Table 4. Related Links

| PARTS     | PRODUCT FOLDER        | SAMPLE & BUY | TECHNICAL DOCUMENTS | TOOLS &<br>SOFTWARE | SUPPORT & COMMUNITY |

|-----------|-----------------------|--------------|---------------------|---------------------|---------------------|

| TPS2592BA | Click here            | Click here   | Click here          | Click here          | Click here          |

| TPS2592BL | Click here Click here |              | Click here          | Click here          | Click here          |

## 13.3 Trademarks

PowerPAD is a trademark of Texas Instruments.

WEBENCH is a registered trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

## 13.4 Electrostatic Discharge Caution

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## 13.5 Glossary

SLYZ022 — TI Glossarv.

This glossary lists and explains terms, acronyms, and definitions.

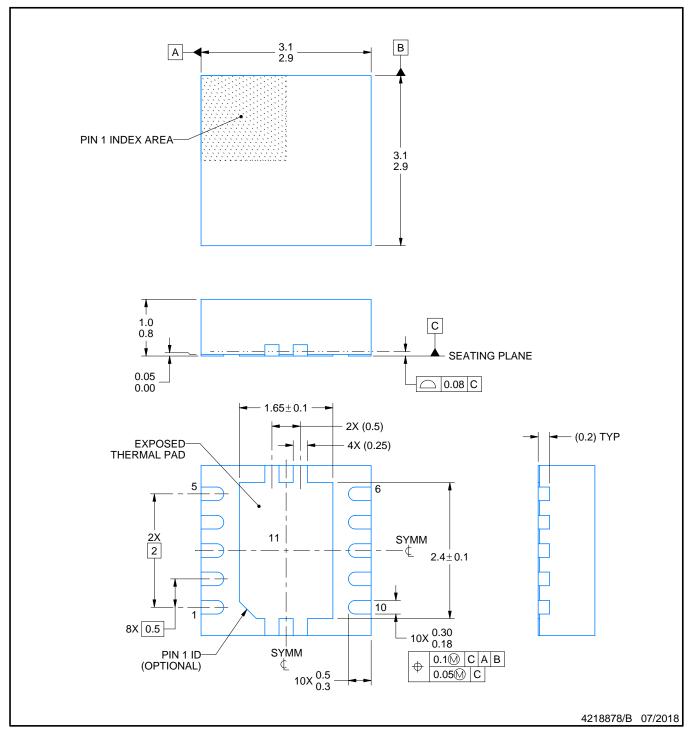

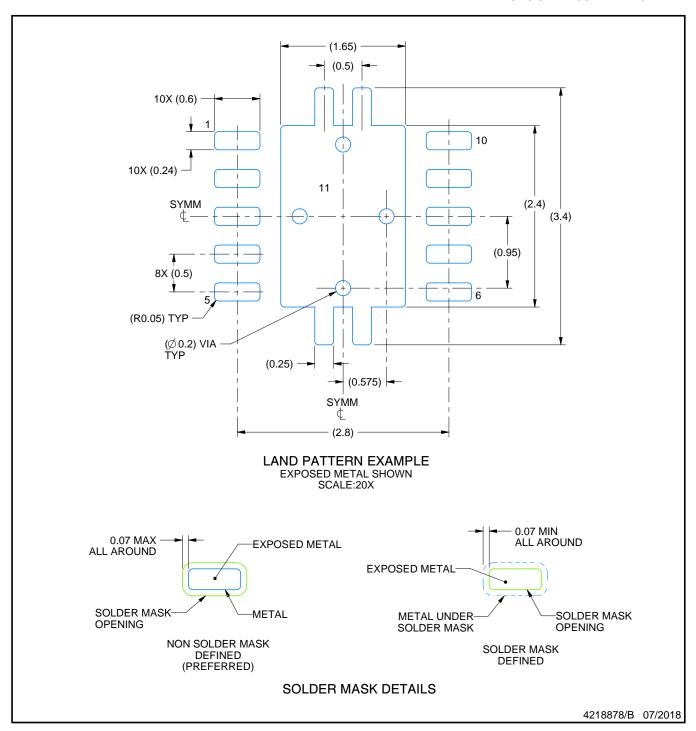

## 14 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

Product Folder Links: TPS2592BA TPS2592BL

www.ti.com 28-Oct-2023

#### PACKAGING INFORMATION

| Orderable Device | Status (1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp      | Op Temp (°C) | Device Marking (4/5) | Samples |

|------------------|------------|--------------|--------------------|------|----------------|--------------|-------------------------------|--------------------|--------------|----------------------|---------|

| TPS2592BADRCR    | NRND       | VSON         | DRC                | 10   | 3000           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 125   | 2592BA               |         |

| TPS2592BADRCT    | NRND       | VSON         | DRC                | 10   | 250            | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 125   | 2592BA               |         |

| TPS2592BLDRCR    | NRND       | VSON         | DRC                | 10   | 3000           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 125   | 2592BL               |         |

| TPS2592BLDRCT    | NRND       | VSON         | DRC                | 10   | 250            | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 125   | 2592BL               |         |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

**Green:** TI defines "Green" to mean the content of Chlorine (Cl) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

# **PACKAGE OPTION ADDENDUM**

www.ti.com 28-Oct-2023

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

www.ti.com 20-Apr-2023

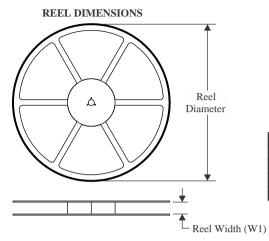

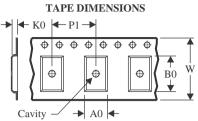

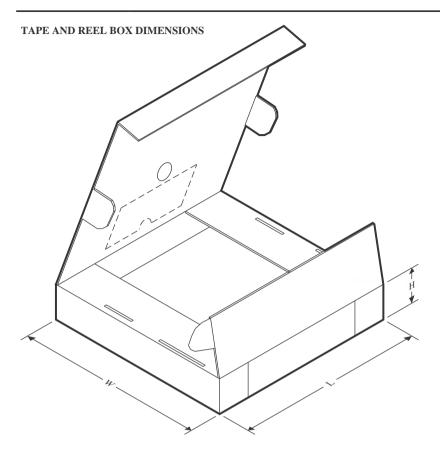

## TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

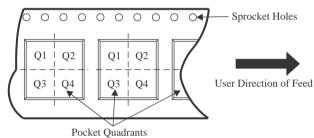

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device        | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|---------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TPS2592BADRCR | VSON            | DRC                | 10 | 3000 | 330.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

| TPS2592BADRCR | VSON            | DRC                | 10 | 3000 | 330.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |