**TPS40074** SLUS617B-APRIL 2005-REVISED OCTOBER 2006

# MIDRANGE INPUT SYNCHRONOUS BUCK CONTROLLER WITH VOLTAGE FEED-FORWARD

# **FEATURES**

- **Operation Over 4.5-V to 28-V Input Range**

- Fixed-Frequency Voltage-Mode Controller

- Integrated Unity Gain Amplifier for Remote **Output Sensing**

- Predictive Gate Drive<sup>™</sup> Generation II for Improved Efficiency

- <1% Internal 700-mV Reference

- Input Voltage Feed Forward Control

- **Prebiased Output Compatible** .

- Internal Gate Drive Outputs for High-Side and Synchronous N-Channel MOSFETs

- Switching Frequency Programmable to 1 MHz •

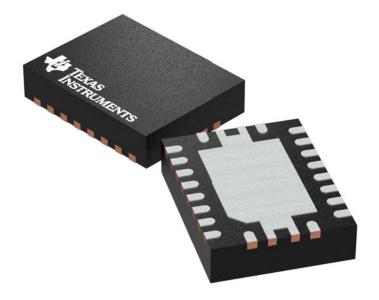

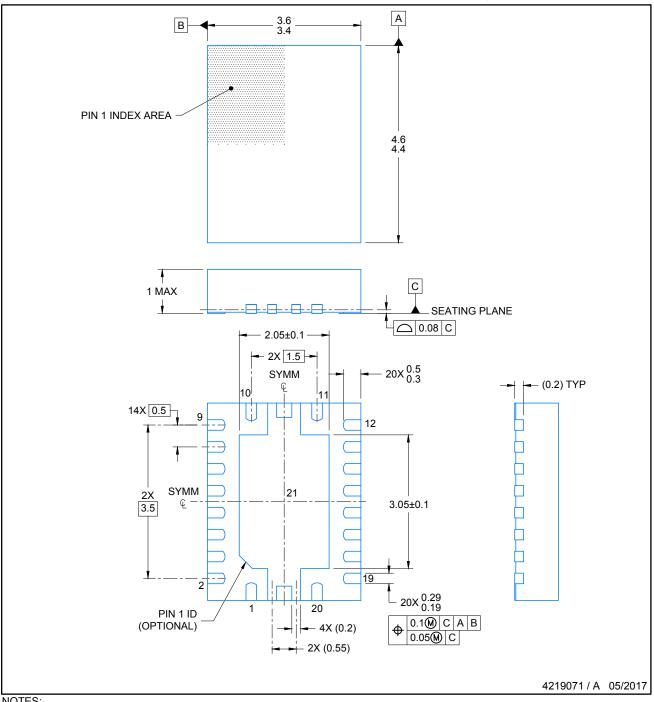

- 20-Pin QFN Package .

- **Thermal Shutdown Protection** •

- Software Design Tool and EVM Available •

# APPLICATIONS

- **Power Modules**

- **Networking/Telecom**

- Industrial .

- Servers

# DESCRIPTION

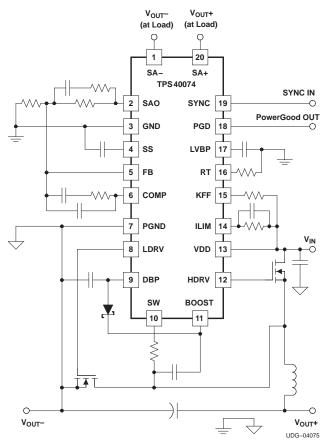

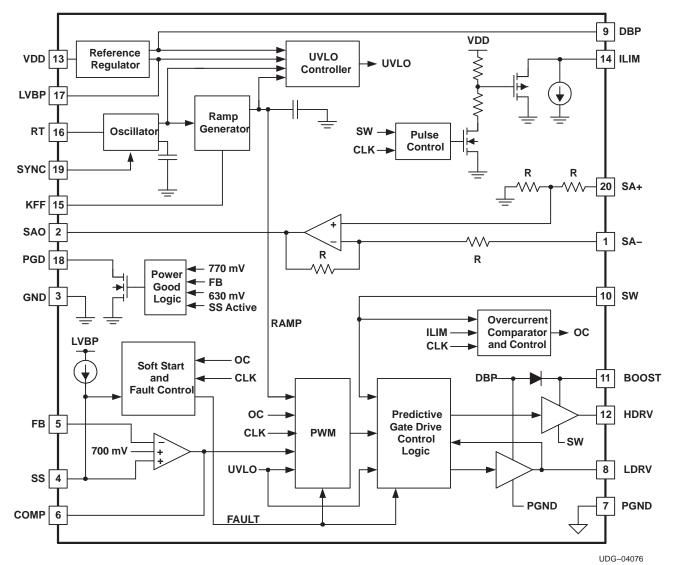

The TPS40074 is a mid voltage, wide input (4.5-V to 28-V), synchronous, step-down controller, offering design flexibility for a variety of user programmable functions, including; soft start, UVLO, operating frequency, voltage feed-forward and high-side FET sensed short circuit protection.

The TPS40074 incorporates MOSFET gate drivers for external N-channel high side and synchronous rectifier (SR) MOSFETs. The gate drive logic incorporates second generation predictive anti-cross conduction circuitry to prevent simultaneous high side and synchronous rectifier conduction, while minimizing to eliminating current flow in the body diode of the SR FET. The TPS40074 allows for starting into pre-biased outputs by not allowing the synchronous rectifier FET to turn on until the commanded voltage during soft start is greater than the existing pre-bias voltage.

The TPS40074 uses voltage feed-forward control techniques to provide good line regulation over a wide input voltage range, and fast response to input line transients. Voltage feed-forward also provides nearly constant power stage gain with input variation to ease loop compensation of wide input range designs. The externally programmable short circuit protection provides fault current limiting, as well as hiccup mode operation for low power dissipation in the presence of a shorted output. The TPS40074 is packaged in a 20-pin QFN package for better thermal performance at higher voltages and frequencies, as well as reduced footprint.

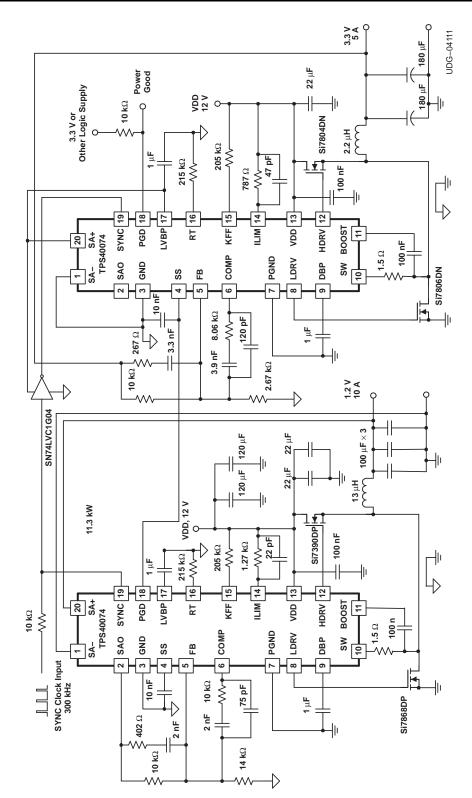

### SIMPLIFIED APPLICATION DIAGRAM

A

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. Predictive Gate Drive is a trademark of Texas Instruments.

#### ORDERING INFORMATION

| T <sub>A</sub> | PACKAGE           | PART NUMBER                 |

|----------------|-------------------|-----------------------------|

| 40°C to 85°C   | Dipotio OEN (DHL) | TPS40074RHLT <sup>(1)</sup> |

| 40 0 10 85 0   | Plastic QFN (RHL) | TPS40074RHLR <sup>(2)</sup> |

- The TPS40074 is available taped and reeled only. Add an T suffix (i.e. TPS40074RHLT) to the orderable part number for quantities of 250 units per small reel.

- (2) Add an R suffix (i.e. TPS40074RHLR) to the orderable part number for quantities of 3,000 units per smalllarge reel.

# **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range unless otherwise noted<sup>(1)</sup>

|                  |                             |                       | TPS40074   | UNIT |

|------------------|-----------------------------|-----------------------|------------|------|

|                  |                             | VDD, ILIM             | 30         |      |

|                  |                             | FB, KFF, PGD, SYNC    | -0.3 to 6  |      |

| $V_{DD}$         | Input voltage range         | SW                    | -0.3 to 40 |      |

|                  |                             | SA+, SA-              | -0.3 to 11 |      |

|                  |                             | SW, transient < 50 ns | -2.5       | V    |

|                  |                             | COMP, RT, SS          | -0.3 to 6  |      |

| V                |                             | BOOST, HDRV           | 50         |      |

| V <sub>OUT</sub> | Output voltage range        | DBP, SAO, LDRV        |            |      |

|                  |                             | LVBP                  | 6          |      |

| I <sub>OUT</sub> | Output current source       | LDRV, HDRV            | 1.5        |      |

|                  | O data di successi di si si | LDRV, HDRV            | 2.0        | Α    |

| IOUT             | Output current sink         | KFF                   | 10         |      |

|                  | <b>0</b> <i>i i i</i>       | RT                    | 1          | mA   |

|                  | Output current              | LVBP                  | 1.5        |      |

| TJ               | Operating junction temp     | erature range         | -40 to 125 |      |

| T <sub>stg</sub> | Storage temperature         |                       | –55 to 150 | °C   |

(1) Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### **RECOMMENDED OPERATING CONDITIIONS**

|                |                                | MIN | NOM MAX | UNIT |

|----------------|--------------------------------|-----|---------|------|

| $V_{DD}$       | Input voltage                  | 4.5 | 28      | V    |

| T <sub>A</sub> | Operating free-air temperature | -40 | 85      | °C   |

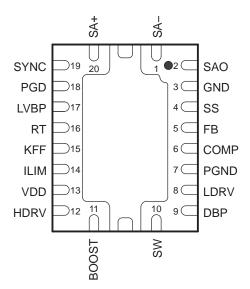

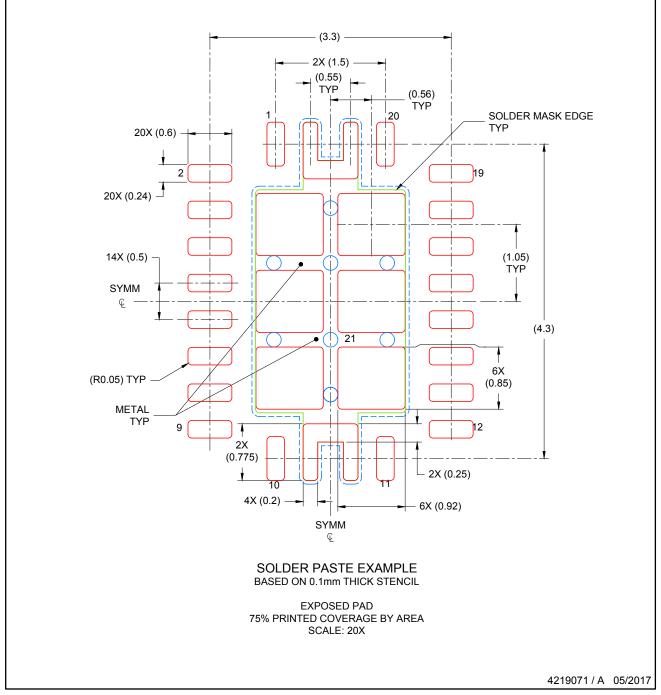

#### RHL PACKAGE (BOTTOM VIEW)

### **ELECTRICAL CHARACTERISTICS**

$T_{A}$  = -40°C to 85°C,  $V_{IN}$  = 12  $V_{dc}, R_{T}$  = 90.9 kΩ,  $I_{KFF}$  = 300 µA,  $f_{SW}$  = 500 kHz, all parameters at zero power dissipation (unless otherwise noted)

|                         | PARAMETER                                           | TEST CONDITIONS                                                                            | MIN   | TYP   | MAX   | UNIT |

|-------------------------|-----------------------------------------------------|--------------------------------------------------------------------------------------------|-------|-------|-------|------|

| INPUT SU                | JPPLY                                               |                                                                                            |       |       |       |      |

| V <sub>DD</sub>         | Input voltage range, VIN                            |                                                                                            | 4.5   |       | 28    | V    |

| OPERATI                 | NG CURRENT                                          |                                                                                            |       |       |       |      |

| I <sub>DD</sub>         | Quiescent current                                   | Output drivers not switching                                                               |       | 2.5   | 3.5   | mA   |

| LVBP                    |                                                     |                                                                                            |       |       | ,     |      |

| V <sub>LVBP</sub>       | Output voltage                                      | $T_A = T_J = 25^{\circ}C$                                                                  | 3.9   | 4.2   | 4.5   | V    |

| OSCILLA                 | TOR/RAMP GENERATOR                                  |                                                                                            |       |       |       |      |

| f <sub>osc</sub>        | Accuracy                                            |                                                                                            | 450   | 500   | 550   | kHz  |

| V <sub>RT</sub>         | RT voltage                                          |                                                                                            | 2.23  | 2.40  | 2.58  | V    |

| t <sub>ON(min)</sub>    | Minimum output pulse time <sup>(1)</sup>            | C <sub>HDRV</sub> = 0 nF                                                                   |       |       | 150   | ns   |

| VIH                     | High-level input voltage, SYNC                      |                                                                                            | 2     |       | 5     | V    |

| V <sub>IL</sub>         | Low-level input voltage, SYNC                       |                                                                                            |       |       | 0.8   | V    |

| I <sub>SYNC</sub>       | Input current, SYNC                                 |                                                                                            |       | 5     | 10    | μA   |

|                         |                                                     | $V_{FB}$ = 0 V, 100 kHz $\leq$ f <sub>SW</sub> $\leq$ 500 kHz                              | 84%   |       | 95%   |      |

|                         | Maximum duty cycle                                  | V <sub>FB</sub> = 0 V, f <sub>SW</sub> = 1 MHz                                             | 76%   |       | 93%   |      |

| V <sub>KFF</sub>        | Feed-forward voltage                                |                                                                                            | 0.35  | 0.40  | 0.45  | V    |

| I <sub>KFF</sub>        | Feed-forward current operating range <sup>(1)</sup> |                                                                                            | 20    |       | 1100  | μA   |

| SOFT ST                 | ART                                                 |                                                                                            | 1     |       |       |      |

| I <sub>SS</sub>         | Charge current                                      |                                                                                            | 7     | 12    | 17    | μA   |

| t <sub>DSCH</sub>       | Discharge time                                      | C <sub>SS</sub> = 3.9 nF                                                                   | 25    |       | 75    |      |

| t <sub>SS</sub>         | Soft-start time                                     | $C_{SS} = 3.9 \text{ nF}, V_{SS} \text{ rising from } 0.7 \text{ V to } 1.6 \text{ V}$     | 210   | 290   | 500   | μs   |

|                         | Command zero output voltage <sup>(2)(1)</sup>       |                                                                                            | 300   |       |       | mV   |

| DBP                     |                                                     |                                                                                            | 1     |       |       |      |

|                         |                                                     | V <sub>DD</sub> > 10 V                                                                     | 7     | 8     | 9     |      |

| V <sub>DBP</sub>        | Output voltage                                      | V <sub>VDD</sub> = 4.5 V, I <sub>OUT</sub> = 25 mA                                         | 4.0   | 4.3   |       | V    |

| ERROR A                 | MPLIFIER                                            |                                                                                            | 1     |       |       |      |

|                         |                                                     | $T_A = T_J = 25^{\circ}C$                                                                  | 0.698 | 0.700 | 0.704 |      |

| V <sub>FB</sub>         | Feedback regulation voltage total variation         | $0^{\circ}C \leq T_{A} = T_{J} \leq 85^{\circ}C$                                           | 0.690 | 0.700 | 0.707 | V    |

|                         |                                                     | $-40^{\circ}C \le T_{A} = T_{J} \le 85^{\circ}C$                                           | 0.690 | 0.700 | 0.715 | V    |

| V <sub>SS(offset)</sub> | Soft-start offset from VSS <sup>(1)</sup>           | Offset from V <sub>SS</sub> to error amplifier                                             |       | 1     |       |      |

| GBWP                    | Gain bandwidth <sup>(1)</sup>                       |                                                                                            | 5     | 10    |       | MHz  |

| A <sub>VOL</sub>        | Open loop gain                                      |                                                                                            | 50    |       |       | dB   |

| I <sub>SRC</sub>        | Output source current                               |                                                                                            | 2.5   | 4.5   |       |      |

| I <sub>SINK</sub>       | Output sink current                                 |                                                                                            | 2.5   | 6     |       | mA   |

| I <sub>BIAS</sub>       | Input bias current                                  | V <sub>FB</sub> = 0.7 V                                                                    | -250  |       | 0     | nA   |

|                         | IRCUIT CURRENT PROTECTION                           |                                                                                            | •     |       |       |      |

| I <sub>ILIM</sub>       | Current sink into ILIM pin                          |                                                                                            | 115   | 135   | 150   | μA   |

| VILIM(ofst)             | Current limit offset voltage                        | V <sub>ILIM</sub> = 11.5 V, (V <sub>SW</sub> - V <sub>ILIM</sub> ) V <sub>VDD</sub> = 12 V | -50   | -30   | -10   | mV   |

| t <sub>HSC</sub>        | Minimum HDRV pulse width                            | During short circuit                                                                       |       | 135   | 225   | ns   |

|                         | Propagation delay to output <sup>(1)</sup>          | -                                                                                          |       | 50    |       | ns   |

|                         |                                                     |                                                                                            | 1     | 50    |       | ne   |

| t <sub>BLANK</sub>      | Blanking time <sup>(1)</sup>                        |                                                                                            |       | 50    |       | ns   |

Ensured by design. Not production tested.

For zero output voltage only. Does not assure lack of activity on HDRV or LDRV.

# **ELECTRICAL CHARACTERISTICS (continued)**

$T_A = -40^\circ C$  to 85°C,  $V_{IN} = 12~V_{dc},~R_T = 90.9~k\Omega,~I_{KFF} = 300~\mu A,~f_{SW} = 500~kHz$ , all parameters at zero power dissipation (unless otherwise noted)

|                        | PARAMETER                                                   | TEST CONDITIONS                                                        | MIN   | TYP   | MAX   | UNIT |

|------------------------|-------------------------------------------------------------|------------------------------------------------------------------------|-------|-------|-------|------|

| V <sub>SW</sub>        | Switching level to end precondition <sup>(3)</sup>          | (V <sub>VDD</sub> - V <sub>SW</sub> )                                  |       | 2     |       | V    |

| t <sub>PC</sub>        | Precondition time <sup>(3)</sup>                            |                                                                        |       |       | 100   | ns   |

| V <sub>ILIM(pre)</sub> | Current limit precondition voltage threshold <sup>(3)</sup> |                                                                        |       | 6.8   |       | V    |

| OUTPUT                 | DRIVERS                                                     |                                                                        |       |       |       |      |

| t <sub>HFALL</sub>     | High-side driver fall time <sup>(3)</sup>                   |                                                                        |       | 36    |       |      |

| t <sub>HRISE</sub>     | High-side driver rise time <sup>(3)</sup>                   | C <sub>HDRV</sub> = 2200 pF, (HDRV - SW)                               |       | 48    |       | ns   |

| t <sub>HFALL</sub>     | High-side driver fall time <sup>(3)</sup>                   | C <sub>HDRV</sub> = 2200 pF, (HDRV - SW)                               |       | 72    |       |      |

| t <sub>HRISE</sub>     | High-side driver rise time <sup>(3)</sup>                   | V <sub>VDD</sub> = 4.5 V                                               |       | 96    |       | ns   |

| t <sub>LFALL</sub>     | Low-side driver fall time <sup>(3)</sup>                    | 0                                                                      |       | 24    |       |      |

| t <sub>LRISE</sub>     | Low-side driver rise time <sup>(3)</sup>                    | $C_{LDRV} = 2200 \text{ pF}$                                           |       | 48    |       | ns   |

| t <sub>LFALL</sub>     | Low-side driver fall time <sup>(3)</sup>                    |                                                                        |       | 48    |       |      |

| t <sub>LRISE</sub>     | Low-side driver rise time <sup>(3)</sup>                    | C <sub>LDRV</sub> = 2200 pF, V <sub>DD</sub> = 4.5 V                   |       | 96    |       | ns   |

|                        |                                                             | I <sub>HDRV</sub> = -0.01 A, (V <sub>BOOST</sub> - V <sub>HDRV</sub> ) |       | 0.7   | 1.0   |      |

| V <sub>ОН</sub>        | High-level output voltage, HDRV                             | $I_{HDRV} = -0.1 \text{ A}, (V_{BOOST} - V_{HDRV})$                    |       | 0.95  | 1.35  | V    |

|                        |                                                             | $(V_{HDRV} - V_{SW}), I_{HDRV} = 0.01A$                                |       | 0.06  | 0.10  |      |

| V <sub>OL</sub>        | Low-level output voltage, HDRV                              | $(V_{HDRV} - V_{SW})$ , $I_{HDRV} = 0.1 \text{ A}$                     |       | 0.65  | 1.00  | V    |

|                        |                                                             | $(V_{\text{DBP}} - V_{\text{LDRV}}), I_{\text{LDRV}} = -0.01\text{A}$  |       | 0.65  | 1.00  |      |

| V <sub>OH</sub>        | High-level output voltage, LDRV                             | $(V_{\text{DBP}} - V_{\text{LDRV}}), I_{\text{LDRV}} = -0.1 \text{ A}$ |       | 0.875 | 1.300 | V    |

|                        |                                                             | $I_{LDRV} = 0.01 \text{ A}$                                            |       | 0.03  | 0.05  |      |

| V <sub>OL</sub>        | Low-level output voltage, LDRV                              | $I_{LDRV} = 0.1 \text{ A}$                                             |       | 0.3   | 0.5   | V    |

| BOOST F                | REGULATOR                                                   |                                                                        |       |       |       |      |

| V <sub>BOOST</sub>     | Output voltage                                              | V <sub>VDD</sub> = 12 V                                                | 15.2  | 17.0  |       | V    |

| UVLO                   | · · ·                                                       |                                                                        | I     |       |       |      |

| V <sub>UVLO</sub>      | Programmable UVLO threshold voltage                         | $R_{KFF}$ = 90.9 k $\Omega$ , turn-on, V <sub>VDD</sub> rising         | 6.2   | 7.2   | 8.2   |      |

|                        | Programmable UVLO hysteresis                                | $R_{\text{KFF}} = 90.9 \text{ k}\Omega$                                | 1.10  | 1.55  | 2.00  | V    |

|                        | Fixed UVLO threshold voltage                                | Turn-on, V <sub>VDD</sub> rising                                       | 4.15  | 4.30  | 4.45  |      |

|                        | Fixed UVLO hysteresis                                       |                                                                        | 275   | 365   |       | mV   |

| POWER                  | •                                                           |                                                                        |       |       |       |      |

| V <sub>PGD</sub>       | Powergood voltage                                           | I <sub>PGD</sub> = 1 mA                                                |       | 370   | 550   |      |

| V <sub>FBH</sub>       | High-level output voltage, FB                               |                                                                        |       | 770   |       | mV   |

| V <sub>FBL</sub>       | Low-level output voltage, FB                                |                                                                        |       | 630   |       |      |

|                        | MPLIFIER                                                    |                                                                        |       |       |       |      |

| V <sub>IO</sub>        | Input offset voltage                                        | $V_{SA+} = V_{SA-} = 1.25$ V, Offset referenced to SA+ and SA-         | -9    |       | 9     | mV   |

| A <sub>DIFF</sub>      | Differential gain                                           | V <sub>SA+</sub> - V <sub>SA-</sub> = 4.5 V                            | 0.995 | 1.000 | 1.005 |      |

| V <sub>ICM</sub>       | Input common mode range <sup>(4)</sup>                      |                                                                        | 0     |       | 6     | V    |

| R <sub>G</sub>         | Internal resistance for setting gain                        |                                                                        | 14    | 20    | 26    | kΩ   |

| он                     | Output source current                                       |                                                                        | 2     | 10    | 15    |      |

| I <sub>OL</sub>        | Output sink current                                         |                                                                        | 15    | 25    | 35    | mA   |

| GBWP                   | Gain bandwidth <sup>(3)</sup>                               |                                                                        |       | 2     |       | MHz  |

|                        | L SHUTDOWN                                                  |                                                                        | 1     |       |       |      |

|                        | Shutdown temperature threshold <sup>(3)</sup>               |                                                                        |       | 165   |       |      |

|                        | Hysteresis <sup>(3)</sup>                                   |                                                                        |       | 15    |       | °C   |

(3) Ensured by design. Not production tested.

(4) 3 V at internal amplifier terminals, 6 V at SA+ and SA- pins.

### Table 1. TERMINAL FUNCTIONS

| TERMINAL |     |     | DECODIDION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |

|----------|-----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| NAME     | NO. | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |

| BOOST    | 11  | I   | The BOOST voltage is 8-V greater than the input voltage. The peak voltage on BOOST is equal to the SW node voltage plus the voltage present at DBP less the bootstrap diode drop. This drop can be 1.4 V for the internal bootstrap diode or 300 mV for an external schottkey diode. The voltage differential between this pin and SW is the available drive voltage for the high-side FET.                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |

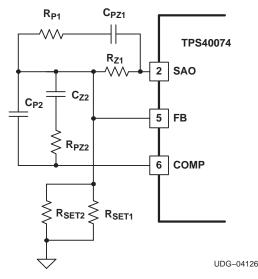

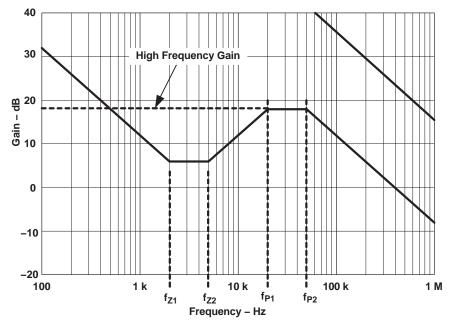

| COMP     | 6   | ο   | Output of the error amplifier, input to the PWM comparator. A feedback network is connected from this pin to the FB pin to compensate the overall loop. This pin is internally clamped to a 3.4-V maximum output drive capability for quicker recovery from a saturated feedback loop situation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |

| DBP      | 9   | 0   | 8-V regulator output used for the gate drive of the N-channel synchronous rectifier and as the supply for charging the bootstrap capacitor. This pin should be bypassed to ground with a $1.0-\mu$ F ceramic capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |

| FB       | 5   | I   | Inverting input to the error amplifier. In normal operation the voltage on this pin is equal to the internal reference voltage, 0.7 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |

| GND      | 3   | -   | Ground reference for the device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |

| HDRV     | 12  | 0   | Floating gate drive for the high-side N-channel MOSFET. This pin switches from BOOST (MOSFET on) to SW (MOSFET off).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |

| ILIM     | 14  | I   | Short circuit protection programming pin. This pin is used to set the overcurrent threshold. An internal current sink from this pin to ground sets a voltage drop across an external resistor connected from this pin to VDD. The voltage on this pin is compared to the voltage drop ( $V_{VDD}$ - $V_{SW}$ ) across the high side N-channel MOSFET during conduction. Just prior to the beginning of a switching cycle this pin is pulled to approximately $V_{VDD}/2$ and released when SW is within 2 V of $V_{VDD}$ or after a timeout (the precondition time) - whichever occurs first. Placing a capacitor across the resistor from ILIM to VDD allows the ILIM threshold to decrease during the switch on time, effectively programming the ILIM blanking time. See <i>Applications Information</i> section. |  |  |  |  |  |  |  |  |

| KFF      | 15  | I   | A resistor is connected from this pin to VDD programs the amount of input voltage feed-forward. The current fed into this pin is used to control the slope of the PWM ramp and program undervoltage lockout. Nominal voltage at this pin is maintained at 400 mV.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

| LDRV     | 8   | 0   | Gate drive for the N-channel synchronous rectifier. This pin switches from DBP (MOSFET on) to PGND (MOSFET off). For proper operation, the total gate charge of the MOSFET connected to LDRV should be less than 50nC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |

| LVBP     | 17  | 0   | 4.2-V reference used for internal device logic and analog functions. This pin should be bypassed to GND with a 0.1-µF ceramic capacitor. External loads less than 1 mA and electrically quiet may be applied.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |

| PGD      | 18  | 0   | This is an open drain output that pulls to ground when soft start is active, or when the FB pin is outside a $\pm 10\%$ band around the 700 mV reference voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

| PGND     | 7   |     | Power ground reference for the device. There should be a low-impedance path from this pin to the source(s) of the lower MOSFET(s).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |

| RT       | 16  | I   | A resistor is connected from this pin to GND to set the switching frequency.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |

| SA+      | 20  | Ι   | Noninverting input of the remote voltage sense amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |

| SA-      | 1   | I   | Inverting input of the remote voltage sense amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |

| SAO      | 2   | 0   | Output of the remote voltage sense amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |

| SS       | 4   | I   | Soft-start programming pin. A capacitor connected from this pin to GND programs the soft-start time. The capacitor is charged with an internal current source of 12 $\mu$ A. The resulting voltage ramp on the SS pin is used as a second non-inverting input to the error amplifier. The voltage at this error amplifier input is approximately 1 V less that that on the SS pin. Output voltage regulation is controlled by the SS voltage ramp until the voltage on the SS pin reaches the internal offset voltage of 1 V plus the internal reference voltage of 700 mV. If SS is below the internal offset voltage of 1 V (300 mV minimum ensured), the resulting output voltage is zero. Also provides timing for fault recovery attempts. Maximum recommended capacitor is 22nF.                               |  |  |  |  |  |  |  |  |

| SW       | 10  | I   | This pin is connected to the switched node of the converter and used for overcurrent sensing as well as gate drive timing. This pin is also the return path from the high-side FET for the floating high-side FET driver. A $1.5-\Omega$ resistor is required in series with this pin to protect against substrate current issues.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |

| SYNC     | 19  | I   | Logic input for pulse train to synchronize oscillator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |

| VDD      | 13  | I   | Supply voltage for the device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |

### SIMPLIFIED BLOCK DIAGRAM

# **APPLICATION INFORMATION**

The TPS40074 allows the user to construct synchronous voltage mode buck converters with inputs ranging from 4.5 V to 28 V and outputs as low as 700 mV. Predictive gate drive circuitry optimizes switching delays for increased efficiency and improved converter output power capability. Voltage feed-forward is employed to ease loop compensation for wide input range designs and provide better line transient response.

An on-board unity gain differential amplifier is provided for remote sensing in applications that require the tightest load regulation. The TPS40074 incorporates circuitry to allow startup into a pre-existing output voltage without sinking current from the source of the pre-existing output voltage. This avoids damaging sensitive loads at startup. The controller can be synchronized to an external clock source or can free run at a user programmable frequency. An integrated power good indicator is available for logic (open drain) output of the condition of the output of the converter.

### MINIMUM PULSE WIDTH

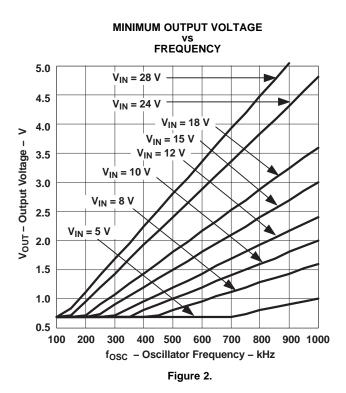

The TPS40074 has limitations on the minimum pulse width that can be used to design a converter. Reliable operation is guaranteed for nominal pulse widths of 150 ns and above. This places some restrictions on the conversion ratio that can be achieved at a given switching frequency. Figure 2 shows minimum output voltage for a given input voltage and frequency.

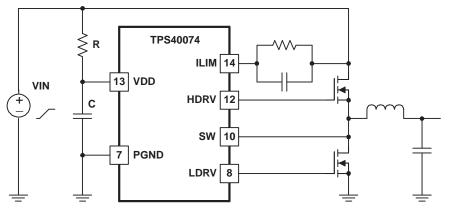

### SLEW RATE LIMIT ON VDD

The regulator that supplies power for the drivers on the TPS40074 requires a limited rising slew rate on VDD for proper operation if the input voltage is above 10 V. If the slew rate is too great, this regulator can over shoot and damage to the part can occur. To ensure that the part operates properly, limit the slew rate to no more than 0.12 V/µs as the voltage at VDD crosses 8 V. If necessary, an R-C filter can be used on the VDD pin of the device. Connect the resistor from the VDD pin to the input supply of the converter. Connect the capacitor from the VDD pin to be excessive (more than a 200-mV) voltage drop across the resistor in normal operation. This places some constraints on the R-C values that can be used. Figure 1 is a schematic fragment that shows the connection of the R-C slew rate limit circuit. Equation 1 and Equation 2 give values for R and C that limits the slew rate in the worst case condition.

UDG-05058

Figure 1. Limiting the Slew Rate

$$R < \frac{0.2 V}{f_{SW} \times Q_{g(TOT)} + I_{DD}}$$

$$C > \frac{V_{VIN} - 8 V}{2}$$

1

where

- $V_{\text{VIN}}$  is the final value of the input voltage ramp

- f<sub>SW</sub> is the switching frequency

- Q<sub>q(TOT)</sub> is the combined total gate charge for both upper and lower MOSFETs (from MOSFET data sheet)

- I<sub>DD</sub> is the TPS40074 input current (3.5 mA maximum)

- SR is the maximum allowed slew rate [12 ×10<sup>4</sup>] (V/s)

# SETTING THE SWITCHING FREQUENCY (PROGRAMMING THE CLOCK OSCILLATOR)

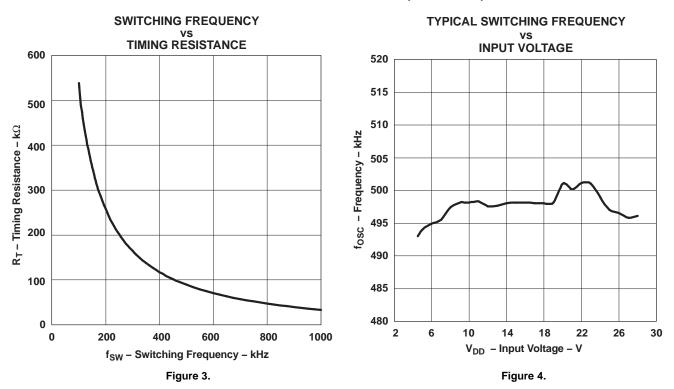

The TPS40074 has independent clock oscillator and PWM ramp generator circuits. The clock oscillator serves as the master clock to the ramp generator circuit. Connecting a single resistor from RT to ground sets the switching frequency of the clock oscillator. The clock frequency is related to  $R_T$  by:

$$R_{T} = \left(\frac{1}{f_{SW}(kHz) \times 17.82 \times 10^{-6}} - 23\right) k\Omega$$

(3)

(1)

(2)

Texas truments

www.ti.com

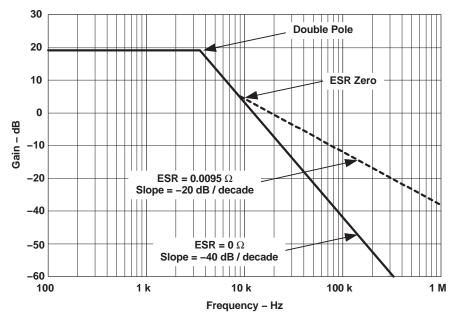

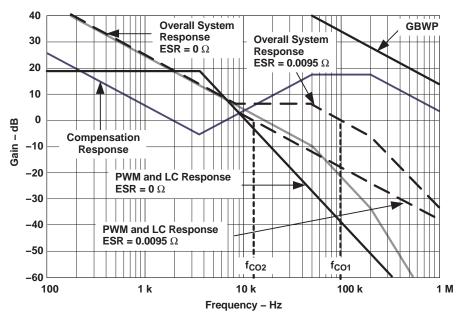

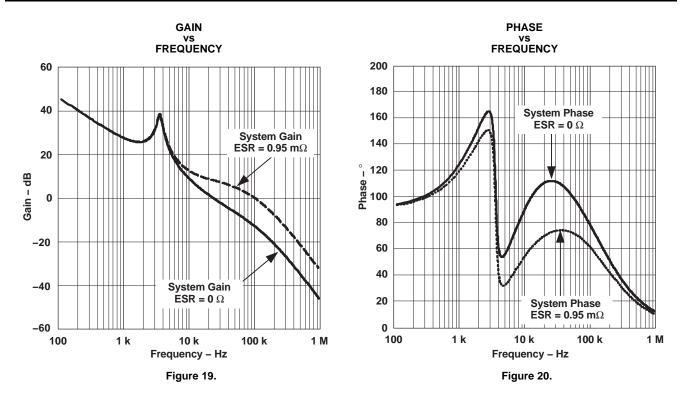

### PROGRAMMING THE RAMP GENERATOR CIRCUIT AND UVLO FUNCTION

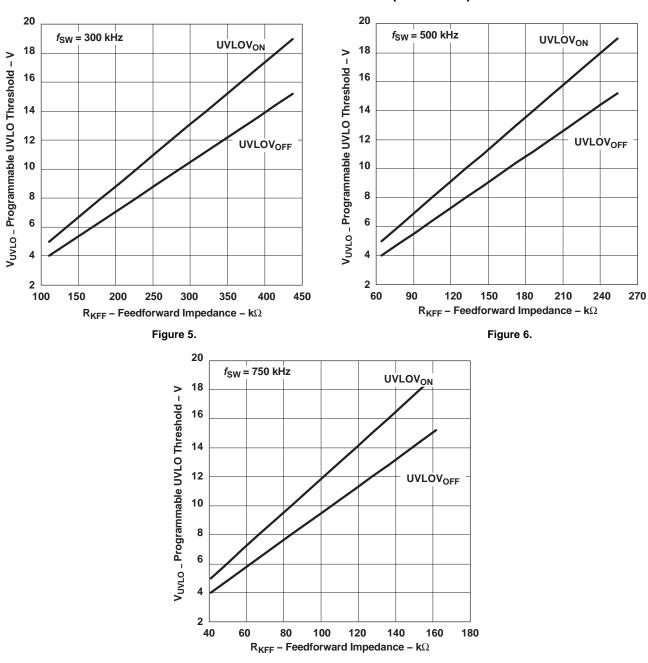

The ramp generator circuit provides the actual ramp used by the PWM comparator and provides voltage feed-forward by varying the PWM ramp slope as the line voltage changes. As the input voltage to the converter increases, the slope of the PWM ramp increase by a proportionate amount. The programmable UVLO circuit works by monitoring the level reached by the PWM ramp during a clock cycle. The PWM ramp must reach approximately 1 V in amplitude during a clock cycle, or the converter is not be allowed to start. This programmable UVLO point is set via a single resistor ( $R_{KFF}$ ) connected from KFF to VDD.  $R_{KFF}$ ,  $V_{START}$  and  $R_{RT}$  are related by (approximately)

$$R_{KFF} = 0.131 \times R_{T} \times V_{UVLO(on)} - 1.61 \times 10^{-3} \times V_{UVLO(on)}^{2} + 1.886 \times V_{UVLO} - 1.363 - 0.02 \times R_{T} - 4.87 \times 10^{-5} \times R_{T}^{2}$$

(4)

where

- V<sub>UVLO(on)</sub> is in volts

- $R_{KFF}$  and  $R_T$  are in  $k\Omega$

This yields typical numbers for the programmed startup voltage. The minimum and maximum values may vary up ±15% from this number. Figure 5 through Figure 7 show the typical relationship of  $V_{UVLO(on)}$ ,  $V_{UVLO(off)}$  and  $R_{KFF}$  at three common frequencies.

**APPLICATION INFORMATION (continued)**

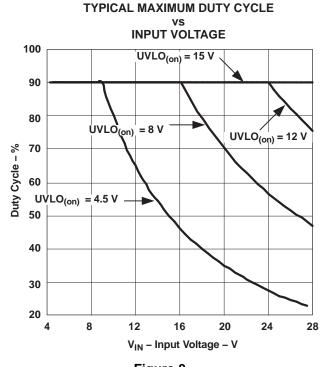

Figure 7.

The programmable UVLO circuit incorporates 20% hysteresis from the start voltage to the shutdown voltage. For example, if the startup voltage is programmed to be 10 V, the controller starts when  $V_{DD}$  reaches 10 V and shuts down when  $V_{DD}$  falls below 8 V. The maximum duty cycle begins to decrease as the input voltage rises to twice the startup voltage. Below this point, the maximum duty cycle is as specified in the electrical table. Note that with this scheme, the theoretical maximum output voltage that the converter can produce is approximately two times the programmed startup voltage. For design, set the programmed startup voltage equal to or greater than the desired output voltage divided by maximum duty cycle (85% for frequencies 500 kHz and below). For example, a 5-V output converter should not have a programmed startup voltage below 5.9 V. Figure 8 shows the theoretical maximum duty cycle (typical) for various programmed startup voltages

Figure 8.

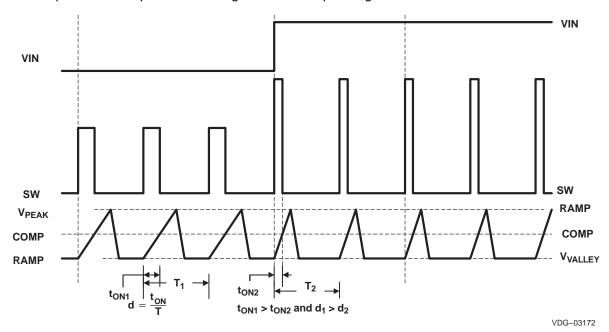

Figure 9 shows the effect of changing input voltage on the duty cycle, and how that change takes place. The pulse width modulator (PWM) ramp input is generated using a current that is proportional to the current into the KFF pin. The TPS40074 holds this pin at a constant 400 mV, so connecting a resistor from KFF to the input power supply causes a current to flow into the KFF pin that is proportional to the input voltage. The slope of the ramp signal to the PWM is therefore proportional to the input voltage. This allows the duty cycle to change with variations in Vin without requiring much response from the error amplifier, resulting in very good line transient response. Another benefit is essentially constant PWM gain over the entire input voltage operating range. This makes the output control loop easier to design for a wide input range converter.

Figure 9. Voltage Feed-Forward and PWM Duty Cycle Waveforms

# PROGRAMMING SOFT START

TPS40074 uses a closed-loop approach to ensure a controlled ramp on the output during start-up. Soft-start is programmed by connecting an external capacitor ( $C_{SS}$ ) from the SS pin to GND. This capacitor is charged by a fixed current, generating a ramp signal. The voltage on SS is level shifted down approximately 1 V and fed into a separate non-inverting input to the error amplifier. The loop is closed on the lower of the level shifted SS voltage or the 700-mV internal reference voltage. Once the level shifted SS voltage rises above the internal reference voltage, output voltage regulation is based on the internal reference. To ensure a controlled ramp-up of the output voltage the soft-start time should be greater than the L-C<sub>OUT</sub> time constant or:

$$t_{START} \ge 2\pi \times \sqrt{L \times C_{OUT}}$$

(seconds)

where

- L is the value of the filter inductor

- C<sub>OUT</sub> is the value of the output capacitance

- t<sub>START</sub> is the output ramp up-time

For a desired soft-start time, the soft-start capacitance, C<sub>SS</sub>, can be found from:

$$C_{SS} \times t_{SS} = \frac{I_{SS}}{V_{FB}}$$

To ensure correct start up of the converter, the soft-start time is limited and can be calculated using Equation 7.

(6)

(5)

$$t_{START} \le \frac{D_{MIN}}{f_{SW} \times 10^{-7}} ms$$

(7)

where

- D<sub>MIN</sub> is the minimum operating duty cycle

- f<sub>SW</sub> is the converter switching frequency

Please note: There is a direct correlation between  $t_{START}$  and the input current required during start-up. The lower  $t_{START}$  is, the higher the input current required during start-up since the output capacitance must be charged faster.

## **PROGRAMMING SHORT CIRCUIT PROTECTION**

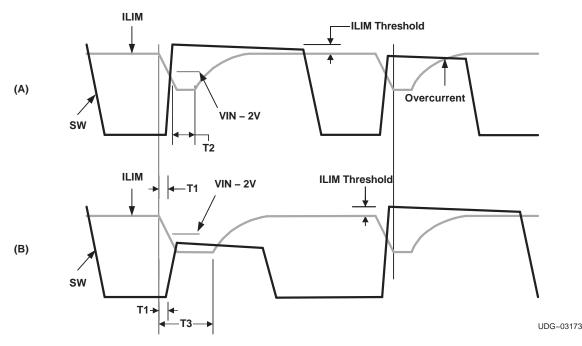

The TPS40074 uses a two-tier approach to short circuit protection. The first tier is a pulse-by-pulse protection scheme. Short circuit protection is implemented by sensing the voltage drop across the high-side MOSFET while it is turned on. The MOSFET drain to source voltage is compared to the voltage dropped across a resistor ( $R_{ILIM}$ ) connected from VDD to the ILIM pin. The voltage drop across this resistor is produced by a constant current sink. If the voltage drop across the MOSFET exceeds the voltage drop across the ILIM resistor the switching pulse is immediately terminated. The MOSFET remains off until the next switching cycle is initiated.

In addition, just prior to the high-side MOSFET turning on, the ILIM pin is pulled down to approximately half of VDD. The ILIM pin is allowed to return to its nominal value after one of two events occur:

- 1. The SW node rises to within approximately 2 V of VDD

- 2. An internal timeout occurs, approximately 125-ns after ILIM is initially pulled down

If the SW node rises to within approximately 2-V of VDD, the device allows ILIM to go back to its nominal value. This is illustrated in Figure 10 A. T1 is the delay time from the internal PWM signal being asserted and the rise of SW. This includes the driver delay of 50 ns typical, and the turn on time of the high-side MOSFET. The MOSFET used should have a turn on time less than 75 ns. T2 is the reaction time of the sensing circuit that allows ILIM to start to return to its nominal value, typically 20ns.

Figure 10. Switching and Current Limit Waveforms and Timing Relationship

The second event that can cause ILIM to return to its nominal value is for an internal timeout to expire. This is illustrated in Figure 10 B as T3. Here SW never rises to VDD-2, for whatever reason, and the internal timer times out. This allows the ILIM pin to start its transition back to its nominal value.

Prior to ILIM starting back to its nominal value, short circuit sensing is not enabled. In normal operation, this insures that the SW node is at a higher voltage than ILIM when short circuit sensing starts, avoiding false trips while allowing for a quicker blanking delay than would ordinarily be possible. Placing a capacitor across  $R_{ILIM}$  sets an exponential approach to the normal voltage at the ILIM pin. This exponential "decay" of the short circuit threshold can be used to compensate for ringing on the SW node after its rising edge and to help compensate for slower turn-on MOSFETs. Choosing the proper capacitance requires care. If the capacitance is too large, the voltage at ILIM does not approach the desired short circuit level quickly enough, resulting in an apparent shift in short circuit threshold as pulse width changes.

The comparator that looks at ILIM and SW to determine if a short circuit condition exists has a clamp on its SW input. This clamp makes the SW node never appear to fall more than 1.4 V (approximately, could be as much as  $2 \text{ V at} - 40^{\circ}\text{C}$ ) below VDD. While ILIM is more than 1.4 V below VDD short circuit sensing is effectively disabled, giving a programmable absolute blanking time. As a general rule, it is best to make the time constant of the R-C at the ILIM pin 20% or less of the nominal pulse width of the converter (See Equation 13)

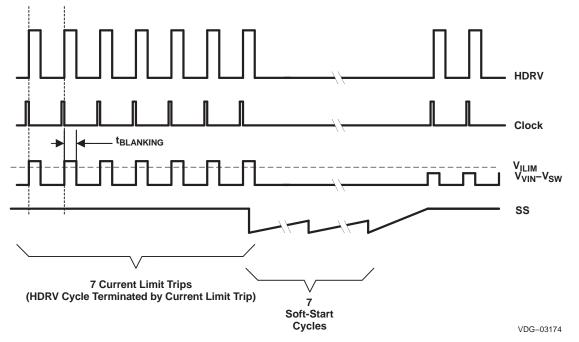

The second tier protection incorporates a fault counter. The fault counter is incremented on each cycle with an overcurrent pulse and decremented on a clock cycle without an overcurrent pulse. When the counter reaches seven (7) a fault condition is declared by the controller. When this happens, the output drivers turn both MOSFETs off. Seven soft-start cycles are initiated (without activity on the HDRV and LDRV outputs) and the PWM is disabled during this period. The counter is decremented on each soft-start cycle. When the counter is decremented to zero the PWM is re-enabled and the controller attempts to restart. If the fault has been removed the output starts up normally. If the output fault is still present the counter counts seven overcurrent pulses and re-enters the second tier fault mode. Refer to Figure 11 for typical fault protection waveforms.

Figure 11. Typical Fault Protection Waveforms

### **TPS40074** SLUS617B-APRIL 2005-REVISED OCTOBER 2006

# **APPLICATION INFORMATION (continued)**

The minimum short circuit limit threshold ( $I_{SCP}$ ) depends on  $t_{START}$ ,  $C_{OUT}$ ,  $V_{OUT}$ , and the load current at turn-on (I<sub>LOAD</sub>).

$$I_{SCP} > \frac{C_{OUT} \times V_{OUT}}{t_{START}} + I_{LOAD}$$

(A) (8)

The short circuit limit programming resistor (R<sub>ILIM</sub>) is calculated from:

$$\mathsf{R}_{\mathsf{ILIM}} = \frac{100 \times \left(\mathsf{R}_{\mathsf{DS}(\mathsf{onMAX})} \times \mathsf{I}_{\mathsf{SCP}} + \mathsf{V}_{\mathsf{ILIM}}(\mathsf{ofst})\right) + 9 \times \mathsf{R}_{\mathsf{VDD}} \times \mathsf{I}_{\mathsf{RVDD}} + 4.5 \,\mathsf{V}}{109 \times \mathsf{I}_{\mathsf{ILIM}}} \quad \Omega$$

where

- $I_{ILIM}$  is the current into the ILIM pin (135  $\mu$ A typical)

- VILIM(ofst) is the offset voltage of the ILIM comparator (-30 mV typical)

- I<sub>SCP</sub> is the short-circuit protection current

- $R_{\text{DS(on)MAX}}$  is the drain-to-source resistance of the high-side MOSFET

- R<sub>VDD</sub> is the slew rate limit resistor if used

- $I_{RVDD}$  is the current through  $R_{VDD}$  and can be calculated using Equation 10.

$I_{RVDD} = f_{SW} \times Q_{g} + I_{DD}$

where

- f<sub>SW</sub> is the switching frequency

- Q<sub>q(TOT)</sub> is the combined total gate charge fro both upper and lower MOSFETs (from MOSFET datasheet)

- Ipp is the TPS40074 input current (3.5-mA maximum)

To find the range of the short circuit threshold values use the following equations.

$$I_{SCP(max)} = \frac{\frac{1.09 \times I_{ILIM(max)} \times R_{ILIM} - 0.09 \times R_{VDD} \times I_{RVDD} - 0.045 + 50 \text{ mV}}{R_{DS(onMIN)}} A$$

(11)

$$I_{SCP(min)} = \frac{1.09 \times I_{ILIM(min)} \times R_{ILIM} - 0.09 \times R_{VDD} \times I_{RVDD} - 0.045 + 10 \text{ mV}}{R_{DS(onMAX)}} A$$

(12)

The TPS40074 provides short-circuit protection only. As such, it is recommended that the minimum short circuit protection level be placed at least 20% above the maximum output current required from the converter. The maximum output of the converter should be the steady state maximum output plus any transient specification that may exist.

The ILIM capacitor maximum value can be found from:

$$C_{ILIM(max)} = \frac{V_{OUT} \times 0.2}{V_{IN} \times R_{ILIM} \times f_{SW}}$$

(Farads) (13)

Note that this is a recommended maximum value. If a smaller value can be used, it should be to improve protection. For most applications, consider using half the maximum value shown in Equation 13.

# **BOOST AND DBP BYPASS CAPACITANCE**

The BOOST capacitance provides a local, low-impedance flying source for the high-side driver. The BOOST capacitor should be a good quality, high-frequency ceramic capacitor. A minimum value of 100-nF is suggested.

The DBP capacitor has to provide energy storage for switching both the synchronous MOSFET and the high-side MOSFET (via the BOOST capacitor). The suggested value for this capacitor is 1-µF ceramic, minimum.

(9)

(10)

### **INTERNAL REGULATORS**

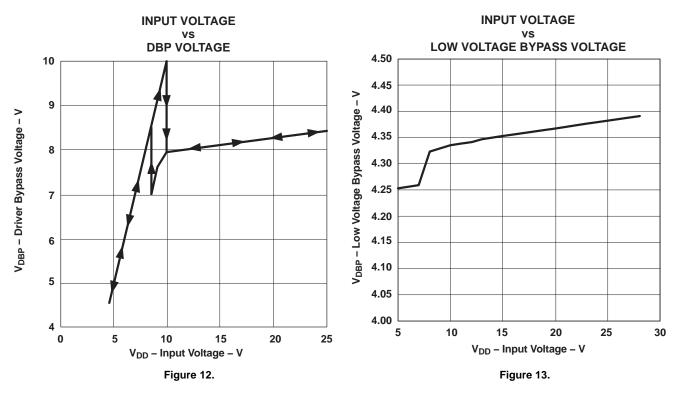

The internal regulators are linear regulators that provide controlled voltages for the drivers and the internal circuitry to operate from. The low-side driver operates directly from the 8-V regulator supply while the high-side driver bootstrap capacitor is charged from this supply. The actual voltage delivered to the high-side driver is the voltage on the DBP pin less any drop from the bootstrap diode. If the internal bootstrap diode is used, the drop across that diode is nominally 1.4 V at room temperature. This regulator has two modes of operation. At voltages below 8.5 V on VDD, the regulator is in a low dropout mode of operation and tries to provide as little impedance as possible from VDD to DBP. When VDD is above 10 V, the regulator regulates DBP to 8 V. Between these two voltages, the regulator is in whatever state it was in when VDD entered this region. The LVBP pin is connected to a 4.2-V regulator that supplies power for the internal control circuitry. Small amounts of current can be drawn from these pins for other external circuit functions, as long as power dissipation in the controller chip remains at acceptable levels and junction temperature does not exceed 125°C. Any external load connected to LVBP should be electrically quiet to avoid degrading performance of the TPS40074. Typical output voltages for these two regulators are shown in Figure 12 and Figure 13.

# DIFFERENTIAL SENSE AMPLIFIER

The TPS40074 has an on board differential amplifier intended for use as a remote sensing amplifier for the output voltage. Use of this amplifier for remote sensing eliminates load regulation issues due to voltage drops that occur between the converter and the actual point of load. The amplifier is powered from the DBP pin and can be used to monitor output voltages up to 6 V with a DBP voltage of 8 V. For lower DBP voltages, the sense amplifier can be used to monitor output voltages up to 2-V below the DBP voltage. The internal resistors used to configure the amplifier for unity gain match each other closely, but their absolute values can vary as much as 30%, so adding external resistance to alter the gain is not accurate in a production environment.

## SYNCHRONIZATION

The SYNC pin accepts logic level signals and is used to synchronize the TPS40074 to an external clock source. Synchronization occurs on the rising edge of the signal at the SYNC pin. There is a fixed delay of approximately 300 ns from the rising edge of the waveform at SYNC to the HDRV output turning on the high-side FET. The pin may be left floating in this function is not used, or it may be connected to GND. The frequency of the external clock must be greater than the free running frequency of the device as set by the resistor on the RT pin ( $R_{RT}$ ). This pin requires a totem pole drive, or open collector/drain if pull up resistor to either LVBP or a separate supply between 2.5 V and 5 V is used. Synchronization does not affect the modulator gain due to the voltage feed forward circuitry. The programmable UVLO thresholds are affected by synchronization. The thresholds are shifted by the ratio of the sync frequency to the free running frequency results in the programmable UVLO thresholds shifting up 20% from their calculated free run values. The synchronization frequency should be kept less than 1.5 times the free run frequency for best performance, although higher multiples can be used.

# POWERGOOD OPERATION

The PGD pin is an open drain output that actively pulls to GND if any of the following conditions are met (assuming that the input voltage is above 4.5 V)

- Soft-start is active ( $V_{VSS} < 3.5 V$ )

- V<sub>FB</sub> < 0.63 V

- V<sub>FB</sub> > 0.77 V

- Programmable UVLO condition not satisfied (V<sub>IN</sub> below programmed level)

- Overcurrent condition exists

- Die temperature is greater than 165°C

### **PRE-BIASED OUTPUTS**

Some applications require that the converter not sink current during startup if a pre-existing voltage exists at the output. Since synchronous buck converters inherently sink current some method of overcoming this characteristic must be employed. Applications that require this operation are typically power rails for a multi supply processor or ASIC. The method used in this controller, is to not allow the low side or rectifier FET to turn on until there the output voltage commanded by the start up ramp is higher than the pre-existing output voltage. This is detected by monitoring the internal pulse width modulator (PWM) for its first output pulse. Since this controller uses a closed loop startup, the first output pulse from the PWM does not occur until the output voltage is commanded to be higher than the pre-existing voltage. This effectively limits the controller to sourcing current only during the startup sequence.

If the pre-existing voltage is higher that the intended regulation point for the output of the converter, the converter starts and sinks current when the soft-start time has completed

### OUTPUT RIPPLE CONSIDERATION

In addition to the typical output ripple associated with switching converters, (which can vary from 5 mV to 150 mV) the TPS40074 exhibits a low-frequency ripple from 5 mV to 50 mV. The ripple, a consequence of the charge pump in the driver supply regulator, is well bounded under changes in line, load, and temperature. The ripple frequency does vary with the converter switching frequency and can vary from 10 kHz to 60 kHz.

(14)

(16)

### **APPLICATION INFORMATION (continued)**

### **TPS40074 POWER DISSIPATION**

The power dissipation in the TPS40074 is largely dependent on the MOSFET driver currents and the input voltage. The driver current is proportional to the total gate charge, Qg, of the external MOSFETs. Driver power (neglecting external gate resistance) can be calculated from:

$$P_{D} = Q_{g} \times V_{DR} \times f_{SW}$$

(Watts/driver)

where

• V<sub>DR</sub> is the driver output voltage

The total power dissipation in the TPS40074, assuming the same MOSFET is selected for both the high-side and synchronous rectifier is described in Equation 15.

$$P_{T} = \left(\frac{2 \times P_{D}}{V_{DR}} + I_{Q}\right) \times V_{IN} \quad (Watts)$$

(15)

or

$P_{T} = (2 \times Q_{g} \times f_{SW} + I_{Q}) \times V_{IN} \quad (Watts)$

where

• I<sub>Q</sub> is the quiescent operating current (neglecting drivers)

1

The maximum power capability of the TPS40074 PowerPAD package is dependent on the layout as well as air flow. The thermal impedance from junction to air ambient assuming 2-oz. copper trace and thermal pad with solder and no air flow is  $\theta_{JA} = 60 \text{ °C/W}$

The maximum allowable package power dissipation is related to ambient temperature by Equation 17.

$$\mathsf{P}_{\mathsf{T}} = \frac{\mathsf{T}_{\mathsf{J}} - \mathsf{T}_{\mathsf{A}}}{\theta_{\mathsf{J}\mathsf{A}}} \quad (\mathsf{Watts}) \tag{17}$$

Substituting Equation 17 into Equation 16 and solving for  $f_{SW}$  yields the maximum operating frequency for the TPS4007x. The result is described in Equation 18.

$$f_{SW} = \frac{\left( \left\lfloor \frac{(I_J - I_A)}{(\theta_{JA} \times V_{IN})} \right\rfloor - I_Q \right)}{(2 \times Q_g)} \quad (Hz)$$

(18)

### **BOOST DIODE**

The TPS40074 has internal diodes to charge the boost capacitor connected from SW to BOOST. The drop across this diode is rather large at 1.4-V nominal at room temperature resulting in the drive voltage to the high-side MOSFET being reduced by this amount from the DBP voltage. If this drop is too large for a particular application, an external diode may be connected from DBP (anode) to BOOST (cathode). This provides significantly improved gate drive for the high-side MOSFET, especially at lower input voltages.

### LOW VOLTAGE OPERATION

If the programmable UVLO is set to less than 6.5 V nominal, connect a 330-k $\Omega$  resistor across the soft-start capacitor. This eliminates a race condition inside the device that can lead to an output voltage overshoot on power down of the part.

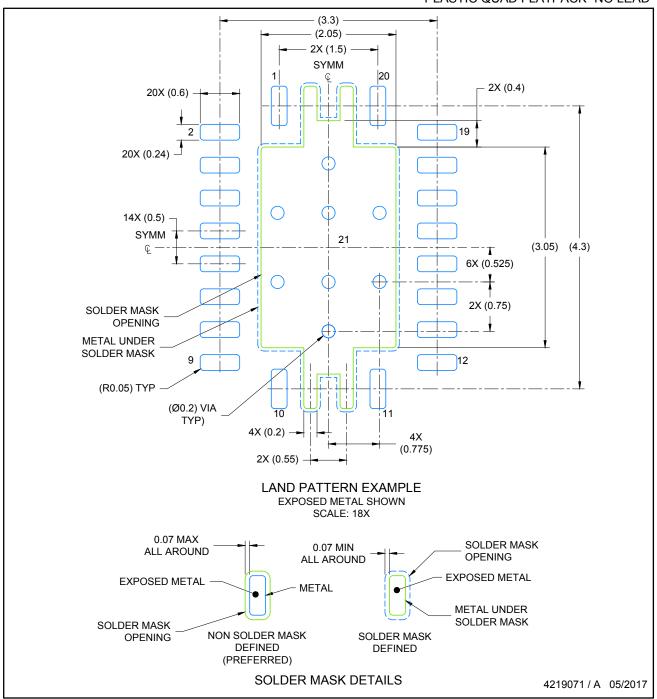

## **GROUNDING AND BOARD LAYOUT**

The TPS40074 provides separate signal ground (GND) and power ground (PGND) pins. Care should be given to proper separation of the circuit grounds. Each ground should consist of a plane to minimize its impedance if possible. The high power *noisy* circuits such as the output, synchronous rectifier, MOSFET driver decoupling capacitor (DBP), and the input capacitor should be connected to PGND plane.

Sensitive nodes such as the FB resistor divider and RT should be connected to the GND plane. The GND plane should only make a single point connection to the PGND plane. It is suggested that the GND pin be tied to the copper area for the PowerPAD underneath the chip. Tie the PGND to the PowerPAD copper area as well and make the connection to the power circuit ground from the PGND pin. Reference the output voltage divider to the GND pin.

Component placement should ensure that bypass capacitors (LVPB and DBP) are located as close as possible to their respective power and ground pins. Also, sensitive circuits such as FB, RT and ILIM should not be located near high dv/dt nodes such as HDRV, LDRV, BOOST, and the switch node (SW). Failure to follow careful layout practices results in sub-optimal operation.

## SYNCHRONOUS RECTIFIER CONTROL

Table 2 describes the state of the rectifier MOSFET control under various operating conditions.

| SYNCHRONOUS RECTIFIER OPERATION DURING                                            |                                                                                               |                                                    |                                                               |  |  |  |  |  |  |  |  |

|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|----------------------------------------------------|---------------------------------------------------------------|--|--|--|--|--|--|--|--|

| SOFT-START                                                                        | NORMAL                                                                                        | FAULT<br>(FAULT RECOVERY IS SAME<br>AS SOFT-START) | OVERVOLTAGE                                                   |  |  |  |  |  |  |  |  |

| Off until first high-side pulse is detected, then on when high-side MOSFET is off | Turns off at the start of a new<br>cycle. Turns on when the<br>high-side MOSFET is turned off | OFF                                                | Turns OFF only at start of next cycle ON if duty cycle is > 0 |  |  |  |  |  |  |  |  |

#### Table 2. Synchronous Rectifier MOSFET States

For proper operation, the total gate charge of the MOSFET connected to LDRV should be less than 50nC.

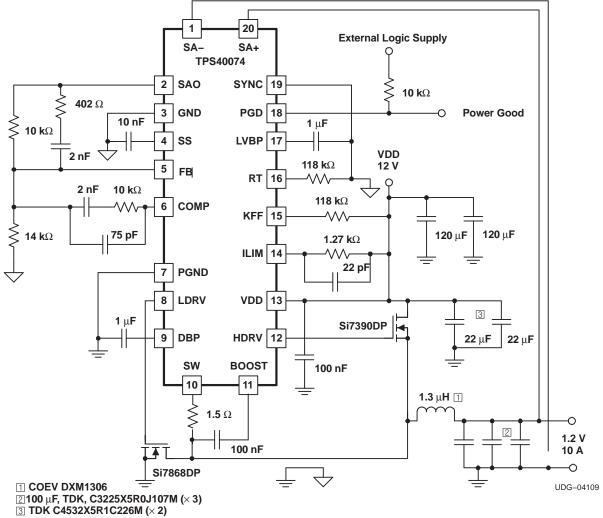

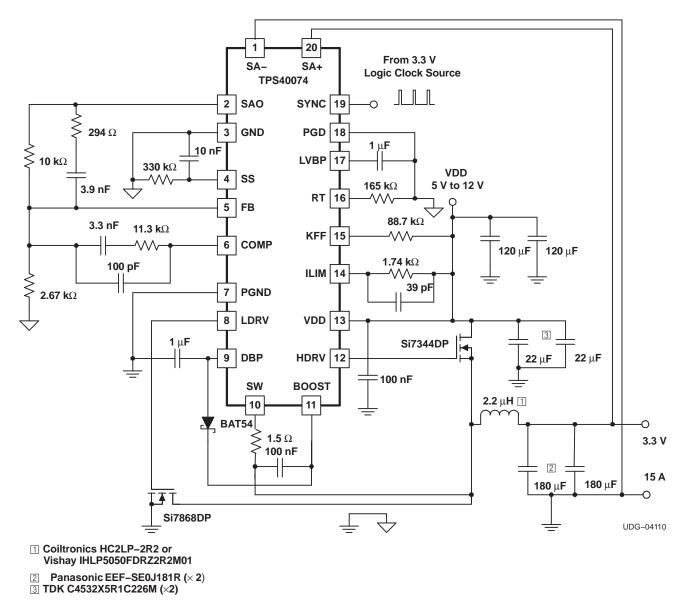

# **DESIGN EXAMPLE**

### **1. SPECIFICATIONS**

| PARAMETER           |                                  | PARAMETER TEST CONDITIONS                        |      | TYP  | MAX  | UNIT |

|---------------------|----------------------------------|--------------------------------------------------|------|------|------|------|

| INPUT CU            | RRENT                            |                                                  | L.   |      |      |      |

| V <sub>IN</sub>     | Input voltage                    |                                                  | 10.8 | 12.0 | 13.2 |      |

| Vo                  | Output voltage                   | I <sub>OUT</sub> = 10 A                          |      | 1.5  | 5    | V    |

|                     | Regulation                       |                                                  | 1.47 |      | 1.53 |      |

| V <sub>RIPPLE</sub> | Output ripple voltage            | I <sub>O(max)</sub> = 15 A                       |      | 30   |      |      |

| V <sub>OVER</sub>   | Output overshoot                 | I <sub>STEP</sub> = 8 A                          |      | 50   |      | mV   |

| V <sub>UNDER</sub>  | Output undershoot                | I <sub>STEP</sub> = 8 A                          |      | 50   |      |      |

| I <sub>LOAD</sub>   | Output current                   |                                                  | 0    |      | 15   | ^    |

| I <sub>SCP</sub>    | Short circuit current trip point |                                                  | 16   |      | 30   | A    |

| η                   | Efficiency                       | V <sub>IN</sub> = 12 V, I <sub>LOAD</sub> = 15 A |      | 85%  |      |      |

| f <sub>SW</sub>     | Switching frequency              |                                                  |      | 400  |      | kHz  |

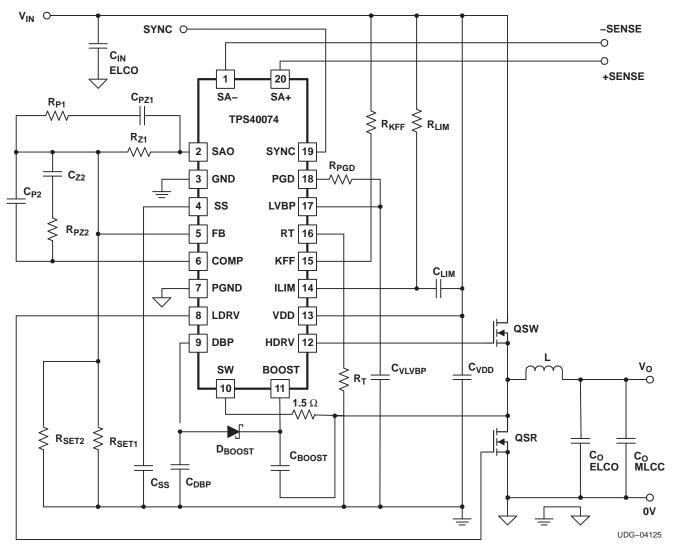

# 2. SCHEMATIC

#### 3. COMPONENT SELECTION

### 3. 1 Power Train Components

Designers familiar with the buck converter can skip to section 3.2 Component Selection for TPS40074.

#### 3.1.1 Output Inductor, Lo

The output inductor is one of the most important components to select. It stores the energy necessary to keep the output regulated when the switch MOSFET is turned off. The value of the output inductor dictates the peak and RMS currents in the converter. These currents are important when selecting other components. Equation 19 can be used to calculate a value for L.

$$L = \frac{V_{O}}{V_{IN(max)}} \times \frac{\left(V_{IN(max)} - V_{O}\right)}{f_{SW} \times \Delta I}$$

(19)

$\Delta$  I is the allowable ripple in the inductor. Selecting  $\Delta I$  also sets the output current when the converter goes into discontinuous mode (DCM) operation. Since this converter utilizes MOSFETs for the rectifier, DCM is not a major concern. Select  $\Delta I$  to be between 20% and 30% of maximum I<sub>LOAD</sub>. For this design,  $\Delta I$  of 3 A was selected. The calculated L is 1.1 µH. A standard inductor with value of 1.0 µH was chosen. This increases  $\Delta I$  by about 10% to 3.3 A.

With this  $\Delta I$  value, calculate the RMS and peak current flowing in L<sub>0</sub>. Note this peak current is also seen by the switching MOSFET and synchronous rectifier.

$$I_{\text{LOAD}_{\text{RMS}}} = \sqrt{I_{\text{LOAD}}^2 + \frac{\Delta l^2}{12}} = 15.03 \text{ A}$$

(20)

$$I_{\text{PK}} = I_{\text{LOAD}} + \frac{\Delta l^2}{2} = 16.65 \text{ A}$$

(21)

#### 3.1.2 Output Capacitor, Co, ELCO and MLCC

Several parameters must be considered when selecting the output capacitor. The capacitance value should be selected based on the output overshoot,  $V_{OVER}$ , and undershoot,  $V_{UNDER}$ , during a transient load,  $I_{STEP}$ , on the converter. The equivalent series resistance (ESR) is chosen to allow the converter meet the output ripple specification,  $V_{RIPPLE}$ . The voltage rating must be greater than the maximum output voltage. Other parameters to consider are: equivalent series inductance which is important in fast transient load situations. Also size and technology can be factors when choosing the output capacitor. In this design a large capacitance electrolytic type capacitor,  $C_O$  ELCO, is used to meet the overshoot and under shoot specifications. Its ESR is chosen to meet the output ripple specification. While a smaller multiple layer ceramic capacitor,  $C_O$  MLCC, is used to filter high frequency noise.

The minimum required capacitance and maximum ESR can be calculated using the equations below.

$$C_{O} > \frac{L \times I_{STEP}^{2}}{2 \times V_{UNDER} \times D_{MAX} \times (V_{IN} - V_{O})}$$

(22)

$$C_{O} > \frac{V_{OVER} \times V_{O}}{2 \times V_{OVER} \times V_{O}}$$

$$ESR < \frac{V_{RIPPLE}}{2 \times V_{OVER} \times V_{O}}$$

(23)

$$ESR < \frac{-\alpha + 2L}{\Delta I}$$

(24)

Using Equation 22 through Equation 24, the capacitance for C<sub>0</sub> should be greater than 495  $\mu$ F and its ESR should be less than 9.1m $\Omega$ . The 1000  $\mu$ F/25 V capacitor from Rubycon's MBZ or Panasonic's series EEU-FL was chosen. Its ESR is 19 m $\Omega$ , so two in parallel are used. The slightly higher ESR is offset by the four times increase in capacitance. A 2.2  $\mu$ F/16 V MLCC is also added in parallel to reduce high frequency noise.

### 3.1.3. Input Capacitor, C<sub>IN</sub>, ELCO and MLCC

The input capacitor is selected to handle the ripple current of the buck stage. Also a relative large capacitance is used to keep the ripple voltage on the supply line low. This is especially important where the supply line is high impedance. It is recommended that the supply line be kept low impedance. The input capacitor ripple current can be calculated using Equation 25.

$$I_{CAP(RMS)} = \sqrt{\left[\left(I_{LOAD(max)} - I_{IN(avg)}^{2}\right) + \frac{\Delta I^{2}}{12}\right] \times D} + I_{IN(avg)}^{2} \times (1 - D)$$

(25)

where

I<sub>IN(avg)</sub> is the average input current

This is calculated simply by multiplying the output DC current by the duty cycle. The ripple current in the input capacitor is 5.05 A. A 1206 MLCC using X7R material has a typical dissipation factor of 5%. For a 2.2  $\mu$ F capacitor at 400 kHz the ESR is approximately 7.2 m $\Omega$ . If two capacitors are used in parallel the power dissipation in each capacitor is less than 46 mW.

A 470 µF/16 V electrolytic capacitor is added to maintain the voltage on the input rail.

### 3.1.4 Switching MOSFET, QSW

The following key parameters must be met by the selected MOSFET.

- Drain source voltage, V<sub>DS</sub>, must be able to withstand the input voltage plus spikes that may be on the switching node. For this design a V<sub>DS</sub> rating of 25 V to 30 V is recommended.

- Drain current, I<sub>D</sub>, at 25°C, must be greater than that calculated using Equation 26. For this design, I<sub>D</sub> should be greater than 5 A.

$$I_{D} = \sqrt{\frac{V_{O}}{V_{IN(min)}} \times \left(I_{LOAD(max)}^{2} + \frac{\Delta I^{2}}{12}\right)}$$

(26)

- Gate source voltage,  $V_{GS}$  must be able to withstand the gate voltage from the control device . For the TPS40074 this is 9 V.

Once the above boundary parameters are defined the next step in selecting the switching MOSFET is to select the key performance parameters. Efficiency is the performance characteristic which drives the other selection criteria. Target efficiency for this design is 90%. Based on 1.5-V output and 15 A this equates to a power loss in the converter of 2.5 W. Using this figure a target of 0.5 W dissipated in the switching MOSFET was chosen.

Equation 27 through Equation 30 can be used to calculate the power loss, P<sub>QSW</sub>, in the switching MOSFET

$$P_{QSW} = P_{QSW(CON)} + P_{QSW(SW)} + P_{QSW(GATE)}$$

(27)

$$P_{QSW(CON)} = R_{DS(on)} \times I_{D}^{2} = R_{DS(on)} \times \frac{V_{O}}{V_{IN}} \times \left(I_{LOAD}^{2} + \frac{\Delta I^{2}}{12}\right)$$

(28)