#### Data Sheet

March 2015

#### Features

- Programmable synthesizers generate any clockrate from 1 kHz to 750 MHz

- Precision synthesizers generate clocks with jitter below 0.7 ps RMS for 10 G PHYs

- Programmable digital PLL synchronize to any clock rate from 1 kHz to 750 MHz

- Flexible two-stage architecture translates between arbitrary data rates, line coding rates and FEC rates

- Digital PLL filter jitter from 14 Hz, 28 Hz, 56 Hz, 112 Hz, 224 Hz, 448 Hz or 896 Hz

- Automatic hitless reference switching and digital holdover on reference fail

- Two reference inputs configurable as single ended

or differential

- · Four LVPECL outputs and two LVCMOS outputs

- Operates from a single crystal resonator or clock oscillator

- · Customer defined default device configuration,

#### **Ordering Information**

ZL30152GGG2 64 Pin LBGA\* Trays

\*Pb Free Tin/Silver/Copper -40°C to +85°C

including input/output frequencies, is available via OTP(One Time Programmable) memory

Dynamically configurable via SPI/I2C interface and volatile configuration registers

## Applications

- Clock Generation for Physical Line Interface:

- SONET/SDH, OC-192/OC-48

- SONET/SDH with FEC

- 10G Base X, R and W

- 100 BaseX, GE, Fibre channel

- Clock Generation and Distribution for back plane Interface:

- TDM, Telecom Bus, Utopia, SBI

- Rapid-IO, PCI-Express, serial MII, Star Fabric, XAUI

## **Table of Contents**

| 1.0 Pin Diagram                                                             | . 9 |

|-----------------------------------------------------------------------------|-----|

| 2.0 Pin Description.                                                        | 10  |

| 3.0 Application Example                                                     | 14  |

| 4.0 Functional Description                                                  | 15  |

| 4.1 Input Sources                                                           |     |

| 4.2 Input Reference Monitoring                                              |     |

| 4.2.1 DPLL General Characteristics                                          |     |

| 4.2.2 DPLL States                                                           |     |

| 4.2.3 DPLL Rate Conversion Function and FEC Support.                        |     |

| 4.2.4 DPLL Input to Output And Output to Output Phase Alignment             |     |

| 4.3 Frequency Synthesis Engine         4.4 Dividers and Skew Management     |     |

| 4.4 Dividers and Skew Management.                                           |     |

| 4.6 Output Drivers                                                          |     |

| 4.7 Input Buffers                                                           |     |

| 4.8 Master Clock Interface.                                                 |     |

| 4.9 Clock Oscillator                                                        |     |

| 4.10 Power Up/Down Sequence                                                 | 26  |

| 4.11 Power Supply Filtering.                                                |     |

| 4.12 Reset and Configuration Circuit                                        |     |

| 4.13 Ultra Low Jitter Synthesizer Filter Components and Recommended Layout  |     |

| 5.0 Configuration and Control                                               |     |

| 5.1 Custom OTP Configuration                                                |     |

| 5.2 GPIO Configuration and Programmability                                  |     |

| 5.3 Configuration Registers                                                 |     |

| 5.3.1 Input Reference Configuration and Programmability                     |     |

| 5.3.3 Output Multiplexer Configuration and Programmability                  |     |

| 5.3.4 Synthesis Macro Configuration and Programmability                     |     |

| 5.3.5 Output Dividers and Skew Management Configuration and Programmability |     |

| 5.3.6 Output Drivers configuration and Programmability                      |     |

| 5.4 State Control and Reference Switch Modes                                |     |

| 5.4.1 Un-managed Mode                                                       |     |

| 5.4.2 Managed Mode                                                          | 35  |

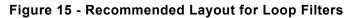

| 6.0 Host Interface                                                          | 36  |

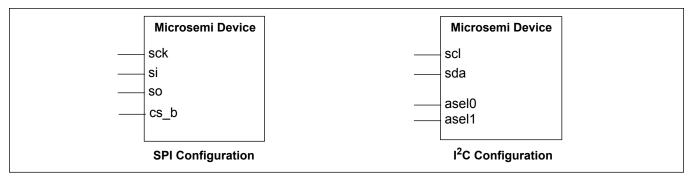

| 6.1 Serial Peripheral Interface                                             |     |

| 6.1.1 Least Significant Bit (LSB) First Transmission Mode                   |     |

| 6.1.2 Most Significant Bit (MSB) First Transmission Mode.                   |     |

| 6.1.3 SPI Burst Mode Operation                                              |     |

| 6.1.4 I2C Interface.                                                        |     |

| 7.0 Register Map                                                            |     |

| 8.0 Detailed Register Map                                                   |     |

| 9.0 AC and DC Electrical Characteristics                                    |     |

| 10.0 Performance Characterization                                           |     |

| 10.1 Output Clocks Jitter Generation                                        |     |

| 10.2 DPLL Performance Characteristics                                       |     |

| 11.0 Thermal Characteristics                                                |     |

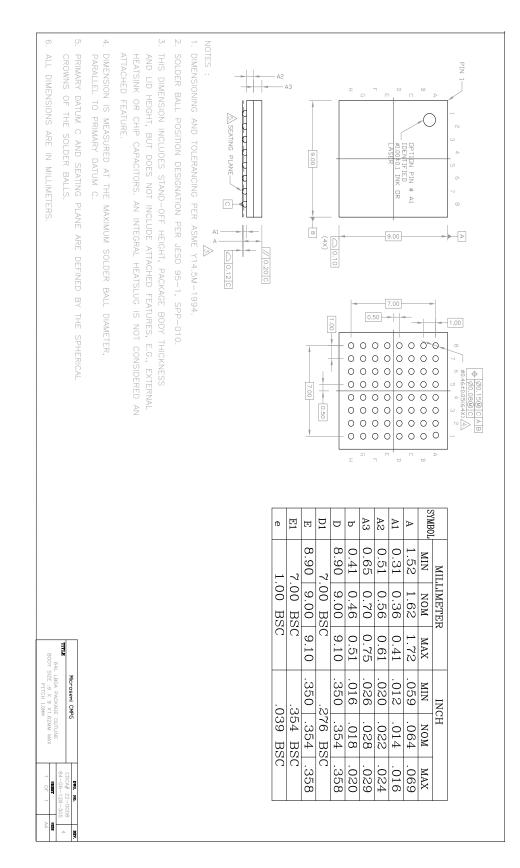

| 12.0 Mechanical Drawing                                                     |     |

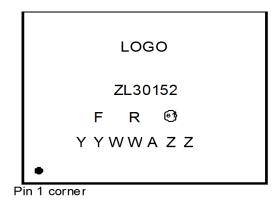

| 13.0 Package Markings                                                       |     |

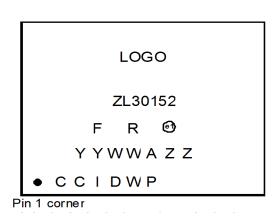

| 13.1 64-pin BGA. Package Top Mark Format                                    | 96  |

# List of Figures

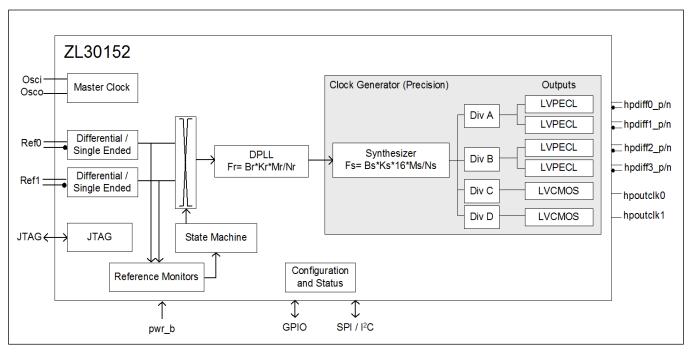

| Figure 1 - Functional Block Diagram                                           |

|-------------------------------------------------------------------------------|

| Figure 2 - Application Diagram                                                |

| Figure 3 - Output Clocks Muxing Configuration                                 |

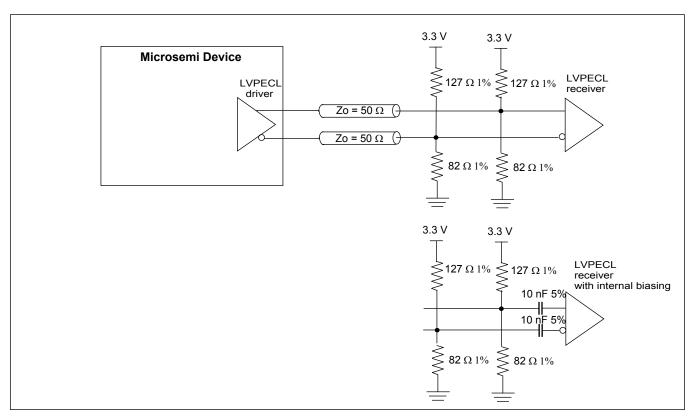

| Figure 4 - Terminating HP LVPECL Outputs                                      |

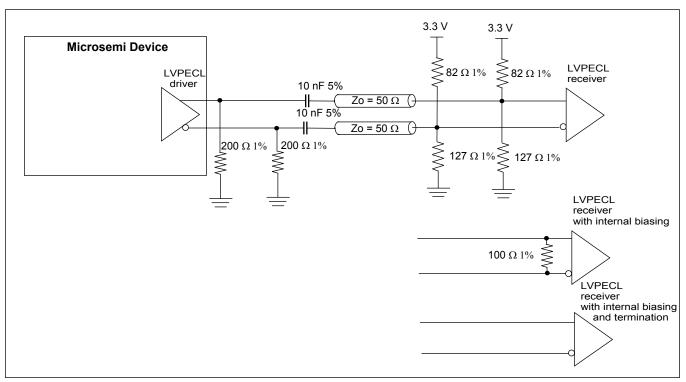

| Figure 5 - Terminating AC Coupled HP LVPECL Outputs                           |

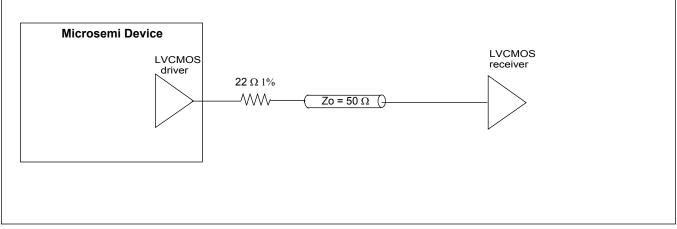

| Figure 6 - Terminating HP LVCMOS Outputs                                      |

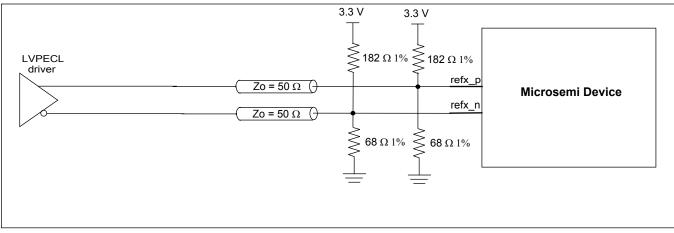

| Figure 7 - Differential DC Coupled LVPECL Termination                         |

| Figure 8 - Differential AC Coupled LVPECL Termination                         |

| Figure 9 - Differential DC Coupled LVDS Termination                           |

| Figure 10 - Differential AC Coupled LVDS Termination                          |

| Figure 11 - Single Ended CMOS Termination                                     |

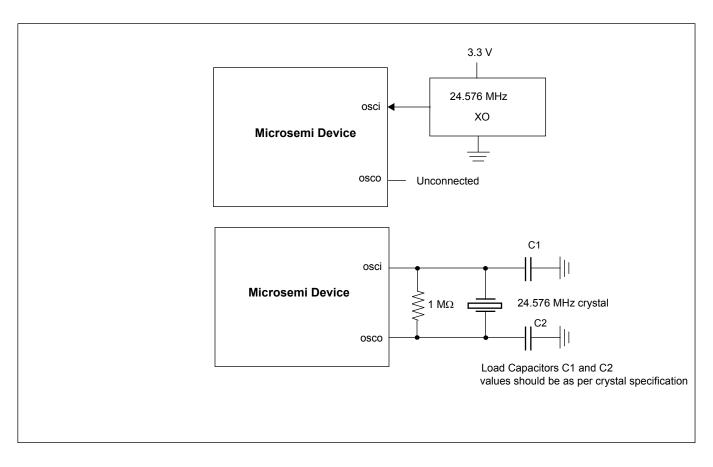

| Figure 12 - Clock Oscillator Circuit                                          |

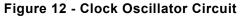

| Figure 13 - Typical Power-Up Reset and Configuration Circuit                  |

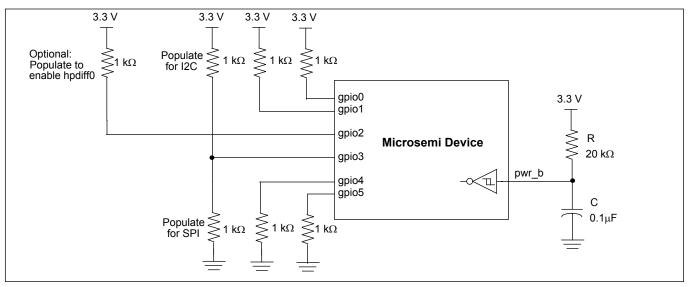

| Figure 14 - APLL Filter Component Values                                      |

| Figure 15 - Recommended Layout for Loop Filters                               |

| Figure 16 - Serial Interface Configuration                                    |

| Figure 17 - Serial Peripheral Interface Functional Waveforms - LSB First Mode |

| Figure 18 - Serial Peripheral Interface Functional Waveforms - MSB First Mode |

| Figure 19 - Example of a Burst Mode Operation                                 |

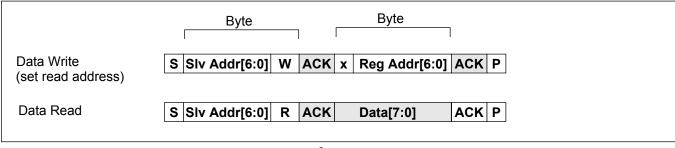

| Figure 20 - I2C Data Write Protocol                                           |

| Figure 21 - I2C Data Read Protocol                                            |

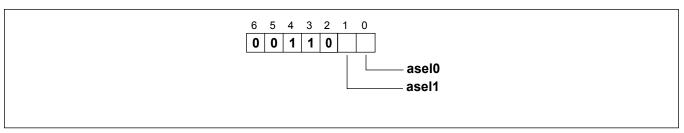

| Figure 22 - I2C 7-bit Slave Address                                           |

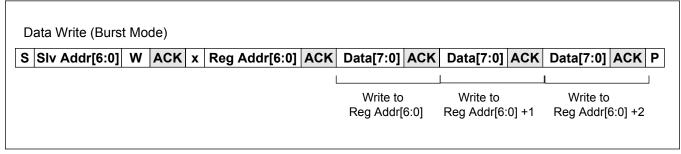

| Figure 23 - I2C Data Write Burst Mode                                         |

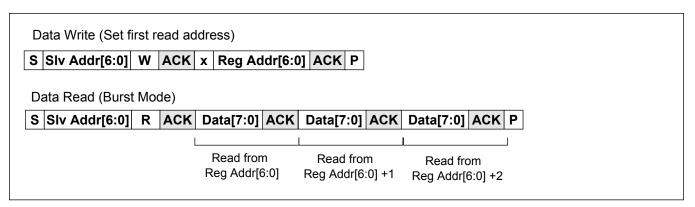

| Figure 24 - I2C Data Read Burst Mode                                          |

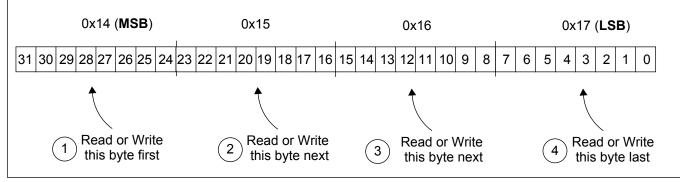

| Figure 25 - Accessing Multi-byte Register Values                              |

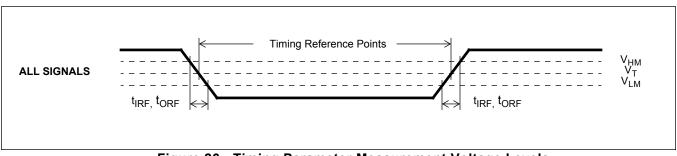

| Figure 26 - Timing Parameter Measurement Voltage Levels                       |

| Figure 27 - Input To Output Timing for hpoutclk0                              |

| Figure 28 - Input To Output Timing To outclk0                                 |

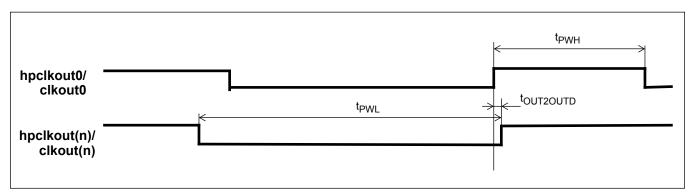

| Figure 29 - Output Timing Referenced to hpclkout0/clkout0                     |

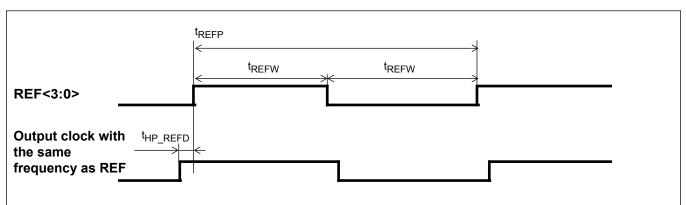

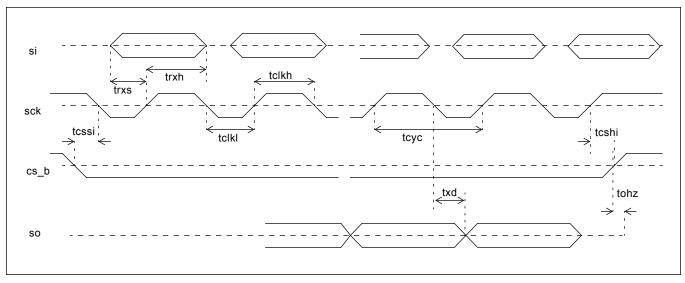

| Figure 30 - Serial Peripheral Interface Timing - LSB First Mode               |

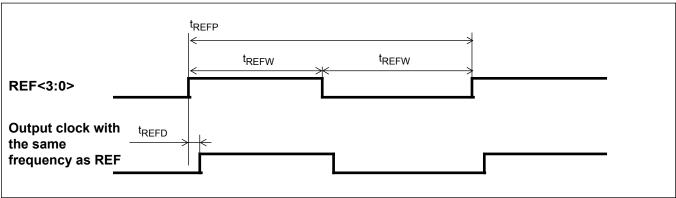

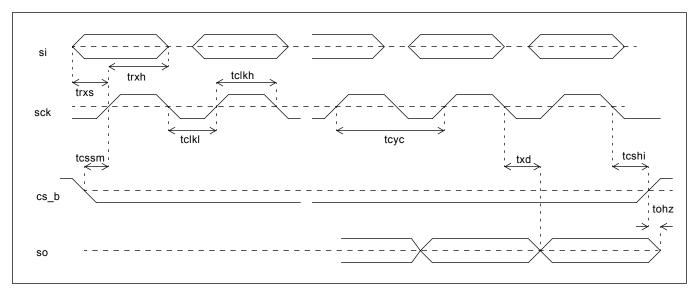

| Figure 31 - Serial Peripheral Interface Timing - MSB First Mode               |

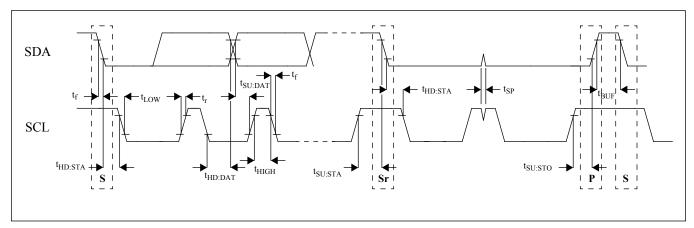

| Figure 32 - I2C Serial Microport Timing                                       |

| Figure 33 - Non-customized Device Top Mark                                    |

| Figure 34 - Custom Factory Programmed Device Top Mark                         |

## List of Tables

| Table 1 - Pin Description                                    | . 10 |

|--------------------------------------------------------------|------|

| Table 2 - Guard Soak Time To Disqualify A Reference          | . 16 |

| Table 3 - Guard Soak Time To Qualify A Reference             | . 16 |

| Table 4 - Master Clock Frequency Selection                   | . 26 |

| Table 5 - Serial Interface Selection                         | . 36 |

| Table 6 - Register Map                                       | . 42 |

| Table 7 - Serial Peripheral Interface Timing.                | . 90 |

| Table 8 - I2C Serial Microport Timing                        | . 92 |

| Table 9 - Jitter Generation Specifications - HPDIFF Outputs  |      |

| Table 10 - Jitter Generation Specifications - HPOUT Outputs. | . 93 |

| Table 11 - DPLL Characteristics                              | . 93 |

| Table 12 - Thermal Data                                      | . 94 |

| Table 13 - Package Marking Legend                            | . 96 |

## **Change Summary**

Below are the changes from the June 2012 issue to the March 2015 issue:

| Page | Item                               | Change                                                            |

|------|------------------------------------|-------------------------------------------------------------------|

| 1    | Ordering Information               | Removed ZL30152GGG (leaded version) from the ordering information |

| 1    | Added Features bullet              | Included availability of customer defined default configurations  |

| 15,  | Updated section 4.0, 5.0 and added | Updated to included the availability of Custom OTP                |

| 29,  | 5.1                                | configuration                                                     |

| 29   |                                    |                                                                   |

| 96   | 13.0, "Package Markings"           | Added section 13 for package markings                             |

Below are the changes from the January 2012 issue to the June 2012 issue:

| Page | Item                            | Change                        |

|------|---------------------------------|-------------------------------|

| 45   | Register 0xC6 - Chip_revision_2 | Updated chip_revision to 0x03 |

| and  |                                 |                               |

| 80   |                                 |                               |

Below are the changes from the December 2011 issue to the January 2012 issue

| Page            | Item                                                 | Change                                                                                                 |  |  |  |  |

|-----------------|------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--|--|--|--|

| 40              | Procedure to write registers                         | Added a procedure to update registers                                                                  |  |  |  |  |

| 41              | Time Between two write accesses to the same register | Changed 200ms to 6ms and added register 0x0D to the list of regsiters that don't require a wait period |  |  |  |  |

| 41              | Sticky read registers                                | Updated StickyR procedure                                                                              |  |  |  |  |

| 45<br>and<br>80 | Register 0xC6- Chip_revision_2                       | Added register 0xC6                                                                                    |  |  |  |  |

| 46              | Register 0x00 - id_reg                               | Updated chip_revision bits[6:5]                                                                        |  |  |  |  |

| 51              | Register 0x0D - Sticky_r_lock                        | Updated description of register 0x0D                                                                   |  |  |  |  |

Below are the changes from the January 2011 issue to the December 2011 issue

| Page | Item     | Change                                                                                                                                                                                                                                           |

|------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | Features | <ul> <li>Output frequency is changed from "1 kHz to 720MHz" to "1kHz to 750MHz"</li> <li>Input frequency is changed from "1 kHz to 720MHz" to "1kHz to 750MHz"</li> <li>Corrected package description in ordering information to LBGA</li> </ul> |

| Page | Item                                                             | Change                                                                                                                                                                                                                                                                                |  |  |  |  |

|------|------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 10   | Pin description                                                  | <ul> <li>Maximum frequency limit on differential outputs i changed from " 720MHz" to "750MHz"</li> <li>Maximum frequency limit on differential inputs is changed from " 720MHz" to "750MHz"</li> <li>Waiting time after pwr_b pin goes high is changed from 30 ms to 50 ms</li> </ul> |  |  |  |  |

| 10   | Pin description- Control and Status(<br>pwr_b pin and GPIO pins) | Waiting time after pwr_b pin goes high is changed from 30 ms to 50 ms                                                                                                                                                                                                                 |  |  |  |  |

| 14   | Application example                                              | Maximum frequency is changed from " 720MHz" to "750MHz"                                                                                                                                                                                                                               |  |  |  |  |

| 15   | Input Sources                                                    | Maximum frequency limit on differential inputs is changed from " 720MHz" to "750MHz"                                                                                                                                                                                                  |  |  |  |  |

| 19   | Divider and skew management                                      | Maximum frequency limit on differential outputs is changed from " 720MHz" to "750MHz"                                                                                                                                                                                                 |  |  |  |  |

| 20   | Output drivers                                                   | Maximum speed of differential outputs is changed from " 720MHz" to "750MHz"                                                                                                                                                                                                           |  |  |  |  |

| 23   | Input Buffers                                                    | Input frequency range for differential inputs is<br>changed fromfrom "1kHz to 720MHz" to "1kHz to<br>750MHz"                                                                                                                                                                          |  |  |  |  |

| 25   | Clock oscillator                                                 | Time for GPIO[1:0] pins to be held high is changed from 30 ms to 50 ms                                                                                                                                                                                                                |  |  |  |  |

| 27   | Power Filtering<br>Reset and Configuration Circuit               | <ul> <li>Application note for power filtering is changed<br/>from ZLAN-269 to ZLAN-230</li> <li>Waiting time after pwr_b pin goes high is</li> </ul>                                                                                                                                  |  |  |  |  |

|      |                                                                  | changed from 30 ms to 50 ms                                                                                                                                                                                                                                                           |  |  |  |  |

| 31   | DPLL0 Lock Indication 2                                          | "1us during 10s period" lock condition is changed to<br>"10us during 1s period" .                                                                                                                                                                                                     |  |  |  |  |

| 34   | Un-managed Mode                                                  | LOS detected a failure and RefSwMask<0> is at<br>logic "1" is changed to<br>LOS detected a failure and HOMask<0> is at logic<br>"1"                                                                                                                                                   |  |  |  |  |

| 35   | Managed Mode                                                     | LOS detected a failure and RefSwMask<0> is at<br>logic "1" is changed to<br>LOS detected a failure and HOMask<0> is at logic<br>"1"                                                                                                                                                   |  |  |  |  |

| 36   | Host interface                                                   | Time for GPIO[ 3 ]pin to be held at their appropriate value is changed form 30 ms to 50 ms                                                                                                                                                                                            |  |  |  |  |

| 41   | Reading from Sticky Read (StickyR)<br>Registers                  | Updated the StickyR procedure                                                                                                                                                                                                                                                         |  |  |  |  |

| 41   | Time between two write accesses to the same register             | For page_register at address 0x7F, there is no waiting time required between two write accesses.                                                                                                                                                                                      |  |  |  |  |

| 42   | Table 6                                                          | Heading of first column is changed from "Page_Addr" to "Reg_Addr"                                                                                                                                                                                                                     |  |  |  |  |

| 46   | Detailed register map:register id_reg                            | Time for bit 7 to go high after the device is reset is changed from 30 ms to 50 ms.                                                                                                                                                                                                   |  |  |  |  |

| Page | Item                                                        | Change                                                                                                                                                                                         |  |  |  |

|------|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 46   | Detailed Register Map                                       | "Page_Address" is changed to "Register_Address" for registers which addresses are from 0x80 to 0x85                                                                                            |  |  |  |

| 46   | Register 0x00                                               | Updated ready bit indication                                                                                                                                                                   |  |  |  |

| 58   | Register 0x33                                               | added details to the description of bits [7:6]                                                                                                                                                 |  |  |  |

| 63   | Register 0x4C                                               | 000 = +/- 0.1% (in Ref0 frequency units) is changed to $000 = +/- 0.1%$ (in Ref1 frequency units)                                                                                              |  |  |  |

| 72   | Register synth_post_div_C                                   | Bit[15:0]: note added for odd post divider                                                                                                                                                     |  |  |  |

| 74   | Register synth_post_div_D                                   | Bit[15:0]: note added for odd post divider                                                                                                                                                     |  |  |  |

| 83   | Register 0xF7                                               | updated register description                                                                                                                                                                   |  |  |  |

| 84   | DC Electrical Characteristics -Power<br>Core                | <ul> <li>"Power for Each Synthesis Engine" is changed to<br/>"Current for Each Synthesis Engine"</li> <li>"PSYN" is changed to "ISYN"</li> </ul>                                               |  |  |  |

| 85   | DC Electrical Characteristics - High<br>Performance Outputs | <ul> <li>All "AV<sub>DD-IO</sub>" symbols are replaced with "AV<sub>DD</sub>"</li> <li>Note added for differential output voltage when differential frequency is higher than 720MHz</li> </ul> |  |  |  |

| 88   | AC Electrical Characteristics* - Inputs                     | Maximum frequency of differential inputs is changed from " 720MHz" to "750MHz"                                                                                                                 |  |  |  |

| 89   | AC Electrical Characteristics* -<br>Outputs                 | Maximum frequency of differential outputs is changed from " 720MHz" to "750MHz"                                                                                                                |  |  |  |

| 93   | Output Clocks Jitter Generation                             | Jitter measurement filter for 77.76MHz is changed from "12kHz-5MHz" to "12kHz-20MHz"                                                                                                           |  |  |  |

| 95   | Mechanical Drawing                                          | Replaced drawing to reflect correct package description                                                                                                                                        |  |  |  |

Below are the changes from the November 2010 issue to the January 2011 issue.

| Page | Item                                                | Change                                                         |  |  |  |  |

|------|-----------------------------------------------------|----------------------------------------------------------------|--|--|--|--|

| 12   | Coarse Frequency Monitor (CFM)                      | Minimum frequency irregularity is changed from 1% to 0.1%      |  |  |  |  |

| 32   | 6.1, "Serial Peripheral Interface"                  | SPI burst mode operation description is added                  |  |  |  |  |

| 34   | Figure 19                                           | Example of a Burst Mode Operation is added                     |  |  |  |  |

| 43   | Register 0x07, bit 2                                | Description is for CFM instead of SCM                          |  |  |  |  |

| 83   | Table - AC Electrical Characteristics*<br>- Outputs | Row 2, clock duty cycle is changed from "43%-57%" to "45%-55%" |  |  |  |  |

| 83   | Table - AC Electrical Characteristics*<br>- Outputs | Row 3, note "From 0.2AVDD-IO to 0.8AVDD-IO" is removed         |  |  |  |  |

## 1.0 Pin Diagram

|   | 1             | 2             | 3           | 4           | 5          | 6           | 7          | 8          |

|---|---------------|---------------|-------------|-------------|------------|-------------|------------|------------|

| A | hpdiff1_p     | hpdiff2_p     | hpdiff3_p   | avss        | filter     | avss        | Osco       | avss       |

| В | <br>hpdiff1_n | <br>hpdiff2_n | hpdiff3_n   | avdd        | filter_ref | )<br>avdd   | osci       | avdd       |

| С | <br>hpdiff0_n | hpdiff0_p     | avss        | avcore      | )<br>at    | avss        | avss       | VSS        |

| D | avss          | avdd          | )<br>avdd   | VSS         | VSS        | VSS         | vdd_io     | O<br>pwr_b |

| E | hpoutclk1     | hpoutclk0     | gpio5       | vcore       | Vss        | )<br>gpio0  | Cs_b_asel0 | Scl_sck    |

| F | avss          | avdd          | test_en     | vcore       | vcore      | O<br>gpio3  | O<br>gpio2 | O<br>gpio1 |

| G | O<br>gpio6    | So_asel1      | ⊖<br>trst_b | avcore      | avss       | avdd        | )<br>tms   | )<br>tdi   |

| н | gpio4         | ⊖<br>si_sda   | ⊖<br>tdo    | C<br>ref0_p | Cref0_n    | C<br>ref1_p | Cref1_n    | ⊖<br>tck   |

- A1 corner is identified by metallized markings.

## 2.0 Pin Description

All device inputs and output are LVCMOS unless it was specifically stated to be differential.

| Ball #                                       | Name                                                                                                 | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------------------------------------|------------------------------------------------------------------------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input Ref                                    | erence                                                                                               |     |                                                                                                                                                                                                                                                                                                                                                                                                                        |

| H4<br>H5<br>H6<br>H7                         | ref0_p<br>ref0_n<br>ref1_p<br>ref1_n                                                                 | I   | <b>Input Reference 0 and 1.</b> Input reference sources used for synchronization. The positive and negative pair of these inputs accepts a differential input signal. The refx_p input terminal accept a CMOS input reference. These inputs could be used as a device external feedback input.                                                                                                                         |

|                                              |                                                                                                      |     | 750 MHz on differential inputs.                                                                                                                                                                                                                                                                                                                                                                                        |

| Output C                                     | locks                                                                                                |     |                                                                                                                                                                                                                                                                                                                                                                                                                        |

| E2<br>E1                                     | hpoutclk0<br>hpoutclk1                                                                               | 0   | High Performance Output Clock 0 to 1. This output can be configured to provide any one of the single ended high performance clock outputs.<br>Maximum frequency limit on single ended LVCMOS outputs is 177.5 MHz                                                                                                                                                                                                      |

| C2<br>C1<br>A1<br>B1<br>A2<br>B2<br>A3<br>B3 | hpdiff0_p<br>hpdiff0_n<br>hpdiff1_p<br>hpdiff1_n<br>hpdiff2_p<br>hpdiff2_n<br>hpdiff3_p<br>hpdiff3_n | 0   | High Performance Differential Output Clock 0 to 3 (LVPECL). This<br>output can be configured to provide any one of the available high<br>performance differential output clocks.<br>Maximum frequency limit on differential outputs is 750 MHz                                                                                                                                                                         |

| Control a                                    | nd Status                                                                                            |     |                                                                                                                                                                                                                                                                                                                                                                                                                        |

| D8                                           | pwr_b                                                                                                | I   | <b>Power-on Reset.</b> A logic low at this input resets the device. To ensure proper operation, the device must be reset after power-up. The pwr_b pin should be held low for at least 2 ms. This pin is internally pulled-up to $V_{DD}$ . User can access device registers either 50 ms after pwr_b goes high, or after bit 7 in register at address 0x00 goes high which can be determined by polling address 0x00. |

Table 1 - Pin Description

| Ball #                                 | Name                                                        | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------------------------------|-------------------------------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| E6<br>F8<br>F7<br>F6<br>H1<br>E3<br>G1 | gpio0<br>gpio1<br>gpio2<br>gpio3<br>gpio4<br>gpio5<br>gpio6 | I/O | <ul> <li>General Purpose Input and Output pins. These are general purpose pins managed by the internal processor based on device configuration.</li> <li>Recommended usage of GPIO include: <ul> <li>DPLL lock indicators</li> <li>DPLL holdover indicators</li> <li>Reference fail indicators</li> <li>Reference select control or monitor</li> <li>Differential output clock enable (per output or as a bank of 2 or 4 outputs)</li> <li>High performance LVCMOS output enable</li> <li>Host Interrupt Output: flags changes of device status prompting the processor to read the enabled interrupt service registers (ISR).</li> <li>Microport interface protocol I2C or SPI</li> <li>Master Clock frequency rate</li> </ul> </li> <li>Pins 5:0 are internally pulled down to GND and pin 6 is internally pulled up to V<sub>DD</sub>.</li> <li>After power on reset, device GPIO[0,1,3,4,5] configure some of device basic functions, GPIO[3] set I2C or SPI control mode, GPIO[1,0] set master clock rate selection. The GPIO[0,1,3] pins must be either pulled low or high with an external 1 KΩ resistor as needed for their assigned functions at reset; or they must be driven low or high for 50 ms after reset, and released and used for normal GPIO functions.</li> </ul> |

| Host Inte                              | rface                                                       |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| E8                                     | scl_sck                                                     | I/O | <b>Clock for Serial Interface.</b> Provides clock for serial micro-port interface. This pin is also the serial clock line (SCL) when the host interface is configured for I2C mode. As an input this pin is internally pulled up to $V_{DD}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| H2                                     | si_sda                                                      | I/O | <b>Serial Interface Input.</b> Serial interface input stream. The serial data stream holds the access command, the address and the write data bits. This pin is also the serial data line (SDA) when host interface is configured for I2C mode. This pin is internally pulled up to $V_{DD}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| G2                                     | so_asel1                                                    | I/O | <b>Serial Interface Output.</b> Serial interface output stream. As an output the serial stream holds the read data bits. This pin is also the I2C address select when host interface is configured for I2C mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| E7                                     | cs_b_asel0                                                  | Ι   | <b>Chip Select for Serial Interface.</b> Serial interface chip select, this is an active low signal. This pin is also the I2C address select when host interface is configured for I2C mode. This pin is internally pulled up to $V_{DD}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

## Table 1 - Pin Description (continued)

| Ball #         | Name               | I/O   | Description                                                                                                                                                                                                                                                                                                                    |  |

|----------------|--------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| APLL Loop      | Filter             |       |                                                                                                                                                                                                                                                                                                                                |  |

| A5             | filter             | A     | External Analog PLL Loop Filter terminal.                                                                                                                                                                                                                                                                                      |  |

| B5             | filter_ref         | A     | Analog PLL External Loop Filter Reference.                                                                                                                                                                                                                                                                                     |  |

| JTAG (IEEE     | E 1149.1) and Test |       |                                                                                                                                                                                                                                                                                                                                |  |

| F3             | test_en            | I     | <b>Test Mode Enable.</b> A logic high at this pin enables device test modes.<br>This pin is internally pulled down to GND. Connect this pin to GND.                                                                                                                                                                            |  |

| C5             | at                 | A-I/O | Analog PLL Test. Test pin for analog PLL. Leave unconnected.                                                                                                                                                                                                                                                                   |  |

| H3             | tdo                | 0     | <b>Test Serial Data Out.</b> JTAG serial data is output on this pin on the falling edge of tck. This pin is held in high impedance state when JTAG scan is not enabled.                                                                                                                                                        |  |

| G8             | tdi                | I     | <b>Test Serial Data In.</b> JTAG serial test instructions and data are shifted in on this pin. This pin is internally pulled up to $V_{DD}$ . If this pin is not used then it should be left unconnected.                                                                                                                      |  |

| G3             | trst_b             | Ι     | <b>Test Reset.</b> Asynchronously initializes the JTAG TAP controller by putting it in the Test-Logic-Reset state. This pin should be pulsed low on power-up to ensure that the device is in the normal functional state. This pin is internally pulled up to VDD. If this pin is not used then it should be connected to GND. |  |

| H8             | tck                | I     | <b>Test Clock.</b> Provides the clock to the JTAG test logic. This pin is internally pulled up to $V_{DD}$ . This pin is internally pulled up to VDD. If this pin is not used then it should be connected to GND.                                                                                                              |  |

| G7             | tms                | I     | <b>Test Mode Select.</b> JTAG signal that controls the state transitions of the TAP controller. This pin is internally pulled up to $V_{DD}$ . If this pin is not used then it should be left unconnected.                                                                                                                     |  |

| Master Clo     | ck                 |       | 1                                                                                                                                                                                                                                                                                                                              |  |

| A7             | OSCO               | A-0   | <b>Oscillator Master Clock.</b> For crystal operation, a crystal is connected from this pin to osci. Not suitable for driving other devices. For clock oscillator operation, this pin is left unconnected.                                                                                                                     |  |

| B7             | osci               | I     | <b>Oscillator Master Clock.</b> For crystal operation, a crystal is connected from this pin to osco. For clock oscillator operation, this pin is connected to a clock source.                                                                                                                                                  |  |

| Power and      | Ground             | I     | 1                                                                                                                                                                                                                                                                                                                              |  |

| D7             | V <sub>DD-IO</sub> |       | Positive Supply Voltage IO. 3.3V <sub>DC</sub> nominal.                                                                                                                                                                                                                                                                        |  |

| E4<br>F4<br>F5 | V <sub>CORE</sub>  |       | Positive Supply Voltage. +1.8V <sub>DC</sub> nominal.                                                                                                                                                                                                                                                                          |  |

#### Table 1 - Pin Description (continued)

| Ball #                                             | Name               | I/O | Description                                                  |

|----------------------------------------------------|--------------------|-----|--------------------------------------------------------------|

| B4<br>B6<br>B8<br>D2<br>D3<br>F2<br>G6             | AV <sub>DD</sub>   |     | Positive Analog Supply Voltage. +3.3V <sub>DC</sub> nominal. |

| C4<br>G4                                           | AV <sub>CORE</sub> |     | Positive Analog Supply Voltage. +1.8V <sub>DC</sub> nominal. |

| C8<br>D4<br>D5<br>D6<br>E5                         | V <sub>SS</sub>    |     | Ground. 0 Volts.                                             |

| A4<br>A6<br>A8<br>C3<br>C6<br>C7<br>D1<br>F1<br>G5 | AV <sub>SS</sub>   |     | Analog Ground. 0 Volts.                                      |

## Table 1 - Pin Description (continued)

## 3.0 Application Example

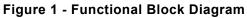

The device integrates a digital PLL and a high-speed low-jitter clock synthesizer. The digital PLL locks to reference frequencies as low as 1 kHz while maintaining loop stability and while maintaining the device's low-jitter generation. The digital PLL ensures reference switches occur in a hitless manner even with low frequency references, preventing bit errors on the transmission links. The digital PLL implements loop filters with settings as low as 14 Hz to clean noisy references; or as high as 896 Hz to closely track less noisy references. The high-speed low-jitter clock synthesizer generates clocks with frequencies as high as 750 MHz with typical jitter performance below 0.7 ps RMS. The digital PLL plus high-speed synthesizer architecture allows the device to easily convert between SONET/SDH and Ethernet frequencies, with or without FEC scaling or line coding.

Figure 2 - Application Diagram

## 4.0 Functional Description

The functional block diagram of the device is shown in Figure 1. The ZL30152 is a Universal Rate Adapting Synchronous Clock Generator that can be configured by any of the following methods; power-up with its default configuration; power-up with a custom OTP (One Time Programmable) configuration; after power-up it can be dynamically configured via the SPI/I2C port. Configurations set via the SPI/I2C are volatile and will need to be rewritten if the device is reset or powered-down. The SPI/I2C port is also used to access the status registers. The ZL30152's detailed operation is described in the following sections.

### 4.1 Input Sources

The device has 3 input sources: 2 input references (single ended or differential) and one oscillator clock source (oscillator or xtal).

The device master clock frequency is configured on reset via external voltage levels on GPIO[1:0] pins. The recommended frequency of the master clock is 24.576 MHz.

The device synchronizes (locks) to any input reference which is a 1 kHz multiple, or it synchronizes (locks) to any input reference which is an ( $M/N \ge 1$  kHz) multiple (FEC rate converted) where M and N are 16 bits wide.

The device input reference frequency is programmed during initialization, change of input reference frequency can be supported if DPLL was forced in to Holdover mode before a frequency change.

The device accepts an input reference with maximum frequency of 177.5 MHz through single ended LVCMOS input (or 750 MHz frequency through differential inputs) and a minimum frequency of 1 kHz.

#### 4.2 Input Reference Monitoring

The input references are monitored by two reference monitor schemes, independent for each reference. They indicate abnormal behavior of the reference signal, for example; drift from its nominal frequency or excessive jitter.

- Loss of Signal Monitor (LOS): LOS is an external signal, fed to one of ZL30152 GPIO pins. LOS is typically generated by a PHY device whose recovered clock is fed to one of ZL30152 reference inputs. PHY device will generate LOS signal when it cannot reliably extract the clock from the line. User can set one of GPIO pins as LOS input by programming corresponding GPIO register.

- **Coarse Frequency Monitor (CFM)**: This circuit monitors the reference over a short time interval. It detects large frequency irregularities (larger than 0.1%).

- **Single Cycle Monitor (SCM)**: This detector checks the period of a single clock cycle to detect large phase hits or the complete loss of the clock.

- **Guard Soak Timer (GST):** Timer associated with the CFM and SCM modules to disqualify the reference input signal (see Table 2)

- The monitor failure indicators are flagged in the status registers and have associated mask bits, as follows:

- Reference Fail Mask: Ref0FailMask<3:0>, Ref1FailMask<3:0>: these mask bits masks the failure indicator on corresponding fail pins/bits.

- Reference Switching Mask for the current active (locked to) reference: RefSwMask<3:0> these mask bits

masks the failure indicators that are used in the automatic reference switching state machine independently

for each supported DPLL.

- Holdover Mask for the current active (locked to) reference: HOMask<3:0>, these mask bits masks the failure indicators that are used to go into auto-holdover independently for each supported DPLL.

- MSB bit for GST and LSB bit for LOS

The single cycle and coarse monitor failure flags feed a timer (Guard Soak Timer) that disqualifies the reference input signal when the failures are present for more than the period of time defined in Table 2.

| Guard Soak Timer Control<br>bits in control register | Time to disqualify a reference | Notes         |

|------------------------------------------------------|--------------------------------|---------------|

| 00                                                   | minimum delay possible         |               |

| 01                                                   | 10 ms                          |               |

| 10                                                   | 50 ms                          | default value |

| 11                                                   | 2.5 s                          |               |

#### Table 2 - Guard Soak Time To Disqualify A Reference

The Guard Soak Timer that is used for the CFM and SCM modules has a built-in decay time hysteresis according to Table 3 (Timer to Qualify a reference) to prevent flickering of status bits at the threshold boundaries.

The Timer to Qualify a reference is a multiple of the Guard Soak Timer. Table 3 shows the multiplication factor to multiply the Guard Soak Timer to calculate the time to qualify a reference.

| Control bits to control the<br>Timer to qualify a<br>reference | Multiples of the Guard Soak Time to qualify a reference | Notes         |

|----------------------------------------------------------------|---------------------------------------------------------|---------------|

| 00                                                             | 2                                                       |               |

| 01                                                             | 4                                                       | Default value |

| 10                                                             | 16                                                      |               |

| 11                                                             | 32                                                      |               |

#### Table 3 - Guard Soak Time To Qualify A Reference

When a GPIO pin is used as a reference fail indicator, it indicates a valid reference if:

- The SCM does not detect phase hits, nor complete loss of clock or Ref<i>FailMask<1> is at logic "0"

- The CFM does not detect phase irregularity or Ref<i>FailMask<2> is at logic "0"

- The Guard Soak Time is triggered or Ref<i>FailMask<3> is at logic "0"

#### 4.2.1 DPLL General Characteristics

#### Pull-in Hold-in range

The DPLL supports pull-in/hold-in of +/-52 ppm, +/-130 ppm or +/-400 ppm or +/-3900 ppm.

#### DPLL bandwidth (jitter/wander transfer)

The DPLL supports the following first order filtering cut-off frequencies (14 Hz, 28 Hz, 56 Hz, 112 Hz, 224 Hz, 448 Hz and 896 Hz), DPLL bandwidth is determined during initialization. Dynamic change of DPLL bandwidth is supported. When changing the bandwidth dynamically, it is recommended to put DPLL to the Holdover mode first and then to change the bandwidth. After the bandwidth has been changed, the DPLL should be set to the Normal mode.

The DPLL locks to an input reference and provides stable low jitter output clock if the selected loop bandwidth is less than 1/30th the input reference frequency. As an example, a 19.44 MHz reference could deploy a bandwidth up to 896 Hz, and a 1 kHz input reference would deploy a loop bandwidth of 14 Hz. For 8 kHz reference we recommend a maximum loop bandwidth of 56 Hz.

#### Jitter/Wander Generation

Jitter generation performance (detailed in Table 9 -, "Jitter Generation Specifications - HPDIFF Outputs" and Table 10 -, "Jitter Generation Specifications - HPOUT Outputs").

Wander generation of this device is negligible.

#### Phase Transients

On reference switch with phase tracking active (i.e., TIE clear active or glitch-less reference switching), the DPLL transitions the phase of the output smoothly, limited by the selected loop bandwidth and by the selected phase slope limit.

The Microsemi device offers the following phase slope limiting options: 61 usec/sec, 7.5 usec/sec, 0.885 usec/sec or unlimited. If required phase slope limit is 0.885 usec/sec or 7.5 usec/sec, user should first set the device to unlimited phase slope and change it to required phase slope limit (0.885 usec/sec or 7.5 usec/sec) only after the device has achieved lock.

#### Holdover Stability

DPLL initial holdover accuracy is better than 50 ppb.

#### Input Tolerance Criteria

Input tolerance indicates that the device tolerates certain jitter, wander and phase transients at its input reference while maintaining outputs within an expected performance and without experiencing any alarms, reference switching or holdover conditions. Input tolerance is associated with input reference source characteristics and the standards associated with input reference type.

#### **DPLL Monitoring**

The DPLL provides lock and holdover indicators.

The lock time is dependent on employed loop bandwidth. The device has a lock time of less than 1 sec for all available DPLL loop bandwidth selections.

#### 4.2.2 DPLL States

The device DPLL supports three states: Free-run, Normal (Locked) and Holdover. The Holdover and Free-run states are used to cope with reference impairments.

Each of these modes have a corresponding state in the internal State Machine described as follows:

**Freerun State:** the Freerun state is entered when synchronization to the reference is not required or is not possible. Typically this occurs immediately following system power-up. In the Freerun State, the device provides timing and synchronization signals which are based on the master clock frequency (supplied to osci pin) only, and are not synchronized to the reference input signals. The freerun accuracy of the output clock is equal to the accuracy of the master clock (osci). So if a ±20 ppm freerun output clock is required, the master clock must also be ±20 ppm.

**Holdover State:** the Holdover State is typically entered when input reference is temporarily disrupted. In the Holdover State, the device provides output clocks which are not locked to an external reference signal, but are based on storage techniques. The storage value is determined while the device is in Normal Mode and locked to an external reference signal. Initial holdover accuracy is a function of DPLL while holdover drift is reliant on the drift of the master clock (osci).

**Normal State:** the Normal State is entered when a valid reference clock is available for synchronization. In the Normal State the device provides output clocks which are synchronized to one of the available 2 input references. From a reset condition - if a valid input reference is available - the device takes less than a second (lock time) to output signals which are synchronized (phase and frequency locked) to the reference input.

#### 4.2.3 DPLL Rate Conversion Function and FEC Support

The DPLL supports rate conversion with a 16 bit forward divider and a 16 bit feedback divider.

The DPLL provides up scaling and down scaling functions.

The DPLL has the ability to switch from normal rate (before FEC is negotiated) to FEC rate and vice versa.

The DPLL supports simple rate conversion (i.e., take in 19.44 MHz and create 255/238 FEC SONET clock of 666.51 MHz), and supports double rate conversion (i.e., take in 19.44 MHz, create FEC 10 GbE clock of 644.5313, which is 66/64 rate converted 625 MHz, or create 690.5692 which is 255/238X66/64 rate converted 625 MHz)

The following is just an example of the frequencies that can be supported (many more frequencies can be supported):

- GbE:

- 25 MHz

- 125 MHz

- XAUI (chip to chip interface, which is a common chassis to chassis interface):

- 156.25 MHz or x2 or x4 version

- OC-192/STM-64:

- 155.52 MHz or x2 or x4 version

- 155.52 MHz x 255/237 (standard EFEC for long reach) or x2 or x4 version

- 155.52 MHz x 255/238 (standard GFEC for long reach) or x2 or x4 version

- 10 GbE:

- 156.25 MHz which is 125 MHz x 10/8 or x2 or x4 version

- 155.52 MHz x 66/64 or x2 or x4 version

- Long reach 10GE might require the following frequencies with simple rate conversion: (156.25 MHz x 255/237) and (156.25 MHz x 255/238).

- The following frequencies with double rate conversion: (155.52 MHz x 66/64 x 255/237) or (155.52 MHz x 66/64 x 255/238) and (156.25 MHz x 66/64 x 255/238) or (156.25 MHz x 66/64 x 255/238). Also, user can use x2 or x4 version of the listed frequencies.

- Application Note ZLAN-267 explains how to generate the most common frequencies.

### 4.2.4 DPLL Input to Output And Output to Output Phase Alignment

#### **Techniques offered for Phase Alignment**

When the output clock is locked to a jitter free and wander free input clock, input to output latency is expected to have a typical error of 0 nsec.

The coarse and fine phase adjustments allow for input to output and output to output latency corrections to compensate for PCB load delay, as detailed in 4.6, "Output Drivers".

#### 4.3 Frequency Synthesis Engine

The device frequency synthesis engine is comprised of a hardware DCO and an analog jitter filtering APLL with built-in digital jitter attenuation scheme. The ultra low jitter frequency synthesis engine can generate output clocks which meet the jitter generation requirements detailed in Table 9 -, "Jitter Generation Specifications - HPDIFF Outputs" and Table 10 -, "Jitter Generation Specifications - HPOUT Outputs".

The frequency synthesis engine's APLL requires an external RC loop filter as described in section 4.13

The frequency synthesis engines can generate any clock which is (M/N X 1 kHz) multiple (FEC rate converted clock). The M and N are 16 bits wide.

When the DPLL is locked to an input reference, the DCO external control can be used. The DCO external control allows for the calibration of the DCO center frequency to adjust for external system oscillator center frequency.

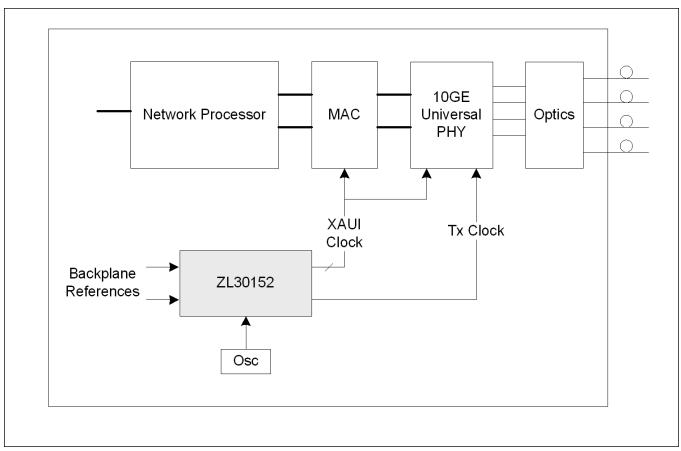

#### 4.4 Dividers and Skew Management

The device has 4 independent dividers associated with frequency synthesis engine.

The divider engines associated with the high performance differential outputs generate output clocks between 1 kHz and 750 MHz with 50% duty cycle. The other divider engines generate output clocks between 1 kHz and 177.5 MHz with 50% duty cycle.

The divider modules generating the single ended output clocks provides the ability to manage the phase skew of the output clock by a coarse step equal to the internal high speed clock period.

The single ended generated output clocks can be stopped either on rising or falling edge (programmed through serial interface or GPIO).

#### 4.5 Output Multiplexer

Figure 3 shows the multiplexing configuration that is supported.

The muxing configuration allows for the oscillator input or the xtal buffered input (osc\_clk) to be driven to one of the available programmable output drivers.

Figure 3 - Output Clocks Muxing Configuration

#### 4.6 Output Drivers

The device has 4 high performance (HP) differential (LVPECL) outputs.

The device has 2 high performance (HP) single ended (LVCMOS) outputs.

High Performance (HP) single ended driver (LVCMOS) supports the jitter specification detailed in Table 10 -, "Jitter Generation Specifications - HPOUT Outputs" and a maximum speed of 177.5 MHz.

The high performance (HP) differential driver (LVPECL) supports the jitter specification detailed in Table 9 -, "Jitter Generation Specifications - HPDIFF Outputs" and a maximum speed of 750 MHz.

HP differential LVPECL outputs should be terminated as shown in Figure 4. Terminating resistors provide 50  $\Omega$  equivalent Thevenin termination as well as biasing for the output LVPECL driver. Terminating resistors should be placed as close as possible to input pins of the LVPECL receiver. If the LVPECL receiver has internal biasing then AC coupling capacitors should be added.

#### Figure 4 - Terminating HP LVPECL Outputs

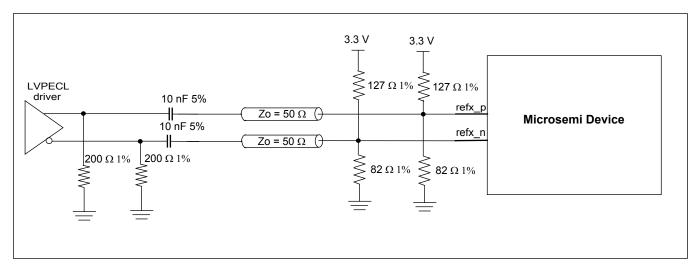

If the transmission line is required to be AC coupled then the termination shown in Figure 5 should be implemented. 200  $\Omega$  resistors are used to provide DC biasing for LVPECL driver. Both AC coupling capacitor and biasing resistors should be placed as close as possible to output pins.

Thevenin termination (127  $\Omega$  and 82  $\Omega$  resistors) provide 50  $\Omega$  termination as well as biasing of the input LVPECL receiver. If the LVPECL receiver has internal DC biasing then the line should be terminated with 100  $\Omega$  termination resistor between positive and negative input. In both cases termination resistors should be places as close as possible to the LVPECL receiver pins. Some LVPECL receivers have internal biasing and termination. In this case no external termination should be present.

Figure 5 - Terminating AC Coupled HP LVPECL Outputs

High performance LVCMOS outputs (hpoutclkx) should be terminated at the source with 22  $\Omega$  resistor as shown in Figure 6.

Figure 6 - Terminating HP LVCMOS Outputs

#### 4.7 Input Buffers

ZL30152 has two reference inputs ref[1:0]\_p/ref[1:0]\_n that can work as either single ended or differential. By default ref0 is differential and ref1 is single ended. This can be changed by programming ref\_config register at address 0x0A.

Input frequency range for differential inputs is: 1 kHz to 750 MHz; for single ended inputs is: 1 kHz to 177.5 MHz.

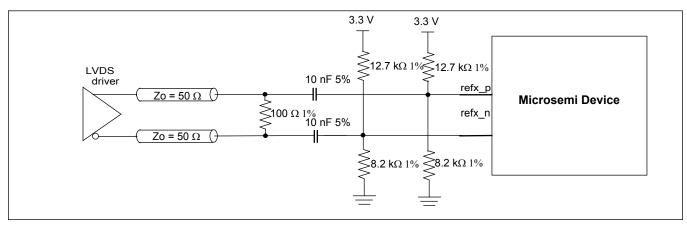

Differential reference inputs need to be properly terminated and biased as shown in Figure 7 and Figure 8 for LVPECL and Figure 9 and Figure 10 for LVDS drivers. When terminating LVPECL signal, it is necessary either to adjust termination resistors for DC coupling or to AC couple the LVPECL driver because ZL30152 differential inputs have different common mode (bias) voltage than LVPECL receivers. Thevenin termination (182  $\Omega$  and 68  $\Omega$  resistors) provide 50 ohm equivalent termination as well as biasing of the input buffer for DC coupled line. For AC coupled line, Thevenin termination with 127  $\Omega$  and 82  $\Omega$  resistors should be used as shown in Figure 8. The value of the AC coupling capacitors will depend on the minimum reference clock frequency. The value of 10 nF is good for input clock frequencies above 100 MHz. For lower clock frequencies capacitor values will have to be increased.

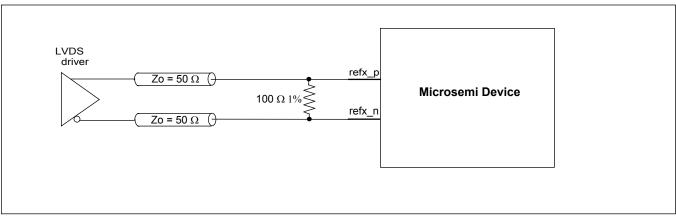

Terminations for DC and AC coupled LVDS line are shown in Figure 9 and Figure 10 respectively. Differential input biasing is provided by LVDS driver in case of DC coupling (Figure 9), whereas for AC coupling (Figure 10) biasing is generated by 12 k $\Omega$  and 8.2 k $\Omega$  resistors. In both cases, the line is terminated with 100  $\Omega$ .resistor.

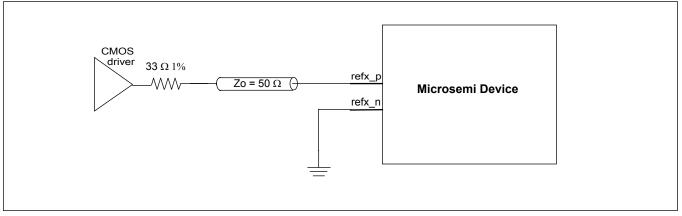

For single ended CMOS inputs, refx\_n input needs to be connected to the ground as shown in Figure 11. The value of series termination resistor will depend on CMOS output driver but the most common values are 33  $\Omega$  and 22  $\Omega$ .

Figure 7 - Differential DC Coupled LVPECL Termination

Figure 8 - Differential AC Coupled LVPECL Termination

Figure 9 - Differential DC Coupled LVDS Termination

Figure 10 - Differential AC Coupled LVDS Termination

Figure 11 - Single Ended CMOS Termination

#### 4.8 Master Clock Interface

The master oscillator determines the DPLL's free-run frequency accuracy and holdover stability. The reference monitor circuitry also uses this frequency as its point of reference (0 ppm) when making frequency measurements. The master clock interface was designed to accept either a free-running clock oscillator (XO) or a crystal (XTAL). Refer to Application Note ZLAN-68 for a list of recommended clock oscillators.

### 4.9 Clock Oscillator

When using a clock oscillator as the master timing source, connect the oscillator's output clock to the **osci** pin as shown in Figure 12. The connection to osci should be direct and not AC coupled. The **osco** pin must be left unconnected.

When using crystal resonator as the master timing source, connect crystal between **osci** and **osco** pins as shown in Figure 12. Crystal should have bias resistor of  $1 M\Omega$  and load capacitances C1 and C2. Value of load capacitances is dependent on crystal and should be as per crystal datasheet. Crystal should be a fundamental mode type -- not an overtone. See ZLAN-68 for crystal recommendation.

The device internal system clocks are generated off the device master clock input (Oscillator or a crystal employing an on-chip buffer/driver). The master clock selection is done at start-up using the available GPIO pins, right after pwr\_b get de-asserted. GPIO[0,1] pins need to be held high for 50 ms after the de-assertion of pwr\_b, after which time they can be released and used as any other GPIO. Alternatively, these pins can be pulled high with 1 K $\Omega$  resistors.

| GPIO [1:0] | Master Clock Frequency |

|------------|------------------------|

| 0          | reserved               |

| 1          | reserved               |

| 2          | reserved               |

| 3          | 24.576 MHz             |

**Table 4 - Master Clock Frequency Selection**

#### 4.10 Power Up/Down Sequence

The 3.3 V power rail should be powered before or simultaneously with the 1.8 V power rail to prevent the risk of latch-up (latch-up occur when the 1.8 V supply exceeds the 3.3 V rail by more than 1.8 V).

The power-down sequence is less critical, however it should be performed in the reverse order to reduce transient currents that consume power.

#### 4.11 Power Supply Filtering

Jitter levels on the output clocks may increase if the device is exposed to excessive noise on its power pins. For optimal jitter performance, the device should be isolated from noise on power planes connected to its 3.3 V and 1.8 V supply pins. For recommended common layout practices, refer to Application Note ZLAN-230.

#### 4.12 Reset and Configuration Circuit

To ensure proper operation, the device must be reset by holding the pwr\_b pin low for at least 2 ms after power-up when 3.3 V and 1.8 V supplies are stable. Following reset, the device will operate under specified default settings.

The reset pin can be controlled with on-board system reset circuitry or by using a stand-alone power-up reset circuit as shown in Figure 13. This circuit provides approximately 2 ms of reset low time. The pwr\_b input has Schmidt trigger properties to prevent level bouncing.

Figure 13 - Typical Power-Up Reset and Configuration Circuit

General purpose pins gpio[0,1,3,4,5] are used to configure device on the power up. They have to be pulled up/down with 1 K $\Omega$  resistors as shown in Figure 13 or they can be pulsed low/high during the pwr\_b low pulse and kept at the same level for at least 50 ms after pwr\_b goes high. After 50 ms they can be released and used as general purpose I/O.

By default all outputs are disabled to allow user first to program required frequencies for different outputs and then to enable corresponding outputs. During the prototype phase, hardware designer can verity if the device is working properly even before software driver is implemented just by pulling up gpio2 pin which enables hpdiff0 output (generates 622.08 MHz by default).

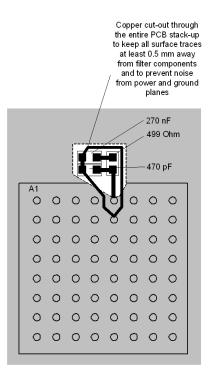

#### 4.13 Ultra Low Jitter Synthesizer Filter Components and Recommended Layout

The APLL for the ultra low jitter synthesizer in the Microsemi device uses external components to help optimize its loop bandwidth. For optimal jitter performance, the following component values are recommended:

Figure 14 - APLL Filter Component Values

Recommended layout for loop filters is shown in Figure 15:

## 5.0 Configuration and Control

The ZL30152 configuration is composed of 253 x 8 bits. The configuration registers are assigned their values by any of the following three methods:

- 1) Default configuration

- 2) Custom OTP (One Time Programmable) configuration

- 3) SPI/I2C configuration

The SPI/I2C host interface allows field programmability of the device configuration registers. As an example, user might start the device at nominal SONET rate, then switch to an FEC rate once the link FEC rate is negotiated.

#### 5.1 Custom OTP Configuration

At power-up the device sets its configuration registers to the user defined custom configuration values stored in it's OTP (One Time Programmable). Custom configurations can be generated using Microsemi's Clockcenter GUI software (ZLS30CLKCTR). For custom configured devices contact your local Microsemi Field Applications Engineer or Sales Manager.

#### 5.2 GPIO Configuration and Programmability

The device GPIO is mapped by the SPI/I2C programmability. The following is an example of control and status signals that can be supported:

- DPLL lock indicators

- DPLL holdover indicators

- Reference 0 and 1 fail indicators

- · Reference select control or monitor

- Differential output clock enable (per output or as a bank of 4 outputs)

- Host Interrupt Output: flags changes of device status prompting the processor to read the enabled interrupt service registers (ISR).

- Output clock stop/start