#### Is Now Part of

## ON Semiconductor®

To learn more about ON Semiconductor, please visit our website at <a href="https://www.onsemi.com">www.onsemi.com</a>

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA Class 3 medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, emplo

March 2012

### FSSD07

# 1-Bit / 4-Bit SD/SDIO and MMC Dual-Host Multiplexer

#### **Features**

■ On Resistance: 5Ω Typical, V<sub>DDC</sub>=2.7V

■ f<sub>toggle</sub>: >75MHz

■ Low On Capacitance: 6pF Typical

■ Low Power Consumption: 2µA Maximum

Supports Secure Digital (SD), Secure Digital I/O (SDIO), and Multimedia Card (MMC) Specifications

Supports 1-Bit / 4-Bit Host Controllers (V<sub>DDH1/H2</sub>=1.65V to 3.6V) Communicating with High-Voltage (2.7-3.6V) and Dual-Voltage Cards (1.65-1.95V, 2.7-3.6V)

- V<sub>DDC</sub>=1.65 to 3.6V, V<sub>DDH1/H2</sub>=1.65 to 3.6V

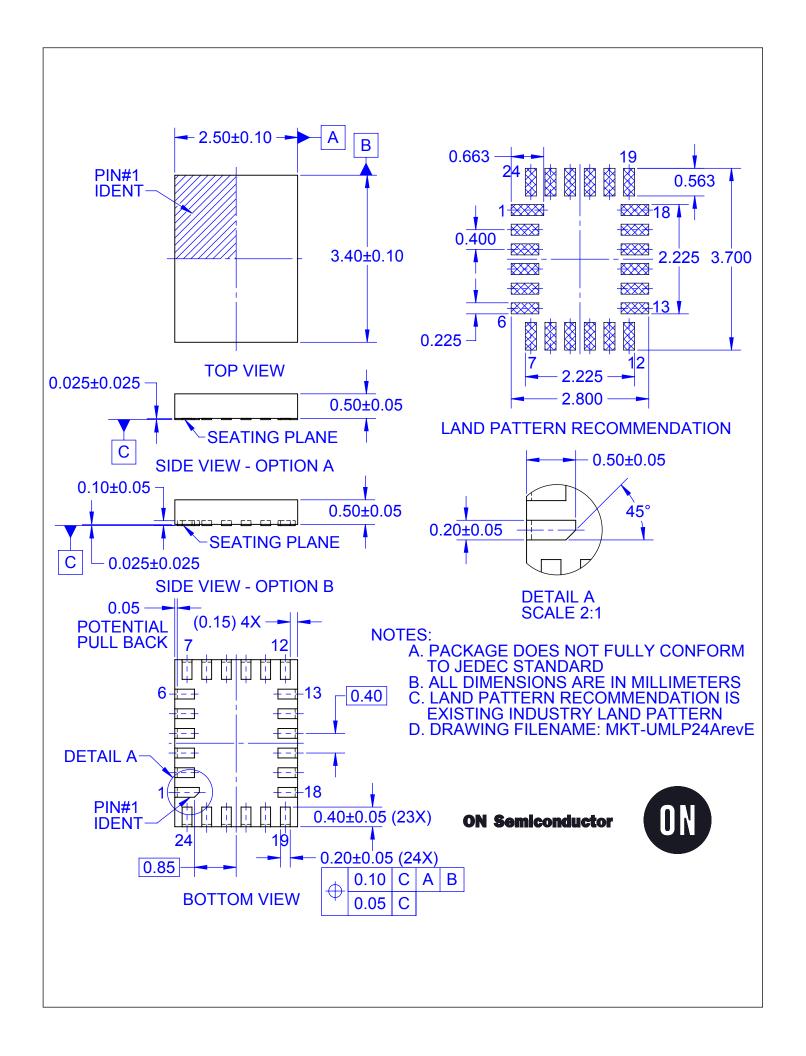

24-Lead MLP and UMLP Packages

### **Applications**

- Cell Phone, PDA, Digital Camera, Portable GPS, and Notebook Computer

- LCD Monitor, TV, and Set-Top Box

#### **Related Resources**

- FSSD07 Evaluation Board

- Evaluation Board Users Guide

- For samples, questions, or board requests; please contact analogswitch @fairchildsemi.com

### Description

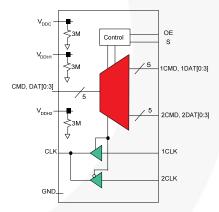

The FSSD07 is a 2:1 multiplexer that allows dual Secure Digital (SD), Secure Digital I/O (SDIO), and Multimedia Card (MMC) host controllers to share a common peripheral. The host controllers can be equal to, greater than, or less than peripheral card supply with minimal power consumption. This configuration enables dual host CMD, CLK, and D[3:0] signals to be multiplexed to a common peripheral.

The architecture includes the necessary bi-directional data and command transfer capability for single high-voltage cards or dual-voltage supply cards. The clock path is a uni-directional buffer.

Typical applications involve switching in portables and consumer applications: cell phones, digital cameras, home theater monitors, set-top boxes, and notebooks.

Figure 1. Analog Symbol Diagram

### **Ordering Information**

| Part<br>Number | Top<br>Mark | Operating<br>Temperature Range | Package Description                                              | Packing<br>Method |

|----------------|-------------|--------------------------------|------------------------------------------------------------------|-------------------|

| FSSD07BQX      | FSSD07      | -40°C to +85°C                 | 24-Lead Molded Leadless Package (MLP), JEDEC MO-220, 3.5 x 4.5mm | Tape &<br>Reel    |

| FSSD07UMX      | JK          | -40°C to +85°C                 | 24-Lead Ultra-thin Molded Leadless Package (UMLP), 0.4mm pitch   | Tape &<br>Reel    |

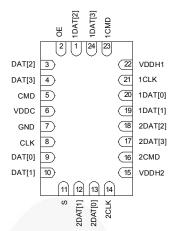

### **Pin Configuration**

Figure 3. UMLP Pin Assignments

### **Pin Definitions**

| Pin# MLP | Pin# UMLP | Name    | Description                              |

|----------|-----------|---------|------------------------------------------|

| 1        | 22        | 1DAT[2] | SDIO Common Port                         |

| 2        | 23        | OE      | Output Enable (Active HIGH)              |

| 3        | 24        | DAT[2]  |                                          |

| 4        | 1         | DAT[3]  | SDIO Common Port                         |

| 5        | 2         | CMD     |                                          |

| 6        | 3         | VDDC    | Power Supply (SDIO Peripheral Card Port) |

| 7        | 4         | GND     | Ground                                   |

| 8        | 5         | CLK     | Clock Path Port                          |

| 9        | 6         | DAT[0]  | SDIO Common Port                         |

| 10       | 7         | DAT[1]  | SDIO COMMON POR                          |

| 11       | 8         | S       | Select Pin                               |

| 12       | 9         | 2DAT[1] | Host Common Port                         |

| 13       | 10        | 2DAT[0] | Host Common Port                         |

| 14       | 11        | 2CLK    | Clock Path Port                          |

| 15       | 12        | VDDH2   | Power Supply (Host Port)                 |

| 16       | 13        | 2CMD    |                                          |

| 17       | 14        | 2DAT[3] |                                          |

| 18       | 15        | 2DAT[2] | Host Common Port                         |

| 19       | 16        | 1DAT[1] |                                          |

| 20       | 17        | 1DAT[0] |                                          |

| 21       | 18        | 1CLK    | Clock Path Port                          |

| 22       | 19        | VDDH1   | Power Supply (SDIO Host Port)            |

| 23       | 20        | 1CMD    | Host Common Port                         |

| 24       | 21        | 1DAT[3] | HOSE COMMON POR                          |

### **Truth Table**

| OE   | S    | Function                                                             |

|------|------|----------------------------------------------------------------------|

| HIGH | LOW  | 1CMD, 1CLK, 1DAT[3:0] connected to CMD, CLK, DAT[3:0]                |

| HIGH | HIGH | 2CMD, 2CLK,2DAT[3:0] connected to CMD, CLK, DAT[3:0]                 |

| LOW  | Х    | CMD, DAT[3:0] ports high impedance; CLK is function of selected nCLK |

#### **Typical Application VDDC** VDDH1 FSSD07 1.65V to 3.6V 1.65V to 3.6V $R_{CMD}$ , $R_{DAT[3:0]}$ CMD, DAT[3:0] 1CMD, 1DAT[3:0] WiFi, Bluetooth, Processor #1 MMC or SD Peripheral 1CLK CLK Secure Data/ VDDH2 Multi Media Card **Dual Host Selector** 1.65V to 3.6V SD Card $R_{1CMD, 2CMD} = 10k \text{ to } 100k \text{ ohm}$ $R_{1DAT[3:0]}$ , $_{2DAT[3:0]}$ = 10k to 100k ohm 2CMD, 2DAT[3:0] MMC Card $R_{1CMD, 2CMD} = 4.7k$ to 100k ohm $R_{1DAT[3:0], 2DAT[3:0]} = 50k$ to 100k ohm Processor #2 2CLK OE GND -

Figure 4. Typical Application Diagram

### **Functional Description**

The FSSD07 enables the multiplexing of dual ASIC / baseband processor hosts to a common peripheral card or module, providing bi-directional support of the dualvoltage SD/SDIO or MMC cards available in the marketplace. Each host SDIO port has its own supply rail, such that hosts with different supplies can be interfaced to a common peripheral module or card. The peripheral card supply must be equal to or greater than the host(s) to minimize power consumption. The independent  $V_{DDC}$ ,  $V_{DDH1}$ , and  $V_{DDH2}$  are defined by the supplies connected from the application Power Management ICs (PMICs) to the FSSD07. The clock path is a uni-directional buffered path rather than a bidirectional switch port. The supplies (V<sub>DDC</sub>, V<sub>DDH1</sub>, and V<sub>DDH2</sub>) have an internal termination resistor (typically  $3M\Omega$ ) to ensure the supply rails internally do not float if the application turns off one or all of these sources.

#### CMD, DAT Bus Pull-ups

The CMD and DAT[3:0] ports do not have, internally, the system pull-up resistors as defined in the MMC or SD card system bus specifications. The system bus pull-up must be added external to the FSSD07. The value, within the specific specification limits, is a function of the individual application and type of card or peripheral connected. For SD card applications, the  $R_{\text{CMD}}$  and  $R_{\text{DAT}}$  pull-ups should be between  $10k\Omega$  and  $100k\Omega$ . For MMC applications, the  $R_{\text{CMD}}$  pull-ups should be between  $4.7k\Omega$  and  $100k\Omega$ , and the  $R_{\text{DAT}}$  pull-ups between  $50k\Omega$  and  $100k\Omega$ . The card-side CMD and DAT[3:0] outputs have a circuit that facilitates incident wave switching, so the external pull-up resistors ensure retention of the output high level.

The OE pin can be used to place the CMD and DAT[3:0] into high-impedance mode during power-up sequencing or when the system enters IDLE state (see IDLE State CMD/DAT Bus "Parking").

#### **CLK Bus**

The 1CLK and 2CLK inputs are bi-state buffer architectures, rather than a switch I/O, to ensure 52MHz incident wave switching. Since most host controllers also have a clock enable register bit to enable or disable the system clock when in IDLE mode, the CLK output is not disabled by the OE pin. Instead, the CLK output is a function of whichever host controller clock is selected by the S pin.

Consequently, there is always a clock path connected between the selected host and the card. The state of the CLK pin is a function of the selected host controller nCLK output pin, which facilitates retaining clock duty cycle in the system or performing read / wait operations.

# IDLE State & Power-Up CMD/DAT Bus "Parking"

The SD and MMC card specifications were written for a direct point-to-point communication between host controller and card. The introduction of the FSSD07 in that path, as an expander, requires that the functional operation and system latency not be impacted by the switch characteristics. Since there are various card formats, protocols, and configurable controllers, an OE pin is available to facilitate a fast IDLE transition for the CMD/DAT[3:0] outputs. Some controllers, rather than placing CMD/DAT into high-impedance mode, pull the outputs HIGH for a clock cycle prior to going into high-impedance mode (referred to as "parking" the output). Some legacy controllers pull their outputs HIGH versus high impedance.

If the OE pin is pulled HIGH and the controller places its command and data outputs into high-impedance (driving nCMD/nDAT[3:0]), the FSSD07 CMD/DAT[3:0] output rise time is a function of the RC time constant through the switch path. Pulling OE LOW puts the switches into high impedance, disabling communication from the host to card, and the CMD/DAT[3:0] outputs are pulled HIGH by the system pull-up resistors chosen for the application. This mechanism facilitates power-up sequencing by holding OE LOW until supplies are stable and communication between the host(s) and card is enabled.

#### **Power Optimization**

Since the FSSD07 has multiple supplies ( $V_{DDC}$ ,  $V_{DDH1}$ , and  $V_{DDH2}$ ), the control signals have been referenced to the card peripheral side ( $V_{DDC}$ ). To minimize power consumption, current paths between supplies are isolated when one or more supplies are not present. This includes the configuration of the removal of  $V_{DDC}$  with host controller supplies remaining present.

### **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol                       | Parameter                               | Conditions                                      | Min. | Max.                                                     | Unit |

|------------------------------|-----------------------------------------|-------------------------------------------------|------|----------------------------------------------------------|------|

| $V_{DDC}$                    | Card Supply Voltage                     |                                                 | -0.5 | 4.6                                                      | V    |

| $V_{\rm DDH1}, V_{\rm DDH2}$ | Host Controller Supply Voltage          |                                                 | -0.5 | 4.6                                                      | V    |

| V                            | Switch I/O Voltage <sup>(1)</sup>       | 1DAT[3:0], 2DAT[3:0],<br>1CMD, 2CMD Pins        | -0.5 | V <sub>DDx</sub> <sup>(2)</sup> + 0.3V<br>(4.6V maximum) | V    |

| V <sub>SW</sub>              | Switch I/O Voltage                      | DAT[3:0], CMD Pins                              | -0.5 | V <sub>DDx</sub> <sup>(2)</sup> + 0.3V<br>(4.6V maximum) | V    |

| V <sub>CNTRL</sub>           | Control Input Voltage <sup>(1)</sup>    | S, OE                                           | -0.5 | 4.6                                                      | V    |

| V <sub>CLKI</sub>            | CLK Input Voltage (1)                   | 1CLK, 2CLK                                      | -0.5 | 4.6                                                      | V    |

| V <sub>CLKO</sub>            | CLK Output Voltage <sup>(1)</sup>       | CLK                                             | -0.5 | V <sub>DDx</sub> <sup>(2)</sup> + 0.3V<br>(4.6V maximum) | V    |

| I <sub>INDC</sub>            | Input Clamp Diode Current               |                                                 |      | -50                                                      | mA   |

| I <sub>SW</sub>              | Switch I/O Current                      | SDIO Continuous                                 |      | 50                                                       | mA   |

| I <sub>SWPEAK</sub>          | Peak Switch Current                     | SDIO Pulsed at 1ms<br>Duration, <10% Duty Cycle |      | 100                                                      | mA   |

| T <sub>STG</sub>             | Storage Temperature Range               |                                                 | -65  | +150                                                     | °C   |

| TJ                           | Maximum Junction Temperature            |                                                 |      | +150                                                     | °C   |

| T <sub>L</sub>               | Lead Temperature                        | Soldering, 10 Seconds                           |      | +260                                                     | °C   |

|                              |                                         | I/O to GND                                      |      | 8                                                        |      |

| 505                          | Human Body Model,<br>JEDEC: JESD22-A114 | Supply to GND                                   |      | 10                                                       | kV   |

| ESD                          | OLDES. SEODEE ATTI                      | All Other Pins                                  |      | 5                                                        |      |

|                              | Charged Device Model, JEDEC-JE          | SD-C101                                         |      | 2                                                        |      |

#### Notes:

- 1. The input and output negative ratings may be exceeded if the input and output diode current ratings are observed.

- 2.  $V_{DDx}$  references the specific SDIO port  $V_{DD}$  rail (i.e.  $V_{DDH1}$ ,  $V_{DDH2}$ ,  $V_{DDC}$ ).

### **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to Absolute Maximum Ratings.

| Symbol              | Parame                                                   | Min.            | Max.                 | Unit       |      |

|---------------------|----------------------------------------------------------|-----------------|----------------------|------------|------|

| $V_{DDC}$           | Supply Voltage - Card Side                               | 1.65            | 3.60                 | V          |      |

| $V_{DDH1,}V_{DDH2}$ | Supply Voltage - Dual Host Contro                        | 1.65            | 3.60                 | V          |      |

| $V_{CNTRL}$         | Control Input Voltage - V <sub>S</sub> , V <sub>OE</sub> | 0               | $V_{DDC}$            | V          |      |

| $V_{CLKI}$          | Clock Input Voltage - V <sub>CLKI</sub>                  | 0               | V <sub>DDH1/H2</sub> | V          |      |

|                     |                                                          | CMD, DAT[3:0]   | 0                    | $V_{DDC}$  | V    |

| $V_{\sf SW}$        | Switch I/O Voltage                                       | 1CMD, 1DAT[3:0] | 0                    | $V_{DDH1}$ |      |

|                     |                                                          | 2CMD, 2DAT[3:0] | 0                    | $V_{DDH2}$ | V    |

| T <sub>A</sub>      | Operating Temperature                                    | -40             | +85                  | °C         |      |

| $\theta_{JA}$       | Thermal Resistance, Free Air                             | MLP Package     |                      | +50        | °C/W |

### DC Electrical Characteristics at 1.8V $V_{\text{DDC}}$

All typical values are for  $V_{DDC}$ =1.8V at 25°C unless otherwise specified.

| Cumahad                   | Doromatar                                                    | V <sub>DDC</sub> | V <sub>DDH1</sub> /   | Canditions                                                                                                                                         | T <sub>A</sub> =- | 40 to + | 85°C | I Im!4 |

|---------------------------|--------------------------------------------------------------|------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|---------|------|--------|

| Symbol                    | Parameter                                                    | (V)              | V <sub>DDH2</sub> (V) | Conditions                                                                                                                                         | Min.              | Тур.    | Max. | Unit   |

| Common Pi                 | ns                                                           |                  |                       |                                                                                                                                                    |                   |         |      |        |

| $V_{IK}$                  | Clamp Diode Voltage                                          | 1.80             | 1.80                  | I <sub>IK</sub> =-18mA                                                                                                                             |                   |         | -1.2 | V      |

| V <sub>IH</sub>           | Control Input Voltage<br>High                                | 1.80             | 1.80                  |                                                                                                                                                    | 1.3               |         |      | ٧      |

| V <sub>IL</sub>           | Control Input Voltage<br>Low                                 | 1.80             | 1.80                  |                                                                                                                                                    |                   |         | 0.5  | ٧      |

| I <sub>IN</sub>           | S, OE Input High<br>Current                                  | 1.95             | 1.95                  | V <sub>CNTRL</sub> =0V to V <sub>DDC</sub>                                                                                                         | -1                |         | 1    | μA     |

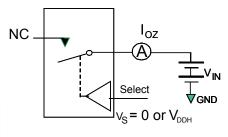

| l <sub>oz</sub>           | Off Leakage, Current of all ports                            | 1.95             | 1.95                  | V <sub>SW</sub> =0V to V <sub>DDC</sub>                                                                                                            | -1.0              | 0.5     | 1.0  | μA     |

| V <sub>OHC</sub>          | CLK Output Voltage<br>High <sup>(3)</sup>                    | 1.95             | 1.95                  | I <sub>OH</sub> =-2mA                                                                                                                              | 1.6               |         |      | ٧      |

| V <sub>oLC</sub>          | CLK Output Voltage<br>Low <sup>(3)</sup>                     | 1.65             | 1.65                  | I <sub>OL</sub> =-2mA                                                                                                                              |                   |         | 90   | mV     |

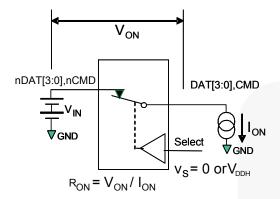

| R <sub>ON</sub>           | Switch On Resistance <sup>(4)</sup>                          | 1.65             | 1.65                  | V <sub>CMD, DAT[3:0]</sub> =0V,<br>I <sub>ON</sub> =-2mA<br>Figure 5                                                                               |                   |         | 10   | Ω      |

| $\Delta R_{ON}$           | Delta On Resistance <sup>(3, 5)</sup>                        | 1.65             | 1.65                  | V <sub>CMD, DAT[3:0]</sub> =0V,<br>I <sub>ON</sub> =- 2mA                                                                                          |                   | 0.85    |      | Ω      |

| Power Supp                | ly                                                           |                  |                       |                                                                                                                                                    |                   |         |      |        |

| I <sub>CC(VDDC)</sub>     | Quiescent Supply<br>Current (Card)                           | 1.95             | 0                     | V <sub>SW</sub> =0 or V <sub>DDC</sub> , I <sub>OUT</sub> =0                                                                                       |                   |         | 2    | μA     |

| I <sub>CC(VDDH1/H2)</sub> | Quiescent Supply<br>Current (Hosts)                          | 1.95             | 1.95                  | $\begin{array}{c} V_{SW} {=} 0 \text{ or } V_{DDX,} \ I_{OUT} {=} 0, \\ V_{CLKI} {=} V_{DDHX,} \\ V_{CLKO} {=} Open, \ OE {=} V_{DDC} \end{array}$ |                   |         | 2    | μA     |

| $\Delta I_{HOST}$         | Delta I <sub>CC(VDDH1, VDDH2)</sub> for One Host Powered Off | 1.95             | 1.95 / 0<br>0 / 1.95  | $V_{SW}$ =0 or $V_{DDX}$ , $I_{OUT}$ =0, $V_{CLKI}$ = $V_{DDHX}$ , $V_{CLKO}$ =Open, OE= $V_{DDC}$                                                 |                   |         | 2    | μA     |

#### Notes:

- 3. Guaranteed by characterization, not production tested.

- 4. On resistance is determined by the voltage drop between the switch I/O pins at the indicated current through the switch.

- 5.  $\Delta$  R<sub>ON</sub>=R<sub>ON max</sub> R<sub>ON min</sub> measured at identical V<sub>CC</sub>, temperature, and voltage.

### DC Electrical Characteristics at 2.7V $V_{\text{DDC}}$

All typical values are for  $V_{DDC}$ =2.7V at 25°C unless otherwise specified.

| 0                             | D                                                            | V 00 | V <sub>DDH1</sub> / | 0                                                                                                     | T <sub>A</sub> = | -40 to +8 | 5°C  | 11 |

|-------------------------------|--------------------------------------------------------------|------|---------------------|-------------------------------------------------------------------------------------------------------|------------------|-----------|------|----|

| Symbol                        | Parameter $V_{DDC}(V) V_{DDH2}(V)$ Conditions                |      | Conditions          | Min.                                                                                                  | Тур.             | Max.      | Unit |    |

| Common                        | Pins                                                         |      |                     |                                                                                                       |                  |           |      |    |

| V <sub>IK</sub>               | Clamp Diode Voltage                                          | 2.7  | 2.7                 | I <sub>IK</sub> =-18mA                                                                                |                  |           | -1.2 |    |

| V <sub>IH</sub>               | Control Input Voltage<br>High                                | 2.7  | 2.7                 |                                                                                                       | 1.8              |           |      | V  |

| V <sub>IL</sub>               | Control Input Voltage<br>Low                                 | 2.7  | 2.7                 |                                                                                                       |                  |           | 0.8  |    |

| I <sub>IN</sub>               | S, OE Input High Current                                     | 3.6  | 3.6                 | V <sub>CNTRL</sub> =0V to V <sub>DDC</sub>                                                            | -1               |           | 1    | μA |

| l <sub>oz</sub>               | Off Leakage Current of all Ports                             | 3.6  | 3.6                 | V <sub>SW</sub> =0V to V <sub>DDC</sub>                                                               | -1.0             | 0.5       | 1.0  | μΑ |

| V <sub>OHC</sub>              | CLK Output Voltage<br>High <sup>(6)</sup>                    | 2.7  | 2.7                 | I <sub>OH</sub> =-2mA                                                                                 | 2.4              |           |      | ٧  |

| V <sub>OLC</sub>              | CLK Output Voltage<br>Low <sup>(6)</sup>                     | 3.6  | 3.6                 | I <sub>OL</sub> =-2mA                                                                                 |                  |           | 90   | mV |

| R <sub>ON</sub>               | Switch On Resistance <sup>(7)</sup>                          | 2.7  | 2.7                 | V <sub>CMD, DAT[3:0]</sub> =0V,<br>I <sub>ON</sub> =-2mA<br>Figure 5                                  |                  | 5.0       | 8.0  | Ω  |

| $\Delta R_{ON}$               | Delta On Resistance <sup>(6, 8)</sup>                        | 2.7  | 2.7                 | V <sub>CMD, DAT[3:0]</sub> =0V,<br>I <sub>ON</sub> =- 2mA                                             |                  | 0.8       |      | Ω  |

| Power Su                      | ıpply                                                        |      |                     |                                                                                                       |                  |           |      |    |

| I <sub>CC(VDDC)</sub>         | Quiescent Supply Current (Card)                              | 3.6  | 0                   | V <sub>SW</sub> =0 or V <sub>DDC</sub> , I <sub>OUT</sub> =0                                          |                  |           | 2    | μA |

| I <sub>CC</sub><br>(VDDH1/C2) | Quiescent Supply Current (Hosts)                             | 3.6  | 3.6                 | $V_{SW}$ =0 or $V_{DDx}$ , $I_{OUT}$ =0, $V_{CLKI}$ = $V_{DDHx}$ , $V_{CLKO}$ =Open, $OE$ = $V_{DDC}$ |                  |           | 2    | μA |

| $\Delta I_{HOST}$             | Delta I <sub>CC(VDDH1, VDDH2)</sub> for One Card Powered Off | 3.6  | 3.6 / 0<br>0 / 3.6  | $V_{SW}$ =0 or $V_{DDx}$ , $I_{OUT}$ =0, $V_{CLKI}$ = $V_{DDHx}$ , $V_{CLKO}$ =Open, $OE$ = $V_{DDC}$ |                  |           | 2    | μA |

#### Notes:

- 6. Guaranteed by characterization, not production tested.

- On resistance is determined by the voltage drop between the switch I/O pins at the indicated current through the switch.

- 8.  $\Delta$  R<sub>ON</sub>=R<sub>ON max</sub> R<sub>ON min</sub> measured at identical V<sub>CC</sub>, temperature, and voltage.

### AC Electrical Characteristics at 1.8V $V_{\text{DDC}}$

All typical values are for  $V_{DDC}$ =1.8V at 25°C unless otherwise specified.

| Comple ed                    | Danamatan                                     | V 00                 | V <sub>DDH1</sub> /   | Conditions                                                           | T <sub>A</sub> =-4 | 10 to + | 85°C | Unit |

|------------------------------|-----------------------------------------------|----------------------|-----------------------|----------------------------------------------------------------------|--------------------|---------|------|------|

| Symbol                       | Parameter                                     | V <sub>DDC</sub> (V) | V <sub>DDH2</sub> (V) | Conditions                                                           | Min.               | Тур.    | Max. | Unit |

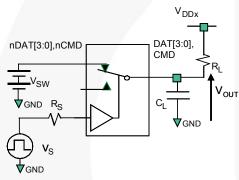

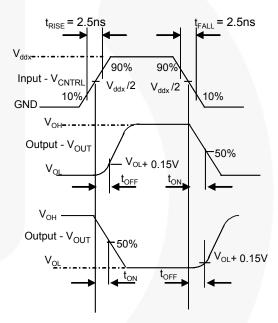

| t <sub>ON</sub>              | Turn-On Time,<br>S, OE to CMD, DAT[3:0]       | 1.65 to 1.95         | 1.65 to 3.6           | $V_{SW}$ =0V, $R_L$ =1k $\Omega$ , $C_L$ =20pF<br>Figure 7, Figure 8 |                    | 8       | 18   | ns   |

| t <sub>OFF</sub>             | Turn-Off Time,<br>S, OE to CMD, DAT[3:0]      | 1.65 to 1.95         | 1.65 to 3.6           | $V_{SW}$ =0V, $R_L$ =1k $\Omega$ , $C_L$ =20pF<br>Figure 7, Figure 8 |                    | 6       | 13   | ns   |

| t <sub>RISE1/</sub><br>FALL1 | CMD/DAT Output Edge Rates <sup>(9)</sup>      | 1.65 to 1.95         | 1.65 to 3.6           | $R_L$ =1k $\Omega$ , $C_L$ =20pF<br>(10-90%)<br>Figure 7, Figure 8   |                    | 3       |      | ns   |

| t <sub>PD</sub>              | Switch Propagation Delay <sup>(9)</sup>       | 1.65 to 1.95         | 1.65 to 3.6           | $R_L$ =1k $\Omega$ , $C_L$ =20pF<br>Figure 7, Figure 89              |                    | 4.5     | 9    | ns   |

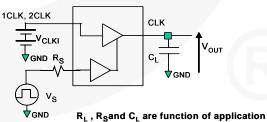

| t <sub>pLH</sub>             | LH Propagation Delay 1CLK, 2CLK to CLK        | 1.65 to 1.95         | 1.65 to 3.6           | C <sub>L</sub> =20pF<br>Figure 10, Figure<br>11                      |                    | 4       | 6    | ns   |

| t <sub>pHL</sub>             | HL Propagation Delay 1CLK, 2CLK to CLK        | 1.65 to 1.95         | 1.65 to 3.6           | C <sub>L</sub> =20pF<br>Figure 10, Figure<br>11                      |                    | 4       | 6    | ns   |

| t <sub>RISE2/</sub><br>FALL2 | CLK Output Edge Rates <sup>(9)</sup>          | 1.65 to 1.95         | 1.65 to 3.6           | C <sub>L</sub> =20pF (10-90%)<br>Figure 7, Figure 8                  |                    | 3       |      | ns   |

| O <sub>IRR</sub>             | Off Isolation <sup>(9)</sup>                  | 1.8                  | 1.65 to 3.6           | f=10MHz, $R_T$ =50 $\Omega$ , $C_L$ =20pF, Figure 12                 |                    | -60     |      | dB   |

| Xtalk                        | Non-Adjacent Channel Crosstalk <sup>(9)</sup> | 1.8                  | 1.65 to 3.6           | f=10MHz, $R_T$ =50 $\Omega$ , $C_L$ =20pF, Figure 13                 |                    | -60     |      | dB   |

| f <sub>toggle</sub>          | Clock Frequency <sup>(9)</sup>                | 1.8                  | 1.65 to 3.6           | C <sub>L</sub> =20pF                                                 |                    | 75      |      | MHz  |

#### Note:

9. Guaranteed by characterization, not production tested.

### AC Electrical Characteristics at 3.3V $V_{\text{DDC}}$

All typical values are for  $V_{DDC}$ =3.3V at 25°C unless otherwise specified.

| Council of                   | Donomotor                                         | V 00                 | V <sub>DDH1</sub> / V <sub>DDH2</sub> | Conditions                                                           | T <sub>A</sub> =- | 40 to + | 85°C | I Im!4 |

|------------------------------|---------------------------------------------------|----------------------|---------------------------------------|----------------------------------------------------------------------|-------------------|---------|------|--------|

| Symbol                       | Parameter                                         | V <sub>DDC</sub> (V) | (V)                                   | Conditions                                                           | Min.              | Тур.    | Max. | Unit   |

| t <sub>ON</sub>              | Turn-On Time,<br>S, OE to CMD, DAT[3:0]           | 2.7 to 3.6           | 1.65 to 3.6                           | $V_{SW}$ =0V, $R_L$ =1k $\Omega$ , $C_L$ =20pF Figure 7, Figure 8    |                   | 8       | 18   | ns     |

| t <sub>OFF</sub>             | Turn-Off Time,<br>S, OE to CMD, DAT[3:0]          | 2.7 to 3.6           | 1.65 to 3.6                           | $V_{SW}$ =0V, $R_L$ =1k $\Omega$ , $C_L$ =20pF<br>Figure 7, Figure 8 |                   | 6       | 13   | ns     |

| t <sub>RISE1/</sub><br>FALL1 | CMD/DAT Output Edge<br>Rates <sup>(10)</sup>      | 2.7 to 3.6           | 1.65 to 3.6                           | $R_L$ =1k $\Omega$ , $C_L$ =20pF (10-<br>90%)<br>Figure 7, Figure 8  |                   | 3       |      | ns     |

| t <sub>PD</sub>              | Switch Propagation<br>Delay <sup>(10)</sup>       | 2.7 to 3.6           | 1.65 to 3.6                           | $R_L$ =1k $\Omega$ , $C_L$ =20pF<br>Figure 7, Figure 8               |                   | 2.5     | 6    | ns     |

| t <sub>pLH</sub>             | LH Propagation Delay 1CLK, 2CLK to CLK            | 2.7 to 3.6           | 1.65 to 3.6                           | C <sub>L</sub> =20pF<br>Figure 10, Figure 11                         |                   | 4       | 6    | ns     |

| t <sub>pHL</sub>             | HL Propagation Delay 1CLK, 2CLK to CLK            | 2.7 to 3.6           | 1.65 to 3.6                           | C <sub>L</sub> =20pF<br>Figure 10, Figure 11                         |                   | 4       | 6    | ns     |

| t <sub>RISE2/</sub><br>FALL2 | CLK Output Edge<br>Rates <sup>(10)</sup>          | 2.7 to 3.6           | 1.65 to 3.6                           | C <sub>L</sub> =20pF (10-90%)<br>Figure 7, Figure 8                  |                   | 3       |      | ns     |

| O <sub>IRR</sub>             | Off Isolation <sup>(10)</sup>                     | 2.7                  | 1.65 to 3.6                           | f=10MHz, $R_T$ =50Ω, $C_L$ =20pF<br>Figure 12                        |                   | -60     |      | dB     |

| Xtalk                        | Non-Adjacent Channel<br>Crosstalk <sup>(10)</sup> | 2.7                  | 1.65 to 3.6                           | f=10MHz, $R_T$ =50 $\Omega$ , $C_L$ =20pF, Figure 13                 |                   | -60     |      | dB     |

| f <sub>toggle</sub>          | Clock Frequency <sup>(10)</sup>                   | 2.7                  | 1.65 to 3.6                           | C <sub>L</sub> =20pF                                                 |                   | 75      |      | MHz    |

#### Note:

10. Guaranteed by characterization, not production tested.

### Capacitance

| Cumbal                 | Doromotor                                                                      | V <sub>DDC</sub> | V <sub>DDH1/H2</sub> | Conditions                                                                       | T <sub>A</sub> =-4 | 0 to + | 85°C | l lmi4 |

|------------------------|--------------------------------------------------------------------------------|------------------|----------------------|----------------------------------------------------------------------------------|--------------------|--------|------|--------|

| Symbol                 | Parameter                                                                      | (V)              | (V)                  | Conditions                                                                       | Min.               | Тур.   | Max. | Unit   |

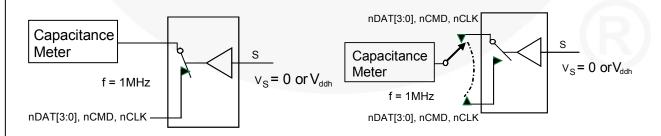

| C <sub>IN(S, OE,</sub> | Control and nCLK Pin Input Capacitance <sup>(11)</sup>                         | 0                | 2.7                  | V <sub>DDC</sub> =0V                                                             |                    | 2.5    |      | pF     |

| C <sub>ON</sub>        | Common Port On<br>Capacitance <sup>(11)</sup><br>(C <sub>DAT[3:0], CMD</sub> ) | 2.7              | 2.7                  | V <sub>OE</sub> =V <sub>DDC</sub> , V <sub>bias</sub> =0.5V, f=1MHz<br>Figure 14 |                    | 7.5    |      | pF     |

| C <sub>OFF</sub>       | Input Source Off<br>Capacitance <sup>(11)</sup>                                | 2.7              | 2.7                  | V <sub>OE</sub> =0V, V <sub>bias</sub> =0.5V, f=1MHz<br>Figure 15                |                    | 4      |      | pF     |

#### Note:

11. Guaranteed by characterization, not production tested.

### **Test Diagrams**

Figure 5. On Resistance

$R_L$ ,  $R_S$ , and  $C_L$  are functions of the application environment (see AC tables for specific values).  $C_L$  includes test fixture and stray capacitance.

Figure 7. AC Test Circuit Load

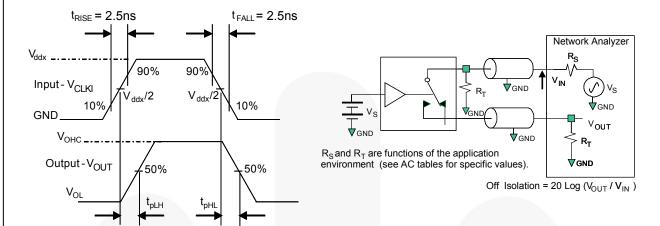

Figure 9. Switch Propagation Delay (tPD) Waveform

Each switch port tested separately.

Figure 6. Off Leakage

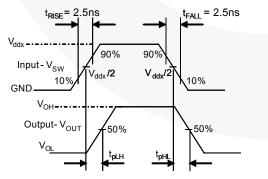

Figure 8. Turn On/Off Time Waveforms

R<sub>L</sub> , R<sub>S</sub>and C<sub>L</sub> are function of application environment (see AC Tables for specific values)

C<sub>L</sub> includes test fixture and stray capacitance

Figure 10. AC Test Circuit Load (CLK)

### Test Diagrams (Continued)

Figure 11. CLK Propagation Delay Waveforms

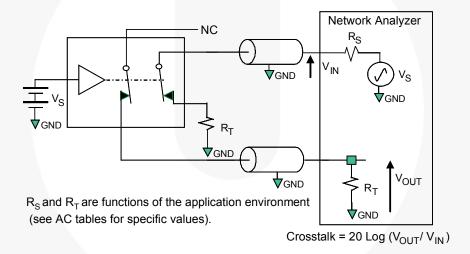

Figure 12. Channel Off Isolation

Figure 13. Channel-to-Channel Crosstalk

Figure 14. Channel On Capacitance

Figure 15. Channel Off Capacitance

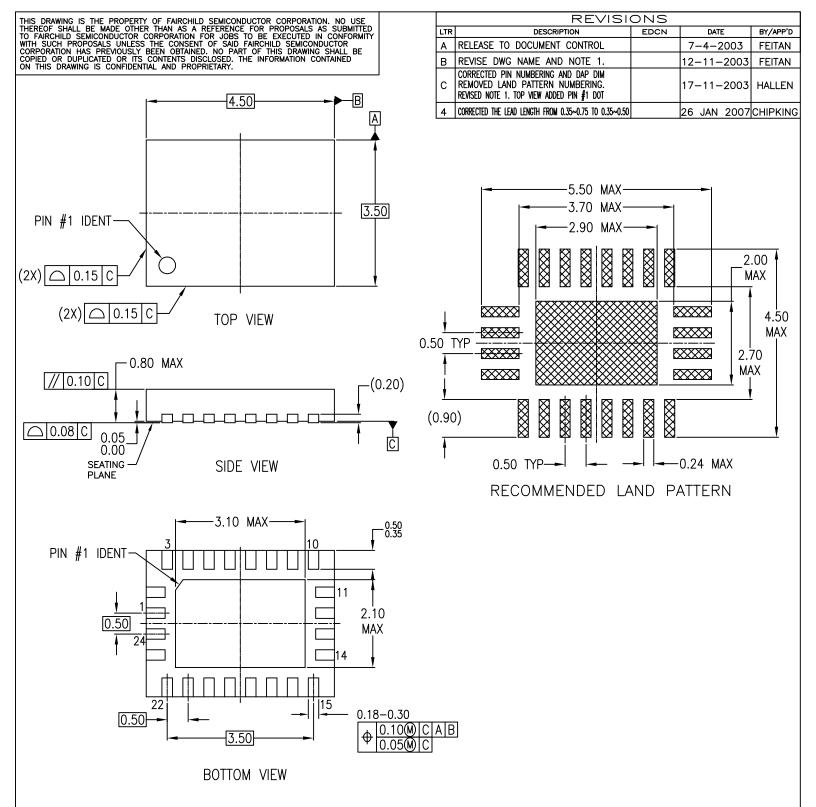

### NOTES:

- A. CONFORMS TO JEDEC REGISTRATION MO-220, VARIATION WFSD-2 FOR DIMENSIONS ONLY. PIN NUMBERING DOES NOT COMPLY.

- B. DIMENSIONS ARE IN MILLIMETERS.

- C. DIMENSIONS AND TOLERANCES PER ASME Y14.5M, 1994

| VILPZ4Brev4 | 24Brev4 |

|-------------|---------|

|-------------|---------|

| APF     | PROVALS      | DATE      | EALD                   |                                                                     |                |            |     |  |  |  |

|---------|--------------|-----------|------------------------|---------------------------------------------------------------------|----------------|------------|-----|--|--|--|

| DRAWN   | FEITAN       | 31-3-2003 | SEMICO                 | FAIRCHILD Bayan Lepas, FIZ, SEMICONDUCTOR: 11900, Penang, Malaysia. |                |            |     |  |  |  |

| DFTG. C | HK.          |           |                        |                                                                     |                |            |     |  |  |  |

|         |              |           | _ ^ 4                  | I D 1                                                               | 11 D OII       | AD IEDEO   |     |  |  |  |

| ENGR. C | CHK.         |           | 24LD, MLP, QUAD, JEDEC |                                                                     |                |            |     |  |  |  |

|         |              |           | 1                      | MO-220, 3.5x4.5 MM                                                  |                |            |     |  |  |  |

|         |              |           |                        | MU-Z                                                                | .ZU, J.J       | MM C.+X    |     |  |  |  |

|         |              |           |                        |                                                                     | ,              |            |     |  |  |  |

|         | PROJECTIO    | N         | SCALE                  | SIZE                                                                | DRAWING NUMBER |            | REV |  |  |  |

| 1 4     | $\neg$       | =         | N/A                    | N / A                                                               | MKT-           | -MLP24B    | 4   |  |  |  |

| 1 6     |              | _         | 11//                   | ' '/ '                                                              | IVIIVI         | IVILIZID   |     |  |  |  |

|         | INCH<br>[MM] | ~         | DO NOT                 | SCALE                                                               | DRAWING        | SHEET 1 of | 1   |  |  |  |

ON Semiconductor and in are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdt/Patent-Marking.pdf">www.onsemi.com/site/pdt/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and exp

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910

Japan Customer Focus Center

Phone: 81-3-5817-1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

FSSD07UMX FSSD07BQX