# LPR550AL

## MEMS motion sensor: dual axis pitch and roll ±500°/s analog gyroscope

### Preliminary data

### Features

- 2.7 V to 3.6 V single-supply operation

- Wide operating temperature range (-40 °C to +85 °C)

- High stability overtemperature

- Analog absolute angular-rate output

- Two separate outputs for each axis (1x and 4x amplified)

- Integrated low-pass filters

- Low power consumption

- Embedded power-down

- Embedded self-test

- High shock and vibration survivability

- ECOPACK<sup>®</sup> RoHS and "Green" compliant (see Section 5)

### **Applications**

- Pointing devices, remote and game controllers

- Gaming applications

- Motion control with user interface

- Industrial and robotics

### Description

The LPR550AL is a low-power dual-axis micromachined gyroscope capable of measuring angular rate along pitch and roll axes.

It provides excellent temperature stability and high resolution over an extended operating temperature range (-40 °C to +85 °C).

The LPR550AL has a full scale of  $\pm$  500 °/s and is capable of detecting rates with a -3 dB bandwidth up to 140 Hz.

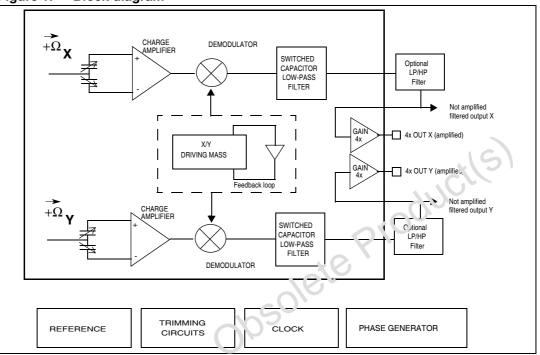

The gyroscope is the combination of one actuator and one acceleremeter integrated in a single micromachined structure.

It includes a sensing element composed by single driving mass, kept in continuous oscillating movement and able to react when an angular rate is applied based on the Coriolis principle.

A CMOS IC provides the measured angular rate to the external world through an analog output voltage, allowing high level of integration and production trimming to better match sensing element characteristics.

ST's gyroscope family leverages on robust and mature manufacturing process already used for the production of micromachined accelerometers.

ST is already in the field with several hundreds million sensors with excellent acceptance from the market in terms of quality, reliability and performance.

LPR550AL is provided in plastic land grid array (LGA) package. Several years ago ST pioneered successfully the usage of this package for accelerometers. Today ST has the widest manufacturing capability and strongest expertise in the world for production of sensor in plastic LGA package.

### Table 1. Device summary

| Order code | Temperature range (°C) | Package          | Packing       |

|------------|------------------------|------------------|---------------|

| LPR550AL   | -40 to +85             | LGA-16 (5x5x1.5) | Tray          |

| LPR550ALTR | -40 to +85             | LGA-16 (5x5x1.5) | Tape and reel |

Doc ID 15813 Rev 2

This is preliminary information on a new product now in development or undergoing evaluation. Details are subject to change without notice.

# Contents

| 1    | Block diagram and pin description |                                        |  |  |

|------|-----------------------------------|----------------------------------------|--|--|

|      | 1.1                               | Pin description                        |  |  |

| 2    | Мес                               | hanical and electrical specifications5 |  |  |

|      | 2.1                               | Mechanical characteristics 5           |  |  |

|      | 2.2                               | Electrical characteristics 6           |  |  |

|      | 2.3                               | Absolute maximum ratings 6             |  |  |

| 3    | Tern                              | ninology                               |  |  |

|      | 3.1                               | Sensitivity                            |  |  |

|      | 3.2                               | Zero-rate level                        |  |  |

|      | 3.3                               | Self-test                              |  |  |

|      | 3.4                               | High pass filter reset (HP) 7          |  |  |

| 4    | Арр                               | lication hints                         |  |  |

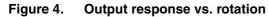

|      | 4.1                               | Output response vs. rotation           |  |  |

|      | 4.2                               | Soldering information                  |  |  |

| 5    | Pack                              | cage information                       |  |  |

| 6    | Revi                              | is on history                          |  |  |

|      | ete                               |                                        |  |  |

| 0050 |                                   |                                        |  |  |

|      |                                   |                                        |  |  |

## **1** Block diagram and pin description

### Figure 1. Block diagram

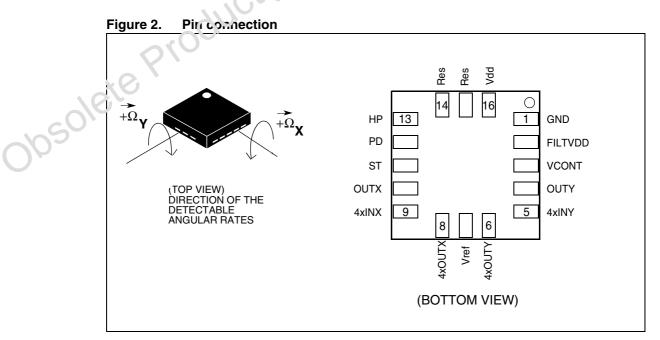

## 1.1 Pin description

57

| 12 PD mode)   13 HP High pass filter recet (logic 0: normal operation mologic1: externer, high pass filter is reset)   14,15 Res Trecerved. Connect to Vdd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Table 2. | Findescription |                                                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------------|---------------------------------------------------------------------------------------------------------|

| 2   FILTVDD   PLL filter connection pin #2     3   VCONT   PLL filter connection pin #1     4   OUTY   Not amplified output     5   4xINY   Input of 4x amplifier     6   4xOUTY   Y rate signal output voltage (amplified)     7   Vref   Reference voltage     8   4xOUTX   X rate signal output voltage (amplified)     9   4xINX   Input of 4x amplifier     10   OUTX   Not amplified output     11   ST   Self-test (logic 0: normal mode, logic 1: self-test)     12   PD   Power-down (logic 0: normal mode; logic 1: power-mode)     13   HP   High pass filter recet (logic 0: normal operation mode)     14,15   Res   Frecerved. Connect to Vdd | Pin #    | Pin name       | Analog function                                                                                         |

| 3   VCONT   PLL filter connection pin #1     4   OUTY   Not amplified output     5   4xINY   Input of 4x amplifier     6   4xOUTY   Y rate signal output voltage (amplified)     7   Vref   Reference voltage     8   4xOUTX   X rate signal output voltage (amplified)     9   4xINX   Input of 4x amplifier     10   OUTX   Not amplified output     11   ST   Self-test (logic 0: normal mode; logic 1: self-test)     12   PD   Power-down (logic 0: normal mode; logic 1: power-mode)     13   HP   High pass filter recet (logic 0: normal operation mologic1: externet, high pass filter is reset)     14,15   Res   Trecerved. Connect to Vdd       | 1        | GND            | 0V supply voltage                                                                                       |

| 4OUTYNot amplified output54xINYInput of 4x amplifier64xOUTYY rate signal output voltage (amplified)7VrefReference voltage84xOUTXX rate signal output voltage (amplified)94xINXInput of 4x amplifier10OUTXNot amplified output11STSelf-test (logic 0: normal mode; logic 1: self-test)12PDPower-down (logic 0: normal mode; logic 1: power-mode)13HPHigh pass filter recet (logic 0: normal operation mologic1: externel high pass filter is reset)14,15ResTrecerved. Connect to Vdd                                                                                                                                                                         | 2        | FILTVDD        | PLL filter connection pin #2                                                                            |

| 54xINYInput of 4x amplifier64xOUTYY rate signal output voltage (amplified)7VrefReference voltage84xOUTXX rate signal output voltage (amplified)94xINXInput of 4x amplifier10OUTXNot amplified output11STSelf-test (logic 0: normal mode; logic 1: self-test)12PDPower-down (logic 0: normal mode; logic 1: power-mode)13HPHigh pass filter recet (logic 0: normal operation mologic1: externer, high pass filter is reset)14,15ResTrecerved. Connect to Vdd                                                                                                                                                                                                 | 3        | VCONT          | PLL filter connection pin #1                                                                            |

| 6   4xOUTY   Y rate signal output voltage (amplified)     7   Vref   Reference voltage     8   4xOUTX   X rate signal output voltage (amplified)     9   4xINX   Input of 4x amplifier     10   OUTX   Not amplified output     11   ST   Self-test (logic 0: normal mode, logic 1: self-test)     12   PD   Power-down (logic 0: normal mode; logic 1: power-mode)     13   HP   High pass filter recet (logic 0: normal operation mologic1: externet, high pass filter is reset)     14,15   Res   /neterved. Connect to Vdd                                                                                                                              | 4        | OUTY           | Not amplified output                                                                                    |

| 7   Vref   Reference voltage     8   4xOUTX   X rate signal output voltage (amplified)     9   4xINX   Input of 4x amplifier     10   OUTX   Not amplified output     11   ST   Self-test (logic 0: normal mode, logic 1: self-test)     12   PD   Power-down (logic 0: normal mode; logic 1: power-mode)     13   HP   High pass filter report (logic 0: normal operation mode)     14,15   Res   Step refer to Vdd                                                                                                                                                                                                                                        | 5        | 4xINY          | Input of 4x amplifier                                                                                   |

| 8   4xOUTX   X rate signal output voltage (amplified)     9   4xINX   Input of 4x amplifier     10   OUTX   Not amplified output     11   ST   Self-test (logic 0: normal mode; logic 1: self-test)     12   PD   Power-down (logic 0: normal mode; logic 1: power-mode)     13   HP   High pass filter recet (logic 0: normal operation mologic1: externet high pass filter is reset)     14,15   Res   Trecerved. Connect to Vdd                                                                                                                                                                                                                          | 6        | 4xOUTY         | Y rate signal output voltage (amplified)                                                                |

| 9   4xINX   Input of 4x amplifier     10   OUTX   Not amplified output     11   ST   Self-test (logic 0: normal mode, logic 1: self-test)     12   PD   Power-down (logic 0: normal mode; logic 1: power-mode)     13   HP   High pass filter recet (logic 0: normal operation mologic1: externel high pass filter is reset)     14,15   Res   /neterved. Connect to Vdd                                                                                                                                                                                                                                                                                    | 7        | Vref           | Reference voltage                                                                                       |

| 10   OUTX   Not amplified output     11   ST   Self-test (logic 0: normal mode, logic 1: self-test)     12   PD   Power-down (logic 0: normal mode; logic 1: power-mode)     13   HP   High pass filter recet (logic 0: normal operation mologic1: externel high pass filter is reset)     14,15   Res   Trecerved. Connect to Vdd                                                                                                                                                                                                                                                                                                                          | 8        | 4xOUTX         | X rate signal output voltage (amplified)                                                                |

| 11   ST   Self-test (logic 0: normal mode, logic 1: self-test)     12   PD   Power-down (logic 0: normal mode; logic 1: power-mode)     13   HP   High pass filter recet (logic 0: normal operation mologic1: externed high pass filter is reset)     14,15   Res   Trecerved. Connect to Vdd                                                                                                                                                                                                                                                                                                                                                               | 9        | 4xINX          | Input of 4x amplifier                                                                                   |

| 12 PD Power-down (logic 0: normal mode; logic 1: power-mode)   13 HP High pass filter recet (logic 0: normal operation mologic1: externer, high pass filter is reset)   14,15 Res Trecerved. Connect to Vdd                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 10       | OUTX           | Not amplified output                                                                                    |

| 12 PD mode)   13 HP High pass filter recent (logic 0: normal operation mologic1: external high pass filter is reset)   14,15 Res Second Connect to Vdd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 11       | ST             | Self-test (logic 0: normal moc'e, logic 1: self-test)                                                   |

| 13HPlogic1: existing high pass filter is reset)14,15ResInecerved. Connect to Vdd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 12       | PD             | Power-down (logic 0: norma' mode; logic 1: power-down mode)                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 13       | HP             | High pass filter recet (logic 0: normal operation mode;<br>logic1: existing, high pass filter is reset) |

| 16 Vdd Fower supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 14,15    | Res            | Treasived. Connect to Vdd                                                                               |

| ct(S)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 16       | Vdd            | Fower supply                                                                                            |

| 16 Vdd Fover supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Pr       | oduct(S)       |                                                                                                         |

Table 2.Pin description

## 2 Mechanical and electrical specifications

### 2.1 Mechanical characteristics

### Table 3.Mechanical characteristics @ Vdd = 3 V, T = 25 °C unless otherwise noted<sup>(1)</sup>

| Symbol | Parameter                                | Test condition         | Min. | Typ. <sup>(2)</sup> | Max. | Unit     |

|--------|------------------------------------------|------------------------|------|---------------------|------|----------|

| FSA    | Measurement range                        | 4x OUT (amplified)     |      | ±500                |      | °/s      |

| FS     | Measurement range                        | OUT (not amplified)    |      | ±2000               |      | °/s      |

| SoA    | Sensitivity <sup>(3)</sup>               | 4x OUT (amplified)     |      | 2                   |      | mV/ °/s  |

| So     | Sensitivity                              | OUT (not amplified)    |      | 0.5                 |      | m`// °/s |

| SoDr   | Sensitivity change vs temperature        | Delta from 25°C        |      | 0.03                | Ċ    | ∽⁄₀/°C   |

| Voff   | Zero-rate level <sup>(3)</sup>           |                        |      | 1.23                | XV   | V        |

| Vref   | Reference voltage                        |                        |      | 1.23                | 00   | V        |

| OffDr  | Zero-rate level change<br>Vs temperature | Delta from 25°C        |      | 0. 18               |      | °/s/°C   |

| NL     | Non linearity                            | Best fit straight line | 0    | ±1                  |      | % FS     |

| BW     | Bandwidth <sup>(4)</sup>                 |                        |      | 140                 |      | Hz       |

| Rn     | Rate noise density                       |                        | 5    | 0.059               |      | °/s//Hz  |

| Тор    | Operating<br>temperature range           | 0                      | -40  |                     | +85  | °C       |

1. The product is factory calibrated at 3 V. The opgratic nal power supply range is specified in Table 4.

2. Typical specifications are not guaranteed

3. Sensitivity and zero-rate level are not ratio netric to supply voltage

4. The product is capable of measuring angular rates extending from DC to the selected BW.

#### 2.2 **Electrical characteristics**

Electrical characteristics @ Vdd =3 V, T=25 °C unless otherwise noted<sup>(1)</sup> Table 4.

| Symbol                                       | Parameter                            | meter Test condition    |         | Typ. <sup>(2)</sup> | Max.      | Unit |  |

|----------------------------------------------|--------------------------------------|-------------------------|---------|---------------------|-----------|------|--|

| Vdd                                          | Supply voltage                       |                         | 2.7     | 3                   | 3.6       | V    |  |

| ldd                                          | Supply current                       | PD pin connected to GND |         | 6.8                 |           | mA   |  |

| IddPdn                                       | Supply current in<br>power-down mode | PD pin connected to Vdd |         | 1                   | 5         | μA   |  |

| Vst                                          | Solf toot input                      | Logic 0 level           | 0       |                     | 0.2*Vdd   | v    |  |

| V51                                          | Self-test input                      | Logic 1 level           | 0.8*Vdd |                     | Vdd       | ľ    |  |

| VPD                                          | Power down input                     | Logic 0 level           | 0       |                     | 0.2*\'לגי |      |  |

| VPD                                          | Power-down input                     | Logic 1 level           | 0.8*Vdd |                     | \'dr.     | v    |  |

| Тор                                          | Operating temperature range          |                         | -40     | 200                 | +85       | °C   |  |

| 1. The product is factory calibrated at 3 V  |                                      |                         |         |                     |           |      |  |

| 2. Typical specifications are not guaranteed |                                      |                         |         |                     |           |      |  |

| 2. Typical specifications are not guaranteed |                                      |                         |         |                     |           |      |  |

| 2.3 Absolute maximum ratings                 |                                      |                         |         |                     |           |      |  |

|                                              |                                      |                         |         |                     |           |      |  |

#### Absolute maximum ratings 2.3

Stresses above those listed as "Abso ute maximum ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device under these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

|          | G                        |

|----------|--------------------------|

| Table 5. | Absolute maximum ratings |

| Symbol |                  | Ratings                                   | Maximum value             | Unit |

|--------|------------------|-------------------------------------------|---------------------------|------|

|        | Vdd              | Supply voltage                            | -0.3 to 6                 | V    |

|        | ריע              | Input voltage on any control pin (PD, ST) | -0.3 to Vdd +0.3          | V    |

| Obsole | T <sub>STG</sub> | Storage temperature range                 | -40 to +125               | °C   |

|        | А                | Acceleration                              | 3000 <i>g</i> for 0.5 ms  |      |

|        |                  | Acceleration                              | 10000 <i>g</i> for 0.1 ms |      |

|        | ESD              | Electrostatic discharge protection        | 2 (HBM)                   | kV   |

This is a mechanical shock sensitive device, improper handling can cause permanent damage to the part

This is an ESD sensitive device, improper handling can cause permanent damage to the part

### 3 Terminology

### 3.1 Sensitivity

An angular rate gyroscope is a device that produces a positive-going output voltage for counterclockwise rotation around the sensitive axis considered. Sensitivity describes the gain of the sensor and can be determined by applying a defined angular velocity to it. This value changes very little over temperature and time.

### 3.2 Zero-rate level

Zero-rate level describes the actual output signal if there is no angular rate present. The zero-rate level of precise MEMS sensors is, to some extent, a result of stress to the sensor and therefore zero-rate level can slightly change after mounting the sensor onto a printed circuit board or after exposing it to extensive mechanical stress. This value changes very little over temperature and time.

### 3.3 Self-test

Self-test allows testing of the mechanical and electrical part of the sensor, allowing the seismic mass to be moved by means of an electrication test-force. The self-test function is off when the ST pin is connected to GND. When the ST pin is tied to Vdd, an actuation force is applied to the sensor, emulating a definite Coriolis force. In this case the sensor output will exhibit a voltage change in its DC level which is also dependent on the supply voltage. When ST is active, the device output level is given by the algebraic sum of the signals produced by the velocity acting on the sensor and by the electrostatic test-force. If the output signals change within the amplitude specified in *Table 3*, then the mechanical element is working properly and the parameters of the interface chip are within the defined specifications.

### 3.4 High pass filter reset (HP)

The LPR550AL provides the possibility to reset the optional external high pass filter by applying a high logic value to the HP pad. This procedure ensures faster response, especially during overload conditions. Moreover, this operation is suggested each time the device is powered.

## 4 Application hints

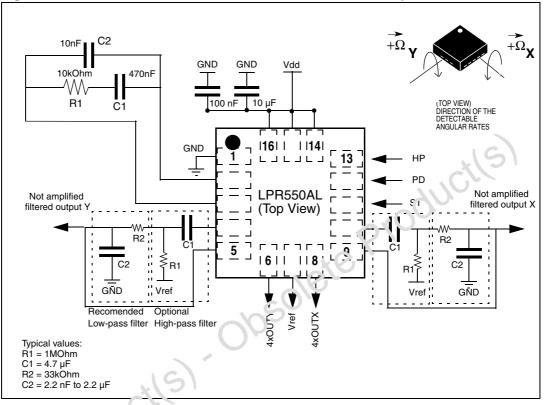

Figure 3. LPR550AL electrical connections and external component values

Power supply decoupling capacitors (100 nF ceramic or polyester + 10  $\mu$ F Aluminum) should be placed as near as possible to the device (common design practice).

The LP  $\pi_5$ :0AL allows band limiting the output rate response through the use of an external low pass filter (suggested) and/or high pass filter (optional) in addition to the embedded low  $\pi_5$  filter (f<sub>t</sub> = 140 Hz).

4xOUTX and 4xOUTY are respectively OUTX and OUTY amplified outputs lines, internally buffered to ensure low output impedance.

If external high pass or low pass filtering is not applied it is mandatory to short-circuit respectively pad 4 to pad 5 and pad 9 to pad 10 when amplified outputs are used.

When only not\_amplified outputs are used (OUTX/Y), it is suggested to set pads 5 and 9 to fixed reference voltage (GND/Vref).

When high pass filter is applied to not amplified output (OUTx), it is recommended to buffer the line before entering ADC for performance optimization.

The LPR550AL IC includes a PLL (phase locked loop) circuit to synchronize driving and sensing interfaces. Capacitors and resistors must be added at the **FILTVDD** and **VCONT** pins (as shown in *Figure 3*) to implement a low-pass filter.

### 4.1 Output response vs. rotation

### 4.2 Soldering information

The LGA package is compliant with the ECOPACK<sup>®</sup>, Fulls and "Green" standard. It is qualified for soldering heat resistance according to JEDEC J-STD-020C.

Leave "pin 1 indicator" unconnected during sudsting.

Land pattern and soldering recommendations are available at www.st.com.

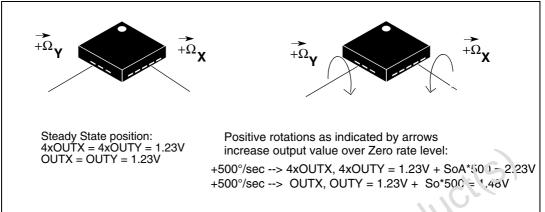

### 5 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: www.st.com. ECOPACK is an ST trademark.

Doc ID 15813 Rev 2

## 6 Revision history

### Table 6.Document revision history

|        | Date        | Revision | Changes                                                              |

|--------|-------------|----------|----------------------------------------------------------------------|

|        | 04-Jun-2009 | 1        | Initial release                                                      |

|        | 06-Jul-2009 | 2        | Small text changes to improve readability.<br>Updated <i>Table 4</i> |

| obsole | tepro       | Jucil    | opared rapie 4                                                       |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidia. ie: (ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and ser ices doscribed herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and solvices described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property Liq. is is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a licer se grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a tria ranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein or considered as a tria ranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained to the trian the trian trian.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR BALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOP A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN VIRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRCD JC 'S OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PF OP IN TY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of S. p. of ucts with provisions different from the statements and/or technical features set forth in this document shall immediately void any war any granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability, of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2009 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

Doc ID 15813 Rev 2

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

STMicroelectronics: LPR550ALTR LPR550AL